Академический Документы

Профессиональный Документы

Культура Документы

EE 471 Group12 Lab3 Report

Загружено:

Le HieuИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

EE 471 Group12 Lab3 Report

Загружено:

Le HieuАвторское право:

Доступные форматы

EE471 Lab 3 Report

Designing an ALU

Working with an SRAM, Reg File, I/O,

and C Stuff Cont.

GROUP 12

Nguyn c Phc

L Trung Hiu

Trn Anh Hng Nga

EE471 Lab 03 Report

Group 12

I. Abstract:

The objective of this lab project is:

Design, implement, and test the circuitry to support the arithmetic operations ADD

and SUBTRACT.

Design, implement, and test the circuitry to support the logical operations shift,

comparison, AND, OR, exclusive OR.

Integrate the ALU subsystem with the SRAM and register file subsystems.

Learn and work with basic C variables and their addresses.

II. Introduction:

In this third project, we will build upon some of the things thatwe have learned in the

second one then add some new ideas. Our initial objective will be to design, implement, and test

a simplified arithmetic and logic unit ALU. The ALU will support the arithmetic operations

addition and subtraction and the logical operations shift, comparison, AND, OR, and exclusive

OR. We will then integrate the ALU with the SRAM and register file subsystems.

Finally, we will continue to grow our knowledge of the C language by working with variables

and their addresses. We will see that our earlier work with the SRAM carries directly to our

studies of C variables and their addresses.

III. Design procedure:

Designing and Bulding an ALU

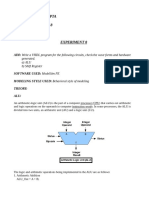

For the first part of the lab, we will design, implement, and test a basic ALU. We will then

integrate it with the memory subsystem we developed earlier. This design will only support

subset of the arithmetic and logical functionality typically found in an industrial strength

ALU. A high-level block diagram for the unit is given in the accompanying figure.

The subsystem supports three unidirectional data busses (two in and one out), one control

bus, and four status flags or bits.

EE471 Lab 03 Report

Group 12

The ALU will support the following operations:

Arithmetic

1. Addition

2. Subtraction

Logical

1. AND

2. OR

3. XOR

4. SLT set less than (see your text)

5. SLL shift left logical 0..3 positions

EE471 Lab 03 Report

Group 12

A. VERILOG CODE

1. Module NOP

//NOP

module Nop(nop,negative_nop,zero_nop);

output wire [31:0]nop;

output wire negative_nop,zero_nop;

buf buf0(nop[0],1'b0);

buf buf1(nop[1],1'b0);

buf buf2(nop[2],1'b0);

buf buf3(nop[3],1'b0);

buf buf4(nop[4],1'b0);

buf buf5(nop[5],1'b0);

buf buf6(nop[6],1'b0);

buf buf7(nop[7],1'b0);

buf buf8(nop[8],1'b0);

buf buf9(nop[9],1'b0);

buf buf10(nop[10],1'b0);

buf buf11(nop[11],1'b0);

buf buf12(nop[12],1'b0);

buf buf13(nop[13],1'b0);

buf buf14(nop[14],1'b0);

buf buf15(nop[15],1'b0);

buf buf16(nop[16],1'b0);

buf buf17(nop[17],1'b0);

buf buf18(nop[18],1'b0);

buf buf19(nop[19],1'b0);

buf buf20(nop[20],1'b0);

buf buf21(nop[21],1'b0);

buf buf22(nop[22],1'b0);

buf buf23(nop[23],1'b0);

buf buf24(nop[24],1'b0);

buf buf25(nop[25],1'b0);

buf buf26(nop[26],1'b0);

buf buf27(nop[27],1'b0);

buf buf28(nop[28],1'b0);

buf buf29(nop[29],1'b0);

buf buf30(nop[30],1'b0);

buf buf31(nop[31],1'b0);

buf buf32(negative_nop,1'b0);

buf buf33(zero_nop,1'b0);

endmodule

EE471 Lab 03 Report

Group 12

2. Module FULLADDER

// Fulladder

module fulladder(s, c, x, y, c0);

output s, c;

input x, y, c0;

parameter delay = 0;

xor #delay xor1(s, x, y, c0);

and #delay and1(z1, x, y);

and #delay and2(z2, x, c0);

and #delay and3(z3, y, c0);

or #delay or1(c, z1, z2, z3);

endmodule

3. Module MUX_2TO1

// MUX_2TO1

module MUX_2to1(f,a,b,sel);

input a,b,sel;

output f;

parameter delay = 0;

not #delay not1(nsel,sel);

and #delay and1(f1,a,nsel);

and #delay and2(f2,b,sel);

or #delay or1(f,f1,f2);

endmodule

4. Module ADD_SUB1BIT

// ADD_SUB1BIT

// fulladder(add_sub) each bit

// To select Addition or Subtraction operation

// sel=0-->add=A+B+0, sel=1-->sub=A+notB+1

module Add_Sub1bit(sum, Cout, x, y, Cin, sel);

input x, y, Cin, sel;

output sum, Cout;

parameter delay = 0;

not #delay not1(noty, y);

wire result;

MUX_2to1 mymux(result,y,noty,sel);

fulladder myfulladder (sum, Cout, x, result, Cin);

endmodule

EE471 Lab 03 Report

Group 12

5. Module ADD_SUB32BIT

// ADD_SUB32BIT

module Add_Sub32bit(sum, Cout, overflow, negative, zero, x, y, control);

input [31:0] x,y;

input control;

output [31:0]sum;

output Cout,zero,overflow,negative;

parameter delay = 0;

Add_Sub1bit bit0(sum[0], Cout0, x[0], y[0], control, control);

Add_Sub1bit bit1(sum[1], Cout1, x[1], y[1], Cout0, control);

Add_Sub1bit bit2(sum[2], Cout2, x[2], y[2], Cout1, control);

Add_Sub1bit bit3(sum[3], Cout3, x[3], y[3], Cout2, control);

Add_Sub1bit bit4(sum[4], Cout4, x[4], y[4], Cout3, control);

Add_Sub1bit bit5(sum[5], Cout5, x[5],y[5],Cout4, control);

Add_Sub1bit bit6(sum[6], Cout6, x[6],y[6],Cout5, control);

Add_Sub1bit bit7(sum[7], Cout7, x[7],y[7],Cout6, control);

Add_Sub1bit mybit8(sum[8],Cout8,x[8],y[8],Cout7, control);

Add_Sub1bit mybit9(sum[9],Cout9,x[9],y[9],Cout8, control);

Add_Sub1bit mybit10(sum[10],Cout10,x[10],y[10],Cout9, control);

Add_Sub1bit mybit11(sum[11],Cout11,x[11],y[11],Cout10, control);

Add_Sub1bit mybit12(sum[12],Cout12,x[12],y[12],Cout11, control);

Add_Sub1bit mybit13(sum[13],Cout13,x[13],y[13],Cout12, control);

Add_Sub1bit mybit14(sum[14],Cout14,x[14],y[14],Cout13, control);

Add_Sub1bit mybit15(sum[15],Cout15,x[15],y[15],Cout14, control);

Add_Sub1bit bit16(sum[16],Cout16,x[16],y[16],Cout15, control);

Add_Sub1bit bit17(sum[17],Cout17,x[17],y[17],Cout16, control);

Add_Sub1bit bit18(sum[18],Cout18,x[18],y[18],Cout17, control);

Add_Sub1bit bit19(sum[19],Cout19,x[19],y[19],Cout18, control);

Add_Sub1bit bit20(sum[20],Cout20,x[20],y[20],Cout19, control);

Add_Sub1bit bit21(sum[21],Cout21,x[21],y[21],Cout20, control);

Add_Sub1bit bit22(sum[22],Cout22,x[22],y[22],Cout21, control);

Add_Sub1bit bit23(sum[23],Cout23,x[23],y[23],Cout22, control);

Add_Sub1bit bit24(sum[24],Cout24,x[24],y[24],Cout23, control);

Add_Sub1bit bit25(sum[25],Cout25,x[25],y[25],Cout24, control);

Add_Sub1bit bit26(sum[26],Cout26,x[26],y[26],Cout25, control);

Add_Sub1bit bit27(sum[27],Cout27,x[27],y[27],Cout26, control);

Add_Sub1bit bit28(sum[28],Cout28,x[28],y[28],Cout27, control);

Add_Sub1bit bit29(sum[29],Cout29,x[29],y[29],Cout28, control);

Add_Sub1bit bit30(sum[30],Cout30,x[30],y[30],Cout29, control);

Add_Sub1bit bit31(sum[31],Cout, x[31],y[31],Cout30, control);

xor #delay xor1(overflow,Cout30,Cout);

EE471 Lab 03 Report

Group 12

and #delay and1(negative,1,sum[31]);//NEGATIVE DETECTION

zero myzero(zero,sum);//ZERO DETECTION

endmodule

6. Module ZERO DETECTION

// ZERO DETECTION

module zero(flag_0,sum);

input [31:0]sum;

output flag_0;

parameter delay = 0;

or #delay or1 (temp1, sum[0],sum[1],sum[2],sum[3]);

or #delay or2 (temp2, sum[4],sum[5],sum[6],sum[7]);

or #delay or3 (temp3, sum[8],sum[9],sum[10],sum[11]);

or #delay or4 (temp4, sum[12],sum[13],sum[14],sum[15]);

or #delay or5 (temp5, sum[16],sum[17],sum[18],sum[19]);

or #delay or6 (temp6, sum[20],sum[21],sum[22],sum[23]);

or #delay or7 (temp7, sum[24],sum[25],sum[26],sum[27]);

or #delay or8 (temp8, sum[28],sum[29],sum[30],sum[31]);

or #delay or9 (temp9, temp1,temp2,temp3,temp4);

or #delay or10(temp10, temp5,temp6,temp7,temp8);

nor #delay nor1 (flag_0,temp9,temp10);

endmodule

7. Module SLT

// SLT

module slt(Less,zero_slt,negative_slt, x, y); //////underconstruction

output wire [31:0] Less;

input[31:0] x, y;

output wire negative_slt,zero_slt;

parameter delay = 0;

wire [31:0] sum;

wire Cout, Overflow,zero,negative;

assign Less[31:1] = 0;

Add_Sub32bit my1(sum, Cout, Overflow, negative,zero, x, y, 1);//Subtraction

xor #delay xor1(Less[0], sum[31], Overflow);

and #delay and1(negative_slt,1,Less[31]);//NEGATIVE DETECTION

zero myzero(zero_slt,Less);//ZERO DETECTION

endmodule

EE471 Lab 03 Report

Group 12

8. Module XOR

// XOR

module XOR_function(result_xor, zero_xor, negative_xor, x, y);

input [31:0] x,y;

output [31:0] result_xor;

output zero_xor, negative_xor;

parameter delay = 0;

xor #delay xor0(result_xor[0],x[0],y[0]);

xor #delay xor1(result_xor[1],x[1],y[1]);

xor #delay xor2(result_xor[2],x[2],y[2]);

xor #delay xor3(result_xor[3],x[3],y[3]);

xor #delay xor4(result_xor[4],x[4],y[4]);

xor #delay xor5(result_xor[5],x[5],y[5]);

xor #delay xor6(result_xor[6],x[6],y[6]);

xor #delay xor7(result_xor[7],x[7],y[7]);

xor #delay xor8(result_xor[8],x[8],y[8]);

xor #delay xor9(result_xor[9],x[9],y[9]);

xor #delay xor10(result_xor[10],x[10],y[10]);

xor #delay xor11(result_xor[11],x[11],y[11]);

xor #delay xor12(result_xor[12],x[12],y[12]);

xor #delay xor13(result_xor[13],x[13],y[13]);

xor #delay xor14(result_xor[14],x[14],y[14]);

xor #delay xor15(result_xor[15],x[15],y[15]);

xor #delay xor16(result_xor[16],x[16],y[16]);

xor #delay xor17(result_xor[17],x[17],y[17]);

xor #delay xor18(result_xor[18],x[18],y[18]);

xor #delay xor19(result_xor[19],x[19],y[19]);

xor #delay xor20(result_xor[20],x[20],y[20]);

xor #delay xor21(result_xor[21],x[21],y[21]);

xor #delay xor22(result_xor[22],x[22],y[22]);

xor #delay xor23(result_xor[23],x[23],y[23]);

xor #delay xor24(result_xor[24],x[24],y[24]);

xor #delay xor25(result_xor[25],x[25],y[25]);

xor #delay xor26(result_xor[26],x[26],y[26]);

xor #delay xor27(result_xor[27],x[27],y[27]);

xor #delay xor28(result_xor[28],x[28],y[28]);

xor #delay xor29(result_xor[29],x[29],y[29]);

xor #delay xor30(result_xor[30],x[30],y[30]);

xor #delay xor31(result_xor[31],x[31],y[31]);

and #delay and1(negative_xor,1,result_xor[31]);//NEGATIVE DETECTION

EE471 Lab 03 Report

Group 12

zero myzero(zero_xor,result_xor);//ZERO DETECTION

endmodule

9. Module AND

// AND

module AND_function(result_and, zero_and, negative_and, x, y);

input [31:0] x,y;

output [31:0] result_and;

output zero_and, negative_and;

parameter delay = 0;

and #delay and0(result_and[0],x[0],y[0]);

and #delay and1(result_and[1],x[1],y[1]);

and #delay and2(result_and[2],x[2],y[2]);

and #delay and3(result_and[3],x[3],y[3]);

and #delay and4(result_and[4],x[4],y[4]);

and #delay and5(result_and[5],x[5],y[5]);

and #delay and6(result_and[6],x[6],y[6]);

and #delay and7(result_and[7],x[7],y[7]);

and #delay and8(result_and[8],x[8],y[8]);

and #delay and9(result_and[9],x[9],y[9]);

and #delay and10(result_and[10],x[10],y[10]);

and #delay and11(result_and[11],x[11],y[11]);

and #delay and12(result_and[12],x[12],y[12]);

and #delay and13(result_and[13],x[13],y[13]);

and #delay and14(result_and[14],x[14],y[14]);

and #delay and15(result_and[15],x[15],y[15]);

and #delay and16(result_and[16],x[16],y[16]);

and #delay and17(result_and[17],x[17],y[17]);

and #delay and18(result_and[18],x[18],y[18]);

and #delay and19(result_and[19],x[19],y[19]);

and #delay and20(result_and[20],x[20],y[20]);

and #delay and21(result_and[21],x[21],y[21]);

and #delay and22(result_and[22],x[22],y[22]);

and #delay and23(result_and[23],x[23],y[23]);

and #delay and24(result_and[24],x[24],y[24]);

and #delay and25(result_and[25],x[25],y[25]);

and #delay and26(result_and[26],x[26],y[26]);

and #delay and27(result_and[27],x[27],y[27]);

and #delay and28(result_and[28],x[28],y[28]);

and #delay and29(result_and[29],x[29],y[29]);

EE471 Lab 03 Report

Group 12

and #delay and30(result_and[30],x[30],y[30]);

and #delay and31(result_and[31],x[31],y[31]);

and #delay and32(negative_and,1,result_and[31]);//NEGATIVE DETECTION

zero myzero(zero_and,result_and);//ZERO DETECTION

endmodule

10. Module OR

// OR

module OR_function(result_or, zero_or, negative_or, x, y);

input [31:0] x,y;

output [31:0] result_or;

output zero_or, negative_or;

parameter delay = 0;

or #delay or0(result_or[0],x[0],y[0]);

or #delay or1(result_or[1],x[1],y[1]);

or #delay or2(result_or[2],x[2],y[2]);

or #delay or3(result_or[3],x[3],y[3]);

or #delay or4(result_or[4],x[4],y[4]);

or #delay or5(result_or[5],x[5],y[5]);

or #delay or6(result_or[6],x[6],y[6]);

or #delay or7(result_or[7],x[7],y[7]);

or #delay or8(result_or[8],x[8],y[8]);

or #delay or9(result_or[9],x[9],y[9]);

or #delay or10(result_or[10],x[10],y[10]);

or #delay or11(result_or[11],x[11],y[11]);

or #delay or12(result_or[12],x[12],y[12]);

or #delay or13(result_or[13],x[13],y[13]);

or #delay or14(result_or[14],x[14],y[14]);

or #delay or15(result_or[15],x[15],y[15]);

or #delay or16(result_or[16],x[16],y[16]);

or #delay or17(result_or[17],x[17],y[17]);

or #delay or18(result_or[18],x[18],y[18]);

or #delay or19(result_or[19],x[19],y[19]);

or #delay or20(result_or[20],x[20],y[20]);

or #delay or21(result_or[21],x[21],y[21]);

or #delay or22(result_or[22],x[22],y[22]);

or #delay or23(result_or[23],x[23],y[23]);

or #delay or24(result_or[24],x[24],y[24]);

or #delay or25(result_or[25],x[25],y[25]);

or #delay or26(result_or[26],x[26],y[26]);

EE471 Lab 03 Report

Group 12

10

or #delay or27(result_or[27],x[27],y[27]);

or #delay or28(result_or[28],x[28],y[28]);

or #delay or29(result_or[29],x[29],y[29]);

or #delay or30(result_or[30],x[30],y[30]);

or #delay or31(result_or[31],x[31],y[31]);

and #delay and1(negative_or,1,result_or[31]);//NEGATIVE DETECTION

zero myzero(zero_or,result_or);//ZERO DETECTION

endmodule

11. AND SHIFT function

//AND SHIFT FUNCTION

module ANDshift_function(result_and, zero_and, negative_and, x, y);

input [31:0] x;

input y;

output [31:0] result_and;

output zero_and, negative_and;

parameter delay = 0;

and #delay and0(result_and[0],x[0],y);

and #delay and1(result_and[1],x[1],y);

and #delay and2(result_and[2],x[2],y);

and #delay and3(result_and[3],x[3],y);

and #delay and4(result_and[4],x[4],y);

and #delay and5(result_and[5],x[5],y);

and #delay and6(result_and[6],x[6],y);

and #delay and7(result_and[7],x[7],y);

and #delay and8(result_and[8],x[8],y);

and #delay and9(result_and[9],x[9],y);

and #delay and10(result_and[10],x[10],y);

and #delay and11(result_and[11],x[11],y);

and #delay and12(result_and[12],x[12],y);

and #delay and13(result_and[13],x[13],y);

and #delay and14(result_and[14],x[14],y);

and #delay and15(result_and[15],x[15],y);

and #delay and16(result_and[16],x[16],y);

and #delay and17(result_and[17],x[17],y);

and #delay and18(result_and[18],x[18],y);

and #delay and19(result_and[19],x[19],y);

and #delay and20(result_and[20],x[20],y);

and #delay and21(result_and[21],x[21],y);

and #delay and22(result_and[22],x[22],y);

EE471 Lab 03 Report

Group 12

11

and #delay and23(result_and[23],x[23],y);

and #delay and24(result_and[24],x[24],y);

and #delay and25(result_and[25],x[25],y);

and #delay and26(result_and[26],x[26],y);

and #delay and27(result_and[27],x[27],y);

and #delay and28(result_and[28],x[28],y);

and #delay and29(result_and[29],x[29],y);

and #delay and30(result_and[30],x[30],y);

and #delay and31(result_and[31],x[31],y);

and #delay and32(negative_and,1,result_and[31]);//NEGATIVE DETECTION

zero myzero(zero_and,result_and);//ZERO DETECTION

endmodule

12. Module SHIFT

//Shift module

module shift(shifta,a);

output [31:0]shifta;

input [31:0]a;

buf buf00(shifta[31],a[30]);

buf buf01(shifta[30],a[29]);

buf buf02(shifta[29],a[28]);

buf buf03(shifta[28],a[27]);

buf buf04(shifta[27],a[26]);

buf buf05(shifta[26],a[25]);

buf buf06(shifta[25],a[24]);

buf buf07(shifta[24],a[23]);

buf buf08(shifta[23],a[22]);

buf buf09(shifta[22],a[21]);

buf buf10(shifta[21],a[20]);

buf buf11(shifta[20],a[19]);

buf buf12(shifta[19],a[18]);

buf buf13(shifta[18],a[17]);

buf buf14(shifta[17],a[16]);

buf buf15(shifta[16],a[15]);

buf buf16(shifta[15],a[14]);

buf buf17(shifta[14],a[13]);

buf buf18(shifta[13],a[12]);

buf buf19(shifta[12],a[11]);

buf buf20(shifta[11],a[10]);

buf buf21(shifta[10],a[9]);

EE471 Lab 03 Report

Group 12

12

buf buf22(shifta[9],a[8]);

buf buf23(shifta[8],a[7]);

buf buf24(shifta[7],a[6]);

buf buf25(shifta[6],a[5]);

buf buf26(shifta[5],a[4]);

buf buf27(shifta[4],a[3]);

buf buf28(shifta[3],a[2]);

buf buf29(shifta[2],a[1]);

buf buf30(shifta[1],a[0]);

buf buf31(shifta[0],0);

endmodule

13. Module SHIFT LEFT CONTROL

//Shift left control MODULE

module sll(shift, zero, negative, SelectCode, x, y);

output [31:0]shift;

output zero, negative;

input [1:0]SelectCode;

input [31:0]x, y;

wire [1:0]nSelectCode;

wire [1:0]control;

wire [31:0]shiftx, shifty;

wire [31:0]shiftandx, shiftandy;

parameter delay = 0;

shift sll01(shiftx,x);

shift sll02(shifty,y);

not #delay not00(nSelectCode[0],SelectCode[0]);

not #delay not01(nSelectCode[1],SelectCode[1]);

and #delay and00(control[0],nSelectCode[0],nSelectCode[1]);

and #delay and01(control[1],SelectCode[0],nSelectCode[1]);

ANDshift_function and02(shiftandx, zero_andx, negative_andx, shiftx, control[0]);

ANDshift_function and03(shiftandy, zero_andy, negative_andy, shifty, control[1]);

OR_function or00(shift,,, shiftandx, shiftandy);

or #delay or01(zero, zero_andx, zero_andy);

or #delay or02(negative, negative_andx, negative_andy);

endmodule

14. Module MUX8TO1

// MUX8TO1 MODULE

module mux8to1(out,nop,add,Xor,And,Or,sub,slt,sll,s2,s1,s0);

output out;

input nop,add,sub,Xor,And,Or,slt,sll,s2,s1,s0;

parameter delay = 0;

EE471 Lab 03 Report

Group 12

13

not #delay not0(ns0,s0);

not #delay not1(ns1,s1);

not #delay not2(ns2,s2);

and #delay and0(temp0,nop,ns2,ns1,ns0);

and #delay and1(temp1,add,ns2,ns1,s0);

and #delay and2(temp2,sub,ns2,s1,ns0);

and #delay and3(temp3,And,ns2,s1,s0);

and #delay and4(temp4,Or,s2,ns1,ns0);

and #delay and5(temp5,Xor,s2,ns1,s0);

and #delay and6(temp6,slt,s2,s1,ns0);

and #delay and7(temp7,sll,s2,s1,s0);

or #delay or1(out,temp0,temp1,temp2,temp3,temp4,temp5,temp6,temp7);

endmodule

15. Module MUX8TO1_32BIT

// MUX8to1_32bit MODULE

module mux8to1_32bit(out,nop,add,Xor,And,Or,sub,slt,sll,s2,s1,s0);

output[31:0] out;

input[31:0] nop,add,sub,Xor,And,Or,slt,sll;

input s2,s1,s0;

mux8to1 bit0(out[0],nop[0],add[0],Xor[0],And[0],Or[0],sub[0],slt[0],sll[0],s2,s1,s0);

mux8to1 bit1(out[1],nop[1],add[1],Xor[1],And[1],Or[1],sub[1],slt[1],sll[1],s2,s1,s0);

mux8to1 bit2(out[2],nop[2],add[2],Xor[2],And[2],Or[2],sub[2],slt[2],sll[2],s2,s1,s0);

mux8to1 bit3(out[3],nop[3],add[3],Xor[3],And[3],Or[3],sub[3],slt[3],sll[3],s2,s1,s0);

mux8to1 bit4(out[4],nop[4],add[4],Xor[4],And[4],Or[4],sub[4],slt[4],sll[4],s2,s1,s0);

mux8to1 bit5(out[5],nop[5],add[5],Xor[5],And[5],Or[5],sub[5],slt[5],sll[5],s2,s1,s0);

mux8to1 bit6(out[6],nop[6],add[6],Xor[6],And[6],Or[6],sub[6],slt[6],sll[6],s2,s1,s0);

mux8to1 bit7(out[7],nop[7],add[7],Xor[7],And[7],Or[7],sub[7],slt[7],sll[7],s2,s1,s0);

mux8to1 bit8(out[8],nop[8],add[8],Xor[8],And[8],Or[8],sub[8],slt[8],sll[8],s2,s1,s0);

mux8to1 bit9(out[9],nop[9],add[9],Xor[9],And[9],Or[9],sub[9],slt[9],sll[9],s2,s1,s0);

mux8to1 bit10(out[10],nop[10],add[10],Xor[10],And[10],Or[10],sub[10],slt[10],sll[10],s2,s1,s0);

mux8to1 bit11(out[11],nop[11],add[11],Xor[11],And[11],Or[11],sub[11],slt[11],sll[11],s2,s1,s0);

mux8to1 bit12(out[12],nop[12],add[12],Xor[12],And[12],Or[12],sub[12],slt[12],sll[12],s2,s1,s0);

mux8to1 bit13(out[13],nop[13],add[13],Xor[13],And[13],Or[13],sub[13],slt[13],sll[13],s2,s1,s0);

mux8to1 bit14(out[14],nop[14],add[14],Xor[14],And[14],Or[14],sub[14],slt[14],sll[14],s2,s1,s0);

mux8to1 bit15(out[15],nop[15],add[15],Xor[15],And[15],Or[15],sub[15],slt[15],sll[15],s2,s1,s0);

mux8to1 bit16(out[16],nop[16],add[16],Xor[16],And[16],Or[16],sub[16],slt[16],sll[16],s2,s1,s0);

mux8to1 bit17(out[17],nop[17],add[17],Xor[17],And[17],Or[17],sub[17],slt[17],sll[17],s2,s1,s0);

mux8to1 bit18(out[18],nop[18],add[18],Xor[18],And[18],Or[18],sub[18],slt[18],sll[18],s2,s1,s0);

mux8to1 bit19(out[19],nop[19],add[19],Xor[19],And[19],Or[19],sub[19],slt[19],sll[19],s2,s1,s0);

mux8to1 bit20(out[20],nop[20],add[20],Xor[20],And[20],Or[20],sub[20],slt[20],sll[20],s2,s1,s0);

mux8to1 bit21(out[21],nop[21],add[21],Xor[21],And[21],Or[21],sub[21],slt[21],sll[21],s2,s1,s0);

mux8to1 bit22(out[22],nop[22],add[22],Xor[22],And[22],Or[22],sub[22],slt[22],sll[22],s2,s1,s0);

mux8to1 bit23(out[23],nop[23],add[23],Xor[23],And[23],Or[23],sub[23],slt[23],sll[23],s2,s1,s0);

EE471 Lab 03 Report

Group 12

14

mux8to1 bit24(out[24],nop[24],add[24],Xor[24],And[24],Or[24],sub[24],slt[24],sll[24],s2,s1,s0);

mux8to1 bit25(out[25],nop[25],add[25],Xor[25],And[25],Or[25],sub[25],slt[25],sll[25],s2,s1,s0);

mux8to1 bit26(out[26],nop[26],add[26],Xor[26],And[26],Or[26],sub[26],slt[26],sll[26],s2,s1,s0);

mux8to1 bit27(out[27],nop[27],add[27],Xor[27],And[27],Or[27],sub[27],slt[27],sll[27],s2,s1,s0);

mux8to1 bit28(out[28],nop[28],add[28],Xor[28],And[28],Or[28],sub[28],slt[28],sll[28],s2,s1,s0);

mux8to1 bit29(out[29],nop[29],add[29],Xor[29],And[29],Or[29],sub[29],slt[29],sll[29],s2,s1,s0);

mux8to1 bit30(out[30],nop[30],add[30],Xor[30],And[30],Or[30],sub[30],slt[30],sll[30],s2,s1,s0);

mux8to1 bit31(out[31],nop[31],add[31],Xor[31],And[31],Or[31],sub[31],slt[31],sll[31],s2,s1,s0);

endmodule

B. TESTBENCH

module ALUStimulus();

parameter ClockDelay = 10;

reg [31:0] BussA, BussB;

reg [2:0] ALUControl;

reg [1:0] SelectCode;

wire [31:0] Output;

wire Zero, Overflow, Carryout, Negative;

alu myalu(Output,Carryout, Zero, Overflow, Negative, BussA, BussB, ALUControl, SelectCode);

initial

begin

$monitor($time, " Output=%h, Carryout=%b, BussA=%h, BussB=%h,

ALUControl=%b, Zero=%b, Overflow=%b, Negative=%b",

Output, Carryout, BussA, BussB, ALUControl, Zero, Overflow, Negative);

/* No Operation */

ALUControl=000;

BussA=32'h00000DEF; BussB=32'h00000ABC;

#(ClockDelay);

BussA=32'h00001234; BussB=32'h00000105;

#(ClockDelay);

BussA=32'h7FFFFFFF; BussB=32'h00000001;

#(ClockDelay);

BussA='h0;BussB='h0;

/* Addition unit testing */

ALUControl=001;

BussA=32'h00000DEF; BussB=32'h00000ABC; // Should output 000018AB

#(ClockDelay);

BussA=32'h00001234; BussB=32'h00000105; // Should output 00001339

#(ClockDelay);

BussA=32'h7FFFFFFF; BussB=32'h00000001; // Should output 80000000,

overflow, negative

#(ClockDelay);

EE471 Lab 03 Report

Group 12

15

BussA='h0;BussB='h0;

// Should output 0, zero

#(ClockDelay);

BussA='hffffffff;BussB='hffffffff; // Should output 'hfffffffe, negative

#(ClockDelay);

BussA='h1;BussB='hffffffff;

// Should output 0, zero

#(ClockDelay);

BussA='h0;BussB='hffffffff;

// Should output 'hffffffff, negative

#(ClockDelay);

/* Subtraction unit testing */

ALUControl=010;

BussA=32'h00000DEF; BussB=32'h00000ABC; // Should output 00000333

#(ClockDelay);

BussA=32'h00001234; BussB=32'h00000105; // Should output 0000112F

#(ClockDelay);

BussA=32'h80000000; BussB=32'h00000001; // Should output 7FFFFFFF, overflow

#(ClockDelay);

BussA=32'h1; BussB=32'h80000000; // Should output 80000001, overflow

#(ClockDelay);

BussA='h1;BussB='h1;

#(ClockDelay);

BussA='h0;BussB='h0;

#(ClockDelay);

BussA='hffffffff;BussB='hfffffffe;

#(ClockDelay);

BussA='hfffffffe;BussB='hffffffff;

#(ClockDelay);

BussA='hf;BussB='he;

#(ClockDelay);

BussA='he;BussB='hf;

#(ClockDelay);

BussA='h0;BussB='hf;

#(ClockDelay);

BussA='hf;BussB='h0;

#(ClockDelay);

/* and */

ALUControl=011;

#(ClockDelay);

BussA='h0ff0;BussB='hf00f;

#(ClockDelay);

BussA='h0ff0;BussB='hff00;

#(ClockDelay);

BussA='hffffffff;BussB='h0;

/* or */

ALUControl=100;

#(ClockDelay);

BussA='h0ff0;BussB='hf00f;

#(ClockDelay);

EE471 Lab 03 Report

Group 12

16

BussA='h0ff0;BussB='hff00;

#(ClockDelay);

BussA='hffffffff;BussB='h0;

/* xor */

ALUControl=101;

#(ClockDelay);

BussA='h0ff0;BussB='hf00f;

#(ClockDelay);

BussA='h0ff0;BussB='hff00;

#(ClockDelay);

BussA='hffffffff;BussB='h0;

/* slt */

ALUControl=110;

#(ClockDelay);

BussA='h0ff0;BussB='hf00f;

#(ClockDelay);

BussA='h0ff0;BussB='hff00;

#(ClockDelay);

BussA='h0;BussB='h0;

#(ClockDelay);

BussA='hffffffff;BussB='hfffffffe;

#(ClockDelay);

BussA='hf;BussB='he;

#(ClockDelay);

BussA='he;BussB='hf;

#(ClockDelay);

BussA='h0;BussB='hf;

#(ClockDelay);

BussA='hf;BussB='h0;

#(ClockDelay);

/* sll */

ALUControl=111;

SelectCode=00;

#(ClockDelay);

BussA='h0ff0;BussB='hf00f;

#(ClockDelay);

BussA='b01;BussB='b11;

#(ClockDelay);

BussA='h0;BussB='h0;

#(ClockDelay);

BussA='hffffffff;BussB='hfffffffe;

#(ClockDelay);

BussA='hfffffffe;BussB='hffffffff;

#(ClockDelay);

BussA='hf;BussB='he;

#(ClockDelay);

BussA='he;BussB='hf;

#(ClockDelay);

EE471 Lab 03 Report

Group 12

17

BussA='h0;BussB='hf;

#(ClockDelay);

BussA='hf;BussB='h0;

#(ClockDelay);

SelectCode=01;

#(ClockDelay);

BussA='h0ff0;BussB='hf00f;

#(ClockDelay);

BussA='b01;BussB='b11;

#(ClockDelay);

BussA='h0;BussB='h0;

#(ClockDelay);

BussA='hffffffff;BussB='hfffffffe;

#(ClockDelay);

BussA='hfffffffe;BussB='hffffffff;

#(ClockDelay);

BussA='hf;BussB='he;

#(ClockDelay);

BussA='he;BussB='hf;

#(ClockDelay);

BussA='h0;BussB='hf;

#(ClockDelay);

BussA='hf;BussB='h0;

#(ClockDelay);

#(ClockDelay);

end

endmodule

C. SIMULATION ON MODELSIM

1. ALUControl = 000 : NOP

EE471 Lab 03 Report

Group 12

18

2. ALUControl = 001 : ADD

3. ALUControl = 010 : SUB

EE471 Lab 03 Report

Group 12

19

4. ALUControl = 011 : AND

5. ALUControl = 100 : OR

6. ALUControl = 101 : XOR

7. ALUControl = 110 : SLT ( Ouput =1 when A<B, Output=0 when A B )

EE471 Lab 03 Report

Group 12

20

8. ALUControl = 111 : SLL

SelecCode = 00, shift left A

SelecCode = 01, shift left B

D. SIGNALTAP

EE471 Lab 03 Report

Group 12

21

Learning the C Language The Next Steps

Working with C in the PC Environment and Some of the Tools

Part 1 Getting to Know Pointers

Declare several variables of the following types: two variables of type int, two variables of type

float, and two variables of type char.

Declare the following pointer type variables: one pointer to int, one pointer to float, and one

pointer to char.

Assign the address of one of the integer variables to the pointer to int. Print out the value of that

integer. Repeat with the second integer. Repeat with the two floats and then the two chars.

1. C code

#include <stdio.h>

#include <iostream>

int main()

{

int int1, int2;

float float1, float2;

char char1, char2;

int* intptr;

float* floatptr;

char* charptr;

intptr=&int1;

printf("First integer has value of %d\n", *intptr);

intptr=&int2;

printf("Second integer has value of %d\n", *intptr);

floatptr=&float1;

printf("First float has value of %f\n", *floatptr);

floatptr=&float2;

printf("Second float has value of %f\n", *floatptr);

charptr=&char1;

printf("First char has value of %c\n", *charptr);

charptr=&char2;

printf("Second char has value of %c\n", *charptr);

system("pause");

return 0;

}

EE471 Lab 03 Report

Group 12

22

2. Running the program:

Part 2 Working with the pointer:

Declare the following variables of type integer. Initialize each to the values indicated.

A = 25

B = 16

C=7

D=4

E=9

Declare one more variable, result, of type integer. Next, declare and define five variables of type

pointer to integer and let each refer to one of the variables.

Finally, perform the computation: result = ((A B)*(C+D))/E

1. C-code:

#include <stdio.h>

#include <iostream>

int main()

{

int A=25, B=16, C=7, D=4, E=9;

int result;

int* Aptr; int* Bptr; int* Cptr; int* Dptr; int* Eptr;

Aptr=&A; Bptr=&B; Cptr=&C; Dptr=&D; Eptr=&E;

result=((*Aptr-*Bptr)*(*Cptr+*Dptr))/(*Eptr);

EE471 Lab 03 Report

Group 12

23

printf("result = %d\n", result);

system("pause");

return 0;

}

2. Running the program

Вам также может понравиться

- Lpic FLCДокумент19 страницLpic FLCLokesh DewanganОценок пока нет

- Lab 1Документ9 страницLab 1Chinmayi AvasaralaОценок пока нет

- Lab4 Sheet AludesignДокумент7 страницLab4 Sheet AludesignSANJEEV MALLICKОценок пока нет

- LAB 5 - Implementing An ALU: GoalsДокумент9 страницLAB 5 - Implementing An ALU: GoalsBlmjdb AbdelhafidОценок пока нет

- Programming FPGAsДокумент38 страницProgramming FPGAssayuri8910Оценок пока нет

- Eda Unit-1Документ58 страницEda Unit-1Prasanth VarasalaОценок пока нет

- Lab 1Документ5 страницLab 1sean_bostic7193Оценок пока нет

- Lab 8Документ3 страницыLab 8Prasanth PraseОценок пока нет

- Lab 4 Verilog Gate Level ModellingДокумент11 страницLab 4 Verilog Gate Level Modellingsafdarmunir070Оценок пока нет

- Digital System Design: Submitted by Taha SaeedДокумент7 страницDigital System Design: Submitted by Taha SaeedTaha SaeedОценок пока нет

- Chapter 3Документ105 страницChapter 3s9222647Оценок пока нет

- 15EC302J Vlsi Lab StudentsДокумент53 страницы15EC302J Vlsi Lab Studentshahemeb608Оценок пока нет

- 05-Combinational Design 2Документ62 страницы05-Combinational Design 2AmitKumarОценок пока нет

- Lab 6Документ11 страницLab 6vivek2mbОценок пока нет

- 04using Library ModulesДокумент20 страниц04using Library ModulesHaoyuan LiuОценок пока нет

- Verilog ReferenceДокумент77 страницVerilog ReferencePRANJAL SHRIVASTAVAОценок пока нет

- FPGA Design Flow & Experiment 1Документ5 страницFPGA Design Flow & Experiment 1Faid MuzahidОценок пока нет

- Introduction to Microprocessors LabДокумент6 страницIntroduction to Microprocessors LabIlbey EvcilОценок пока нет

- Using Library ModulesДокумент23 страницыUsing Library ModulesJuan Rafael Villen PulidoОценок пока нет

- Asic DesignДокумент18 страницAsic DesignoumeiganОценок пока нет

- 15EC302J Vlsi Lab Students PDFДокумент54 страницы15EC302J Vlsi Lab Students PDFakaash ramnathОценок пока нет

- Verilog HDL BasicsДокумент73 страницыVerilog HDL BasicsSyed AshmadОценок пока нет

- Overview of Verilog HDL Design Session 1Документ10 страницOverview of Verilog HDL Design Session 1Shashwat KanhaiyaОценок пока нет

- 0008 - Programming Part 2Документ6 страниц0008 - Programming Part 2Animesh GhoshОценок пока нет

- Single Precision Floating Point UnitДокумент45 страницSingle Precision Floating Point UnitSumeet SauravОценок пока нет

- Introduction To Verilog Abstraction Levels (Theory) - FPGA & Embedded Systems Lab - Computer Science & Engineering - COE PUNE Virtual LabДокумент4 страницыIntroduction To Verilog Abstraction Levels (Theory) - FPGA & Embedded Systems Lab - Computer Science & Engineering - COE PUNE Virtual Labdeepakk_alpineОценок пока нет

- Department of Electrical Engineering: Ee-421: Digital Sysem DesignДокумент20 страницDepartment of Electrical Engineering: Ee-421: Digital Sysem DesignAhmed AliОценок пока нет

- CSE 308 Homework 4Документ5 страницCSE 308 Homework 4Naveed AhmedОценок пока нет

- FinalSolutions F09Документ8 страницFinalSolutions F09boooreshОценок пока нет

- EE 471 Lab 3 Designing an ALUДокумент8 страницEE 471 Lab 3 Designing an ALUChi Toan Dang TranОценок пока нет

- Lab 5Документ4 страницыLab 5petermurtarghОценок пока нет

- Resolve Infinite Loop Zero Delay GLSДокумент9 страницResolve Infinite Loop Zero Delay GLSJagadish KgОценок пока нет

- Lab1 DSPДокумент15 страницLab1 DSPAli HassanОценок пока нет

- Department of Electrical Engineering: Lab No # 2: Introduction To Verilog (CLO4, P3)Документ9 страницDepartment of Electrical Engineering: Lab No # 2: Introduction To Verilog (CLO4, P3)Muhammad RehanОценок пока нет

- Componentes Combinacionales en VHDLДокумент9 страницComponentes Combinacionales en VHDLseb wood21Оценок пока нет

- Implementing a 32-bit ALU in VerilogДокумент9 страницImplementing a 32-bit ALU in VerilogJoey WangОценок пока нет

- Verilog Lab Manual Intro to VerilogДокумент50 страницVerilog Lab Manual Intro to VerilogDavid Solomon Raju YellampalliОценок пока нет

- Hardware Description Languages: VerilogДокумент26 страницHardware Description Languages: VerilogSrikanth ReddyОценок пока нет

- ECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitДокумент8 страницECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitsantoshmphilОценок пока нет

- DVCon Europe 2015 TA5 1 PaperДокумент7 страницDVCon Europe 2015 TA5 1 PaperJon DCОценок пока нет

- DSD RTL Coding Lec8Документ31 страницаDSD RTL Coding Lec8Arshad RasheedОценок пока нет

- Configuring 555 timer, MUX, DEMUX digital circuitДокумент5 страницConfiguring 555 timer, MUX, DEMUX digital circuitErfan RazaliОценок пока нет

- HDL Design LecДокумент10 страницHDL Design Lecsugunakar711Оценок пока нет

- Assembly Language and Computer Organization ExplainedДокумент68 страницAssembly Language and Computer Organization ExplainedNicolas AmezquitaОценок пока нет

- Single Precision Floating Point UnitДокумент46 страницSingle Precision Floating Point UnitSumeet SauravОценок пока нет

- Lab 07Документ10 страницLab 07api-241454978Оценок пока нет

- Lab Manual: Submmitted byДокумент70 страницLab Manual: Submmitted byMuhammad owais Muhammad munirОценок пока нет

- Lab Report FpgaДокумент34 страницыLab Report FpgaMuhammad Furqan JavedОценок пока нет

- Verilog Introduction: SynopsisДокумент7 страницVerilog Introduction: SynopsisMeghana VeggalamОценок пока нет

- 271/469 Verilog Tutorial: and - or Andout A and - or Andout AДокумент17 страниц271/469 Verilog Tutorial: and - or Andout A and - or Andout AkhoaОценок пока нет

- Verilog TutДокумент21 страницаVerilog TutNishana KumarОценок пока нет

- Exercises Lg1 Lg6Документ4 страницыExercises Lg1 Lg6Helga PravinОценок пока нет

- BaitapVerilog LabДокумент6 страницBaitapVerilog LabHoàng Quốc HuyОценок пока нет

- Combinational Logic Design With VerilogДокумент13 страницCombinational Logic Design With VerilogWong JulianОценок пока нет

- Report On Special Assignment "Implementation of 8-Bit ALU On SPARTAN-3"Документ18 страницReport On Special Assignment "Implementation of 8-Bit ALU On SPARTAN-3"Dhruv Joshi100% (6)

- VHDL CodesДокумент53 страницыVHDL CodesANOOP MISHRAОценок пока нет

- Week 1-2 Introduction To Hardware Description LanguageДокумент23 страницыWeek 1-2 Introduction To Hardware Description LanguageReuel Patrick CornagoОценок пока нет

- ECE-II SHRESHT GUPTA EXPERIMENT 8 ALU SHIFT REGISTER VHDLДокумент9 страницECE-II SHRESHT GUPTA EXPERIMENT 8 ALU SHIFT REGISTER VHDLLakshay SharmaОценок пока нет

- Projects With Microcontrollers And PICCОт EverandProjects With Microcontrollers And PICCРейтинг: 5 из 5 звезд5/5 (1)

- CS202 Lab2submission LeTrungHieu 10ESДокумент27 страницCS202 Lab2submission LeTrungHieu 10ESLe HieuОценок пока нет

- LeTrungHieu 10ES ECE351 Lab1reportДокумент13 страницLeTrungHieu 10ES ECE351 Lab1reportLe HieuОценок пока нет

- CS202 Lab1 LeTrungHieu 10ESДокумент11 страницCS202 Lab1 LeTrungHieu 10ESLe HieuОценок пока нет

- TOEFL Speaking Sample 2 - Independent Task Planning & ResponsesДокумент7 страницTOEFL Speaking Sample 2 - Independent Task Planning & ResponsesLe HieuОценок пока нет

- Speaking NotesДокумент10 страницSpeaking NotespolmkiОценок пока нет

- CS202 Lab1 LeTrungHieu 10ESДокумент11 страницCS202 Lab1 LeTrungHieu 10ESLe HieuОценок пока нет

- ECE371 Lab1Report Group2Документ9 страницECE371 Lab1Report Group2Le HieuОценок пока нет

- Ee332 HW1 VN 2013Документ4 страницыEe332 HW1 VN 2013Le HieuОценок пока нет

- STAT451 HW1.2 Group1Документ12 страницSTAT451 HW1.2 Group1Le HieuОценок пока нет

- Verilog Tutorial: 1-Bit Full AdderДокумент8 страницVerilog Tutorial: 1-Bit Full AdderLe HieuОценок пока нет

- Student Shop Exercise ECE 271 Name: Lê Trung Hiếu Class: 10ES Instructor: Mr Nguyen The NghiaДокумент9 страницStudent Shop Exercise ECE 271 Name: Lê Trung Hiếu Class: 10ES Instructor: Mr Nguyen The NghiaLe HieuОценок пока нет

- BPO UNIT - 5 Types of Securities Mode of Creating Charge Bank Guarantees Basel NormsДокумент61 страницаBPO UNIT - 5 Types of Securities Mode of Creating Charge Bank Guarantees Basel NormsDishank JohriОценок пока нет

- Biomotor Development For Speed-Power Athletes: Mike Young, PHD Whitecaps FC - Vancouver, BC Athletic Lab - Cary, NCДокумент125 страницBiomotor Development For Speed-Power Athletes: Mike Young, PHD Whitecaps FC - Vancouver, BC Athletic Lab - Cary, NCAlpesh Jadhav100% (1)

- Abinisio GDE HelpДокумент221 страницаAbinisio GDE HelpvenkatesanmuraliОценок пока нет

- Transformer Oil Testing MethodsДокумент10 страницTransformer Oil Testing MethodsDEE TOTLVJAОценок пока нет

- 2019-10 Best Practices For Ovirt Backup and Recovery PDFДокумент33 страницы2019-10 Best Practices For Ovirt Backup and Recovery PDFAntonius SonyОценок пока нет

- Antiquity: Middle AgesДокумент6 страницAntiquity: Middle AgesPABLO DIAZОценок пока нет

- Environmental Assessment of Sewer ConstructionДокумент32 страницыEnvironmental Assessment of Sewer ConstructionKaleab TadesseОценок пока нет

- CGSC Sales Method - Official Sales ScriptДокумент12 страницCGSC Sales Method - Official Sales ScriptAlan FerreiraОценок пока нет

- Creatures Since Possible Tanks Regarding Dengue Transmission A Planned Out ReviewjnspeДокумент1 страницаCreatures Since Possible Tanks Regarding Dengue Transmission A Planned Out Reviewjnspeclientsunday82Оценок пока нет

- Quiz-Travel - Beginner (A1)Документ4 страницыQuiz-Travel - Beginner (A1)Carlos Alberto Rodriguez LazoОценок пока нет

- Neuropathology of Epilepsy: Epilepsy-Related Deaths and SUDEPДокумент11 страницNeuropathology of Epilepsy: Epilepsy-Related Deaths and SUDEPTeuku AvicennaОценок пока нет

- Key ssl101 Academic Skills For University Success ssl101cДокумент196 страницKey ssl101 Academic Skills For University Success ssl101cHùng NguyễnОценок пока нет

- NameДокумент5 страницNameMaine DagoyОценок пока нет

- Distinguish Between Tax and FeeДокумент2 страницыDistinguish Between Tax and FeeRishi Agarwal100% (1)

- Emerson Park Master Plan 2015 DraftДокумент93 страницыEmerson Park Master Plan 2015 DraftRyan DeffenbaughОценок пока нет

- Ijimekko To Nakimushi-Kun (The Bully and The Crybaby) MangaДокумент1 страницаIjimekko To Nakimushi-Kun (The Bully and The Crybaby) MangaNguyễn Thị Mai Khanh - MĐC - 11A22Оценок пока нет

- JD - Software Developer - Thesqua - Re GroupДокумент2 страницыJD - Software Developer - Thesqua - Re GroupPrateek GahlanОценок пока нет

- The Changing Face of War - Into The Fourth GenerationДокумент5 страницThe Changing Face of War - Into The Fourth GenerationLuis Enrique Toledo MuñozОценок пока нет

- Guidelines Tax Related DeclarationsДокумент16 страницGuidelines Tax Related DeclarationsRaghul MuthuОценок пока нет

- Microsoft Word 2000 IntroductionДокумент72 страницыMicrosoft Word 2000 IntroductionYsmech SalazarОценок пока нет

- THE PEOPLE OF FARSCAPEДокумент29 страницTHE PEOPLE OF FARSCAPEedemaitreОценок пока нет

- WassiДокумент12 страницWassiwaseem0808Оценок пока нет

- Introduction To OpmДокумент30 страницIntroduction To OpmNaeem Ul HassanОценок пока нет

- Amul ReportДокумент48 страницAmul ReportUjwal JaiswalОценок пока нет

- Conceptual FrameworkДокумент24 страницыConceptual Frameworkmarons inigoОценок пока нет

- Oblicon SampleДокумент1 страницаOblicon SamplelazylawatudentОценок пока нет

- Put The Items From Exercise 1 in The Correct ColumnДокумент8 страницPut The Items From Exercise 1 in The Correct ColumnDylan Alejandro Guzman Gomez100% (1)

- PREMIUM BINS, CARDS & STUFFДокумент4 страницыPREMIUM BINS, CARDS & STUFFSubodh Ghule100% (1)

- Control SystemsДокумент269 страницControl SystemsAntonis SiderisОценок пока нет

- Budget ControlДокумент7 страницBudget ControlArnel CopinaОценок пока нет