Академический Документы

Профессиональный Документы

Культура Документы

Low-Complexity Reliability-Based Message-Passing Decoder Architectures For Non-Binary LDPC Codes

Загружено:

Nsrc Nano ScientifcОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Low-Complexity Reliability-Based Message-Passing Decoder Architectures For Non-Binary LDPC Codes

Загружено:

Nsrc Nano ScientifcАвторское право:

Доступные форматы

Low-Complexity Reliability-Based Message-Passing Decoder Architectures for on-Binary LDPC Codes

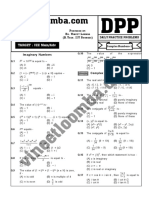

A!M" The main aim of the project is to design #Low-Complexity ReliabilityBased Message-Passing Decoder Architectures for on-Binary LDPC Codes$% AB&'RAC'" Non-binary low-density parity-check (NB-LDPC codes can achie!e better error-correcting performance than their binary co"nterparts at the cost of higher decoding comple#ity when the codeword length is moderate$ The recently de!eloped iterati!e reliability-based majority-logic NB-LDPC decoding has better performance-comple#ity tradeoffs than pre!io"s algorithms$ This paper first proposes enhancement schemes to the iterati!e hard reliability-based majoritylogic decoding (%&'B-(L)D $ Compared to the %&'B algorithm* o"r enhanced (+- %&'B algorithm can achie!e significant coding gain with small hardware o!erhead$ Then low-comple#ity partial-parallel NB-LDPC decoder architect"res are de!eloped based on these two algorithms$ (any e#isting NB-LDPC code constr"ction methods lead to ,"asi-cyclic or cyclic codes$ Both types of codes are considered in o"r design$ (oreo!er* no!el schemes are de!eloped to keep a small proportion of messages in order to red"ce the memory re,"irement witho"t ca"sing noticeable performance loss$ %n addition* a shift-message str"ct"re is proposed by "sing memories concatenated with !ariable node "nits to enable efficient partialparallel decoding for cyclic NB-LDPC codes$ Compared to pre!io"s designs based

K.Aravind Reddy (Director) 9652926926, 9640648

Cell No:

on the (in-ma# decoding algorithm* o"r proposed decoders ha!e at least tens of times lower comple#ity with moderate coding gain loss$ BL(C) D!A*RAM"

-ig. /N0 architect"re when

messages are kept$

'((L&" 1ilin# %2+ 3$4 % and (odel2im 5$6c$

APPL!CA'!( AD+A 'A*,&" 7ith moderate performance loss* the proposed decoders can achie!e at least tens of times higher efficiency compared to pre!io"s designs based on the (in-ma# algorithm$

K.Aravind Reddy (Director) 9652926926, 9640648

Cell No:

-"t"re work will be de!oted to f"rther impro!ing the performance and red"cing the hardware comple#ity of (L)D-based algorithms for NBLDPC decoding$

R,-,R, C,&" L$ Barna"lt and D$ Declerc,* 8-ast decoding algorithm for LDPC o!er *9 in Proc$ %nf$ Theory 7orkshop* 4::;* pp$ <:=<;$ &$ 7ymeersch* &$ 2teendam* and ($ (oeneclaey* 8Log-domain decoding of LDPC codes o!er *9 in Proc$%+++%nt$Conf$ Comm"n$* 4::6* pp$ <<4=<<5$ C$2pagnol*+$Popo!ici*and7$(arnane*8&ardwareimplementation of LDPC decoders*9%+++Trans$Circ"its2yst$%*'eg$Papers* !ol$ >5* no$ ?4* pp$ 45:3= 454:$ D$ Declerc, and ($ -ossorier* 8Decoding algorithms for nonbinary LDPC codes o!er *9 %+++ Trans$ Comm"n$* !ol$ >>* no$ 6* pp$ 5;;=56;* @pr$ 4::<$ /$2a!in*8(in-(a#decodingfornonbinaryLDPCcodes*9inProc$ 2ymp$ %nf$ Theory* 4::A* pp$ 35:=356$ %+++ %nt$

K.Aravind Reddy (Director) 9652926926, 9640648

Cell No:

Вам также может понравиться

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- HW3 Sol PDFДокумент44 страницыHW3 Sol PDFbsudheertecОценок пока нет

- Errata 2008 PDFДокумент2 страницыErrata 2008 PDFAtul KumbharОценок пока нет

- Graph TheoryДокумент2 страницыGraph Theoryrws1000Оценок пока нет

- Cbse Class 2Документ8 страницCbse Class 2Amitoj SinghОценок пока нет

- Graph ProblemsДокумент6 страницGraph ProblemsHasan Farooq0% (1)

- 2 Iteration Bound PDFДокумент19 страниц2 Iteration Bound PDF蕭名群Оценок пока нет

- M and HCFДокумент12 страницM and HCFPrem KumarОценок пока нет

- MATHEMATICS IN THE MODERN WORLD Activity 1Документ4 страницыMATHEMATICS IN THE MODERN WORLD Activity 1Ana Marie ValenzuelaОценок пока нет

- Disjoint SsetsДокумент37 страницDisjoint SsetsdpkmdsОценок пока нет

- Basic Calculus Quiz1Документ3 страницыBasic Calculus Quiz1IchigoОценок пока нет

- Data Structures Lab ManualДокумент30 страницData Structures Lab ManualSuman ChinivarОценок пока нет

- Speed - Time Graphs P.2 Questions For 0580 Mathematics IgcseДокумент37 страницSpeed - Time Graphs P.2 Questions For 0580 Mathematics Igcseabdulkarimalgamal2008Оценок пока нет

- Library GenesisДокумент8 страницLibrary GenesisAjay kumarОценок пока нет

- Notes StanfordДокумент232 страницыNotes Stanfordjinyup1000100% (1)

- University of Science & Technology of Southern Philippines: Oroquieta CampusДокумент7 страницUniversity of Science & Technology of Southern Philippines: Oroquieta CampusJohn CedrickОценок пока нет

- 2001CCCStage1Results PDFДокумент7 страниц2001CCCStage1Results PDFสฮาบูดีน สาและОценок пока нет

- Edulabz: InternationalДокумент6 страницEdulabz: InternationalrajikrajanОценок пока нет

- VL2023240500682 DaДокумент3 страницыVL2023240500682 Dakx.graphyОценок пока нет

- Hecke's Theory of Modular Forms and Dirichlet SeriesДокумент150 страницHecke's Theory of Modular Forms and Dirichlet SeriesluisufspaiandreОценок пока нет

- The Disjoint Set Class SДокумент21 страницаThe Disjoint Set Class SPrabha KrishnanОценок пока нет

- Pset 2 MMWДокумент12 страницPset 2 MMWMark UlitОценок пока нет

- How To Convert Octal To Binary Step by StepДокумент1 страницаHow To Convert Octal To Binary Step by StepSyahmiSyaNizarОценок пока нет

- UWATERLOO CS341 Midterm Solution 2011Документ3 страницыUWATERLOO CS341 Midterm Solution 2011zengxiliangОценок пока нет

- Complex Numbers-1 JEE Main and Advanced PDFДокумент6 страницComplex Numbers-1 JEE Main and Advanced PDFSrinivasaОценок пока нет

- LS - 0 - 2 - 1 - 023e7404312ef-Trigonometry Bhagwati Maths 51 To 134Документ6 страницLS - 0 - 2 - 1 - 023e7404312ef-Trigonometry Bhagwati Maths 51 To 134Nitin DangiОценок пока нет

- Design and Analysis of Algorithm PracticalsДокумент93 страницыDesign and Analysis of Algorithm PracticalsprogrammerОценок пока нет

- Aneesh Shetty 1pageДокумент1 страницаAneesh Shetty 1pageSEELAM ALEXANDERОценок пока нет

- Sets - Venn Diagram ApplicationsДокумент7 страницSets - Venn Diagram ApplicationsRaghavan RaghuОценок пока нет

- Utc501 PDFДокумент2 страницыUtc501 PDFAli HusseiniОценок пока нет

- DAA FinalДокумент43 страницыDAA FinalSunny VarshneyОценок пока нет