Академический Документы

Профессиональный Документы

Культура Документы

22vol2no3 PDF

Загружено:

Chen CYОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

22vol2no3 PDF

Загружено:

Chen CYАвторское право:

Доступные форматы

IRACST Engineering Science and Technology: An International Journal (ESTIJ), ISSN: 2250-3498, Vol.2, No.

3, June 2012

A 16-BIT RISC PROCESSOR FOR COMPUTER HARDWARE INTRODUCTION

Anuruddh Sharma#1

Electronics & Communication dept. Acropolis Institute of Research & Tecnology Indore,India

Mukti Awad#2

Electronics & Communication dept. Acropolis Institute of Research & Tecnoogy Indore ,India

Abstract- Processors are the heart of all smart devices, whether they be electronic devices or otherwise. Their smartness comes as a direct result of the decisions and controls that processor makes .The existing commercial microprocessors are provided as black box units; with which users are unable to monitor internal signals and operation process, neither can they modify the original structure. In order to solve this problem 16-bit fully functional single cycle processor is designed in terms of its architecture and its functional capabilities. The procedure of design and verification for a 16-bit processor is introduced in this paper. The key architecture elements are being described, as well as the hardware block diagram and internal structure. The summary of instruction set is presented. This processor is modify as a VERILOG Hardware Description Language (VERILOGHDL) and gives access to every internal signal. In order to consume fewer resources, the design of arithmetic logical unit (ALU) is optimized. The RTL views and verified simulation results of processor are shown in this paper. The synthesis report of the design is also described. The design architecture is written in VERILOG Hardware Description Language (VERILOGHDL) code using Xilinx ISE tool for synthesis and simulation. Keywords: Arithmetic logical unit (ALU); control unit (CU); comparator; shifter; rotation; instruction se; VERILOGHDL; Xilinx.

processor. Therefore its architecture is well structured and simple enough so that it can be built by first grade students, without any design experience. These all requirements can be obtained by the FPGA based processor with Hardware Description Language VERILOGHDL. Figure 1 shows the basic steps to design the processor. The remaining paper is organized as follows. The next section of the paper describes the internal architecture of 16-bit fully functional single cycle processor, System operation and interaction between different units, ALU and Instructions. Section III introduces functional simulation results. Section IV describes logic synthesis.

I.

INTRODUCTION

Fig.1. Design Flow Steps Methodology

Processors are divided into 3 categories: 8-bit, 16-bit and 32bit processor, depending upon the demand of performance, cost, power and programmability. 8-bit processors have extreme low cost and consume less power for simple control system. In contrast to 8-bit, 32-bit processors have high programmability, high performance and are widely used in cellular phone and PDA that need high computation but it has high power consumption. On the other hand 16-bit processors have high performance and power than 8-bit processor and low power consumption than 32-bit processor. They are often used in 16-bit applications such as disk driver controller, cellular communication and airbags. The 16-bit fully functional single cycle processor is applicable for real tasks and also used for assembly language programming. We need to participate in the process of processor design and to understand the inner structure of

II.

GENERAL ARCHITECTURE OF TEACHING PROCESSOR

A processor incorporates most or all of the functions of a computers Central Processing Unit (CPU) on a single IC or microchip. In order to accomplish these several innovative and unconventional design tradeoffs have been made, without compromising the goals. The general architecture of 16-bit teaching processor is shown in figure 2. It contains number of basic pieces. There is a register array of 8-bit and 16-bit, a 16bit ALU, a 16-bit shifter, a program counter, an instruction register, a 16-bit comparator, an address register and control unit. All of these units communicate through a common 16-bit tri-state data bus.

505

IRACST Engineering Science and Technology: An International Journal (ESTIJ), ISSN: 2250-3498, Vol.2, No. 3, June 2012

A. System operations and interaction between different units The block diagram of the ALU is shown in Figure 3. It consumes only one adder unit and can co-operate with the multiplexer to realize different calculations. Table 1 shows consumed resources of the two methods.

The top level design consists of the processor block and a memory block communicating through a bi-directional data bus, an address bus, and few control lines. The processor fetches instructions from external memory and executes these instructions to run a program. These instructions are stored in instruction register and decoded by control unit. The control unit causes the appropriate signal interaction for processor unit to execute the instruction. If the instruction is an add of two registers, the control unit would cause the first register value to be written in operational register (OpReg) for temporary storage. The second register value would then be placed on data bus. The ALU is now set at add mode and result will be stored in output register (OutReg). Output register stores the resulting value until it is copied to the final destination. When executing an instruction, number of steps takes place. Program counter holds the address in memory of the current instruction. After an instruction has finished execution, the program counter is advanced to where the next instruction is located. If the processor is executing a linear stream of instructions, this is the next instruction. If a branch is taken, the program counter is loaded with next instruction location directly. The processor values the address register, which gives output as new address on the address bus. At the same time, control unit sets the R/W (read write signals) to 0 for read operation and sets signal VMA (Valid Memory Address) to 1, signaling the memory that the address is now valid. Memory decodes the address and places the memory data on data bus. When data has been placed on data bus, memory set the READY signal to 1 indicating that the memory data is ready for consumption. Control unit causes the memory data to be written into the instruction register. The control unit is now access and decodes the instruction. The decoded instruction executes, and process starts over again.

Fig.3 ALU Block Diagram

Table 1. Consumed Resources Report

Behavior Description Number Slices Number of input LUTs of 4 54 80

Structural Description 49 77

An alternative way adopted, structural description is to split the ALU into two modules, Logic module and Arithmetic module. During a component design experiment, to facilitate the manual operation, the parameter is set as 4 bits; otherwise, for a principal machine design, only the parameter needs to be changed to 16 bits to become a 16-bit ALU. The advanced ALU has basic arithmetic and logical operations including addition (+), subtraction (-), multiplication (*), negation (^), and in addition of some other operations such as bit shifts (<<,>>), bitwise logic operations (&,/,^,~), and logical operations (&&,!,). C. Instructions

Fig.2. Internal architecture of 16-bit processor

Instructions can be divided into five major categories: CPU Control instructions like NOP, STOP or SET does not generate numeric result but alter the processors state. The SET and CLR instructions allow setting and clearing of any status or control flag. Data Transfer instructions like MOV, LOAD or PUSH copy the content of an internal register to another register, a memory location, or load the data from these sources to register file. Branch and Subroutine -- instructions like JMP, CALL or RET alter the value of program counter and access the call stack. Arithmetic and Logic -- instructions like ADD, NEG or XOR generate numeric result as a function of two

B.

Arithmetic logical unit (ALU)

The arithmetic operations are comprised of addition, addition with carry, subtraction, subtraction with borrows. Most of the time behavioral method of hardware description is employed using the following expressions: A+B, A+B+C, A-B, A-B-C The behavioral capabilities of HDL can be more powerful and more convenient for some designs. However, in this case the behavioral description will likely imply more adder unit usage in order to realize these functions.

506

IRACST Engineering Science and Technology: An International Journal (ESTIJ), ISSN: 2250-3498, Vol.2, No. 3, June 2012

source operands, in unsigned integer depending of the state of SF flag. Multiplication and Division -- these instructions generate two results during execution. The multiplication will output a 32-bit result and the division will output a quotient and a remainder.

Table2. INSTRUCTION SET

SUBI Immediate subtraction AND Logic AND OR Logic OR NOT Logic NOT SHL Shift left SHR Shift right

SUBI Rd, k

Rd

Rd k

AND Rd, Rs OR Rd, Rs NOT Rd

Rd Rd Rd

Rd Rs Rd or Rs NOT (Rd)

Fig.4. Instruction format per instruction type

register SHL Rd

register SHR Rd

Rd(n+1) Rd(n), Rd(0) 0 Rd(n) Rd(n+1), Rd(7) 0 PC PC+k PC Rd

D. Simulation Results Functional simulation is the way to verify a design. In our design we verify the components of processor by the functional simulation and obtained the simulated data which confirms the work ability of our design. Here we also found that functional simulation is also verified for the whole processor.

JMP Immediate jump JMR Jump to register JMR Rd BRC Branch if carry BRC k

if (C = 1) then PC PC + k

BRZ Branch if zero BRZ k BRH Branch if half- BRH k carry LDI Load LDI Rd, k immediate LDD Direct load LDD Rd,[A] from memory LDX Indirect load LDX Rd,[Rs] from memory STD Direct storage memory STX Indirect storage LDP Load program counter STD [A],Rd to STX [Rd],Rs to from LDP Rd

if (C = 1) then PC PC + k if (C = 1) then PC Rd Rd Rd [A] PC + k k [A] [Rs] Rs

Fig.5. Simulation Result of ALU

[Rd] Rs Rd PC

Rd: Destination register, Rs: Source register k: Constant, PC: Program counter A: Address

Fig.6. Simulation Result of Shifter

507

IRACST Engineering Science and Technology: An International Journal (ESTIJ), ISSN: 2250-3498, Vol.2, No. 3, June 2012

Fig.7. Simulation Result of Comparator

Fig.11. Simulation Result of Control Unit

Fig.12. Simulation Result of CPU Fig.8. Simulation Result of Biregister

E. Logic Synthesis The RTL description of a design is taken through logic synthesis in an EDA tool, which generates a gate-level description (net list) automatically. It converts the VERILOGHDL code into gate level architecture.

Fig.9. Simulation Result of Triregister

Fig.13. RTL View of ALU

Fig.14. RTL View of Shifter

Fig.10. Simulation Result of RAM

Fig.15. RTL View of Comparator

508

IRACST Engineering Science and Technology: An International Journal (ESTIJ), ISSN: 2250-3498, Vol.2, No. 3, June 2012

executes for all the various instructions. We verified all the result and found them too correctly. IV. APPLICATION DOMAIN

Fig.16. RTL View of RAM

The program used to evaluate the performance of the CPU must make use of all type of instructions to manipulate the stack, execute subroutines and access RAM. With a view to meet the requirements above, a program that calculates Fibonacci series elements can be used. V. FUTURE WORK

In order to obtain a more sophisticated architecture we can add some advanced techniques like pipelining, interrupt handler and input/output controllers obtaining a competitive general purpose 16 bit RISC processor. REFERENCES

[1] Andrei-Sorin F., Corneliu B., 2010 Savage 16-16 bit RISC Architecture General Purpose Microprocessor in Proc. IEEE Journal. (Pp.3-8) [2] Venelin Angelov, Volker L., 2009 The Educational Processor Sweet16 in Proc. IEEE Conference. (Pp.555-559) [3] Xiao Tiejun, Liu Fang, 2008 16-bit Teaching Microprocessor Design and Application in Proc. IEEE International Symposium on It in Medicine and Education. (Pp.160-163) [4] J. O. Hamblen and M. D. Furman, Rapid Prototyping of Digital Systems. Springer, 2001. [5] Cross, J.E. and Soetan, R. A., 1988 Teaching Microprocessor Design using the 8086 Microprocessor in Proc. IEEE Conference on Southeastcon88. (Pp. 175-180) [6] D. L. Perry, VHDL, 3rd ed. McGraw-Hill, 1988. [7] J. Reichardt and B. Schwarz, VHDL-Synthesis. Oldenburg, 2001. [8] Bannatyne, R, 1998 Migrating from 8 to 16-bit Processors [9] P. Verplaetse, J. Campenhout, ESCAPE: Environment for the Simulation of Computer Architecture for the Purpose of Education, IEEE TCCA Newsletter, February, pp. 57-59, 1999. [10] M. Jaumain, M. Osee, A. Richard, A. Vander Biest, P. Mathys, Educational simulation of the RiSC processor, ICEE International Conference on Engineering Education, 2007.

Fig.17. RTL View of Control Unit

Fig.18. RTL View of CPU

If we push the top-level design we can find the internal structure like this.

Fig.19. Internal Structure of the CPU

III.

CONCLUSION

The 16-bit fully functional single cycle processor was described using VERILOGHDL. The design of ALU was optimized so that it consumes fewer resources. Compared with the existing commercial micro-processors, it has advantage because it is an open core which benefits with an in-depth understanding of the microprocessors interior structure. Functional simulation shows that the processor

509

Вам также может понравиться

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Lecture 4 Symmetrical ComponentsДокумент15 страницLecture 4 Symmetrical ComponentsJomel CristobalОценок пока нет

- Instrument Calibration ExplanationДокумент10 страницInstrument Calibration ExplanationCris RonaldОценок пока нет

- Case 1 2 Nestle The Infant Formula ControversyДокумент4 страницыCase 1 2 Nestle The Infant Formula ControversyboulevardkhoaОценок пока нет

- ScalarbeamerДокумент12 страницScalarbeamerAnoop Shamdasani100% (1)

- Siemens MRI MAGNETOM-World MR-Basics MRI-brochure English 1800000001924325Документ46 страницSiemens MRI MAGNETOM-World MR-Basics MRI-brochure English 1800000001924325Paulo HenriqueОценок пока нет

- Devices and Communication Buses For Devices NetworkДокумент211 страницDevices and Communication Buses For Devices NetworkDhrumeet PatelОценок пока нет

- Huawei Active Antennas Design Guideline v05 VF-ESДокумент35 страницHuawei Active Antennas Design Guideline v05 VF-ESestebanarca100% (2)

- PRECOMMISSIONING and COMMISSIONING METHOD STATEMENT PROCEDURE FOR CCTV SYSTEMДокумент2 страницыPRECOMMISSIONING and COMMISSIONING METHOD STATEMENT PROCEDURE FOR CCTV SYSTEMHumaid ShaikhОценок пока нет

- SIMATIC PROFINET System Description PDFДокумент182 страницыSIMATIC PROFINET System Description PDFChen CYОценок пока нет

- SIMATIC Logon PDFДокумент74 страницыSIMATIC Logon PDFChen CYОценок пока нет

- PCS 7 Readme V8.1Документ64 страницыPCS 7 Readme V8.1Chen CY100% (1)

- 1 2 3 4 5 6 Windows Logic Controller Winlc RTX Simatic: User ManualДокумент154 страницы1 2 3 4 5 6 Windows Logic Controller Winlc RTX Simatic: User ManualDavid MartinОценок пока нет

- Procedure of Archive Program For Pcs7 Rev AДокумент9 страницProcedure of Archive Program For Pcs7 Rev AChen CYОценок пока нет

- cpc030 Datasheet PDFДокумент4 страницыcpc030 Datasheet PDFChen CYОценок пока нет

- PN Test Readme V10 Feb15Документ7 страницPN Test Readme V10 Feb15Chen CYОценок пока нет

- Lecture 2Документ63 страницыLecture 2Chen CYОценок пока нет

- מדריך modelsim למתחיליםДокумент22 страницыמדריך modelsim למתחיליםRonОценок пока нет

- Revolutionizing The Grease-Making Process: Voices & ViewsДокумент2 страницыRevolutionizing The Grease-Making Process: Voices & ViewsChen CYОценок пока нет

- Lecture 1Документ31 страницаLecture 1Chen CYОценок пока нет

- 7Документ1 страница7Chen CYОценок пока нет

- A New 16-Bit RISC Processor Architecture - Controller State Machines and Functional Verification Using VHDL PDFДокумент12 страницA New 16-Bit RISC Processor Architecture - Controller State Machines and Functional Verification Using VHDL PDFChen CYОценок пока нет

- LCD Driver Solution PDFДокумент0 страницLCD Driver Solution PDFChen CYОценок пока нет

- Sap ComputerДокумент6 страницSap ComputerAyaz AhmadОценок пока нет

- HDL-Based Design Methodology of 16-Bit RISC Microprocessor PDFДокумент6 страницHDL-Based Design Methodology of 16-Bit RISC Microprocessor PDFChen CYОценок пока нет

- 18fxx2 PDFДокумент316 страниц18fxx2 PDFChen CYОценок пока нет

- HDL-Based Design Methodology of 16-Bit RISC Microprocessor PDFДокумент6 страницHDL-Based Design Methodology of 16-Bit RISC Microprocessor PDFChen CYОценок пока нет

- Esquema Arduino UNO R3Документ1 страницаEsquema Arduino UNO R3stangne1Оценок пока нет

- 16f81x PDFДокумент0 страниц16f81x PDFChen CYОценок пока нет

- 18f8x80 PDFДокумент4 страницы18f8x80 PDFChen CYОценок пока нет

- 16f872 PDFДокумент0 страниц16f872 PDFChen CYОценок пока нет

- 16ce62x PDFДокумент0 страниц16ce62x PDFChen CYОценок пока нет

- 12c5xx PDFДокумент0 страниц12c5xx PDFChen CYОценок пока нет

- 16c55x PDFДокумент97 страниц16c55x PDFChen CYОценок пока нет

- 16lc74b 16 PDFДокумент0 страниц16lc74b 16 PDFChen CYОценок пока нет

- PIC16C6X: 8-Bit CMOS MicrocontrollersДокумент0 страницPIC16C6X: 8-Bit CMOS MicrocontrollersChen CYОценок пока нет

- Cancel Fals Distr AlertДокумент1 страницаCancel Fals Distr AlertIGORОценок пока нет

- Broadband Networks Prof. Dr. Abhay Karandikar Electrical Engineering Department Indian Institute of Technology, Bombay Lecture - 29 Voice Over IPДокумент22 страницыBroadband Networks Prof. Dr. Abhay Karandikar Electrical Engineering Department Indian Institute of Technology, Bombay Lecture - 29 Voice Over IPKrishna GhimireОценок пока нет

- Physics Investigatory ProjectДокумент15 страницPhysics Investigatory Projecttdycfgjdyjf82% (11)

- Lesson 1-17: Identifying Ports: IC Training - Module One: Computing FundamentalsДокумент2 страницыLesson 1-17: Identifying Ports: IC Training - Module One: Computing FundamentalsVinMarОценок пока нет

- HK T Renec8v01xДокумент14 страницHK T Renec8v01xApoli ApatoroОценок пока нет

- Notes Switchgear and Protection Unit 2Документ32 страницыNotes Switchgear and Protection Unit 2Pratik SinghОценок пока нет

- How To Check CPU VoltageДокумент4 страницыHow To Check CPU VoltageHamdan AhmadОценок пока нет

- Millman's Theorem: Chapter 10 - DC Network AnalysisДокумент17 страницMillman's Theorem: Chapter 10 - DC Network AnalysisAce Dela CruzОценок пока нет

- Chapter 4 - Synchronous GeneratorsДокумент21 страницаChapter 4 - Synchronous GeneratorsnehmeОценок пока нет

- Xitanium 20W LH 0.15-0.5A 48V 230VДокумент7 страницXitanium 20W LH 0.15-0.5A 48V 230VJane DoeОценок пока нет

- Electrical Principles Peter Phillips Full ChapterДокумент51 страницаElectrical Principles Peter Phillips Full Chaptertami.cobb436100% (5)

- Plasma Antenna: A Seminar Presentation ONДокумент16 страницPlasma Antenna: A Seminar Presentation ONbalu54Оценок пока нет

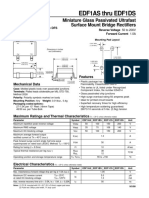

- EDF1AS Thru EDF1DS: Miniature Glass Passivated Ultrafast Surface Mount Bridge RectifiersДокумент2 страницыEDF1AS Thru EDF1DS: Miniature Glass Passivated Ultrafast Surface Mount Bridge RectifiersCarlosОценок пока нет

- Scientech 2801Документ89 страницScientech 2801Santiago Alberto Ramirez MarinОценок пока нет

- Electrical Load List: Mohammed N.M. Al-Baddah & PartnerДокумент12 страницElectrical Load List: Mohammed N.M. Al-Baddah & PartnerJesОценок пока нет

- IMP REF Design and Characterization of Ferroelectric Negative CapacitanceДокумент126 страницIMP REF Design and Characterization of Ferroelectric Negative Capacitancesai prashanthОценок пока нет

- SE-797.2 ARTICLE 23 Standard Practice For Measuring Thickness by Manual Ultrasonic Pulse-Echo Contact MethodДокумент8 страницSE-797.2 ARTICLE 23 Standard Practice For Measuring Thickness by Manual Ultrasonic Pulse-Echo Contact MethodSean LavergneОценок пока нет

- Brochure Shield PowerДокумент2 страницыBrochure Shield PowerRizki Heru HermawanОценок пока нет

- Copy Tripping and Control of Impulse GeneratorДокумент14 страницCopy Tripping and Control of Impulse Generatorrare machineОценок пока нет

- 02 Pca-N3060-LcdДокумент2 страницы02 Pca-N3060-LcdGUDANG BERITA KITAОценок пока нет

- Pressurisation Unit ScheduleДокумент1 страницаPressurisation Unit ScheduleArmağan DemirelОценок пока нет

- Wein Bridge Oscillators PresentationДокумент15 страницWein Bridge Oscillators PresentationHarish KumarОценок пока нет

- Power Industry in Vidarbha RegionДокумент10 страницPower Industry in Vidarbha RegionKetan PoddarОценок пока нет