Академический Документы

Профессиональный Документы

Культура Документы

Conformal ECO Flow

Загружено:

Umesh ParasharОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Conformal ECO Flow

Загружено:

Umesh ParasharАвторское право:

Доступные форматы

Encounter Conformal ECO Designer

ECO automation for greater predictability and design convergence

Cadence Encounter Conformal ECO Designer enables designers to implement RTL engineering change orders (ECOs) for pre- and post-mask layout, and offers early ECO prototyping capabilities for driving critical Yes/No project decisions. Cadence ECO solutions combine automatic ECO analysis, logic optimization, and design netlist modication with world-class equivalence checking to provide superior performance, productivity, and predictability, helping you achieve convergence on your design goals.

Engineering Change Orders

Engineering change orders (ECOs) have a wide variety of implementations that range from adding or removing logic in a design to more subtle changes such as cleaning up routing for signal integrity. All ECOs are focused on delivering products to market as fast as possible with minimal risk to correctness and schedule. ECOs can be a time of high stress, long work hours, and uncertainty. Even if the logic change is implemented in the netlist, there might not be enough spare gates on the mask to implement the change. Available ows for processing ECOs may remove some of the uncertainty of whether the product will work, but they are still a manual process that typically requires many cycles to achieve correct implementation. If the ECO were implemented with only metal-layer changes, the cost would be greatly reduced. Having this early knowledge of implementability, a design team can change plans and target workable solutions rather than wasting time in failed attempts and extended schedules.

RTL Logic equivalence checking

Logic Synthesis (Area, Power, Timing, Yield) Datapath and Test Synthesis Floorplanning and Physical Synthesis ECOs

Extended functional checks Semantic checks Structural checks

Equivalence checking support for advanced datapath optimizations

Automatic ECO analysis and design netlist modification

Place and Route Physically-aware placement and spare gate mapping for for pre- and post-mask ECO

Encounter Conformal ECO Designer

Final Layout

ECOs

Encounter Conformal ECO Designer GXL

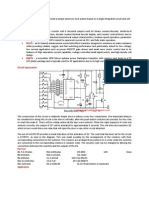

Figure 1: Encounter Conformal ECO Designer offers automatic ECO analysis and design netlist modication

Encounter Conformal ECO Designer

Encounter Conformal ECO Designer

Cadence offers the most complete ECO solution that spans from RTL to GDS. This solution consists of Encounter Conformal ECO Designer for ECO automation for RTL-level functional changes, Encounter RTL Compiler for logic synthesis and ECO logic optimization, and Encounter Design Implementation System for physical implementation of the ECO changes. This combined solution brings automation and predictability to the ECO process. Conformal ECO Designer is a unique technology that offers functional ECO analysis, optimization, and generation capability. It combines proven equivalence checking and functional checks, and uses formal techniques to analyze, abstract, and implement the functional ECO. Conformal ECO Designer is available in two congurations: an XL offering, which targets primarily the pre-mask ECO ow; and a GXL offering, which targets the pre-mask and post-mask ECO ow with metal-only layers and spare gates. The GXL conguration leverages physical database knowledge to generate ECO placement guidance for downstream place-and-route tools.

New RTL (R2)

Old RTL (R1)

ECO netlist (G3) is the hand-off point to the back-end physical implementation tool targeting a pre-mask or post-mask flow. Tool features: Supports combinational and sequential (the addition of new state elements) changes of the design

Synthesis

Synthesis

Test Insertion

Place & Route

Encounter Digital Implementation System

Incremental Optimizations P&R

Supports the addition of new ports Preserves the clock trees Preserves the scan chain Preservers the original netlist structure (G1) when it creates the new ECO netlist (G3) Recycles freed-up cells during the ECO analysis process

New Netlist (G2)

Old Netlist (G1)

Old DEF

Encounter Conformal ECO Designer

ECO Netlist (G3)

Final Netlist

P&R Guidance File

Figure 2: The Encounter Conformal ECO Designer implementation ow

Decreases the risk of missing critical bugs through independent verication technology

to make sure the ECO implementation was successful both for front-end and back-end signoff.

Features

Conformal ECO Designer combines logic equivalence checking (for the most complex SoC and datapath-intensive designs) with functional ECO analysis, design netlist modication, and logic optimization.

Functional ECO analysis

Conformal ECO Designer has a built-in ECO analysis engine that can identify the differences between the original design netlist and the new design netlist. Users can perform ECO analysis on the entire design or on specic modules within the design hierarchy, which is typically more efcient. Once the ECO analysis step is completed and the logic change optimized, Conformal ECO Designer performs the necessary netlist modications to achieve the new function in the original design netlist. The output is the ECO netlist. Alternately, Conformal ECO Designer can write out an ECO script that can be used to make direct changes to the place-and-route database.

Benefits

Provides faster turnaround time by minimizing manual intervention and eliminating time-consuming iterations Generates early estimates on ECO feasibility by quantifying designer intent Implements complex ECOs that are typically not attempted manually Enables front-end designers in fabless semiconductor companies earlier netlist handoff to ASIC vendors Improves designer productivity and offers exibility to do ECO with metal-only layers, thus reducing manufacturing costs and driving faster design convergence toward tapeout Reduces verication time signicantly by using abstraction techniques to verify multi-milliongate designs much faster than traditional gate-level simulation

Equivalence checking for ECOs

During development, a design undergoes numerous iterations prior to nal layout, and each step in this process has the potential to introduce logical bugs. Conformal ECO Designer checks the functional equivalence of different versions of a design at these various stages and enables designers to identify and correct errors as soon as they are introduced, ensuring initial intent remainsintact. Equivalence checking also plays an important role in the ECO implementation process. It helps the ECO analysis tool identify which modules and logic cones in the design require change to implement the ECO. For instance, in Figure 2, the original netlist is compared against the new netlist to determine what has changed. Equivalence checking is also used at the tail end of the process

Physically-aware pre-mask ECOs

Conformal ECO Designer (GXL) has the ability to read the DEF layout database corresponding to the original place-androute design netlist, LEF, Liberty synthesis libraries, and SDC timing constraints to optimize changes, estimate routing, and legally place the generated ECO logic into the design oorplan. The output of Conformal ECO Designer is the ECO netlist and the corresponding placement DEF le. This ow can reduce timing closure itera-

www.cadence.com

Encounter Conformal ECO Designer

tions during place-and-route, especially in late-state pre-mask ECO situations, to drive design convergence.

Spare gate mapping for postmaskECOs

Conformal ECO Designer (GXL) can also read the DEF layout database corresponding to the original design netlist, LEF, Liberty synthesis libraries, and SDC to optimally map ECO logic to standard cell and gate-array spare gates. The mapping engine is timing and spare cell location-aware. This capability enables the designer to get an early estimate of the ECO feasibility and drive convergence in the back-end implementation ow. Conformal ECO Designer (GXL) can also recycle freed-up cells in the ECO mapping process. The output is the ECO netlist and a spare gate mapping le, which instructs the place-and-route tool how to map the newly added ECO logic to specic spare logic resources in the layout.

issues sometimes experienced by new users. In tandem, non-equivalent analysis can be invoked if non-equivalences are encountered and can present concise root cause information for quicker debug. For hierarchical designs, Conformal ECO Designer includes smart technology for accelerating setup requirements through boundary conditions proling

Cadence Services and Support

Cadence application engineers can answer your technical questions by telephone, email, or Internetthey can also provide technical assistance and custom training Cadence certied instructors teach more than 70 courses and bring their real-world experience into the classroom More than 25 Internet Learning Series (iLS) online courses allow you the exibility of training at your own computer via the Internet Cadence Online Support gives you 24x7 online access to a knowledgebase of the latest solutions, technical documentation, software downloads, and more

Encounter Conformal Technology

To shorten overall design-cycle times and minimize silicon re-spins, designers need production-proven validation. Encounter Conformal verication technologies offer the most comprehensive and trusted solutions for equivalence checking, timing constraints management, asynchronous clock-domain-crossing synchronization checks, functional ECO analysis and generation, and low-power design verication. The Encounter Conformal technology family consists of Conformal Constraint Designer, Conformal Equivalence Checker, Conformal Low Power, and Conformal ECO Designer.

Integrated environment

An intuitive GUI is provided for setup and debugging, allowing the user to work more productively and quickly pinpoint the cause of equivalence mismatches. Included are: Graphical debugging via an integrated schematic viewer that shows logic values for each error vector Full cross-highlighting between RTL model and circuit Automatic error candidate identication with assigned and weighted percentages Logic-cone pruning to focus debugging on relevant information

Platforms

Linux (32-bit, 64-bit) Sun Solaris (64-bit) IBM AIX (64-bit)

Language Support

Verilog (1995, 2001, 2005) SystemVerilog VHDL (87, 93) SPICE (traditional, LVS) EDIF Liberty Mixed languages

Smart setup and diagnosis

Conformal ECO Designer includes a set of intelligent analysis commands to ease setup and diagnosis. Smart setup investigates the current environment and automatically remedies common setup

Cadence is transforming the global electronics industry through a vision called EDA360. With an application-driven approach to design, our software, hardware, IP, and services help customers realize silicon, SoCs, and complete systems efciently and protably. www.cadence.com

2012 Cadence Design Systems, Inc. All rights reserved. Cadence, the Cadence logo, Conformal, and Encounter are registered trademarks of Cadence Design Systems, Inc. All others are properties of their respective holders. 22719 04/12 MK/DM/PDF

Вам также может понравиться

- Boxer EngineДокумент84 страницыBoxer EngineTOONGA100% (7)

- Atlatl Dart TuningДокумент3 страницыAtlatl Dart TuningGuillermo BustosОценок пока нет

- Verilog Coding For SynthesisДокумент21 страницаVerilog Coding For Synthesisbibincm100% (1)

- 10-Coding Guidelines 07Документ16 страниц10-Coding Guidelines 07sckidОценок пока нет

- Design For Test by Alfred L CrouchДокумент117 страницDesign For Test by Alfred L CrouchSrikanth100% (4)

- Tutorial Complete CadenceДокумент59 страницTutorial Complete Cadenceswain.ayasОценок пока нет

- Intel® Core™ Voltage Regulator-Down (VRD) 11.1 - Processor Power Delivery Design GuidelinesДокумент132 страницыIntel® Core™ Voltage Regulator-Down (VRD) 11.1 - Processor Power Delivery Design Guidelinesaqua01Оценок пока нет

- SCT 4 Platform Design Spec Rev1 4 PDFДокумент62 страницыSCT 4 Platform Design Spec Rev1 4 PDFChhoemSovannОценок пока нет

- NoC Memory ControllerДокумент74 страницыNoC Memory ControllerAshish BabuОценок пока нет

- Tutorial CadenceДокумент226 страницTutorial CadenceRafael Sanchotene Silva50% (2)

- Astrology, Vedic, Eook) - Gayatri Devi Vasudev - Art of Matching Charts (OCR)Документ178 страницAstrology, Vedic, Eook) - Gayatri Devi Vasudev - Art of Matching Charts (OCR)virpara100% (12)

- Jaimini's Chara Dasha: My ApproachДокумент24 страницыJaimini's Chara Dasha: My ApproachViru MandiОценок пока нет

- KP Watch Predictive Technique 1Документ18 страницKP Watch Predictive Technique 1vaibhavsattikarОценок пока нет

- JLN550 InstalДокумент54 страницыJLN550 InstalCostas PeppasОценок пока нет

- Clock Domain CrossingДокумент15 страницClock Domain CrossingMukesh PandaОценок пока нет

- DC TutorialДокумент132 страницыDC TutorialYongwoo KimОценок пока нет

- VerilogTutorial 2Документ80 страницVerilogTutorial 2Manjinder Singh BaathОценок пока нет

- Tessent AppNote Memory Shared BUSДокумент38 страницTessent AppNote Memory Shared BUSUmesh Parashar100% (2)

- Parallel Per-Critical-Clock (PPCC) Logic Synthesis and Netlist Fusion For Best PPA and ConvergenceДокумент9 страницParallel Per-Critical-Clock (PPCC) Logic Synthesis and Netlist Fusion For Best PPA and ConvergencepankajmudgilОценок пока нет

- Good VLSI Design Test Power TutorialДокумент1 515 страницGood VLSI Design Test Power TutorialprakashthamankarОценок пока нет

- 008 ArchitecturalДокумент45 страниц008 ArchitecturalPrashant SinghОценок пока нет

- Astrovision Emagazine Mar 2008Документ80 страницAstrovision Emagazine Mar 2008badriaa_1Оценок пока нет

- Application Specific Integrated Circuit (ASIC) TechnologyОт EverandApplication Specific Integrated Circuit (ASIC) TechnologyNorman EinspruchОценок пока нет

- Multi Clock DesignДокумент37 страницMulti Clock DesignRoc Kim Sí ĐiểuОценок пока нет

- Predicting With KP Horary-20090530-152835Документ11 страницPredicting With KP Horary-20090530-152835Santanu Halder100% (1)

- AQUATOOL A Generalized Decision Support System For Water Resources Planning and Operational Management 1996 Journal of HydrologyДокумент23 страницыAQUATOOL A Generalized Decision Support System For Water Resources Planning and Operational Management 1996 Journal of Hydrologyhoc_kinowОценок пока нет

- Practical Design For Transferring Signals Between Clock DomainsДокумент4 страницыPractical Design For Transferring Signals Between Clock DomainsbikirangОценок пока нет

- Introduction To Logic Synthesis Using Verilog HDLДокумент84 страницыIntroduction To Logic Synthesis Using Verilog HDLritesh_necОценок пока нет

- Allegro15 7TrainingBook1-11918Документ504 страницыAllegro15 7TrainingBook1-11918Văn CôngОценок пока нет

- ABCs of Synthesis Part OneДокумент37 страницABCs of Synthesis Part Onemadhu.thomas4541100% (1)

- Using OCC For Full Scan Design PDFДокумент6 страницUsing OCC For Full Scan Design PDFUmesh ParasharОценок пока нет

- Signal Integrity PDFДокумент23 страницыSignal Integrity PDFKhadar Basha100% (1)

- DC Tutorial Using DVДокумент126 страницDC Tutorial Using DVYongwoo KimОценок пока нет

- Rambus 112G XSR and LR SerDes PHYs EbookДокумент10 страницRambus 112G XSR and LR SerDes PHYs EbookLe Tan100% (1)

- MQ SSL/TLS Channels Including V8 ChangesДокумент23 страницыMQ SSL/TLS Channels Including V8 ChangesAnkit GuptaОценок пока нет

- RAM Sequential ATPGДокумент14 страницRAM Sequential ATPGUmesh ParasharОценок пока нет

- Tmax For ATPG N DiagnosisДокумент23 страницыTmax For ATPG N DiagnosisUmesh ParasharОценок пока нет

- 23 RohiniNakPadasInRavanaSamhitaДокумент15 страниц23 RohiniNakPadasInRavanaSamhitaSaptarishisAstrology100% (9)

- Tutorial LSIДокумент64 страницыTutorial LSIrahulОценок пока нет

- Atpg Coverage LossДокумент4 страницыAtpg Coverage LossUmesh ParasharОценок пока нет

- 2200SRM1266 (06 2006) Uk enДокумент28 страниц2200SRM1266 (06 2006) Uk enEbied Yousif Aly100% (9)

- Verilog Interview Questions and AnswersДокумент16 страницVerilog Interview Questions and AnswersAashish AggarwalОценок пока нет

- Low Power Techniques in VlsiДокумент21 страницаLow Power Techniques in VlsiKool RakeshОценок пока нет

- Tutorial For Design Compiler: Shell PromptДокумент7 страницTutorial For Design Compiler: Shell Promptsudhakar kandiОценок пока нет

- Digital Design of Signal Processing Systems: A Practical ApproachОт EverandDigital Design of Signal Processing Systems: A Practical ApproachРейтинг: 5 из 5 звезд5/5 (1)

- High-Bandwidth Memory Interface DesignДокумент86 страницHigh-Bandwidth Memory Interface DesignfhxlnxОценок пока нет

- WPS Chapter 7Документ34 страницыWPS Chapter 7richemengОценок пока нет

- Set Max Delay Vs False PathsДокумент3 страницыSet Max Delay Vs False PathsUmesh ParasharОценок пока нет

- Achieve High Test Coverage For SoCДокумент26 страницAchieve High Test Coverage For SoCUmesh Parashar100% (3)

- SWT 2 3 101 Brochure.Документ8 страницSWT 2 3 101 Brochure.Uhrin ImreОценок пока нет

- 2004-SNUG-paper Verilog PLI Versus SystemVerilog DPI PDFДокумент18 страниц2004-SNUG-paper Verilog PLI Versus SystemVerilog DPI PDFSaurabhABCОценок пока нет

- Dynamic Power Reduction WPДокумент6 страницDynamic Power Reduction WPRanganadh MvОценок пока нет

- SoC System DesignДокумент82 страницыSoC System DesignA B Shinde100% (2)

- M A P U PT PX A U P: Easuring Ctive Ower Sing SER ErspectiveДокумент13 страницM A P U PT PX A U P: Easuring Ctive Ower Sing SER ErspectiveStudent100% (1)

- Low-Power VLSI Design.Документ168 страницLow-Power VLSI Design.Tarun PrasadОценок пока нет

- X HCIДокумент13 страницX HCInithin_kumar_10100% (1)

- Low-Power Digital VLSI DesignДокумент530 страницLow-Power Digital VLSI DesignBhaskar KОценок пока нет

- Eda Scripting LanguagesДокумент7 страницEda Scripting LanguagesManchiramesh GupthaОценок пока нет

- Process MonitorДокумент25 страницProcess MonitorNitu Vlsi100% (1)

- Cadence Design With RTL Compiler PhysicalДокумент138 страницCadence Design With RTL Compiler PhysicalStudentОценок пока нет

- Interconnection NetworksДокумент91 страницаInterconnection NetworksSibghat RehmanОценок пока нет

- Intel (R) USB 3.0 EXtensible Host Controller Driver - Bring Up Guide r1.03Документ32 страницыIntel (R) USB 3.0 EXtensible Host Controller Driver - Bring Up Guide r1.03Michael Camilo Palma EscobarОценок пока нет

- Usb 3Документ75 страницUsb 3jintomathew100% (1)

- Mentorpaper 102908Документ79 страницMentorpaper 102908rohan357Оценок пока нет

- Introduction To Questa Autocheck Covercheck, and Formal Connectivity Checking PDFДокумент133 страницыIntroduction To Questa Autocheck Covercheck, and Formal Connectivity Checking PDFStacy McmahonОценок пока нет

- Time Borrowing and Time StealingДокумент9 страницTime Borrowing and Time StealingPradeep JagathratchaganОценок пока нет

- Smes - Lab3 - Systemc-TlmДокумент3 страницыSmes - Lab3 - Systemc-TlmTulio GaldencioОценок пока нет

- Switch Hardware ArchitectureДокумент65 страницSwitch Hardware ArchitecturevickygssnОценок пока нет

- Gsa Dac 2011 3dic GuideДокумент62 страницыGsa Dac 2011 3dic Guideyucl_98792Оценок пока нет

- Hiertest RAK Lab 16.1Документ41 страницаHiertest RAK Lab 16.1Veeranjaneyulu Dhikonda100% (1)

- Q T F SVA: Uick Utorial ORДокумент60 страницQ T F SVA: Uick Utorial ORsubash100% (1)

- PT PXДокумент4 страницыPT PXSuresh MandavaОценок пока нет

- Structured Analog CMOS DesignДокумент41 страницаStructured Analog CMOS DesignAshok BanjaraОценок пока нет

- Spruhj 7 AДокумент168 страницSpruhj 7 AAjaykumarОценок пока нет

- 14 MemoryДокумент95 страниц14 MemoryPrafulani GajbhiyeОценок пока нет

- Formal Verification of Low Power TechniquesДокумент6 страницFormal Verification of Low Power TechniquesShiva TripathiОценок пока нет

- Application-Specific Integrated Circuit ASIC A Complete GuideОт EverandApplication-Specific Integrated Circuit ASIC A Complete GuideОценок пока нет

- C KarakaДокумент13 страницC Karakajaiswal.utkarshОценок пока нет

- Astrology Dec2010 PDFДокумент47 страницAstrology Dec2010 PDFUmesh ParasharОценок пока нет

- Cell Based ATPG PDFДокумент8 страницCell Based ATPG PDFUmesh ParasharОценок пока нет

- C KarakaДокумент13 страницC Karakajaiswal.utkarshОценок пока нет

- Ieee 1149.6 FaqДокумент2 страницыIeee 1149.6 FaqUmesh ParasharОценок пока нет

- 3D IC DFT Chen SNUGДокумент9 страниц3D IC DFT Chen SNUGUmesh ParasharОценок пока нет

- Appnote HighCompressionДокумент6 страницAppnote HighCompressionUmesh ParasharОценок пока нет

- Ecc PDFДокумент68 страницEcc PDFUmesh Chandra ParasarОценок пока нет

- Tessent Scan (Dftadvisor) : Why The Clock Inputs On Some D Flop Flops Are Assigned Uo Faults?Документ3 страницыTessent Scan (Dftadvisor) : Why The Clock Inputs On Some D Flop Flops Are Assigned Uo Faults?Umesh ParasharОценок пока нет

- Cell Based ATPGДокумент8 страницCell Based ATPGUmesh ParasharОценок пока нет

- DFT Framwork Cpravikr 1Документ10 страницDFT Framwork Cpravikr 1Umesh ParasharОценок пока нет

- CLK Jitter CrossTalk Skew VGoodДокумент11 страницCLK Jitter CrossTalk Skew VGoodUmesh ParasharОценок пока нет

- Current Conveyor Application Notes MaximДокумент5 страницCurrent Conveyor Application Notes MaximUmesh ParasharОценок пока нет

- Swo-A (Clerks) Recruitment in Central Bank of India - 2012 (English)Документ19 страницSwo-A (Clerks) Recruitment in Central Bank of India - 2012 (English)mukeshОценок пока нет

- Answer To The Question No: (A) : Pattern Recognition Is The Process of Recognizing Patterns by UsingДокумент4 страницыAnswer To The Question No: (A) : Pattern Recognition Is The Process of Recognizing Patterns by UsingKhaled faisalОценок пока нет

- Unit No 1Документ64 страницыUnit No 1Aadil VahoraОценок пока нет

- Easy Harmony XA2 - XA2ED33Документ5 страницEasy Harmony XA2 - XA2ED33Rogger CriolloОценок пока нет

- MATLAB Modeling of SPT and Grain Size Data in Producing Soil-ProfileДокумент5 страницMATLAB Modeling of SPT and Grain Size Data in Producing Soil-Profileicv.xaviОценок пока нет

- 5000 KW Gearbox High Pinion Bearing Temperatures 1644227029Документ7 страниц5000 KW Gearbox High Pinion Bearing Temperatures 1644227029MC AОценок пока нет

- Dcs 2019 Questions PaperДокумент14 страницDcs 2019 Questions PaperDASHARATH VISHAWAKARMAОценок пока нет

- MATHSДокумент221 страницаMATHSAbdulai FornahОценок пока нет

- 3) Production SchedulingДокумент26 страниц3) Production SchedulingJhon Ace DuricoОценок пока нет

- Error MsgsДокумент162 страницыError Msgsapi-19417993Оценок пока нет

- Control of Concentration in CSTR Using DMC and Conventional Pid Based On Relay Feedback MethodДокумент8 страницControl of Concentration in CSTR Using DMC and Conventional Pid Based On Relay Feedback MethodSadagopan RajaОценок пока нет

- Parson Merton CritiqueДокумент9 страницParson Merton CritiqueVishnu VarmaОценок пока нет

- Manually Updating The Firmwares On A Dell PowerEdge R710 - Atualizar Firmwares DellДокумент6 страницManually Updating The Firmwares On A Dell PowerEdge R710 - Atualizar Firmwares Dellaltero spОценок пока нет

- Math Iv Chapter 3Документ60 страницMath Iv Chapter 3Benjamin AkingeneyeОценок пока нет

- LAB REPORT BUCKLING OF STRUTS (Reference)Документ13 страницLAB REPORT BUCKLING OF STRUTS (Reference)jajenОценок пока нет

- ThinkSmart Hub SpecДокумент5 страницThinkSmart Hub SpecJose LopezОценок пока нет

- Random Sampling - QuizizzДокумент7 страницRandom Sampling - Quizizzmacjoven101Оценок пока нет

- DBMS Practice QueestionsДокумент2 страницыDBMS Practice QueestionsAbhibhava Bhatt VIII [E] 4Оценок пока нет

- Kolkata and North-East Centre at Tezpur: Indian Statistical InstituteДокумент1 страницаKolkata and North-East Centre at Tezpur: Indian Statistical InstitutePoonam NaiduОценок пока нет

- Test For CarbohydratesДокумент15 страницTest For CarbohydratesKevin SangОценок пока нет

- PNP Transistor OperationДокумент5 страницPNP Transistor OperationmohanОценок пока нет

- Bacterial ClassificationДокумент2 страницыBacterial ClassificationAndrew JavierОценок пока нет

- Electronic Door LockДокумент2 страницыElectronic Door LocktaindiОценок пока нет