Академический Документы

Профессиональный Документы

Культура Документы

Digital Integrated Circuits

Загружено:

shahanisubhashОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Digital Integrated Circuits

Загружено:

shahanisubhashАвторское право:

Доступные форматы

Digital Integrated

Digital Integrated

Circuits

Circuits

A Design Perspective

A Design Perspective

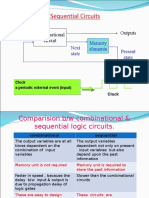

Designing Sequential

Designing Sequential

Logic Circuits

Logic Circuits

Mux

Mux

-

-

Based Positive Latch

Based Positive Latch

CLK

CLK

CLK

D

Q

CLK = 1, latch is transparent

CLK = 0, latch retains data

Sizing of transistors is not critical for realizing correct functionality since feedback

loop will be open when sampling data (no contention).

Not power efficient since it presents a load of 4 transistors to the CLK signal

Mux

Mux

-

-

Based Positive Latch

Based Positive Latch

NMOS only

CLK

CLK

Q

M

Q

M

Reduced CLK load to two transistors.

Drawbacks: Use of NMOS-only pass transistors results in a degraded 1 (V

dd

-V

tn

).

This impacts noise margin especially for low V

dd

values w.r.t. V

tn

. It also causes static

power dissipation in the first inverter since PMOS is not fully turned off.

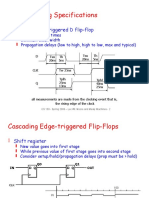

Master Master- -Slave (Positive Edge Slave (Positive Edge- -Triggered) Register Triggered) Register

1

0 D

CLK

Q

M

Master

0

1

CLK

Q

Slave

Q

M

Q

D

CLK

Cascade of two opposite latches trigger on edge

Also called master-slave latch pair

When CLK=0, Master is transparent, and D passes to Q

M

. The slave stage is in hold

mode, keeping the previous value by using feedback.

When CLK=1, the slave stage samples the output of the master stage (Q

M

), while

master goes into hold mode.

The value of Q is the value of D right before the rising edge of the clock, achieving

the (+ve) edge triggered effect.

Master

Master

-

-

Slave Register

Slave Register

Q

M

Q

D

CLK

T

2

I

2

T

1

I

1

I

3

T

4

I

5

T

3

I

4

I

6

Multiplexer-based latch pair

When CLK=0, Master is transparent, and D passes to Q

M

. The slave stage is in hold

mode, keeping the previous value by using feedback.

When CLK=1, the slave stage samples the output of the master stage (Q

M

), while

master goes into hold mode.

Drawback: high load presented to the clock signal (8 transistors) - > high power

dissipation

Master

Master

-

-

Slave Register

Slave Register

Q

M

Q

D

CLK

T

2

I

2

T

1

I

1

I

3

T

4

I

5

T

3

I

4

I

6

Multiplexer-based latch pair

Assuming delay of clock inverter = 0

t

pd_inv

= delay of each inverter, t

pd_tx

= delay of transmission gate

The setup time is the time before the rising edge of the clock that the input D must be valid. How long before

the rising edge of the clock must D be stable such that Q

M

samples the value reliably? Setup time = 3t

pd_inv

+

t

pd_tx

Propagation delay is the time it takes Q

M

to propagate to output Q. t

c-q

= t

pd_tx

+ t

pd_inv

.

The hold time is the time that the input must be held stable after the rising edge of the clock. T

1

turns off when

the clock goes high. Any changes in the input after the clock goes high do not affect the output. Hold time = 0

Reduced Clock Load Master Reduced Clock Load Master- -Slave Register Slave Register

D

Q

T

1

I

1

CLK

CLK

T

2

CLK

CLK

I

2

I

3

I

4

Feedback transmission gate is eliminated by directly cross-coupling the inverters - > lower clock loading.

Drawbacks:

T

1

and its source driver must overpower the feedback inverter (I

2

) to switch state of the cross coupled inverter.

The input of I

1

must be brought below its switching threshold in order to make a transition. I

2

must be made

weak (minimum sized, or increasing its L if T

1

is minimum sized which is desirable to reduce power

dissipation in latches and clock distribution network)

Reverse conduction the second stage can affect the state of the first latch. When slave stage is on, it is

possible for the combination of T

2

and I

4

to influence the data stored in the I

1

-I

2

latch. As long as I

4

is weak,

this is not a major problem.

Avoiding Clock Overlap

Avoiding Clock Overlap

CLK

CLK

A

B

(a) Schematic diagram of negative

master-slave register

(b) Overlapping clock pairs

X

D

Q

CLK

CLK

CLK

CLK

Assumptions: Delay of CLK generating inverter is

zero. No variations exist in wires used to

route the 2 clock signals. This effect is called

clock skew, which causes the clock signals to

overlap.

Two failures:

(1) When CLK goes high, the slave stage should

stop sampling the master stage output and

go into hold mode. With CLK overlap, both

sampling pass transistors conduct and there

is a direct path from D to Q. Thus data at the

output can change on the rising edge of the

clock, which is undesirable for a (-ve edge-

triggered register) Race condition

(2) The primary advantage of the MUX-based

register is that feedback loop is open during

sample period. Thus sizing of devices is not

critical to function correctly. With CLK

overlap, node A can be driven by both D and

B (would impact speed).

Overpowering the Feedback Loop

Overpowering the Feedback Loop

-

-

Cross

Cross

-

-

Coupled Pairs

Coupled Pairs

Forbidden State

S

S

R

Q

Q

Q

Q R S Q

Q 0 0 Q

1 0 1 0

0 1 0 1

0 1 1 0 R

Q

NOR-based set-reset

When both S and R are 0, the flip-flop is in quiescent state and both outputs retain their values (cross coupled

NORs look like cross coupled inverters). If a positive pulse is applied to S, output Q is forced into a 1 state. A

positive pulse applied to R resets the flip-flop, and Q goes to 0.

Asynchronous!

Ratioed

Ratioed

CMOS SR Latch

CMOS SR Latch

M

1

M

2

M

3

M

4

Q

M

5

S

M

6

CLK

M

7

R

M

8

CLK

V

DD

Q

Synchronous It consists of a cross-coupled inverter pair + 4 extra

transistors to drive the flip-flop from one state to

another and to provide synchronization. In steady

state, one inverter resides in high state, while other

in low.

Transistor sizing is essential to ensure that the flip-

flop can transition from one state to the other when

requested.

Case: If Q is 1 and R pulse is applied. In order to

make latch switch, we must bring Q below the

switching threshold of the inverter M1-M2, and

quickly. Once this is achieved, the positive feedback

causes the flip-flop to invert states. Thus, M5, M6,

M7, M8 should be sized up.

The combination between M4, M7, M8 form a ratioed

inverter.

To switch the latch from Q=0 to Q=1, it is essential

that the low level of the ratioed inverter (M5-M6)-M2

be below the switching threshold of M3-M4 (V

DD

/2).

Boundary condition occurs when V

Q

=V

DD

/2.

(W/L)

5-6

is the effective ratio of the series-connected

devices.

kn

1

]

1

,

_

1

]

1

,

_

2

) ( '

2

) ( '

2

2

2

6 5

DSATp

DSATp Tp DD p

DSATn

DSATn Tn DD n

V

V V V

L

W

k

V

V V V

L

W

k

Вам также может понравиться

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- Unit-Iii Sequential Logic CircuitsДокумент104 страницыUnit-Iii Sequential Logic CircuitsAswin ThangarajuОценок пока нет

- Unit 3 VLSIДокумент93 страницыUnit 3 VLSIPraba KaranОценок пока нет

- Unit-IV, V VLSI DESIGNДокумент91 страницаUnit-IV, V VLSI DESIGN2k20EC034 ANSHULIYERОценок пока нет

- Ακολουθιακά Κυκλώματα MosДокумент31 страницаΑκολουθιακά Κυκλώματα MosmallikaОценок пока нет

- Sequential LogicДокумент68 страницSequential LogicbabahussainОценок пока нет

- 954 As10 ECC211 2023Документ9 страниц954 As10 ECC211 2023sourishchandra08Оценок пока нет

- How CMOS Circuits Implement LogicДокумент20 страницHow CMOS Circuits Implement Logicaleph13experienceОценок пока нет

- Sequential StaticДокумент20 страницSequential Staticvivek singhОценок пока нет

- Exp D - FFДокумент5 страницExp D - FFalokjadhavОценок пока нет

- Setup1 1210Документ32 страницыSetup1 1210Akhila PurushothamanОценок пока нет

- Lec 11 Sequential Logic CircuitsДокумент49 страницLec 11 Sequential Logic CircuitsDeependra NigamОценок пока нет

- Synchronous: Sequential LogicДокумент67 страницSynchronous: Sequential LogickenОценок пока нет

- FlipflopsДокумент80 страницFlipflopsvikramkolanuОценок пока нет

- Working of C MOS (Single Edge Triggered)Документ4 страницыWorking of C MOS (Single Edge Triggered)Avinash BaldiОценок пока нет

- VLSI: MOS Characteristic - 5Документ41 страницаVLSI: MOS Characteristic - 5CGОценок пока нет

- Static Sequential CircuitsДокумент29 страницStatic Sequential CircuitsfneojwgfjeОценок пока нет

- Microsoft PowerPoint - ECE 334-Lecture 21nMOS - Currentand Transmission GatesДокумент5 страницMicrosoft PowerPoint - ECE 334-Lecture 21nMOS - Currentand Transmission GatesFatmir KelmendiОценок пока нет

- Experiment No. 3.1Документ5 страницExperiment No. 3.1Harshal AmbatkarОценок пока нет

- Typical Timing Specifications: Positive Edge-Triggered D Flip-FlopДокумент50 страницTypical Timing Specifications: Positive Edge-Triggered D Flip-Flopanusha killariОценок пока нет

- Transmission Gate Based CircuitsДокумент43 страницыTransmission Gate Based CircuitsParul TrivediОценок пока нет

- Chapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State UniversityДокумент6 страницChapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State Universitydemos2011Оценок пока нет

- Introduction To IC 555 TimerДокумент66 страницIntroduction To IC 555 TimermuraliОценок пока нет

- Monostable MultivibratorДокумент4 страницыMonostable MultivibratorSakshi GosaviОценок пока нет

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Документ34 страницыDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaОценок пока нет

- UntitledДокумент8 страницUntitledlalita chauhanОценок пока нет

- 555 Timer Operation and ApplicationsДокумент16 страниц555 Timer Operation and ApplicationsMassSomeshОценок пока нет

- Learn The Basics First!: Flip FlopsДокумент7 страницLearn The Basics First!: Flip FlopsBharath Kumar100% (1)

- Digital Electronics II: Tutorial QuestionsДокумент3 страницыDigital Electronics II: Tutorial QuestionsreddygjОценок пока нет

- CounterДокумент22 страницыCounterMahesh MahiОценок пока нет

- ECE465 Clocking Methodologies Lecture NotesДокумент21 страницаECE465 Clocking Methodologies Lecture NotesMohammed El-AdawyОценок пока нет

- EE 213 Experiment 9: Design and Study Multi-vibrators Using 555 Timer ICДокумент5 страницEE 213 Experiment 9: Design and Study Multi-vibrators Using 555 Timer ICMuhammad SameerОценок пока нет

- University of Engineering and Technology, Lahore Department of Electrical EngineeringДокумент5 страницUniversity of Engineering and Technology, Lahore Department of Electrical EngineeringMuhammad SameerОценок пока нет

- Static Sequential XIДокумент30 страницStatic Sequential XISHOBHIT SHARMAОценок пока нет

- Module-4: Flip-Flops, Registers and CountersДокумент111 страницModule-4: Flip-Flops, Registers and CountersSanchitha GowdaОценок пока нет

- Sequential & Combinational Timing AnalysisДокумент8 страницSequential & Combinational Timing AnalysisSahil SharmaОценок пока нет

- Synchronous Sequential LogicДокумент69 страницSynchronous Sequential Logic魏延任Оценок пока нет

- Computer Architecture 1Документ39 страницComputer Architecture 1ARAFAT GaamanОценок пока нет

- Notes 326 Set8Документ16 страницNotes 326 Set8Bakshi AmitОценок пока нет

- 555 TimerДокумент76 страниц555 TimerSai Krishna KodaliОценок пока нет

- 555 Timer PDFДокумент76 страниц555 Timer PDFronaldo19940% (1)

- Integratedelectronics (Unit2) 555 TIMER ASTABLE MONOSTABLE MVДокумент5 страницIntegratedelectronics (Unit2) 555 TIMER ASTABLE MONOSTABLE MVYogeshwaranОценок пока нет

- Logic Gate Delay and Transition Time AnalysisДокумент24 страницыLogic Gate Delay and Transition Time AnalysisKarthick NpОценок пока нет

- Flip FlopsДокумент60 страницFlip FlopsA10-14Rajat KumarОценок пока нет

- 05 SeqДокумент46 страниц05 SeqRenju TjОценок пока нет

- Design of Static Flip-Flops For Low-Power DigitalДокумент8 страницDesign of Static Flip-Flops For Low-Power DigitalxmzbiskydemrfuvsjvОценок пока нет

- Clocking Part 2Документ4 страницыClocking Part 2Dmitry LeyzerovichОценок пока нет

- Modeling and Analysis of DC-DC Converters Under Pulse Skipping ModulationДокумент6 страницModeling and Analysis of DC-DC Converters Under Pulse Skipping ModulationJeba AntonyОценок пока нет

- Gce Electronics Book Chapter 3Документ45 страницGce Electronics Book Chapter 3ventricebarrett14Оценок пока нет

- 10 Latches FFДокумент32 страницы10 Latches FFPalash SwarnakarОценок пока нет

- Performance Analysis of CMOS Flip-FlopsДокумент3 страницыPerformance Analysis of CMOS Flip-FlopsEditor IJRITCCОценок пока нет

- ENG112-Introduction to Electrical and Computer Engineering Fall 2003 Prof. Russell Tessier Understanding Sequential Circuit TimingДокумент8 страницENG112-Introduction to Electrical and Computer Engineering Fall 2003 Prof. Russell Tessier Understanding Sequential Circuit Timingchuku7Оценок пока нет

- ECE 124 Digital Circuits and Systems Assignment #6Документ4 страницыECE 124 Digital Circuits and Systems Assignment #6jahnavi thotaОценок пока нет

- Multi VibratorsДокумент24 страницыMulti VibratorsAnanthnag BezgamОценок пока нет

- Dynamic CMOSДокумент15 страницDynamic CMOSPoornanand NaikОценок пока нет

- M54HC221/221A M74HC221/221A: Dual Monostable MultivibratorДокумент14 страницM54HC221/221A M74HC221/221A: Dual Monostable MultivibratornooorОценок пока нет

- Topic 4Документ55 страницTopic 4tanay.s1Оценок пока нет

- 110 Waveform Generator Projects for the Home ConstructorОт Everand110 Waveform Generator Projects for the Home ConstructorРейтинг: 4 из 5 звезд4/5 (1)

- Figure 3.7. Four Basic Components of The 6812 Processor.: Processor Registers Bus Interface Unit Control Address DataДокумент18 страницFigure 3.7. Four Basic Components of The 6812 Processor.: Processor Registers Bus Interface Unit Control Address DatashahanisubhashОценок пока нет

- SyllabusДокумент2 страницыSyllabusshahanisubhashОценок пока нет

- Ece Engr 501 Chapter 02Документ29 страницEce Engr 501 Chapter 02shahanisubhashОценок пока нет

- Reliable NoC Design Literature ReviewДокумент1 страницаReliable NoC Design Literature ReviewshahanisubhashОценок пока нет

- MicroPADs for ASSURED Diagnostic TestsДокумент14 страницMicroPADs for ASSURED Diagnostic TestsshahanisubhashОценок пока нет

- Solutions Manual To Computer Architecture Pipelined and Parallel Processor DesignДокумент64 страницыSolutions Manual To Computer Architecture Pipelined and Parallel Processor DesignKapil Malhotra67% (3)

- DSD Lab 7Документ1 страницаDSD Lab 7shahanisubhashОценок пока нет

- Biom ChatДокумент7 страницBiom ChatshahanisubhashОценок пока нет

- ECE 251 HWДокумент2 страницыECE 251 HWshahanisubhashОценок пока нет

- Error ControlДокумент1 страницаError ControlshahanisubhashОценок пока нет

- Describe Another Possible Implementation of A Multiplier CircuitДокумент2 страницыDescribe Another Possible Implementation of A Multiplier CircuitshahanisubhashОценок пока нет

- T1 2 SignedConversionsДокумент3 страницыT1 2 SignedConversionsshahanisubhashОценок пока нет

- Lecture 5Документ6 страницLecture 5shahanisubhashОценок пока нет

- Change of VariableДокумент10 страницChange of VariableshahanisubhashОценок пока нет

- Laws and Theorems of Boolean AlgebraДокумент1 страницаLaws and Theorems of Boolean AlgebraJeff Pratt100% (5)

- Ics151 Fq05 FinalДокумент15 страницIcs151 Fq05 FinalshahanisubhashОценок пока нет

- Random Variables ExplainedДокумент6 страницRandom Variables ExplainedDigonto BistritoОценок пока нет

- Presentation PDFДокумент28 страницPresentation PDFshahanisubhashОценок пока нет

- Shahani Anmol PDFДокумент4 страницыShahani Anmol PDFshahanisubhashОценок пока нет

- Air Terminal ControlДокумент1 страницаAir Terminal ControlshahanisubhashОценок пока нет

- PPFormДокумент1 страницаPPFormParyushan BujurgeОценок пока нет

- PPFormДокумент1 страницаPPFormParyushan BujurgeОценок пока нет

- Signature Verification FormДокумент1 страницаSignature Verification FormshahanisubhashОценок пока нет

- Eee342 hw3 PDFДокумент2 страницыEee342 hw3 PDFRedion XhepaОценок пока нет

- The Camera Sensor Used in Mavic Pro and its High Frame Rate ModesДокумент3 страницыThe Camera Sensor Used in Mavic Pro and its High Frame Rate ModesAksanОценок пока нет

- All Rights Reserved, Central Computer Centre, SVNIT SuratДокумент1 страницаAll Rights Reserved, Central Computer Centre, SVNIT SuratVishwajeet S BОценок пока нет

- Ancillary Time Code (ATC) According To SMPTE 12M-2Документ2 страницыAncillary Time Code (ATC) According To SMPTE 12M-2mbush600% (1)

- Haier HLH37ATBBДокумент43 страницыHaier HLH37ATBBelectroniclm5795Оценок пока нет

- Regulador de Voltage KVGC 202Документ168 страницRegulador de Voltage KVGC 202enriqueunoОценок пока нет

- Basic Electrical Engineering Course Outcomes (39Документ3 страницыBasic Electrical Engineering Course Outcomes (39Mega rani RОценок пока нет

- USB Driver Installation and Modem Settings User Guide Cara Instalasi USB Driver Dan ModemДокумент18 страницUSB Driver Installation and Modem Settings User Guide Cara Instalasi USB Driver Dan ModemSaIiang Vaikha Shalma AnatashaОценок пока нет

- LCA Lec20-21 Thevenin-Norton 082010Документ19 страницLCA Lec20-21 Thevenin-Norton 082010Kainat KhalidОценок пока нет

- 568C3 OverviewДокумент15 страниц568C3 OverviewchioutedОценок пока нет

- LG Oled65g6p T-Con Board Layout Voltages 2017Документ10 страницLG Oled65g6p T-Con Board Layout Voltages 2017Fernando AguiarОценок пока нет

- LINEAR INTEGRATED CIRCUITS Unit3 Raghudathesh VTUДокумент30 страницLINEAR INTEGRATED CIRCUITS Unit3 Raghudathesh VTUraghudatheshОценок пока нет

- Fujitsu Esprimo X923 Desktop PC: Data SheetДокумент8 страницFujitsu Esprimo X923 Desktop PC: Data Sheetconmar5mОценок пока нет

- Secondary Storage Devices: A Secondary Storage Device Refers To Any Non-Volatile StorageДокумент22 страницыSecondary Storage Devices: A Secondary Storage Device Refers To Any Non-Volatile StorageAsh KingОценок пока нет

- FPGA Based Real Time Sensor Data AcquisitionДокумент26 страницFPGA Based Real Time Sensor Data AcquisitiondelviОценок пока нет

- Microprocessor Assignment on 8085 Architecture, Instructions, and ProgrammingДокумент2 страницыMicroprocessor Assignment on 8085 Architecture, Instructions, and ProgrammingM B KalikotayОценок пока нет

- SV Legacy SwapnilДокумент15 страницSV Legacy SwapnilSazzad HossainОценок пока нет

- Ver1.00 ETR306 Manual Eng PDFДокумент213 страницVer1.00 ETR306 Manual Eng PDFSergio Miguel Galindez SanchezОценок пока нет

- M863G Motherboard Manual ECS PCChips 863G 1 5E EnglishДокумент38 страницM863G Motherboard Manual ECS PCChips 863G 1 5E EnglishMeire Ellen MonteiroОценок пока нет

- Hella India ELECTRONICS Pvt. LTDДокумент30 страницHella India ELECTRONICS Pvt. LTDHimanshu BishtОценок пока нет

- C Programe1Документ7 страницC Programe1njpatel9Оценок пока нет

- VLSI Digital Signal Processing Systems by Keshab K ParhiДокумент25 страницVLSI Digital Signal Processing Systems by Keshab K Parhirahil1650% (4)

- Assignment ReportДокумент6 страницAssignment ReportAnaОценок пока нет

- Multiple Choice Questions For Electronics Engineering Part 1Документ4 страницыMultiple Choice Questions For Electronics Engineering Part 1Anshad100% (1)

- X555LI Repair Guide Signal Measurement PointsДокумент7 страницX555LI Repair Guide Signal Measurement Pointsopenid_6iaTksxPОценок пока нет

- Acti 9 iPF & iPRD - Surge Arrester - A9L15691Документ3 страницыActi 9 iPF & iPRD - Surge Arrester - A9L15691mustofa elektroОценок пока нет

- Transmission Lines and WaveguidesДокумент21 страницаTransmission Lines and WaveguidesVASANTHKUMAR M SОценок пока нет

- EE 201 Voltage/current Dividers - 1Документ13 страницEE 201 Voltage/current Dividers - 1bagru baafОценок пока нет

- G7 8 CSS Explo Module 4Документ27 страницG7 8 CSS Explo Module 4Heart NicoleОценок пока нет

- 27 GHZ Silicon - Contacted Waveguide - Coupled GeSi Avalanche PhotodiodeДокумент7 страниц27 GHZ Silicon - Contacted Waveguide - Coupled GeSi Avalanche Photodiodeanushpamathi SundararajanОценок пока нет