Академический Документы

Профессиональный Документы

Культура Документы

6t Sram Cell

Загружено:

Khushi SidАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

6t Sram Cell

Загружено:

Khushi SidАвторское право:

Доступные форматы

T SRAM Cell6

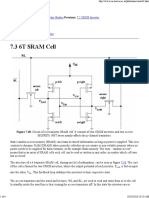

Figure 7.18: Circuit of a 6 transistor SRAM cell. It consists of two CMOS inverters and two access .MOSFETs. NBT stress mainly affects the p-channel transistors

Static random access memory (SRAM) can retain its stored information as long as power is supplied. This is in contrast to dynamic RAM (DRAM) where periodic refreshes are necessary or non-volatile memory where no power needs to be supplied for data retention, as for example flash memory. The term ``random access'' means that in an array of SRAM cells each cell can be read or written in any .order, no matter which cell was last accessed

The structure of a 6 transistor SRAM cell, storing one bit of information, can be seen in Figure 7.18. The core of the cell is formed by two CMOS inverters, where the output potential of each inverter is .fed as input into the other . This feedback loop stabilizes the inverters to their respective state

The access transistors and the word and bit lines, WL and BL, are used to read and write from or to the cell. In standby mode the word line is low, turning the access transistors off. In this state the inverters are in complementary state. When the p-channel MOSFET of the left inverter is turned on, .the potential is high and the p-channel MOSFET of inverter two is turned off, is low

To write information the data is imposed on the bit line and the inverse data on the inverse bit line, . Then the access transistors are turned on by setting the word line to high. As the driver of the bit lines is much stronger it can assert the inverter transistors. As soon as the information is stored in the inverters, the access transistors can be turned off and the information in the inverter is .preserved

For reading the word line is turned on to activate the access transistors while the information is sensed at the bit lines .

Static Noise Margin 1.3.7

Figure 7.19: Static noise margin (SNM) of the unstressed SRAM cell. The window in the ``butterfly'' .curve illustrates the hardiness against DC noise A key figure of merit for an SRAM cell is its static noise margin (SNM). It can be extracted by nesting the largest possible square in the two voltage transfer curves (VTC) of the involved CMOS inverters, as seen in Figure 7.19. The SNM is defined as the side-length of the square, given in volts. When an .external DC noise is larger than the SNM, the state of the SRAM cell can change and data is lost

Steady State Degradation 1.3.7

The effect of NBTI impacts one or both p-channel MOSFETs in the SRAM cell, depending on the charge state during temperature stress. The result is a degraded VTC and, therefore, a degraded .SNM

Figure 7.20: Degradation of one p-channel MOSFET in an SRAM cell. An interface trap density cm .causes read failure even at zero noise Figure 7.20 shows the impact of NBTI on an SRAM cell. Here, only one of the p-channel MOSFETs is degraded. This is the typical situation when the information stored in the cell does not change frequently. An interface trap density of is enough to drastically reduce the SNM. At the window .completely disappears and the SRAM cell loses its functionality

Figure 7.21: Degradation of both p-channel MOSFET in an SRAM cell. The original ``butterfly'' curve is .completely degenerated Assumed degradation of both p-channel MOSFETs results in shift of the VTCs of both inverters .(Figure 7.21). This leads to a complete degeneration of the original VTCs

Вам также может понравиться

- 6T SRAM SimulationДокумент9 страниц6T SRAM SimulationAzza FaiadОценок пока нет

- A Comparative Study of 6T, 8T and 9T SRAM CellДокумент4 страницыA Comparative Study of 6T, 8T and 9T SRAM CellijaertОценок пока нет

- 6T SRAM simulationДокумент9 страниц6T SRAM simulationAzza FaiadОценок пока нет

- VLSI - Memory Design (SRAM)Документ19 страницVLSI - Memory Design (SRAM)Karthik RamasamyОценок пока нет

- Hspice 2005Документ173 страницыHspice 2005何明俞Оценок пока нет

- CMOS Digital Integrated Circuits: Lec 5 SPICE Modeling of MOSFETДокумент16 страницCMOS Digital Integrated Circuits: Lec 5 SPICE Modeling of MOSFETNIET14Оценок пока нет

- Mos Transistor TheoryДокумент144 страницыMos Transistor TheorymailtolokiОценок пока нет

- MOSFETДокумент21 страницаMOSFETParul Trivedi100% (1)

- Zipper Cmos Logic CircuitДокумент15 страницZipper Cmos Logic CircuitShreerama Samartha G BhattaОценок пока нет

- 33 7 LM V1 S1 Delay ModelingДокумент39 страниц33 7 LM V1 S1 Delay ModelingPriyanka AshishОценок пока нет

- Clocked CmosДокумент24 страницыClocked CmosAnil KumarОценок пока нет

- VLSI Lab CompendiumДокумент52 страницыVLSI Lab CompendiumSaad Ali Khan SherwaniОценок пока нет

- VLSI Design Assignment ReportДокумент18 страницVLSI Design Assignment ReportAlamgir MohammedОценок пока нет

- Wire ModelingДокумент68 страницWire ModelingprocatellОценок пока нет

- CMOS OpAmp Design FundamentalsДокумент62 страницыCMOS OpAmp Design FundamentalsNikitaPrabhuОценок пока нет

- Flash ADC MidsemДокумент9 страницFlash ADC MidsemBikashKumarMoharanaОценок пока нет

- VLSI UNIT 1 Part - III PDFДокумент35 страницVLSI UNIT 1 Part - III PDFKARTHIKAYEN AОценок пока нет

- Lecture 8 - Circuits Design Issues and Layout FormationДокумент18 страницLecture 8 - Circuits Design Issues and Layout FormationevildoctorbluetoothОценок пока нет

- Foundry Technologies 180-Nm Cmos, RF Cmos and Sige Bicmos: High-Performance Devices For A Wide Range of ApplicationsДокумент4 страницыFoundry Technologies 180-Nm Cmos, RF Cmos and Sige Bicmos: High-Performance Devices For A Wide Range of Applicationssandeep_sggsОценок пока нет

- Mississippi State University Dallas Semiconductor: Standard Cell TutorialДокумент133 страницыMississippi State University Dallas Semiconductor: Standard Cell Tutorialshri3415Оценок пока нет

- ECE 4141-Experiment 3 - CMOS NAND Transistors Sizing Simulation Using PSPICEДокумент6 страницECE 4141-Experiment 3 - CMOS NAND Transistors Sizing Simulation Using PSPICEAnwar Zainuddin100% (2)

- Two Stage Op-AmpДокумент4 страницыTwo Stage Op-AmpShreerama Samartha G BhattaОценок пока нет

- SRAM ArchitectureДокумент35 страницSRAM ArchitectureDr-Irfan Ahmad PindooОценок пока нет

- ESDynamic Logic CircuitsДокумент61 страницаESDynamic Logic CircuitsMandovi BorthakurОценок пока нет

- DelayДокумент31 страницаDelayvarun186Оценок пока нет

- SramДокумент34 страницыSramRicha GuptaОценок пока нет

- Digital Integrated Circuits: A Design PerspectiveДокумент84 страницыDigital Integrated Circuits: A Design PerspectivedurraizaliОценок пока нет

- Aulas15 16Документ16 страницAulas15 16Pramod Reddy RОценок пока нет

- Elmore Delay in RC Networks: September 16, 2010Документ3 страницыElmore Delay in RC Networks: September 16, 2010Siddharth SabharwalОценок пока нет

- Logical Effort: Boris Murmann Center For Integrated Systems Stanford UniversityДокумент10 страницLogical Effort: Boris Murmann Center For Integrated Systems Stanford UniversitysatyajtiОценок пока нет

- PROJECT1 S 2013 v2 PDFДокумент4 страницыPROJECT1 S 2013 v2 PDFHarshal SinghОценок пока нет

- CMOS CM & Biasing CircuitsДокумент50 страницCMOS CM & Biasing Circuitsabhi_jОценок пока нет

- Design of A RISC Microcontroller Core in 48 HoursДокумент11 страницDesign of A RISC Microcontroller Core in 48 HoursPulkit TrivediОценок пока нет

- Formal Verification Methods: SAT, BDDs, Model Checking & Equivalence CheckingДокумент52 страницыFormal Verification Methods: SAT, BDDs, Model Checking & Equivalence CheckingNavathej BangariОценок пока нет

- DFT For SRAMДокумент9 страницDFT For SRAMsuneeldvОценок пока нет

- HSPICE TutorialДокумент7 страницHSPICE TutorialSreyas MohanОценок пока нет

- Basic Cell HSpice CodeДокумент4 страницыBasic Cell HSpice CodeWaqar IshaqОценок пока нет

- Introduction To Cmos Vlsi Design: SPICE SimulationДокумент28 страницIntroduction To Cmos Vlsi Design: SPICE SimulationSarthak SharmaОценок пока нет

- Mosfet 1Документ33 страницыMosfet 1Palash SwarnakarОценок пока нет

- ZhengchenДокумент139 страницZhengchenAnh PhanОценок пока нет

- CMOS BasicsДокумент41 страницаCMOS BasicsYeshoda MallikarjunaОценок пока нет

- Delay Time Estimation in Digital DesignДокумент12 страницDelay Time Estimation in Digital DesignSandeep PaulОценок пока нет

- Dynamic Logic Circuits: A. MarzukiДокумент25 страницDynamic Logic Circuits: A. Marzukisreekanthreddy peramОценок пока нет

- Lab 5 Music Player and Audio Amp Fall 2014Документ8 страницLab 5 Music Player and Audio Amp Fall 2014SteveОценок пока нет

- Schematic and Layout Design of a Differential Amplifier CircuitДокумент9 страницSchematic and Layout Design of a Differential Amplifier CircuitFrancisco De KamimoreОценок пока нет

- RV12 RISC-V CPU Core DatasheetДокумент73 страницыRV12 RISC-V CPU Core DatasheetJoão VictorОценок пока нет

- Power Dissipation in CMOS Circuits: Advanced VLSI EEE 6405 Slide1 Abm Harun-Ur RashidДокумент28 страницPower Dissipation in CMOS Circuits: Advanced VLSI EEE 6405 Slide1 Abm Harun-Ur RashidAbu RaihanОценок пока нет

- ETIN25 - Analogue IC Design Laboratory Manual - Lab 2: Jonas Lindstrand Martin Liliebladh Markus Törmänen September 2011Документ14 страницETIN25 - Analogue IC Design Laboratory Manual - Lab 2: Jonas Lindstrand Martin Liliebladh Markus Törmänen September 2011Western777Оценок пока нет

- RC Optimization Best PracticesДокумент12 страницRC Optimization Best PracticespradeepmanthaniОценок пока нет

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Документ34 страницыDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaОценок пока нет

- Hspice ExampleДокумент3 страницыHspice ExamplesriIITОценок пока нет

- Lecture3 PartitionДокумент24 страницыLecture3 Partitionapi-3834272Оценок пока нет

- MOS Transistor IV Modeling and Regions of OperationДокумент47 страницMOS Transistor IV Modeling and Regions of OperationRaga LasyaОценок пока нет

- Verilog ReferenceДокумент77 страницVerilog ReferencePRANJAL SHRIVASTAVAОценок пока нет

- Enee359a Sizing PDFДокумент47 страницEnee359a Sizing PDFRakesh SahuОценок пока нет

- Resource Efficient LDPC Decoders: From Algorithms to Hardware ArchitecturesОт EverandResource Efficient LDPC Decoders: From Algorithms to Hardware ArchitecturesОценок пока нет

- MOS Integrated Circuit DesignОт EverandMOS Integrated Circuit DesignE. WolfendaleОценок пока нет

- Millimicrosecond Pulse Techniques: International Series of Monographs on Electronics and InstrumentationОт EverandMillimicrosecond Pulse Techniques: International Series of Monographs on Electronics and InstrumentationОценок пока нет

- 7.3 6T SRAM Cell: 7.4 Ring Oscillator 7. Case Studies 7.2 CMOS InverterДокумент4 страницы7.3 6T SRAM Cell: 7.4 Ring Oscillator 7. Case Studies 7.2 CMOS InverterGowtham SpОценок пока нет

- LinesДокумент1 страницаLinesKhushi SidОценок пока нет

- Radiation: Sources 1. Natural Sources: A. Cosmic Rays B. EnvironmentalДокумент9 страницRadiation: Sources 1. Natural Sources: A. Cosmic Rays B. EnvironmentalKhushi SidОценок пока нет

- TurkeyДокумент1 страницаTurkeyKhushi SidОценок пока нет

- RepentanceДокумент1 страницаRepentanceKhushi SidОценок пока нет

- Scenario of Symbol Table Code in C LanguageДокумент4 страницыScenario of Symbol Table Code in C LanguageKhushi SidОценок пока нет

- TurkryДокумент1 страницаTurkryKhushi SidОценок пока нет

- CompaniesДокумент3 страницыCompaniesKhushi SidОценок пока нет

- LinesДокумент1 страницаLinesKhushi SidОценок пока нет

- Job Title Technical Report Writer School/Institute/Centre SeecsДокумент2 страницыJob Title Technical Report Writer School/Institute/Centre SeecsKhushi SidОценок пока нет

- 6th Central Pay Commission Salary CalculatorДокумент15 страниц6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Call CenterДокумент3 страницыCall CenterKhushi SidОценок пока нет

- DIGITAL SIGNAL PROCESSING 4.4 ExercisesДокумент19 страницDIGITAL SIGNAL PROCESSING 4.4 ExercisesKhushi SidОценок пока нет

- W1 (KG) W2 (KG) W3 (KG) Spring Load Guage Reading (KG) Load Case 1 Load Case 2 Load Case 3 Load Case 4Документ2 страницыW1 (KG) W2 (KG) W3 (KG) Spring Load Guage Reading (KG) Load Case 1 Load Case 2 Load Case 3 Load Case 4Khushi SidОценок пока нет

- TurkeyДокумент1 страницаTurkeyKhushi SidОценок пока нет

- Primary ResearchДокумент2 страницыPrimary ResearchKhushi SidОценок пока нет

- Social EVILS: DR Rahim Iqbal MBBS (PB) .MPH (H.S.A) Senior Demonstrator Rawalpindi Medical College RawalpindiДокумент32 страницыSocial EVILS: DR Rahim Iqbal MBBS (PB) .MPH (H.S.A) Senior Demonstrator Rawalpindi Medical College RawalpindiKhushi SidОценок пока нет

- Sin Function Plots in MATLABДокумент5 страницSin Function Plots in MATLABKhushi SidОценок пока нет

- Binder 1Документ9 страницBinder 1Khushi SidОценок пока нет

- Apply for PhD Support in UKДокумент3 страницыApply for PhD Support in UKKhushi SidОценок пока нет

- Best Sample Paper For Pieas TestДокумент2 страницыBest Sample Paper For Pieas TestKhushi SidОценок пока нет

- Radiation: Sources 1. Natural Sources: A. Cosmic Rays B. EnvironmentalДокумент9 страницRadiation: Sources 1. Natural Sources: A. Cosmic Rays B. EnvironmentalKhushi SidОценок пока нет

- FaithДокумент1 страницаFaithKhushi SidОценок пока нет

- Lab No 7Документ13 страницLab No 7Khushi SidОценок пока нет

- 08 Helping Material PDFДокумент16 страниц08 Helping Material PDFKhushi SidОценок пока нет

- Argument Format For GREДокумент1 страницаArgument Format For GREKhushi SidОценок пока нет

- SufismДокумент1 страницаSufismKhushi SidОценок пока нет

- FaithДокумент1 страницаFaithKhushi SidОценок пока нет

- Transistor Configuration Comparison ChartДокумент1 страницаTransistor Configuration Comparison ChartKhushi SidОценок пока нет

- 6th Central Pay Commission Salary CalculatorДокумент15 страниц6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Instructions With LINKДокумент2 страницыInstructions With LINKJoubert LimaОценок пока нет

- EM12c: Troubleshooting Guide For Agent Availability Issues: Agent Unreachability / Status Pending / Metric Collection Error (Doc ID 1556515.1)Документ6 страницEM12c: Troubleshooting Guide For Agent Availability Issues: Agent Unreachability / Status Pending / Metric Collection Error (Doc ID 1556515.1)KoushikKc ChatterjeeОценок пока нет

- HUAWEI - E5172s-22 - LTE CPE - User Guide - FI PDFДокумент51 страницаHUAWEI - E5172s-22 - LTE CPE - User Guide - FI PDFyigit ozcanОценок пока нет

- Computer Networks Lab: Delhi Technological UniversityДокумент4 страницыComputer Networks Lab: Delhi Technological UniversityRonit KatariaОценок пока нет

- GK EXAM TITLEДокумент11 страницGK EXAM TITLETekg KarkiОценок пока нет

- Accops-Competitive AnalysisДокумент4 страницыAccops-Competitive AnalysisCastОценок пока нет

- AUTOSAR 3.2 Based Protocol Data Unit Router ModuleДокумент6 страницAUTOSAR 3.2 Based Protocol Data Unit Router ModuleEditor IJRITCCОценок пока нет

- CloudДокумент31 страницаCloudRam MetkarОценок пока нет

- Shahin Ahmed Laskar: First Find Out The Longest Match Prefix For 30.1.1.1/8Документ7 страницShahin Ahmed Laskar: First Find Out The Longest Match Prefix For 30.1.1.1/8fernandodaudОценок пока нет

- FW-300i Troubleshooting Guide v1.7Документ21 страницаFW-300i Troubleshooting Guide v1.7MichelleОценок пока нет

- Implementation of Cisco Physical Access Control SolutioДокумент114 страницImplementation of Cisco Physical Access Control Solutiowong vui torngОценок пока нет

- Micro Focus COBOL Animator HOW-ToДокумент32 страницыMicro Focus COBOL Animator HOW-ToSaurabhОценок пока нет

- Low Power, Low Price, Low Pin Count (20 Pin) Microcontroller With 4 KB OTPДокумент54 страницыLow Power, Low Price, Low Pin Count (20 Pin) Microcontroller With 4 KB OTPDavid helwlletОценок пока нет

- Shell Automation An Introduction To Bash Shell Scripting: Anoop JohnДокумент23 страницыShell Automation An Introduction To Bash Shell Scripting: Anoop JohnDodo winyОценок пока нет

- Extract block info in CIDRДокумент7 страницExtract block info in CIDRhimanchalОценок пока нет

- Ch. 4-MemoryManagement PDFДокумент42 страницыCh. 4-MemoryManagement PDFmikiasОценок пока нет

- EcoStruxure Process Expert Release Notes Foundation LibraryДокумент4 страницыEcoStruxure Process Expert Release Notes Foundation LibraryEl el irenОценок пока нет

- How To Remove VSCSI DiskДокумент6 страницHow To Remove VSCSI DiskilovedocОценок пока нет

- Athlon PDFДокумент12 страницAthlon PDFEquipo 7Оценок пока нет

- Prelim Quiz 2Документ3 страницыPrelim Quiz 2mycah cabualОценок пока нет

- IntroductionДокумент6 страницIntroductionKrutika BandreОценок пока нет

- Operation Manual: Valuejet Layer EditorДокумент51 страницаOperation Manual: Valuejet Layer EditorPaulo QuaresmaОценок пока нет

- Mobile Switching Center ServerДокумент3 страницыMobile Switching Center ServerCong-Son TranОценок пока нет

- Cisco IOS Image For GNS3 GitHubДокумент2 страницыCisco IOS Image For GNS3 GitHubEzequiel Almiron Galan0% (1)

- Sip Isdn Call FlowДокумент6 страницSip Isdn Call FlowphuongldОценок пока нет

- Life Cycle of A ThreadДокумент4 страницыLife Cycle of A ThreadshaunpackardОценок пока нет

- HPC Unit Test QuestionsДокумент5 страницHPC Unit Test QuestionsBECOB204 Sumaira HedaooОценок пока нет

- Digital Electronics and Microprocessor Lecture NotesДокумент187 страницDigital Electronics and Microprocessor Lecture Notes514 Vaibhavi PawarОценок пока нет

- RG-RIIP Inspection Platform Operational ManualДокумент22 страницыRG-RIIP Inspection Platform Operational ManualTun KyawОценок пока нет

- Data Types NotesДокумент9 страницData Types NotesSanthanaОценок пока нет