Академический Документы

Профессиональный Документы

Культура Документы

Laboratory 10 - LDO

Загружено:

Ariana Ribeiro LameirinhasИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Laboratory 10 - LDO

Загружено:

Ariana Ribeiro LameirinhasАвторское право:

Доступные форматы

experiment 10

Goal of the experiment

The goal of this experiment is to design a Low Dropout regulator using general purpose OP-Amp and PMOS and study its characteristics with extension to study characteristics of TPS7250 IC. We aim to design a linear voltage regulator with high efficiency which is used in low noise high efficiency applications.

10.3 Measurements to be taken

1 2 3

V0 = Vref _1 + R2 R1i the load regulation of the system. Load regulation Output Characteristics - Measure is given by dV0 V0 when Io is varying from minimum to maximum value. V0 = Vref _1 + R2 R1i V0 dV V 0 1 V V _ 0 20 R 1i ref = + Transfer Characteristics -R Measure the line regulation of the system. Line regulation dV0 V V is given by dV when is varying from minimum to maximum value. dI0 0 0 V0 dV0 V0 = Vref _1 + R2 R1i dI0 by applying the ripple input voltage and measuring Measure the ripple rejection dV 0 dV0 V0 dI0 voltage. the output ripple V0 dV Measure the output impedance of the LDO, which is given by dI 0 . We have shown 0 the sample output of load regulation and line regulation in Figure 10.2.

10.1 Brief theory and motivation

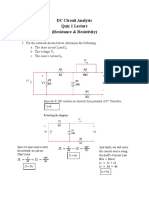

LDO is used to produce regulated voltage for high efficiency low noise applications. Please view the recorded lectures at [23] for a detailed description of voltage regulators. In case of DC-DC converter switching takes place (as shown by PWM waveform) and switching is a source of noise but in LDO no switching takes place hence it is used as voltage regulator in low noise high efficient systems. As shown in the circuit below LDO uses PMOS along with OP-Amp so that power dissipation in OP-Amp is minimal and efficiency is high. The regulated output voltage is given by V0 = Vref _1 + R2 R1i. VUN dV0 V0

S.No. 1 2 3 4

Reference Voltage

Output Voltage

V0 dV0 dI0

R Vref

Table 10.1: Variation of Load Regulation with Load Current in an LDO

R2 10k

VF1

R2

R 10k R2 VO = Vref [1+ ] R1 RL Z1 +

R6 10k R4 10k V1 D1 R5 2k

R1

Figure 10.1: Low Dropout Regulator (LDO)

R3 10k

10.2 Specifications

Generate 3V output when input voltage is varying from 4V to 5V. page 56 Figure 10.2: A regulator circuit and its simulated outputs - line regulation and load regulation

Analog System Lab Kit PRO

2 3

Take the plots of output characteristics, transfer characteristics and ripple rejection from the Oscilloscope and compare it with simulation results. Obtain the Load Regulation - Vary the load such that load current varies and obtain the output voltage, see the point till where output voltage remains constant. After that output will fall as the load current increases. Obtain the Ripple Rejection - Apply the input ripple voltage and see the output ripple voltage, with the input ripple voltage output ripple voltage will rise. Obtain the Line Regulation - Vary the input voltage and plot the output voltage as a function of the input voltage. Until the input reaches a certain value, the output voltage remains constant; after this point, the output voltage will rise as the input voltage is increased. Calculate the output impedance. S.No. 1 2 3 4 S.No. 1 2 3 4 Ripple Input Voltage Ripple Output Voltage Input Voltage Line Regulation

4 5

6

Input resistance (ohms)

Input voltage (V)

Figure 10.3: Variation of Line Regulation with Input Voltage in an LDO

10.4 What should you submit

1

Simulate the circuits and compute the output characteristics, transfer characteristics, and ripple rejection.

10.5 Exercise Set 10

Perform the same experiment with the specialized IC for LDO from Texas Instrument TPS7250 and compare the characteristics of both systems. page 57

Analog System Lab Kit PRO

experiment 10

Вам также может понравиться

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Tugas 2Документ2 страницыTugas 2shoffi arifin100% (2)

- Creating A Symbol For A Part: Figure 1: Download The ModelsДокумент9 страницCreating A Symbol For A Part: Figure 1: Download The ModelsAriana Ribeiro LameirinhasОценок пока нет

- Torque Control Guide: Tightening Torque and Tensile LoadДокумент2 страницыTorque Control Guide: Tightening Torque and Tensile LoadAriana Ribeiro LameirinhasОценок пока нет

- Introduction ElectromagneticsДокумент96 страницIntroduction ElectromagneticsAriana Ribeiro LameirinhasОценок пока нет

- Simulink 8.3 - Release 2014a - ElectronicsДокумент87 страницSimulink 8.3 - Release 2014a - ElectronicsAriana Ribeiro LameirinhasОценок пока нет

- Tea 5777Документ47 страницTea 5777Ariana Ribeiro LameirinhasОценок пока нет

- XiangYong ZhouДокумент8 страницXiangYong ZhouAriana Ribeiro LameirinhasОценок пока нет

- A Dimensions: (MM) B Recommended Land Pattern: (MM) : WE-PD SMD Shielded Power InductorДокумент6 страницA Dimensions: (MM) B Recommended Land Pattern: (MM) : WE-PD SMD Shielded Power InductorAriana Ribeiro LameirinhasОценок пока нет

- Tea 5767Документ40 страницTea 5767Ariana Ribeiro LameirinhasОценок пока нет

- Part 5Документ36 страницPart 5Ariana Ribeiro LameirinhasОценок пока нет

- Tea 5764Документ68 страницTea 5764Ariana Ribeiro LameirinhasОценок пока нет

- Chip Inductor (Chip Coil) : Power Inductor (Wire Wound Type) LQH55P Series (2220 Size)Документ2 страницыChip Inductor (Chip Coil) : Power Inductor (Wire Wound Type) LQH55P Series (2220 Size)Ariana Ribeiro LameirinhasОценок пока нет

- Series: Inductors For Standard CircuitsДокумент13 страницSeries: Inductors For Standard CircuitsAriana Ribeiro LameirinhasОценок пока нет

- Part 4Документ31 страницаPart 4jagadees21Оценок пока нет

- Chapter 4 - Analog Integrated Circuit Design by John ChomaДокумент92 страницыChapter 4 - Analog Integrated Circuit Design by John ChomaAriana Ribeiro LameirinhasОценок пока нет

- Spru889 - High Speed DSP Systems DesignДокумент77 страницSpru889 - High Speed DSP Systems DesignAriana Ribeiro LameirinhasОценок пока нет

- Chapter 5 - Analog Integrated Circuit Design by John ChomaДокумент95 страницChapter 5 - Analog Integrated Circuit Design by John ChomaAriana Ribeiro LameirinhasОценок пока нет

- 108104011Документ2 страницы108104011Raja ReddyОценок пока нет

- SCAA048 - Filtering TechniquesДокумент7 страницSCAA048 - Filtering TechniquesAriana Ribeiro LameirinhasОценок пока нет

- Chapter 6 - Analog Integrated Circuit Design by John ChomaДокумент134 страницыChapter 6 - Analog Integrated Circuit Design by John ChomaAriana Ribeiro Lameirinhas100% (1)

- Chapter 2 - Analog Integrated Circuit Design by John ChomaДокумент99 страницChapter 2 - Analog Integrated Circuit Design by John ChomaAriana Ribeiro LameirinhasОценок пока нет

- BJT Models and Biasing Circuits ExplainedДокумент125 страницBJT Models and Biasing Circuits ExplainedAriana Ribeiro LameirinhasОценок пока нет

- Nice Contact Headquarters LocationsДокумент1 страницаNice Contact Headquarters LocationsAriana Ribeiro LameirinhasОценок пока нет

- Telit LE70-868Документ41 страницаTelit LE70-868Ariana Ribeiro LameirinhasОценок пока нет

- Chapter 1 - Analog Integrated Circuit Design by John ChomaДокумент87 страницChapter 1 - Analog Integrated Circuit Design by John ChomaAriana Ribeiro LameirinhasОценок пока нет

- Anderson Final ETD VersionДокумент492 страницыAnderson Final ETD VersionAriana Ribeiro LameirinhasОценок пока нет

- ACS800 Manual For Laboratory WorksДокумент16 страницACS800 Manual For Laboratory WorksAriana Ribeiro LameirinhasОценок пока нет

- AMS ThesisДокумент85 страницAMS ThesisAriana Ribeiro LameirinhasОценок пока нет

- Multi Level Open End WindingДокумент6 страницMulti Level Open End WindinglohitashriyaОценок пока нет

- Datasheet Atmega32Документ346 страницDatasheet Atmega32Mas NyamОценок пока нет

- 2008 - Space Vector Based Hybrid PWM Techniques For Reduced Current Ripple by Gopalaratnam Narayanan and Di ZhaoДокумент14 страниц2008 - Space Vector Based Hybrid PWM Techniques For Reduced Current Ripple by Gopalaratnam Narayanan and Di ZhaoAriana Ribeiro LameirinhasОценок пока нет

- Complementary CMOS Inverter DC CharacteristicsДокумент47 страницComplementary CMOS Inverter DC CharacteristicsMuhammad Ali ShoaibОценок пока нет

- IC-R5 ServiceManualДокумент39 страницIC-R5 ServiceManualAntonio JacintoОценок пока нет

- Experiment 3Документ3 страницыExperiment 3ugurgul123Оценок пока нет

- Experiment No: 6: D.C. Motor Position Control SystemДокумент10 страницExperiment No: 6: D.C. Motor Position Control SystemMayank ShahabadeeОценок пока нет

- Operational AmplifiersДокумент42 страницыOperational AmplifiersOvijit KarmokarОценок пока нет

- Transistor Bias CircuitsДокумент13 страницTransistor Bias CircuitsKim NamjoonОценок пока нет

- 358 NДокумент14 страниц358 NGerardo BarbozaОценок пока нет

- LF151 LF251 - LF351: Wide Bandwidth Single J-Fet Operational AmplifierДокумент9 страницLF151 LF251 - LF351: Wide Bandwidth Single J-Fet Operational AmplifierEspino GámezОценок пока нет

- This Is The Only Piece of Paper You Will Turn In. Please Plan To Fit All Answers On This Page! Answer SheetДокумент24 страницыThis Is The Only Piece of Paper You Will Turn In. Please Plan To Fit All Answers On This Page! Answer SheetVenkatraman SwaminathanОценок пока нет

- Digital Electronics - Contd.: Rijil RamchandДокумент24 страницыDigital Electronics - Contd.: Rijil RamchandAshna JoseОценок пока нет

- Energy Efficient Cmos Full-Adders For Arthmetic ApplicationsДокумент24 страницыEnergy Efficient Cmos Full-Adders For Arthmetic Applicationsbalakrishna_battaОценок пока нет

- Digital Design MindbreakersДокумент5 страницDigital Design MindbreakersSriram Seshagiri100% (1)

- Design and Simulation of 4-Bit Flash Analog to Digital Converter for SpeedДокумент7 страницDesign and Simulation of 4-Bit Flash Analog to Digital Converter for SpeedAlisha KshetriОценок пока нет

- Circuit Analysis Midterm Exam PDFДокумент5 страницCircuit Analysis Midterm Exam PDFJuanito CayОценок пока нет

- Registers and Counters: 吳俊興 國立高雄大學 資訊工程學系 January 2006Документ28 страницRegisters and Counters: 吳俊興 國立高雄大學 資訊工程學系 January 2006Ayush GuptaОценок пока нет

- 4017 & 4026Документ3 страницы4017 & 4026Ronny SinagaОценок пока нет

- Unit - Ii Non Linear Waveshaping: Clipping CircuitsДокумент28 страницUnit - Ii Non Linear Waveshaping: Clipping CircuitsfaizankahanОценок пока нет

- Transistor NPN - 2SD880YДокумент2 страницыTransistor NPN - 2SD880Yararagi koyomiОценок пока нет

- Eup3482aeup3482a PDFДокумент11 страницEup3482aeup3482a PDFfabloОценок пока нет

- Dual Slope Integrating DVMДокумент4 страницыDual Slope Integrating DVMmohit100% (1)

- Description Features: InfinityДокумент5 страницDescription Features: InfinityRegistroregistroglobОценок пока нет

- CIT Refreshing Test TitleДокумент2 страницыCIT Refreshing Test TitleMani BharathiОценок пока нет

- Static Timing Analysis: - RoshanДокумент60 страницStatic Timing Analysis: - Roshanmani krishna yakkatiОценок пока нет

- Design of Fully Differential Operational Amplifier With High Gain, Large Bandwidth and Large Dynamic RangeДокумент93 страницыDesign of Fully Differential Operational Amplifier With High Gain, Large Bandwidth and Large Dynamic RangeAhmed EdrisОценок пока нет

- MHZ 1-Micron Cmos Pipelined 8-Bit Adder Using True Single-Phase Logic-Flip-FlopsДокумент4 страницыMHZ 1-Micron Cmos Pipelined 8-Bit Adder Using True Single-Phase Logic-Flip-FlopsMamta JatoliaОценок пока нет

- Unit 2 - Gate Level ModellingДокумент48 страницUnit 2 - Gate Level Modellingdave vegafriaОценок пока нет

- Ei Lab Model QPДокумент4 страницыEi Lab Model QPskarthikpriyaОценок пока нет

- Refresher Course in Transistor CombinedДокумент149 страницRefresher Course in Transistor CombinedZyxmn Daley JesОценок пока нет

- Lectures 16 To 18 - Op-AmpДокумент19 страницLectures 16 To 18 - Op-AmpAniketsingh MundlothОценок пока нет