Академический Документы

Профессиональный Документы

Культура Документы

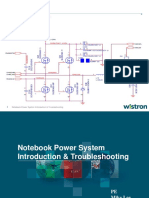

E420 Power Sequence

Загружено:

jesteraceАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

E420 Power Sequence

Загружено:

jesteraceАвторское право:

Доступные форматы

Lenovo E420 analysis, Wistron OEM, HM65 chipset. Protective isolation conduction conditions.

BQ24745 satisfied as long as the main power supply 22 feet, 2 feet AC_IN thresh old 17.6V, large internal 2.4V. 13 feet ACOK internal MOS transistor will be high impedance, 3-pin output 3.3V reference voltage provided pullups. Common point voltage is generated DCBATOUT. 3.3V and 5V system standby chip BD95280. BD95280 30 feet to the main power supply will be from 28 feet out after a 3.3V linear voltage PWR_5V3D3V_VREG2 And 5V linear voltage PWR_5V3D3V_VREG1, through PG4119, G9306 in order to conve rt 3D3V_PWR_2 and 5V_PWR_2 This board 5V_PWR_2 suspended only for the chip to 3 feet and 22 feet to provid e the BOOT voltage of 4.7V. 3D3V_PWR_2 convert 3D3V_AUX_S5 by PR4122 3D3V_AUX_S5 convert RTC_AUX_S5 through Q6001 replace the RTC battery. Provide the PCH RTC circuit provides power and 32.768KHZ clock. 3D3V_AUX_S5 another way to convert 3D3V_AUX_KBC, primarily to provide power for the EC and the reference voltage. Powered BAT_IN # LID_CLOSE # AC_IN_KBC EC_RST 4 have a high level signal, this machine in the boot BIOS chip. EC are met within the given S5_ENABLE converted through a resistor R3603 3V_5V_ EN As BD95280 2 feet and 21 feet as the opening of 3.3V and 5V signal. Thus BD95280 will produce 3V_PWR and 5V_PWR voltage is converted to 3D3V_S5 fol lowed by jumpers and 5V_S5 This 2-powered role and the PCH V5REF_Sus (PCH Southbridge internal power supply, this voltage is not normal, r esulting in full-board USB can not be used) VCCSUS3_3 (VccSus3_3 normal PLTRST # This signal only works) When the 3.3V and 5V normal, BD95280 issue 3V_5V_POK sent pQ1901 The cut-off on the pQ1901 produce PM_RSMRST # sent to the PCH E22 point (this s ignal with EC issued, 3V_5V_POK not generated on the front pQ1901 conduction to this signal low) PCH received PM_RSMRST # issued after SUS_CLK (32.768kZH) to the EC 77 feet to turn the clock EC EC on the clock, power, reset all OK premise issue AC_PRESENT (AC adapter into normal) to PCH Shorting the EC 93 feet KBC_PWRBTN_EC # and GND release, rising edge triggered, EC issued PM_PWRBTN # (rising edge active) to PCH PCH received the EC PM_PWRBTN # start signal, the first issue to the EC SLP_S4 # 21 feet the other way SLP_S4 # sent to PU4601 3 feet as memory, open signal to produce 1D5V_S3 Issuing SLP_S3 #, this signal is converted into the 5V_S0 3D3V_S5 1D5V_S0 5V_S5 3D3V_S0 converted into 1D5V_S3 SLP_S3 # Q3606 makes the cut-off all the way to the role and produce PS_S3CNTRL , PS_S3CNTRL role and Q3704 Makes Q3704 cutoff produce 0D75V_EN. 0D75V_EN normal high after the SLP_S4 # simultaneously sent to PU4604 as a turn -on signal, such that the resulting 0D75V_S0 (memory termination voltage) SLP_S3 # PU4701 role and another way of a pin as open signal, 1D5V_S3 and 1D8V_ S0 supply are normal issued RUNPWROK. RUNPWROK sent to PCH, inform RUN series power supply are normal. RUNPWROK another road and P *** P_S3 # phase as a turn-on signal is sent to the U3609, resulting PWR_1D05V_EN PWR_1D05V_EN and turn signals with RUNPWROK role and PU4501 as 3 feet, producin g 1D05V_VTT When the power supply is normal 1D05V_VTT issued after 1.05VTT_PWRGD 1.05VTT_PWRGD role and PU4801 of 15 feet as a turn-on signal, generating VCCSA_

PWR (0.85v) VCCSA_PWR normally issued after D85V_PWRGD to PCH, D85V_PWRGD another way to PU 4201 9 feet, as the CPU turn signal. PU4201 CPU on received signal, the output H_CPU_SVIDDAT (data) H_CPU_SVIDCLK (clock) H_CPU_SVIDDAT and H_CPU_SVIDCLK main communication with the CPU VID similar ide ntification. After decoding will return pu4201 PU4201 get decoded message is generated after the CPU power VCC_CORE and VCC_GF XCORE (CPU internal set of significant supply) VR_SVID_ALERT # (thermal alarm active low) (This signal is directly connected t o CPU, effective after, PU4201 will reduce CPU clock speed) CPU power supply to normal after PU4201 7 feet issued IMVP_PWRGD, another IMVP_ PWRGD normal PCH issue CLK_EXP_P and CLK_EXP_N CPU master clock, and motherboard desired clock frequency (this board internal clock chip integration and PCH) EC issued from 84 feet S0_PWR_GOOD, this signal is delayed by 200 ms in SLP_S3 # will be issued after normal. S0_PWR_GOOD and D85V_PWRGD are normally generated after PWROK. IMVP_PWRGD ANDed with S0_PWR_GOOD produce SYS_PWROK to PCH through U3603 PCH PCH received internally ANDed with PWROK and issued PM_DRAM_PWRGD PM_DRAM_PWRGD and 0D75V_EN phase to the CPU via U3701 produce VDDPWRGOOD After receiving VDDPWRGOOD CPU, PCH also issued to the CPU H_CPUPWRGD PCH issue PLT_RST reset CPU, EC, reader. PCH modules within the North Bridge. PCH internal Northbridge module is reset, PCH issued in a valid DGPU_PWR_EN # DGPU_PWR_EN # make Q9305 off, resulting DGPU_PWR_EN left the Q9301 Q9301 MOS is the right half of the G tube cutoff low Q9302 Q9302 conduction electrode potent ial makes the 3D3V_S0 into 3D3V_VGA_S0 as independence was VDDQ supply Makes the D9101 and D9201 DGPU_PWR_EN role in the off-state generator 8209A_EN/ DEM_VGA 8209A_EN/DEM_VGA as PU9201 opening signal such that the resulting VGA_CORE_PWR (independence was the main power supply) VGA_CORE_PWR normal PU9201 issue PWR_VGA_CORE_PGOOD through R9214 into DGPU_PWR OK (powered with R9213 and C9212 RC delay provided) DGPU_PWROK convert 1D5V_VGA_PWOK_R through R8601 DGPU_PWR_EN DGPU_PWROK as U9302 turn-signal generating 1V_VGA_S0 1V_VGA_S0 normally issued after 9025_PGOOD_1V, 8209A_EN/DEM_VGA 9025_PGOOD_1V DGPU_PWR_EN 3 group roles and Q9304 high signal In the conduction state so Q9304, Q9303, G low electrode potential, so that the RUN_ENABLE Q9303 into conduction RUNON_R_1, RUNON_R_1 voltage is 20V, so U9301 is turned into the 1D5V_S3 1D5V_VGA_S0 9025_PGOOD_1V and DGPU_PWR_EN as U9303 turn-signal generating 1D8V_LDO_VGA, whe n 1D8V_LDO_VGA normal U9303 issued 1D8V_S0_VGA_PG. Thus significant independence and memory have all the required electricity generation. 1D5V_VGA_PWOK 1D8V_S0_VGA_PG PLT_RST # 3 set of high-level signal phase generat ed through U8301 VGA_RST # Finally there VGA_RST # Reset significant independence.

Вам также может понравиться

- Laptop Power Sequence Final by IntersotДокумент15 страницLaptop Power Sequence Final by IntersotHas BiansyahОценок пока нет

- Hasee HP500 Laptop SchematicsДокумент41 страницаHasee HP500 Laptop SchematicsbrunnofranklinОценок пока нет

- Akai TV2111Документ38 страницAkai TV2111hermogoОценок пока нет

- ADLTSДокумент5 страницADLTSSanju KulkarniОценок пока нет

- PanasonicДокумент57 страницPanasonicbmwboy2844Оценок пока нет

- PC Hardware Power Supply Cooling and ProtectionДокумент64 страницыPC Hardware Power Supply Cooling and ProtectionAbhijith MarathakamОценок пока нет

- SAMSUNG LCD Tecnología 3D - Mod UN65C8000XFXZAДокумент105 страницSAMSUNG LCD Tecnología 3D - Mod UN65C8000XFXZAAntonio DalioОценок пока нет

- Data Sheet TFS-764-HGДокумент36 страницData Sheet TFS-764-HGRumah Sakit Umum Daerah NoonganОценок пока нет

- BQ 25601Документ60 страницBQ 25601Epran SaputraОценок пока нет

- Optocoupler Solutions Guide PDFДокумент24 страницыOptocoupler Solutions Guide PDFBen Salah IssamОценок пока нет

- Pure Sine Invereter InfoДокумент107 страницPure Sine Invereter Infoolawale gbadeboОценок пока нет

- DSO Function GeneratorДокумент9 страницDSO Function GeneratorEdidjo DarwinОценок пока нет

- What Is North Bridge and South Bridge ArchitectureДокумент5 страницWhat Is North Bridge and South Bridge ArchitectureRejis SinnerОценок пока нет

- Laptop Level-1 Service Training - Course Syllabus: Tools and Testing EquipmentsДокумент12 страницLaptop Level-1 Service Training - Course Syllabus: Tools and Testing EquipmentsHari HargovindОценок пока нет

- Daewoo Dvd-p480 SMДокумент67 страницDaewoo Dvd-p480 SMfrewellОценок пока нет

- Coa - Lecture 3 - BNCДокумент5 страницCoa - Lecture 3 - BNCShizz denariОценок пока нет

- Atmega 32 U 4Документ433 страницыAtmega 32 U 4hummbumОценок пока нет

- SMD Resistor Examples (EIA-96 Code)Документ6 страницSMD Resistor Examples (EIA-96 Code)Rohit SainiОценок пока нет

- Linear or LDO Regulators & Step-Down Switching RegulatorsДокумент2 страницыLinear or LDO Regulators & Step-Down Switching Regulatorskasim leeОценок пока нет

- SCR Diac TriacДокумент7 страницSCR Diac TriacSubaskaran SalavanОценок пока нет

- TV Service TipsДокумент5 страницTV Service TipsAnil BpsОценок пока нет

- Design: IdeasДокумент6 страницDesign: IdeasSamantha EwingОценок пока нет

- Building A Soldering StationДокумент28 страницBuilding A Soldering StationDaniel Anton100% (1)

- Laptop Chip Level Repair Classroom Notes PDFДокумент108 страницLaptop Chip Level Repair Classroom Notes PDFLenin BabuОценок пока нет

- Triac PDFДокумент4 страницыTriac PDFgopu705204Оценок пока нет

- LCD TV Repair PDFДокумент44 страницыLCD TV Repair PDFQuinn QuinnОценок пока нет

- Power Semiconductor Devices and Thyristor FamilyДокумент11 страницPower Semiconductor Devices and Thyristor FamilyAzeez McОценок пока нет

- All About Logic Families PDFДокумент32 страницыAll About Logic Families PDFSaiKanthG100% (1)

- 30 LED ProjectsДокумент31 страница30 LED ProjectsVlatko KrstevskiОценок пока нет

- Introduction To Laptop Fix and DiagnosesДокумент51 страницаIntroduction To Laptop Fix and Diagnosesablacon64Оценок пока нет

- Kalimati, KTM, PH:01-4285805, 9849000843 Bagbazar, KTM, PH:01-4226887, 9851269099Документ19 страницKalimati, KTM, PH:01-4285805, 9849000843 Bagbazar, KTM, PH:01-4226887, 9851269099Řohan DhakalОценок пока нет

- Solar Controller and Inverter CatalogueДокумент10 страницSolar Controller and Inverter CatalogueAnonymous 4MLEo9TVQОценок пока нет

- Idoc - Pub - LCD Monitor Repair PDFДокумент26 страницIdoc - Pub - LCD Monitor Repair PDFElektroNiОценок пока нет

- Voltage-Supply (Voltage Display - LCD Panel) - TV Problems and Repair SolutionsДокумент4 страницыVoltage-Supply (Voltage Display - LCD Panel) - TV Problems and Repair SolutionsverОценок пока нет

- TroubleshootingДокумент45 страницTroubleshootingZoran ProkicОценок пока нет

- XO-1 Schematics PDFДокумент25 страницXO-1 Schematics PDFshibilvОценок пока нет

- Voltage Regulator Module Enterprise Voltage Regulator Down 11 1 Guidelines PDFДокумент62 страницыVoltage Regulator Module Enterprise Voltage Regulator Down 11 1 Guidelines PDFMario EstebanОценок пока нет

- Catalogue 2Документ30 страницCatalogue 2Radhakrishna YenuguОценок пока нет

- 3.1 Computer Hardware ComponentДокумент70 страниц3.1 Computer Hardware ComponentBiha RoseliОценок пока нет

- Luminous Inverter Catalogue 2020 PDFДокумент20 страницLuminous Inverter Catalogue 2020 PDFArjunОценок пока нет

- THYRISTORДокумент26 страницTHYRISTORLovely Jaze SalgadoОценок пока нет

- Laptop SIO Power-UpДокумент2 страницыLaptop SIO Power-Upbong bernalbongОценок пока нет

- Laptop Power SequencingДокумент14 страницLaptop Power SequencingOlivier Ouina100% (2)

- AN1585Документ17 страницAN1585DanОценок пока нет

- تشريح شاشة DELL D1025TMДокумент23 страницыتشريح شاشة DELL D1025TMzizo6636Оценок пока нет

- SequenceДокумент3 страницыSequencePRAMA PUTRAОценок пока нет

- Telwin 111 RepairДокумент20 страницTelwin 111 RepairKlavdija CankarОценок пока нет

- Asus H61 Common SequenceДокумент4 страницыAsus H61 Common SequencesachinОценок пока нет

- Chassis Z8 Manual de EntrenamientoДокумент47 страницChassis Z8 Manual de EntrenamientoLuis ColochoОценок пока нет

- Laptop Power SequenceДокумент2 страницыLaptop Power SequenceGabriel Meneses100% (1)

- Panasonic Service and Technology Company: Technical GuideДокумент98 страницPanasonic Service and Technology Company: Technical GuideJosé Luis Gordillo RubioОценок пока нет

- LP Rep v.2Документ3 страницыLP Rep v.2madumadawa rajapakshaОценок пока нет

- Kenwood Kdc-138 CR 139 S SMДокумент38 страницKenwood Kdc-138 CR 139 S SMdani37aigОценок пока нет

- Labgruppen FP3400 PWR SMДокумент60 страницLabgruppen FP3400 PWR SMDiego Alejandro Sepúlveda Vargas100% (2)

- Power On Detail Step With TimingДокумент15 страницPower On Detail Step With Timingz4rm4r100% (4)

- Motherboard Power Timing Knowledge AnalysisДокумент5 страницMotherboard Power Timing Knowledge Analysisabhilashvaman5542Оценок пока нет

- Voltage To Frequency ConverterДокумент7 страницVoltage To Frequency ConverterRodfer SorianoОценок пока нет

- Boot TimingДокумент11 страницBoot Timingabhilashvaman5542Оценок пока нет

- Power Sequences VariationДокумент2 страницыPower Sequences VariationLeth ComputerRepairОценок пока нет

- Switch Power Supply UC3842Документ3 страницыSwitch Power Supply UC3842mariaОценок пока нет

- A Fully Analog 5Gb/s Clock-and-Data Recovery Circuit in 90nm CMOSДокумент19 страницA Fully Analog 5Gb/s Clock-and-Data Recovery Circuit in 90nm CMOSJan SenОценок пока нет

- Application of DSP On Tms320c6713 DSKДокумент50 страницApplication of DSP On Tms320c6713 DSKRain VIIОценок пока нет

- NVIDIA QuestionsДокумент5 страницNVIDIA QuestionsJibin P John0% (1)

- Sigmadsp 28-/56-Bit Audio Processor With Two Adcs and Four Dacs Adau1701Документ56 страницSigmadsp 28-/56-Bit Audio Processor With Two Adcs and Four Dacs Adau1701Anthony HubbardОценок пока нет

- Ads 7870Документ43 страницыAds 7870Moorthy VenkatachalamОценок пока нет

- Casio CTK630 ServiceДокумент20 страницCasio CTK630 ServiceEduardo Arriagada MartinezОценок пока нет

- AMD Interview QuestionsДокумент4 страницыAMD Interview QuestionsRohit Somkuwar100% (1)

- Datasheet 18F4431Документ397 страницDatasheet 18F4431Tấn ĐạoОценок пока нет

- 5 Pen PC TechnologyДокумент44 страницы5 Pen PC TechnologyRajanshuman PradhanОценок пока нет

- A Peek Inside The ComputerДокумент36 страницA Peek Inside The ComputerMelvin Escopete0% (1)

- Bipolar Stepper Motor Driver 74194Документ12 страницBipolar Stepper Motor Driver 74194mekuannintmesfin100% (2)

- CD 40102 BДокумент13 страницCD 40102 BPradeepa SenanayakeОценок пока нет

- Mealy and Moore Sequential CircuitsДокумент12 страницMealy and Moore Sequential CircuitsSangameshwer EnterprisesОценок пока нет

- Flip Flop MultivibratorДокумент161 страницаFlip Flop MultivibratorMuhammad Rizani RusliОценок пока нет

- Pioneer VSX D307 Audio Video Receiver Service ManualДокумент56 страницPioneer VSX D307 Audio Video Receiver Service ManualRuben NavaОценок пока нет

- Timesource 2500Документ203 страницыTimesource 2500Sebastian JoehnkОценок пока нет

- S1200 HSCДокумент10 страницS1200 HSCMd. Tauhidul IslamОценок пока нет

- OCC CIS 1100 Test 1 CH 1,2,3 ReviewДокумент12 страницOCC CIS 1100 Test 1 CH 1,2,3 ReviewFab Five Certified TutorsОценок пока нет

- Theory of Operation PDFДокумент46 страницTheory of Operation PDFSv KoОценок пока нет

- Kenwood KRF v5200d S SMДокумент40 страницKenwood KRF v5200d S SMpriyanthaОценок пока нет

- MX 25 L 12845 EmiДокумент74 страницыMX 25 L 12845 Emirazali1982Оценок пока нет

- IT Short CourceДокумент16 страницIT Short CourceAdmin CvmrmptОценок пока нет

- Heidenhain Doku Endat 383 942 23 15077 PDFДокумент20 страницHeidenhain Doku Endat 383 942 23 15077 PDFmario escottoОценок пока нет

- F MC-16L MB90670/675 Series: 16-Bit Proprietary MicrocontrollerДокумент106 страницF MC-16L MB90670/675 Series: 16-Bit Proprietary MicrocontrollerDavid MendezОценок пока нет

- MC74HC589A 8-Bit Serial or Parallel-Input/Serial-Output Shift Register With 3-State OutputДокумент12 страницMC74HC589A 8-Bit Serial or Parallel-Input/Serial-Output Shift Register With 3-State OutputViviana AlbornozОценок пока нет

- Wind Band Radar Signal Using RF2051Документ8 страницWind Band Radar Signal Using RF2051Khushal KharadeОценок пока нет

- KeyboardДокумент18 страницKeyboardapi-3721578Оценок пока нет

- The Integrating A/D Converter (ICL7135) : Application Note February 1999Документ5 страницThe Integrating A/D Converter (ICL7135) : Application Note February 1999ytnateОценок пока нет

- Lecture 06 - Digital Vlsi DesignДокумент30 страницLecture 06 - Digital Vlsi Designjoao5000Оценок пока нет

- Pin Diagram of 8086, MIN Mode - MAX ModeДокумент10 страницPin Diagram of 8086, MIN Mode - MAX Modenskprasad89Оценок пока нет

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsОт EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsРейтинг: 5 из 5 звезд5/5 (3)

- Chip War: The Fight for the World's Most Critical TechnologyОт EverandChip War: The Fight for the World's Most Critical TechnologyРейтинг: 4.5 из 5 звезд4.5/5 (82)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyОт EverandChip War: The Quest to Dominate the World's Most Critical TechnologyРейтинг: 4.5 из 5 звезд4.5/5 (229)

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)От EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Рейтинг: 5 из 5 звезд5/5 (2)

- Electrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tОт EverandElectrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tРейтинг: 4.5 из 5 звезд4.5/5 (27)

- The Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceОт EverandThe Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceОценок пока нет

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonОт EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonРейтинг: 5 из 5 звезд5/5 (2)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionОт EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionРейтинг: 4.5 из 5 звезд4.5/5 (543)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]От EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Рейтинг: 5 из 5 звезд5/5 (3)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102От EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Рейтинг: 5 из 5 звезд5/5 (2)

- INCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesОт EverandINCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesРейтинг: 5 из 5 звезд5/5 (1)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002От EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Рейтинг: 5 из 5 звезд5/5 (1)

- Multiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...От EverandMultiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...Оценок пока нет

- Retro Gaming with Raspberry Pi: Nearly 200 Pages of Video Game ProjectsОт EverandRetro Gaming with Raspberry Pi: Nearly 200 Pages of Video Game ProjectsОценок пока нет

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeОт EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeРейтинг: 4.5 из 5 звезд4.5/5 (10)

- Cyber-Physical Systems: Foundations, Principles and ApplicationsОт EverandCyber-Physical Systems: Foundations, Principles and ApplicationsHoubing H. SongОценок пока нет

- Digital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosОт EverandDigital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosРейтинг: 5 из 5 звезд5/5 (1)

- 2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersОт Everand2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersРейтинг: 5 из 5 звезд5/5 (1)

- Hacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsОт EverandHacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsРейтинг: 3.5 из 5 звезд3.5/5 (2)

- Power System Control and ProtectionОт EverandPower System Control and ProtectionB. Don RussellРейтинг: 4 из 5 звезд4/5 (11)

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1715193157?v=1)