Академический Документы

Профессиональный Документы

Культура Документы

Papers On DC To DC Converter

Загружено:

dineshpeterОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Papers On DC To DC Converter

Загружено:

dineshpeterАвторское право:

Доступные форматы

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO.

7, JULY 2013 3363

Analysis, Design, and Performance Evaluations of

an Edge-Resonant Switched Capacitor Cell-Assisted

Soft-Switching PWM Boost DCDC Converter and

Its Interleaved Topology

Tomokazu Mishima, Member, IEEE, Yujiro Takeuchi, and Mutsuo Nakaoka, Member, IEEE

AbstractThis paper presents a soft-switching pulsewidth mod-

ulation (PWM) nonisolated boost dcdc converter embedding

an edge-resonant switched capacitor (ER-SWC) cell and its

interleaved circuit topology. The conceptual boost dcdc con-

verter treated herein can achieve high-frequency zero-current

soft-switching turn-on and zero-voltage soft-switching turn-off

operations in the active switches and minimization of a reverse

recovering current in the freewheeling diode under discontinuous

conduction mode partially including critical conduction mode in

the input current. Those advantageous properties enable a wide

range of soft-switching operations together with a high-voltage

step-up conversion ratio with a reduced current stress. Circuit

design guideline based on the soft-switching range is introduced;

then, a theoretical analysis is carried out for investigating the step-

up voltage conversion ratio. For demonstrating the effectiveness of

the ER-SWC soft-switching PWM boost dcdc converter and its

newly developed interleaved topology, laboratory prototypes are

evaluated in experiments; then, their performances are discussed

from a practical point of view.

Index TermsBoost dcdc converter, discontinuous con-

duction mode (DCM), edge resonance, pulsewidth modula-

tion (PWM), soft-switching, switched capacitor, zero-current

soft-switching (ZCS), zero-voltage soft-switching (ZVS).

I. INTRODUCTION

P

ULSEWIDTH modulation (PWM) boost dcdc convert-

ers have been gathering much attention in a variety of

practical power conditioning systems for telecommunication,

renewable energy, and distributed power generations as well as

switching-mode rectiers [1][16]. For minimizing the size and

weight as well as the power dissipation, the substantial reduc-

tion of switching losses is required in a conventional PWMboost

dcdc converter.

Manuscript received June 13, 2012; revised September 3, 2012; accepted

October 13, 2012. Date of current version December 24, 2012. Recommended

for publication by Associate Editor J. A. Cobos.

T. Mishima and Y. Takeuchi are with the Mechatronics Engineering Division,

Graduate School of Maritime Science, Kobe University, Hyogo 658-0022, Japan

(e-mail: mishima@maritime.kobe-u.ac.jp).

M. Nakaoka is with the Electric Energy Saving Research Center, Kyungnam

University, Masan 630-701, Republic of Korea.

Color versions of one or more of the gures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identier 10.1109/TPEL.2012.2227504

By adopting a discontinuous conduction mode (DCM)

scheme, the conventional PWM boost dcdc converter can at-

tain the soft commutation naturally at the turn-on of the active

switch and zero-current soft-switching (ZCS) turn-off of the

freewheeling diode in the wide range of load variation without

any additional circuit component. Those advantages lead to the

simplicity in the main circuit conguration and the control sys-

tems because there is no need to detect the dc input current for

maintaining the continuous current. In addition, the dc voltage

conversion ratio of the conventional PWM boost dcdc con-

verter in DCM is higher than in continuous conduction mode

(CCM) [1], [17].

However, there exists an inherent technical issue in the DCM

scheme: the current stress in the power devices and components

as well as in the input smoothing capacitor is larger than that

of the PWM boost dcdc converter in CCM; consequently, the

conduction losses signicantly affect the conversion efciency.

Hence, the applicability of the PWM boost dcdc converter in

DCM is currently limited to 100300 W class switching power

converters such as power factor correction converters [14], [18],

[19].

As a solution to overcoming the drawbacks of the PWMboost

dcdc converter in DCM, employment of the edge-resonant

switched capacitor (ER-SWC) cell as shown in Fig. 1 is one of

the effective techniques due to its high efciency and high scal-

ability characteristics. In the soft-switching PWM boost dcdc

converter with the ER-SWC cell, a wide range of soft-switching

operations can be achieved under the condition of DCM/critical

conduction mode (CRM) in the input dc current without any

circulating current, while the current stresses in the power de-

vices and the passive components can also be mitigated owing

to the edge resonance within the switching cell. In addition,

the ER-SWC soft-switching PWM boost dcdc converter can

be usefully extended for the interleaved circuit topology, effec-

tively canceling the input current ripple and reducing the size of

the input inductor and the output capacitor as well as increasing

the power rating. Actually, the validity of the interleaved boost

dcdc converter in DCM has been stated by evaluating a 20-kW

boost dcdc converter prototype in [20].

A similar type of the switching cell has been developed as

the turn-off commutation circuit for GTO in a high-power con-

verter applied for a high-voltage dc transmission [21]. Besides

that, the several applications of the ER-SWC cell into the PWM

0885-8993/$31.00 2012 IEEE

3364 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 7, JULY 2013

r C r C

Cr

Cr

S1 S1

S2

S2

D1

D2

S2

S2

S1

S1

D2

D2

D2

D1

D1

D1

r L r L

r L r L

] 2 e p y T [ ] 1 e p y T [

] 4 e p y T [ ] 3 e p y T [

Fig. 1. Circuit topological family of ER-SWC cells.

converters have been reported in the relevant previous stud-

ies [22], [23]. However, no previous work reports the detailed

discussion on performances of the ER-SWC cell in the PWM

boost dcdc converter from the viewpoints of a soft-switching

operation and a voltage conversion ratio.

The main objective of this paper is to practically evaluate

the effectiveness of the ER-SWC soft-switching PWM boost

dcdc converter in DCM and its interleaved circuit topology by

demonstrating the switching performances, voltage conversion

ratio, steady-state output power regulation characteristics, and

conversion efciency as well as the soft-switching achievable

range in experiments. Moreover, the design procedure for the

circuit parameters in the ER-SWC cell is originally introduced

and its validity is actually proven by the experiment results.

This paper is organized as follows. In the rst place, the

circuit conguration and operation principle of the ER-SWC

soft-switching PWM boost dcdc converter are described in

Section II. Then, the converter steady-state characteristics re-

garding the step-up voltage conversion ratio are demonstrated

by a theoretical analysis in Section III. The circuit design guide-

line of the ER-SWC soft-switching PWM boost dcdc con-

verter is described in Section IV, and the wide-range soft-

switching operations attained in the ER-SWC soft-switching

PWM boost dcdc converter are explained in Section V. Fur-

thermore, its practical effectiveness and feasibility are evalu-

ated and discussed in experiments with the laboratory proto-

types both of the single- and two-phase (interleaved) circuits in

Section VI.

II. CIRCUIT CONFIGURATION AND OPERATION PRINCIPLE

A. Circuit Description

The circuit conguration of the ER-SWC soft-switching

PWM boost dcdc converter in DCM is illustrated in Fig. 2.

+

L

r

V

in

D

1

D

2

S

1

S

2

C

r

R

o

C

o

D

o

V

o

Fig. 2. ER-SWC cell-assisted soft-switching PWM boost dcdc converter

operating under DCM/CRM condition.

The ER-SWC cell consists of two active switches S

1

, S

2

, two

diodes D

1

, D

2

, a resonant capacitor C

r

, and a resonant inductor

L

r

.

The key advantages of the ER-SWC soft-switching PWM

boost dcdc converter are summarized as follows:

1) the ER-SWC cell has high scalability and extensibility

due to its simple and exible circuit conguration (con-

gurable by a CMOS structure as well as an H-bridge

module);

2) a current-sharing technique for the input dc current is

available by S

1

and S

2

, which is effective especially for

power conversions with a large input current;

3) the peak current in the input inductor can be reduced by

the effect of edge resonance of L

r

C

r

as compared with

the conventional PWM boost dcdc converter in DCM;

4) no idling and circulating current inherent to soft-switching

power converters appears in the ER-SWC cell;

5) higher step-up voltage conversion ratio with a smaller peak

current can be attained than the conventional boost dcdc

converter;

6) characteristics on the voltage conversion ratio are linear

with respect to the duty cycle of PWM, so the output volt-

age controller can be implemented by a simple schematic

conguration;

7) the gate signal for S

1

and S

2

can be common, so the gate

drive circuits are simple and low power consuming.

In contrast, there are some drawbacks recognizable in the

family of ER-SWC cell:

1) the voltage stress in the output freewheeling diode D

o

is theoretically twice as large as the conventional PWM

boost dcdc converter;

2) conduction losses increase in the auxiliary diodes D

1

for

Type 2, D

2

for Type 3, and D

1

and D

2

for Type 4 of

Fig. 1, while ZCS turn-off commutations are achievable

in D

1

and D

2

for all the types.

It should be noted that the ER-SWC soft-switching PWM

boost dcdc converter with the DCM scheme can be extended

for its CCM circuit, as shown in Fig. 5.

Another type of an H-bridge-based soft-switching cell that

has duality for the ER-SWC cell as shown in Fig. 6 has been

proposed in [8]. This cell contains a circulating current with

the cell; thereby, the relevant power losses under the heavy-load

condition would affect the conversion efciency. In contrast, the

MISHIMA et al.: ANALYSIS, DESIGN, AND PERFORMANCE EVALUATIONS 3365

0

0

0

0

0

0

0

1 2 3 4 5

t

0

t

1

t

2

t

3

t

4

t

5

S

1

, S

2

T

OFF

i

S1

, i

S2

v

S1

, v

S2

V

o

(V

o

+V

in

)/2

v

D1

, v

D2

i

D1

, i

D2

V

o

(V

o

-V

in

)/2

v

Cr

i

Cr

V

o

v

Lr

i

Lr

V

in

+V

o

V

in

V

in

-V

o

v

Do

i

Do

2V

o

V

o V

o

-V

in

i

ab

v

ab

-V

o

V

o

V

in

T

0

ON

T

(=DT )

Mode

Fig. 3. Relevant voltage and current waveforms of ER-SWC soft-switching

PWM boost dcdc converter in DCM/CRM.

ER-SWC cell discussed herein has no operating mode for the

circulating current; therefore, a higher efciency power conver-

sion can be expected under the heavy-load condition.

B. Operation Principle

The theoretical operating waveforms of the ER-SWC soft-

switching PWM boost dcdc converter are provided in Fig. 3,

and the corresponding mode transitions with the simplied

equivalent circuits are shown in Fig. 4. The circuit operation

during one switching cycle is divided into the ve submodes, as

described in the following.

1) Mode 1 [t

0

t < t

1

], S

1

, S

2

ZCS turn-on mode: The

inductor current i

Lr

is zero, and the active switches S

1

and S

2

are simultaneously turned ON at t

0

. Then, i

Lr

and

the switch currents i

s1

and i

s2

rise gradually from the

zero initial value with the edge resonance by L

r

and C

r

.

+

[Mode 1]

[Mode 2] [Mode 3] [Mode 4]

[Mode 5]

DCM

CRM

Fig. 4. Mode transitions and equivalent circuits during one switching cycle in

DCM/CRM.

Lr

S

1

S2

D

1

D

2

C

r

Do

Co

L

d

Ro

+

-

V

in Vo

Fig. 5. ER-SWC soft-switching PWM boost dcdc converter operating in

CCM.

L

r

D

2

C

r

D

o

C

o

L

d

S

1

S

2

D

1

+

-

Ro

V

in

Vo

Fig. 6. Soft-switching PWM boost dcdc converter in the topological duality

for ER-SWC [8].

Thereby, ZCS turn-on commutation can be achieved in S

1

and S

2

.

During this mode, i

Lr

is written as

i

L

r

(t) =

V

in

+V

o

Z

sin (

r

t t

0

) (1)

where Z =

_

L

r

/C

r

and

r

= 1 /

L

r

C

r

.

The resonant capacitor C

r

is discharged by i

L

r

in this

interval.

3366 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 7, JULY 2013

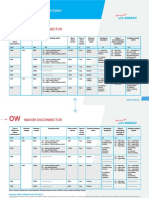

TABLE I

VOLTAGE STRESSES AND SWITCHING TRANSITIONS IN POWER DEVICES FOR EACH ER-SWC CELL

Switch S

1

(turn-on / off) S

2

(turn-on / off) D

1

(turn-on) D

2

(turn-on) D

o

(turn-on&off)

Type 1 V

o

(ZCS/ ZVS) V

o

(ZCS/ ZVS) V

o

V

o

2V

o

(ZCS)

Type 2 V

o

(ZCS/ ZVS) V

o

(ZCS/ ZVS) V

o

(ZCS) V

o

2V

o

(ZCS)

Type 3 V

o

(ZCS/ ZVS) V

o

(ZCS/ ZVS) V

o

V

o

(ZCS) 2V

o

(ZCS)

Type 4 V

o

(ZCS/ ZVS) V

o

(ZCS/ ZVS) V

o

(ZCS) V

o

(ZCS) 2V

o

(ZCS)

2) Mode 2 [t

1

t < t

2

], inductive energy storing mode:

The resonant capacitor C

r

is completely discharged at

t

1

; then, the diodes D

1

and D

2

are forward-biased. The

beginning time t

1

of this submode and its inductor current

I

Lr1

can be determined from (1) as

t

1

= t

0

+

1

r

cos

1

_

V

in

V

in

+V

o

_

(2)

I

L

r 1

= i

L

r

(t

1

) =

_

V

o

(2V

in

+V

o

)

Z

. (3)

During this interval, i

Lr

rises linearly as expressed by

i

L

r

(t) =

V

in

L

r

(t t

1

) +I

L

r 1

. (4)

The inductor current i

Lr

is equally shared by the two

branches S

1

D

1

and S

2

D

2

.

3) Mode 3 [t

2

t < t

3

], S

1

, S

2

ZVS turn-off mode: The

two active switches S

1

and S

2

are turned OFF simulta-

neously at t

2

. Then, the edge resonance begins again in

the ER-SWC cell, and the voltages across S

1

and S

2

in-

crease gradually by the effect of C

r

. Thereby, ZVSturn-off

commutation can be achieved in S

1

and S

2

. The inductor

current I

Lr2

at t

2

can be dened from (4) as

I

L

r 2

= i

L

r

(t

2

) =

V

in

L

r

(t

2

t

1

) +I

L

r 1

(5)

where t

2

= t

0

+DT and D denotes the duty cycle of S

1

and S

2

as dened by

D

T

on

T

. (6)

During this mode, i

Lr

is dened by

i

L

r

(t) = I

max

sin

_

r

(t t

2

) + tan

1

_

ZI

L

r 2

V

in

_

_

(7)

where I

max

represents the peak value of i

Lr

, as expressed

by

I

max

=

_

I

L

r 2

2

+

_

V

in

Z

_

2

. (8)

This operation mode continues until the capacitor voltage

v

cr

equals the output voltage V

o

at t

3

.

4) Mode 4 [t

3

t < t

4

], inductor energy releasing mode:

The resonant capacitor voltage v

cr

rises up to the output

voltage at t

3

; then, the conduction interval of D

1

and D

2

is

terminated. The beginning time t

3

of this submode and the

corresponding inductor current I

L

r 3

can be dened from

(7) as

t

3

= t

2

+

1

r

_

sin

1

_

V

o

V

in

ZI

max

_

+ tan

1

_

V

in

ZI

L

r

2

_

_

(9)

I

L

r 3

= i

L

r

(t

3

) =

_

I

max

2

_

V

o

V

in

Z

_

2

. (10)

The inductor current i

Lr

is forward to the load via D

o

,

and thereby, the input voltage V

in

is boosted to the output

voltage V

o

. During this interval, i

Lr

is expressed by

i

L

r

(t) =

V

in

V

o

L

r

(t t

3

) +I

L

r 3

. (11)

The inductor current i

Lr

gradually decreases and naturally

reaches to the zero level at t

4

. Accordingly, occurrence of

the reverse recovering current in the output freewheeling

diode D

o

can be mitigated.

5) Mode 5 [t

4

t < t

5

], inductor current discontinuous

mode: Inductor current i

Lr

reduces to zero level after

t

4

, which is determined from (11) by

t

4

= t

3

+

L

r

I

L

r 3

V

o

V

in

. (12)

The load current ows through the output capacitor C

o

in this submode; then, the inductor current keeps the zero

level until the next switching cycle starts at t

5

.

According to the circuit topologies in Fig. 1, the theoreti-

cal voltage stresses and commutations of the switching power

devices in the ER-SWC soft-switching PWM boost dcdc con-

verters are summarized in Table I. The two diodes D

1

and D

2

can be turned OFF under ZCS conditions when they are inserted

in series with the positive and negative dc bus lines as depicted

in Type 2-4, by paying for increase of the conduction power

losses.

All of the topological family of the ER-SWC cells in Fig. 1

can be applied to the six nonisolated PWM dcdc converters

(Buck, Boost, BuckBoost,

Cuk, SEPIC, and Zeta), as shown

in Fig. 7.

III. ANALYSIS OF VOLTAGE CONVERSION RATIO

A. Derivation of Voltage Conversion Ratio

The inductor current and voltage waveforms of the ER-SWC

soft-switching PWM boost dcdc converter are illustrated and

compared with those of the conventional hard-switching PWM

boost dcdc converter in DCM under the condition of the same

duty cycle in Fig. 8. The positive voltagesecond area S

A

in

MISHIMA et al.: ANALYSIS, DESIGN, AND PERFORMANCE EVALUATIONS 3367

(a) (b)

(c) (d)

(e) (f)

Fig. 7. Six nonisolated ZCS-PWM dcdc converters with ER-SWC cell:

(a) Buck. (b) Boost. (c) Buckboost. (d)

Cuk. (e) SEPIC. (f) Zeta.

0

t

3

V

in

-V

o

0

V

in

V

in

+V

o

t

1

ER-SWC

Conventional type

T

r1

T

r2 SA

SB

ER-SWC

Conventional type

v

Lr

i

Lr

ILr1

ILr2

ILr3

= 0

t

0

= DT

t

2 = D'T

t

4

= T

t

5

I II III IV

Fig. 8. Current and voltage waveforms of input inductor L

r

in DCM of

conventional and ER-SWC boost dcdc converters under the same duty cycle

condition.

Fig. 8, which derives from the edge resonance in the ER-SWC

cell, produces the negative voltagesecond area S

B

in Fig. 8.

As a result, the negative amplitude of v

Lr

in Fig. 8 is extended

much more than that of the conventional type, then a larger

output voltage V

O

, i.e., higher voltage conversion ratio can be

obtained in the ER-SWC boost dcdc converter.

The voltage conversion ratio (M = V

o

/V

in

) of the ER-SWC

boost dcdc converter in DCMcan be determined fromthe input

and output power balance [24].

By assuming the time origin t

o

= 0 in Fig. 8 for simplicity,

the time integrations of the inductor current i

Lr

in each submode

are dened by

I : S

1

=

_

t

1

0

i

Lr

dt = C

r

V

o

(13)

II : S

2

=

_

t

2

t

1

i

Lr

dt

=

V

in

2L

r

(DT t

1

)

2

+I

Lr1

(DT t

1

) (14)

III : S

3

=

_

t

3

t

2

i

Lr

dt = C

r

V

o

(15)

IV: S

4

=

_

t

4

t

3

i

Lr

dt =

L

r

I

Lr3

2

2(V

o

V

in

)

(16)

V: S

5

=

_

T

t

4

i

Lr

dt = 0. (17)

Therefore, the average input current i

Lr

can be obtained by

i

Lr

=

1

T

_

T

0

i

Lr

dt =

1

T

5

k=1

S

k

. (18)

Neglecting the power losses in the ER-SWC boost dcdc con-

verter, the power balances between the dc power source V

in

and

the load R

o

can be established as

V

in

i

Lr

=

V

o

2

R

o

. (19)

The input power V

in

i

Lr

can be expressed from (13)(18) as

V

in

i

Lr

=

V

in

V

o

T(V

o

V

in

)

_

V

in

2L

r

(D

2

T)

2

+I

Lr1

D

2

T + 2C

r

V

o

_

(20)

where D

2

T = t

2

t

1

. Furthermore, deformation of (19) with

(20) yields the equation regarding the voltage conversion ratio

M as

M

2

(1 + 2C

r

R

o

f

s

)M

R

o

f

s

Z

r

D

2

T

_

_

M

2

+ 2M

r

2

D

2

T

_

= 0. (21)

Equation (21) is the implicit function for V

in

and V

o

, so that

it is reasonable to analyze the voltage conversion ratio M by

computer-aided calculations.

Comparisons of the voltage conversion ratios between the

conventional and ER-SWC boost dcdc converters are depicted

by means of the computer calculations in Fig. 9. It can be un-

derstood from Fig. 9 that the higher step-up voltage conversion

ratio can be attained in the ER-SWC boost dcdc converter than

the conventional one. Note here that the two crossing points

between the CCM and DCM curves of the conventional boost

dcdc converter indicate its CRM points.

The simplied dc voltage transfer functions based on a linear

approximation of the voltage waveform across L

r

in the con-

ventional and ER-SWC boost dcdc converters are indicated in

Table II.

B. Duty Cycle and Current Stress Reductions

Fig. 10(a) depicts the calculation values of the normal-

ized input inductor currents in DCM for the conventional and

3368 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 7, JULY 2013

0

1

2

3

4

5

6

7

8

9

10

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

V

o

l

t

a

g

e

C

o

n

v

e

r

s

i

o

n

R

a

t

i

o

M

Duty Cycle D

ER-SWC: C

r

= 100 [nF]

ER-SWC: C

r

= 56 [nF]

ER-SWC: C

r

= 15 [nF]

Conventional type in DCM

Conventional type in CCM

DCM

CCM

Fig. 9. Calculated voltage conversion ratios of the conventional and

ER-SWC boost dcdc convertersexample circuit parameters: L

r

= 20 H,

R

o

= 80 , and switching frequency f

s

= 40 kHz.

TABLE II

DC VOLTAGE TRANSFER FUNCTIONS OF CONVENTIONAL AND ER-SWC BOOST

DCDC CONVERTERS

Conventional Circuit

CCM

1

1D

DCM

1

2

1 + 1 +

2D

2

R

o

T

L

d

ER SWC Circuit (linear approximation)

DCM/ CRM 1

1

D

{D +

T

r1

+T

r2

2T

}

1

ER-SWC boost dcdc converters under the identical conditions

of P

o

= 1 kW, M = V

o

/V

in

= 200/100 = 2, C

r

= 100 nF,

L

r

= 47 H, input inductor of the conventional boost dc

dc converter L

d

= 47 H, switching frequency f

s

= 1/T =

40 kHz, and the peak inductor current I

Lp

= 23 A. The duty

cycle D

conv

of the conventional boost dcdc converter in DCM

can be obtained by

D

conv

=

L

r

I

Lp

V

in

T

= 0.43 . (22)

The duty cycle D

ERSWC

of the ER-SWC boost dcdc converter

can be determined from (3) and (5) as

D

ERSWC

=

L

r

V

in

T

_

I

Lp

V

o

(2V

in

+V

o

)C

r

L

r

_

= 0.29 (23)

where one sets the origin t

o

= 0 for simplicity. As a result, it

can be understood here that the duty cycle of the active switches

S

1

and S

2

shifts into the smaller range in the ER-SWC boost

dcdc converter than the conventional one, which is benecial

for further reduction of conduction losses in the switching power

devices.

The normalized input inductor currents in DCM are com-

pared between the conventional and ER-SWC boost dcdc

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

N

o

r

m

a

l

i

z

e

d

I

n

d

u

c

t

o

r

C

u

r

r

e

n

Duty Cycle D

ER-SWC

Conventional type (DCM)

DERSWC

Dconv

Lr = 47 H

Ld = 47 H

(a)

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

N

o

r

m

a

l

i

z

e

d

I

n

d

u

c

t

o

r

C

u

r

r

e

n

t

Duty Cycle D

ER-SWC

Conventional type (DCM)

Lr = 47 H

Ld = 22 H

I LpERSWC

I Lpconv

(b)

Fig. 10. Comparison of input inductor currents between conventional and

ER-SWC boost dcdc converters in DCM (a) under the same condition of P

o

,

M, and L

r

, and (b) under the same condition of P

o

, M, and D.

converters in Fig. 10(b) under the identical conditions of

P

o

= 1 kW, M = V

o

/V

in

= 200/100 = 2, C

r

= 100 nF, f

s

=

1/T = 40 kHz, and D = 0.29. The input inductor L

d

of the

conventional boost dcdc converter in DCM can be calculated

from the dc voltage transfer function in Table II as

L

d

=

2R

o

D

2

T

(2M 1)

2

1

= 22 H (24)

while L

r

in the ER-SWC boost dcdc converter remains to be

47 H. Accordingly, the inductor peak current I

Lp

c o nv

of the

conventional boost dcdc converter in DCM is determined by

I

Lp

c o nv

=

V

in

DT

L

d

= 33 A. (25)

On the other hand, the inductor peak current I

Lp

E R S W C

of the

ER-SWCboost dcdc converter is determined from(2), (3), and

MISHIMA et al.: ANALYSIS, DESIGN, AND PERFORMANCE EVALUATIONS 3369

G

a

t

e

P

u

l

s

e

C

u

r

r

e

n

t

o

f

t

h

e

I

n

d

u

c

t

o

r

i

L

r

0 D

min

T D

max

T T

C

u

r

r

e

n

t

o

f

t

h

e

S

w

i

t

c

h

e

s

S

1

,

S

2

Time t

Terminal curve B: Complete S-SW limiting point

B A

A

B

ON

ON

A B

(Po,min)

(Po,max)

Terminal curve A: CRM point

Fig. 11. Variations of inductor current i

Lr

with duty cycle control.

0

0

0 DT T

v

Cr

v

S1

, v

S2

i

S1

, i

S2

Residual Voltage

Semi-ZVS

(a)

0

0

0 DT T

i

Lr

v

S1

, v

S2

i

S1

, i

S2

I

min

Semi-ZCS

(b)

Fig. 12. Voltage and current waveforms for semi-soft-switching in S

1

and S

2

.

(a) Semi-ZVS turn-off in S

1

and S

2

. (b) Semi-ZCS turn-on in S

1

and S

2

.

(5) by

I

Lp

E R S W C

=

V

in

L

r

_

DT

1

r

cos

1

_

V

in

V

in

+V

o

_

_

+

V

o

(2V

in

+V

o

)C

r

L

r

= 23 A (26)

d

v

/

d

t

[

k

V

/

s

]

O

u

t

p

u

t

P

o

w

e

r

P

o

[

k

W

]

Resonant Capacitor C

r

[nF]

dv/dt

P

o,max

P

o,min

0

0.5

1

1.5

2

100 200 300

0

0.5

1

1.5

Output power range

Fig. 13. Output power and voltage rising rates depending on resonant capacitor

C

r

: P

o

= 1 kW.

0

5

10

15

20

25

0 5 10 15 20 25

I

n

d

u

c

t

o

r

C

u

r

r

e

n

t

i

L

r

[

A

]

Time t [s]

P

o

= 200 [W]

V

o

= 200 [V]

C

r

= 62.5 [nF]

L

r

= 10, 15, 22, 33, 47, 68,

H]

L

r,max

= 445 [H]

10 [H]

330 [H] 445 [H]

(a)

0

10

20

30

40

50

60

0 5 10 15 20 25

I

n

d

u

c

t

o

r

C

u

r

r

e

n

t

i

L

r

[

A

]

Time t [s]

P

o

= 1 [kW]

V

o

= 200 [V]

C

r

= 62.5 [nF]

L

r

= 10, 15, 22, 33, 47, 68,

H]

100 [H]

68 [H]

10 [H]

(b)

Fig. 14. Variations of inductor current i

Lr

for minimumand maximumoutput

power settings: (a) P

o

= P

o, min

= 200 W, and (b) P

o

= P

o, max

= 1 kW.

3370 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 7, JULY 2013

Isolation amplifier and voltage limiter

Micro computer-based digital PI controller

Gate Drivers

Fig. 15. Schematic diagram of experimental circuit with output voltage regulation closed-loop control.

TABLE III

CIRCUIT PARAMETERS AND SPECIFICATION OF PROTOTYPE

Parameter Value [unit]

Power rating, P

o

1 [kW]

Input voltage, V

in

18 150 [V]

Output voltage, V

o

200 [V]

Resonant inductor, L

r

74 [H]

Resonant capacitor, C

r

56 [nF]

Variable load resistor, R

o

80 400 []

Output side smoothing capacitor, C

o

1000 [F]

Switching frequency, f

s

40 [kHz]

where one sets the origin t

o

= 0 for simplicity. This compari-

son shows that the peak current can be effectively reduced in the

ER-SWC boost dcdc converter as compared with the conven-

tional one.

IV. DESIGN GUIDELINE OF CIRCUIT PARAMETERS

The circuit parameters of L

r

and C

r

in the ER-SWC cell

should be based on both of the maximum output power P

o,max

with the maximum duty cycle D

max

and the minimum output

power P

o,min

with the minimum duty cycle D

min

[25].

Fig. 11 illustrates the variations of the inductor current i

Lr

and the switching currents i

S1

and i

S2

in accordance with the

output power, where the terminal curve A corresponds with

P

o

= P

o,max

, while the terminal curve B is in the case of

P

o

= P

o,min

. Note here that the complete soft-switching area is

dened in the output power range between P

o,min

and P

o,max

.

In addition to the determination of the zero crossing time of

i

Lr

, t

4

= D

max

T, the maximum output power P

o,max

can be

expressed as

P

o,max

= V

in

i

Lr,max

(27)

where i

Lr

represents the average current of i

Lr

at P

o

= P

o,max

and this value can be obtained from (1), (4), (7), and (11); then,

i

Lr,max

means its maximum value.

On the other hand, the zero crossing time t

4,min

of i

Lr

in the

case of P

o

= P

o,min

can be described as

t

4,min

=

1

r

_

sin

1

_

M 1

M + 1

_

+

2

M

M 1

+

2

_

. (28)

Then, the minimum output power P

o,min

can be given by

P

o,min

= V

in

i

Lr,min

=

2C

r

V

in

V

o

T

_

1 +

V

in

V

o

V

in

_

(29)

where i

Lr,min

denotes the minimum value of the resonant in-

ductor average current i

Lr

.

Equation (29) indicates that P

o,min

is independent of the pa-

rameter L

r

; accordingly, the parameter C

r

can be derived from

(29). Deformation of (29) yields the parameter of the resonant

MISHIMA et al.: ANALYSIS, DESIGN, AND PERFORMANCE EVALUATIONS 3371

Fig. 16. Measured voltage and current waveforms: (a) resonant inductor L

r

(100 V/div, 10 A/div), (b) active switch S

1

(100 V/div, 10 A/div), (c) auxiliary

diode D

1

(100 V/div, 10 A/div), and (d) freewheeling diode D

o

(200 V/div, 10 A/div).

capacitor C

r

as expressed by

C

r

=

(V

o

/V

in

1)P

o, min

2f

s

V

2

o

. (30)

The capacitance C

r

is related to a voltage rising rate (dv/dt)

of S

1

and S

2

at the turn-off transitions, and this index be-

comes maximum at P

o

= P

o,max

. The tradeoff relationship ex-

ists between the controllable output power area and the soft-

switching range. Lowering the setting value of P

o,min

by select-

ing a smaller capacitance for C

r

yields the wider output power

range under the soft-switching condition. In contrast to that, the

smaller the capacitance of C

r

, the larger the dv/dt rate, which

results in increase of the turn-off transitional power losses in S

1

and S

2

.

In order to achieve the soft-switching commutation, t

4,min

should be smaller than the one switching interval T. Therefore,

the parameter of L

r

should meet the condition indicated as

follows:

L

r

< 1

_

C

r

f

s

2

_

sin

1

_

M 1

M + 1

_

+

2

M

M 1

+

2

_

2

. (31)

At the same time, the maximum zero crossing time t

4,max

for

i

Lr

should be determined under the condition expressed by

t

4,min

< t

4,max

T. (32)

V. SOFT-SWITCHING RANGE

The ER-SWC soft-switching boost dcdc converter is con-

trolled by PWM, accordingly the duty cycle D of the active

switches as expressed by (6) varies in accordance with the out-

put power P

o

.

As P

o

decreases, D also decreases and the turn-on time inter-

val of S

1

and S

2

is shorten. When D < D

min

, i.e., P

o

< P

o,min

,

the voltage of the resonant capacitor C

r

is not completely dis-

charged during the interval of Mode 1; thus, a residual voltage

appears across C

r

at t = t

1

. The two active switches S

1

and S

2

are simultaneously turned OFF in this state; thereby, the volt-

ages across S

1

and S

2

jump up from zero to the residual voltage

in C

r

, which generates a small fraction of the over lapping tran-

sition between the switching voltage and current waveforms. As

a result, the switching power losses at the turn-off transitions of

S

1

and S

2

emerge. However, the power losses are much smaller

than those of hard-switching circuit since the residual voltage

of the C

r

is much smaller than a voltage surge due to the hard-

switching turn-off operation. Thus, this switching commutation

can be dened as the semi-ZVS, as depicted in Fig. 12 (a) [26].

In contrast, the circuit operation cannot maintain DCM/CRM

in the case of D > D

max

, and then gets into CCM. In the CCM

operation, no zero current transition appears in the inductor

current i

Lr

through the one switching cycle. A small current

passes through L

r

at the turn-on transition of S

1

and S

2

(at

t = t

0

); then, the currents of S

1

and S

2

instantaneously leap up.

This operation may bring about increase of the turn-on switching

3372 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 7, JULY 2013

Fig. 17. Currentvoltage traces for switching transitions: (a) active switches

S

1

and S

2

(100 V/div, 5 A/div), (b) diodes D

1

and D

2

(100 V/div, 5 A/div),

and (c) freewheeling diode D

o

(200 V/div, 2 A/div).

power losses in S

1

and S

2

, but they are not signicant because

the leaping current derives from the minimum level of the ripple

current in L

r

. Thus, this switching commutation can be dened

as semi-ZCS, as illustrated in Fig. 12 (b) [26].

Fig. 18. Semi-soft-switching waveforms in active switches: semi-ZVS turn-

off in S

1

and S

2

(50 V/div, 2.5 A/div) and (b) semi-ZCS turn-on in S

1

and

S

2

(50 V/div, 2.5 A/div).

0

1

2

3

4

5

6

7

8

9

10

0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8

V

o

l

t

a

g

e

C

o

n

v

e

r

s

i

o

n

R

a

t

i

o

M

Duty Cycle D

Theoritical curves (ER-SWC)

Experimental values: C

r

= 15 [nF]

C

r

= 56 [nF]

C

r

= 100 [nF]

Theoritical curve (Conventional)

Fig. 19. Experimental characteristics of voltage conversion ratios with reso-

nant capacitor C

r

.

The complete soft-switching range is dened in the output

power region between P

o, min

and P

o, max

as explained in the

previous sections. Thus, a wide range of soft-switching opera-

tion can be expected in the ER-SWC boost dcdc converter by

utilizing the semi-soft-switching areas.

VI. EXPERIMENTAL RESULTS AND EVALUATIONS

A. Numerical Design Example

The essential specications of the laboratory prototype are

as follows: P

o, max

= 1 kW, P

o, min

= 200 W, switching fre-

quency f

s

= 40 kHz, input voltage V

in

= 100 V, and output

MISHIMA et al.: ANALYSIS, DESIGN, AND PERFORMANCE EVALUATIONS 3373

0

2

4

6

8

10

12

14

16

18

20

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1

I

n

p

u

t

C

u

r

r

e

n

t

I

i

n

[

A

]

Output Power P

o

[kW]

D = 0.1

D = 0.2

D = 0.3

D = 0.4

D = 0.5

(a)

0

20

40

60

80

100

120

140

160

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1

I

n

p

u

t

V

o

l

t

a

g

e

V

i

n

[

V

]

Output Power P

o

[kW]

D = 0.1

D = 0.2

D = 0.3

D = 0.4

D = 0.5

(b)

78

80

82

84

86

88

90

92

94

96

98

100

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1

E

f

f

i

c

i

e

n

c

y

[

%

]

Output Power P

o

[kW]

D = 0.1

D = 0.2

D = 0.3

D = 0.4

D = 0.5

(c)

Fig. 20. Power regulation characteristics with open-loop control (C

r

=

15 F): (a) input current I

in

= i

Lr

versus output power P

o

, (b) average input

voltage V

in

versus output power P

o

, and (c) actual efciency versus output

power P

o

.

voltage V

o

= 200 V. Note here that the P

o, min

just denotes the

minimum output power under the complete soft-switching con-

ditions, which implies that the prototype can actually deliver the

output power less than 200 W.

A parameter of the resonant capacitor C

r

can be calculated

in accordance with (30), as given by

C

r

=

(V

o

/V

in

1)P

o, min

2f

s

V

2

o

= 62.5 nF. (33)

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

1.1

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

O

u

t

p

u

t

P

o

w

e

r

P

o

[

k

W

]

Duty Cycle D

V

in

= 80 [V]

V

in

= 100 [V]

V

in

= 133 [V]

Conventional

H-SW

converter

operating area

(a)

0

2

4

6

8

10

12

14

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

I

n

p

u

t

C

u

r

r

e

n

t

I

i

n

[

A

]

Duty Cycle D

V

in

= 80 [V]

V

in

= 100 [V]

V

in

= 133 [V]

(b)

90

91

92

93

94

95

96

97

98

99

100

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1

E

f

f

i

c

i

e

n

c

y

[

%

]

Output Power P

o

[kW]

V

in

= 133 [V]

V

in

= 100 [V]

V

in

= 80 [V]

(c)

Fig. 21. Steady-state output power regulation characteristics with a voltage-

mode closed-loop control: (a) output power P

o

versus duty cycle D, (b) average

input current I

in

= i

Lr

versus duty cycle D, and (c) actual efciency versus

output power P

o

.

Fig. 13 illustrates the output power and the dv/dt rate depend-

ing on the resonant capacitor C

r

in the numerical design exam-

ple. When the maximum dv/dt rate is decided to be 300 V/s

in Fig. 13, the actual capacitance C

r

is determined to be 56 H.

Equation (31) provides the maximum value of the resonant

inductor L

r

as follows:

3374 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 7, JULY 2013

0

10

20

30

40

0 5 10 15 20 25

I

n

d

u

c

t

o

r

C

u

r

r

e

n

t

i

L

r

[

A

]

Time t [s]

Parameter B

Parameter A

(a)

0

0.2

0.4

0.6

0.8

1

0 0.1 0.2 0.3 0.4 0.5

O

u

t

p

u

t

P

o

w

e

r

P

o

[

k

W

]

Duty Cycle D

Parameter A: L

r

= 74 [H]

C

r

= 56 [nF]

Parameter B: L

r

= 20 [H]

C

r

= 15 [nF]

(b)

0

5

10

15

20

0.2 [kW] 0.5 [kW] 1 [kW]

R

M

S

V

a

l

u

e

o

f

i

L

r

[

A

]

Parameter A

Parameter B

(c)

90

92

94

96

98

100

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1

E

f

f

i

c

i

e

n

c

y

[

%

]

Output Power P

o

[kW]

Soft Switching

Parameter A: L

r

= 74 [H]

C

r

= 56 [nF]

Parameter B: L

r

= 20 [H]

C

r

= 15 [nF]

(d)

Fig. 22. Actual efciencies and soft-switching range with parameters A and B: (a) resonant inductor currents i

Lr

, (b) P

o

D characteristics, (c) RMS values of

i

Lr

, and (d) actual efciencies and soft-switching range.

L

r

< 445 H. (34)

Combination of (33) and (34) yields the analytical characteris-

tics of i

Lr

under the minimumoutput power setting in Fig. 14(a).

Those characteristics indicate that L

r

which is greater than

445 H is unacceptable for performing the DCM/CRM oper-

ations in the output power range of P

o, min

< P

o

P

o, max

.

Fig. 14(b) demonstrates the analytical characteristics of i

Lr

under the maximum output power setting by taking (32)(34)

into consideration. It can be understood that the inductor current

i

Lr

can be minimized in the case of L

r

= 100 H, but the

converter operation gets into CCM. By considering both the

peak current and conduction time interval of i

Lr

in a practical

balance, L

r

can be determined as follows:

L

r

77 H. (35)

The schematic diagram of the experimental circuit with the

output voltage closed-loop control is illustrated in Fig. 15.

The circuit parameters of the laboratory prototype are listed in

Table III.

93

94

95

96

97

98

99

100

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1 1.2

E

f

c

i

e

n

c

y

[

%

]

Output Power P

o

[kW]

Semi-ZVS Complete soft switching Semi-ZCS

Fig. 23. Actual power conversion efciency considering semi-soft-switching

regions.

B. Switching Performances

High-speed discrete insulated gate bipolar transistors (IGBTs,

IXGN60N60C2) are used for the active switches S

1

and S

2

,

MISHIMA et al.: ANALYSIS, DESIGN, AND PERFORMANCE EVALUATIONS 3375

0

5

10

15

20

25

30

35

40

0.15 0.5 1.1

P

o

w

e

r

L

o

s

s

e

s

[

W

]

Output Power P

o

[kW]

S

1

, S

2

switching losses (turn-on)

S

1

, S

2

switching losses (turn-off)

S

1

, S

2

conduction losses

D

1

, D

2

conduction losses

D

o

conduction loss

D

o

recovery loss

L

r

cupper loss

Other losses

Fig. 24. Power loss analysis.

iin

Fig. 25. Schematic diagram of two-phase ER-SWC soft-switching PWM

boost dcdc converter.

while fast recovery diodes (FRD, DSEI2x30-10C) are applied

for the diodes D

1

and D

2

, and the output freewheeling diode

D

o

.

The experimental operating waveforms are indicated in

Fig. 16. The soft-switching commutations of the active switches

and diodes in the ER-SWC soft-switching PWM boost dcdc

converter prototype can be conrmed as well as the resonant

inductor current in CRM. Note in Fig. 16(b) that the turn-off

voltages across D

1

and D

2

are clamped to the value far less

than the output voltage V

o

(= 200 V) by the effect of the res-

onant capacitor C

r

. Thereby, occurrence of voltage surges can

be avoided at the turn-off transitions of D

1

and D

2

. The cur-

rent ringings that appear in the experimental waveforms during

Mode 2 are caused by the parasitic inductances around the res-

onant capacitor C

r

. Those ringing currents can be alleviated to

some extent by improving the hardware implementation.

The currentvoltage (IV) traces of the turn-on/off transi-

tions in each switching power device are shown in Fig. 17.

ZCS turn-on of the active switches S

1

and S

2

can be conrmed

in Fig. 17(a). It should be remarked herein that the tail cur-

rent inherent to the MOS-gate controlled bipolar power de-

vice IGBT appears in the ZVS turn-off transition of the active

switches [11]. ZVS turn-on of the diodes D

1

and D

2

can be

observed in Fig. 17(b). Furthermore, ZCS turn-on and turn-off

transitions of the freewheeling diode D

o

are clearly observed in

Fig. 17(c).

The switching waveforms of S

1

and S

2

are depicted in Fig. 18

for the semi-ZVS and semi-ZCS areas. Thus, it can be proven

herein that no surge voltage and current appear in the ER-SWC

boost dcdc converter under the semi-soft-switching conditions.

C. Steady-State Characteristics

Fig. 19 depicts the converter characteristics on the voltage

conversion ratio in relation with the resonant capacitor C

r

. It can

be understood from the result that the larger the C

r

, the smaller

the range of operating duty cycle D. This is due to reduction of

the resonant characteristics impedance Z (=

_

L

r

/C

r

), which

contributes to the increase of the voltage conversion ratio as well

as decrease of the duty cycle range. It should also be remarked

in Fig. 19 that the voltage conversion ratio linearly changes

with respect to the duty cycle; hence, the voltage-mode control

scheme can be constructed in a simple conguration. The con-

version efciencies of the ER-SWC soft-switching PWM boost

dcdc converter are demonstrated in Fig. 20 under the open-loop

control condition (V

o

= 200 V constant), apart from the closed-

loop control scheme in Fig. 15. The high conversion efciency

is attained in the range of middle to rated output power, where

the maximum efciency 97.1% can be conrmed at the duty

cycle D = 0.1 with the voltage conversion ratio M = 1.5.

Fig. 21 depicts the converter characteristics with the voltage-

mode closed-loop control for input voltage variations, where the

voltage conversion ratio is set to three patterns: M = 2.5 (V

in

=

80 V), 2.0 (V

in

= 100 V), and 1.5 (V

in

= 133 V) with the con-

stant output voltage V

o

= 200 V. Due to the property of the

ER-SWC cell as mentioned previously, the variable range of

duty cycle is shifted into the smaller region as compared to

that of the conventional boost dcdc converter. As a result, the

average input currents are relatively reduced; then, the high

conversion efciency can be actually obtained. It can be ob-

served in Fig. 21(c) that the maximum efciency attains 96.4%

at M = 1.5

D. Verication for Effectiveness of Parameter Design

Guideline

The output power regulation and the actual conversion ef-

ciency are investigated with the two sets of L

r

C

r

parameters A

(L

r

= 74 H, C

r

= 56 nF) and B (L

r

= 20 H, C

r

= 15 nF).

Note herein that parameter A is selected according to (33) and

(35) together with the design method explained in Section IV,

while parameter Bis one of the examples for the undesigned pa-

rameters. Therefore, the peak value of inductor current i

Lr

with

parameter A is well reduced as compared to that of parameter

B, as shown in Fig. 22(a).

The steady-state output power regulation characteristics of

the ER-SWC soft-switching PWM boost dcdc converter for

parameters A and B are shown in Fig. 22(b) when the voltage

conversion ratio M = 2. It can be understood from Fig. 22(b)

that the circuit operates in the wider range of the duty cycle in

the case of parameter Athan parameter B. On the other hand, the

measured RMS values of i

Lr

are compared between parameters

A and B in Fig. 22(c). It can be known herein that the RMS

values are reduced with parameter A rather than parameter B.

Those results indicate that there is a tradeoff between extension

3376 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 7, JULY 2013

iLr1 iLr2

iLr1 iLr2

iLr1 iLr2

75 % Load

50 % Load

25 % Load

75 % Load

50 % Load

25 % Load

iin

iin

iin

C

u

r

r

e

n

t

[

A

]

C

u

r

r

e

n

t

[

A

]

C

u

r

r

e

n

t

[

A

]

0

5

10

15

20

0

5

10

15

20

0

5

10

15

20

75 % Load

50 % Load

25 % Load

0 10 20 30 40 50 60

t [s]

(a) (b) (c)

iLr1 iLr2

iin

iin

iin

iLr1 iLr2

iLr2 iLr1

Fig. 26. Simulated and experimental waveforms of two-phase interleaved ER-SWC soft-switching PWM boost dcdc converter: (a) simulation waveforms,

(b) measured input inductor currents (2 A/div, 2 s/div), and (c) measured dc input current (2 A/div, 2 s/div).

of the current conduction time in the power devices/components

and reduction of the peak current.

The actual conversion efciencies with parameters A and B

are shown in Fig. 22(d). It can be understood that the efciency

is improved almost 2% by means of parameter A as compared

to parameter B. This efciency improvement is considered due

to the effective reduction of the peak current in the resonant

inductor L

r

by setting the circuit parameters with the design

guideline.

E. Soft-Switching Range and Power Loss Analysis

The actual power conversion efciency and the relevant power

loss analysis of the ER-SWC soft-switching PWM boost dcdc

converter with consideration for the semi-soft-switching opera-

tions are demonstrated in Figs. 23 and 24, respectively. The high

and at curve regarding the conversion efciency can be attained

in the complete soft-switching range of 200 W P

o

1 kW.

The small amount of the turn-on power loss emerges in the active

switches for the power range of P

o

> 1 kW which corresponds

to the semi-ZCS turn-on region; thereby, the conversion ef-

ciency slightly decreases. On the other hand, the turn-off power

loss becomes outstanding in the case of P

o

< 200 W where

the semi-ZVS turn-off transition appears; then, the conversion

efciency drops as well.

It is clearly demonstrated from the results that the high ef-

ciency and wide soft commutation range can be achieved from

the light to overload conditions 0.11.1 kW in the ER-SWC

soft-switching PWM boost dcdc converter.

F. Evaluation of Interleaved Circuit

The two-phase interleaved PWM boost dcdc converter em-

ploying the ER-SWC cells as depicted in Fig. 25 is evaluated

in experiments. The power rating of the interleave circuit is

0

20

40

60

80

100

120

140

0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

I

n

p

u

t

C

u

r

r

e

n

t

R

i

p

p

l

e

[

%

]

Output Power P

o

[W]

Single-Phase

2-Phase Interleaved

Fig. 27. Comparison of ripple factor in input dc current i

in

.

designed to be 1 kW, where two sets of the 500 W100 kHz

single-phase ER-SWC boost dcdc converter are assembled.

Therefore, the equivalent ripple frequency of the input current

and output voltage rises up to 200 kHz. Besides that, the single-

phase circuits designed for the power ratings of 1 kWand 500 W

are also evaluated under the same switching frequency condition

100 kHz.

The interleaving operations of the two-phase prototype can be

conrmed in Fig. 26. A good agreement between the simulated

and experimental waveforms can be observed. As indicated in

those waveforms, the ripple factor of the total input current

i

in

changes depending on the duty cycle of the ER-SWC cell.

Comparing to the 1-kWsingle-phase prototype, the ripple factor

in the two-phase prototype can be well reduced as proven in

Fig. 27.

MISHIMA et al.: ANALYSIS, DESIGN, AND PERFORMANCE EVALUATIONS 3377

92

93

94

95

96

97

98

0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

E

f

f

i

c

i

e

n

c

y

[

%

]

Output Power P

o

[kW]

Single Phase (1 [kW] Design)

Single Phase (500 [W] Design)

2-Phase Interleaved

Fig. 28. Actual efciencies of single and two-phase ER-SWC soft-switching

PWM boost dcdc converters.

The actual efciencies of the single- and two-phase proto-

types are shown in Fig. 28. In the light-load range 200500 W,

the 500-Wsingle-phase prototype produces the higher efciency

curve since its circuit parameters are designed suitable for the

power range. From the middle to heavy load 500 W1 kW, the

two-phase prototype attains the higher efciency curve, exceed-

ing that of the 1-kW single-phase prototype. Those results indi-

cate that the unit control of the operating single-phase circuits

according to the load power is quite effective for the interleaved

ER-SWC soft-switching PWM boost dcdc converter.

VII. CONCLUSION

The practical performance of a newly developed soft-

switching PWMboost dcdc converter with ER-SWCcell under

DCM/CRM conditions and its evaluations have been presented

in this paper.

The high-efciency and wide-range soft-switching operations

attained by the ER-SWCsoft-switching PWMboost dcdc con-

verter have been described in detail. The design guideline that is

based on the soft-switching operation has been explained, and

its design procedure has been actually demonstrated by using a

numerical example of the converter power ratings. By design-

ing the circuit parameters according to the guideline, the current

stresses in the input inductor and the power devices can be ef-

fectively reduced in DCM; then, the high conversion efciency

over 96% can be attained in a 1-kW laboratory prototype. The

power loss analysis based on the prototype has been depicted,

and it has been conrmed that no signicant conduction loss

exists in the additional power devices of the ER-SWC cell and

affects the conversion efciency. It is veried from the theoret-

ical and experimental results that the ER-SWC soft-switching

PWM boost dcdc converter in DCM can be one of the effec-

tive solutions for overcoming the drawbacks of the conventional

PWM boost dcdc converters in DCM and, then, is suitable for

high-efciency and high-frequency power conversion circuits

and systems.

Furthermore, the two-phase interleaved soft-switching PWM

boost dcdc converter with the ER-SWC cells has been newly

developed, and its performance and practical effectiveness have

been originally claried in the experiment in terms of conversion

efciency and ripple factor.

REFERENCES

[1] Y. P. Hsieh, J. F. Chen, T. J. Liang, and L. S. Yang, A novel high step-up

DC-DC converter for a microgrid system, IEEE Trans. Power Electron.,

vol. 26, no. 4, pp. 11271136, Apr. 2011.

[2] D. Y. Jung, Y. H. Ji, S. H. Park, Y. C. Jung, and C. Y. Won, Interleaved

soft-switching boost converter for photovoltaic power-generation system,

IEEE Trans. Power. Electron., vol. 26, no. 4, pp. 11371145, Apr. 2011.

[3] I. Aksoy, H. Bodur, and A. F. Bakan, A new ZVT-ZCS-PWM dc-dc

converter, IEEE Trans. Power Electron., vol. 25, no. 8, pp. 20932105,

Aug. 2010.

[4] S. V. Araujo, R. P. Torrico-Bascope, and G. V. Torrico-Bascope, Highly

efcient high step-up converter for fuel cell power processing based on

three-sate communication cell, IEEE Trans. Ind. Electron., vol. 57, no. 6,

pp. 19871997, Jun. 2010.

[5] H.-L. Do, A soft-switching DC/DC converter with high voltage gain,

IEEE Trans. Power Electron., vol. 25, no. 5, pp. 11931200, May 2010.

[6] E. C. Dias, L. C. G. Freitas, E. A. A. Coelho, J. B. Vieira, Jr., and L. C. de

Freitas, Novel true zero current turn-on and turn-off converters family:

Analysis and experimental results, IET Power Electron., vol. 3, no. 1,

pp. 3342, 2010.

[7] K. B. Park, G. W. Moon, and M. J. Youn, Nonisolated high step-up boost

converter integrated with Sepic converter, IEEE Trans. Power Electron.,

vol. 25, no. 9, pp. 22662275, Sep. 2010.

[8] S. H. Park, G. R. Cha, Y. C. Jung, and C. Y. Won, Design and application

for PV generation system using a soft-switching boost converter with

SARC, IEEE Trans. Ind. Electron., vol. 57, no. 2, pp. 515522, Feb.

2010.

[9] R. J. Wai and R. Y. Duan, High step-up converter with coupled-inductor,

IEEE Trans. Power Electron., vol. 20, no. 5, pp. 10251035, Sep. 2005.

[10] P. Das and G. Moschopoulos, A comparative study of zero-current-

transition PWM converters, IEEE Trans. Ind. Electron., vol. 54, no. 3,

pp. 13191328, Jun. 2007.

[11] T. Mishima and M. Nakaoka, Anewfamily of ZCS-PWMdc-dc converter

with clamping diodes-assisted active edge-resonant cell, in Proc. Int.

Conf. Electr. Mach. Syst., Oct. 2010, pp. 168173.

[12] Y. S. Roh, Y. J. Moon, J. C. Gong, and C. Yoo, Active power factor

correction (PFC) circuit with resistor-free zero-current detection, IEEE

Trans. Power Electron., vol. 26, no. 2, pp. 630637, Feb. 2011.

[13] K.-H. Liu and F. C. Lee, Zero-voltage switching technique in DC/DC

converters, IEEE Trans. Power Electron., vol. 5, no. 3, pp. 293304, Jul.

1990.

[14] B. Su, J. Zhang, and Z. Lu, Totem-pole boost bridgeless PFC rectier

with simple zero-current detection and full-range ZVS operating at the

boundary of DCM/CCM, IEEE Trans. Power Electron., vol. 26, no. 2,

pp. 427435, Feb. 2011.

[15] C. M. Stein, J. Pinheiro, and H. L. Hey, A ZCT auxiliary commutation

circuit for interleaved boost converters operating in critical conduction

mode, IEEE Trans. Power Electron., vol. 17, no. 6, pp. 954961, Nov.

2002.

[16] S. Y. Hui, K. W. Cheng, and S. R. Prakash, A fully soft-switched

extended-period quasi-resonant power-factor-correction circuit, IEEE

Trans. Power. Electron., vol. 12, no. 5, pp. 922930, Sep. 1997.

[17] M. K. Kazimierczuk, Pulse-width Modulated dc-dc Power Converters.

New York: Wiley, 2008.

[18] K. Yao, X. Ruan, X. Mao, and Z. Ye, Reducing storage capacitor of a

DCM boost PFC converter, IEEE Trans. Power. Electron., vol. 27, no. 1,

pp. 151160, Jan. 2012.

[19] K. Yao, X. Ruan, X. Mao, and Z. Ye, Variable-duty-cycle control to

achieve high input power factor for DCM boost PFC converter, IEEE

Trans. Ind. Electron., vol. 58, no. 5, pp. 18561865, May 2011.

[20] X. Huang, X. Wang, T. Nergaard, J. S. Lai, X. Xu, and L. Zhu, Parasitic

ringing and design issues of digitally controlled high power interleaved

boost converters, IEEE Trans. Power Electron., vol. 19, no. 5, pp. 1341

1352, Sep. 2004.

[21] M. Aredes, R. Dias, A. Aquino, C. Portela, and E. Watanabe, Going the

distancePower-electronics-based solutions for long-range bulk power

3378 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 7, JULY 2013

transmission, IEEE Ind. Electron. Mag., vol. 5, no. 1, pp. 3648, Mar.

2011.

[22] K. Konishi, M. Ishibashi, and M. Nakaoka, Three-phase current-fed soft-

switching PWM converter with switched capacitor type resonance DC

link, in Proc. 30th IEEE Power Electron. Spec. Conf., Jul. 1997, vol. 2,

pp. 653658.

[23] S. Chandhaket, K. Ogura, M. Nakaoka, and Y. Konishi, High-frequency

yback transformer linked utility-connected sinewave soft-switching

power conditioner using a switched capacitor snubber, in Proc. 4th Power

Electron. Motion Control Conf., Aug. 2004, vol. 3, pp. 12421247.

[24] T. Mishima, Y. Takeuchi, and M. Nakaoka, A new high step-up soft-

switching PWM boost dc-dc converter with edge-resonant switched ca-

pacitor cell, in Proc. 8th Int. Conf. Power Electron., Jun. 2011, pp. 846

853.

[25] T. Mishima, Y. Takeuchi, and M. Nakaoka, Practical performance eval-

uations of a soft-switching PWM boost DC-DC converter with high ef-

ciency and high scalability edge resonant switched capacitor modular, in

Proc. 3rd IEEE Energy Convers. Congr. Expo., Sep. 2011, pp. 30883095.

[26] Y. Takeuchi, T. Mishima, and M. Nakaoka, New evaluations on soft

commutation range of a soft-switching PWM boost DC-DC converter

with edge-resonant switched capacitor modular, in Proc. 9th IEEE Int.

Conf. Power Electron. Drive Syst., Dec. 2011, pp. 11721177.

Tomokazu Mishima (S00M04) received the B.S.,

M.S., and Ph.D. degrees all in electrical engineering

fromthe University of Tokushima, Tokushima, Japan,

in 1999, 2001, and 2004, respectively.

Since 2010, he has been with Kobe University,

Hyogo, Japan, as an Associate Professor, and in-

volved in the research and development of power

electronics circuits and systems. His research in-

terests include soft-switching dcdc converters, res-

onant converters, and high-frequency inverters for

industrial, automotive, renewable, and sustainable

energy applications.

Dr. Mishima received the Best Paper Award in the 8th IEEE International

Conference on Power Electronics and Drive Systems (IEEE-PEDS 2009), and

the Best Paper Presentation Award in the 38th Annual Conference of the IEEE

Industrial Electronics Society (IEEE-IECON 2012). He serves as an Associate

Editor for the Special Issue on Transportation Electrication and Vehicle Sys-

tems 2013 in IEEE TRANSACTION ON POWER ELECTRONICS. He is a member

of the Institute of Electrical Engineering of Japan, the Institute of Electronics,

Information and Communication Engineers, the Institute of Electrical Installa-

tion of Japan, the Japan Institute of Power Electronics, and the Japan Institute

of Marine Engineering.

Yujiro Takeuchi received the B.S. and M.S. degrees

in marine engineering from Kobe University, Hyogo,

Japan, in 2010 and 2012, respectively, where he was

involved on the research of the soft-switching dcdc

power converters suitable for renewable and sustain-

able energy applications.

Since 2012, he has been with the Department

of Power Electronics Systems Research, Hitachi Re-

search Laboratory, Hitachi, Ltd., Hitachi, Japan, and

involved in the research and development of power

semiconductor devices.

Mr. Takeuchi is a Member of the Institute of Electrical Engineering of Japan

(IEEJ). He received the IEEJ Young Engineers Paper Presentation Award in

2011 and 2013, respectively.

Mutsuo Nakaoka (M83) received the Ph.D. de-

gree in electrical engineering from Osaka University,

Osaka, Japan, in 1981.

From 1995 to 2004, he was a Professor with

the Graduate School of Science and Engineering,

Yamaguchi University, Yamaguchi, Japan, and is

currently a Professor Emeritus. Since 2004, he has

been a Visiting Professor with Kyungnam Univer-

sity, Masan, Korea, and the University of Malaya,

Kuala Lumpur, Malaysia, since 2012. His research

interests include applications and developments of

power electronics circuits and systems for industrial electronics and home ap-

pliances. From 2001 to 2006, he served as the Chairman of the IEEE Industrial

Electronics Society Japan Chapter.

Dr. Nakaoka is a Member of the Institute of Electrical Engineering of Japan,

the Institute of Electronics, Information and Communication Engineers, the

Institute of Electrical Installation of Japan, and the Japan Institute of Power

Electronics. He received many distinguished paper awards on power electronics

such as the 2001 Premium Prize Paper Award from the Institution of Electrical

Engineer (U.K.), the 2001/2003 IEEE IECON Best Paper Award, the Third

Paper Award in the 2000 IEEE International Conference on Power Electron-

ics and Drive Systems (PEDS), the 2003 IEEE Industrial Applications Society

James Melcher Prize Paper Award, and the Best Paper Award of IATC06, IEEE

PEDS 2009 Best Paper Awards, and the Best Paper Award in the 2009 IEEE

International Symposium on Industrial Electronics.

Вам также может понравиться

- Fast Decoupled OutДокумент12 страницFast Decoupled OutdineshpeterОценок пока нет

- Solar PVДокумент7 страницSolar PVdineshpeterОценок пока нет

- 07567599Документ10 страниц07567599dineshpeterОценок пока нет

- RelaysДокумент5 страницRelaysdineshpeterОценок пока нет

- First Year Ct-ActualДокумент12 страницFirst Year Ct-ActualdineshpeterОценок пока нет

- Base - EV PDFДокумент13 страницBase - EV PDFdineshpeterОценок пока нет

- Unit - I: Over Voltages in Electrical Power SystemsДокумент96 страницUnit - I: Over Voltages in Electrical Power SystemsAnonymous Y7WZ3dqoXhОценок пока нет

- Stability Analysis Unit 5Документ20 страницStability Analysis Unit 5dineshpeterОценок пока нет

- 04689447Документ12 страниц04689447dineshpeterОценок пока нет

- Affiliated Institutions B.E. Electrical and Electronics Engineering R - 2013 Program Educational ObjectivesДокумент110 страницAffiliated Institutions B.E. Electrical and Electronics Engineering R - 2013 Program Educational ObjectivesdineshpeterОценок пока нет