Академический Документы

Профессиональный Документы

Культура Документы

Radiation Hardened Lach

Загружено:

Kuldeep SinghОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Radiation Hardened Lach

Загружено:

Kuldeep SinghАвторское право:

Доступные форматы

2470

IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 58, NO. 5, OCTOBER 2011

Novel Soft Error Robust Flip-Flops in 65nm CMOS

David J. Rennie, Member, IEEE, and Manoj Sachdev, Senior Member, IEEE

AbstractCosmic neutron-induced single event upsets have become a dominant failure mechanism in sub-100 nm CMOS memory and logic circuits. In this paper two SEU-robust ip-ops are described which are based on a hardened storage cell, known as the Quatro cell. One ip-op utilizes gates while the other utilizes a pulsed-latch architecture. The proposed ip-ops exhibit as much as a 50% improvement in power-delay product when compared with recently reported hardened ip-ops. A test chip containing the proposed ip-ops arranged in a shift register conguration was fabricated in a 65nm CMOS process. Accelerated neutron radiation testing results show that the proposed ip-ops have excellent soft-error robustness. Index TermsCMOS, ip-op, latch, neutron, soft error.

I. INTRODUCTION ODERN system-on-chips (SOC) can have more than a hundred Mbit of embedded memory (e.g., SRAM) and millions of ip-ops. Each of these circuits contains storage cells to hold data. In sub-100 nm CMOS technologies the amount of charge which holds the data has decreased to the point where cosmic neutron induced single event upsets (SEU), or soft errors, have become a dominant failure mechanism [1]. Research into the mitigation of soft errors has largely focused on embedded memories, due to the fact that traditionally SRAM arrays were more sensitive to soft-errors than ip-ops. Moreover, SOCs typically contain far more bits in SRAM than in ip-ops. In embedded memories the dense array structure allows for the use of an error-correcting code (ECC), which is an effective soft error mitigation technique. However, ip-ops are integrated into the logic and are therefore spread across the SOC. As a result, ECC cannot be employed as a mitigation technique for ip-ops. Some research indicates that in sub-100 nm CMOS processes the per-bit sensitivity of ip-ops to soft-errors may equal that of SRAM [2]. As such, the large number of unprotected ip-ops in modern SOCs creates a signicant vulnerability to the overall soft-error robustness of the chip. The two primary soft-error mitigation techniques for ipops are triple modular redundancy (TMR) and harden by design (HBD). In aerospace applications TMR is often utilized, however the 200% area and power penalty of TMR makes it

Manuscript received January 11, 2011; revised April 11, 2011; accepted June 09, 2011. Date of publication August 30, 2011; date of current version October 12, 2011. D. J. Rennie was with the University of Waterloo, Waterloo, ON N2L 3G1, Canada. He is now the with Synopsys Inc., Mississauga, ON L5B 1M2, Canada (e-mail: djrennie@uwaterloo.ca). M. Sachdev is with the University of Waterloo, Waterloo, ON N2L 3G1, Canada (e-mail: msachdev@uwaterloo.ca). Color versions of one or more of the gures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identier 10.1109/TNS.2011.2162745

an untenable solution for most applications. HBD ip-ops are circuits which are intrinsically hardened against soft-errors. One HBD method involves adding redundant storage nodes in order to create a soft-error robust storage cell, as in the dual interlocked cell (DICE) [3]. While the effectiveness of the DICE cell has degraded with scaling [4], it remains the defacto hardened storage cell. In this paper two HBD ip-ops are introduced which are based on an SEU- hardened storage cell known as the Quatro cell. An SRAM cell which utilizes the Quatro cell to create an SER-robust embedded memory has been previously reported [5]. Compared with existing robust solutions, the proposed ip-ops exhibit improved power-delay performance while providing SEU robustness, as observed in accelerated neutron radiation tests at TRIUMF. Section II of this paper describes the behavior of soft errors in logic, discusses existing soft-error robust storage cells and introduces the novel ip-ops. Section III provides simulation results for performance gures of merit. Section IV provides measured results from accelerated neutron testing at the TRIUMF facility and Section V concludes the paper. II. SOFT ERRORS IN LOGIC A soft error is a data upset caused by cosmic radiation interacting with the silicon substrate. In this paper, we focus on the soft error robustness of ip-ops, which are extensively used in logic circuits to temporarily hold computation or instruction data. A. Flip-Flop Operation The two fundamental components of any ip-op are the transfer gate and the storage cell. The transfer gate provides a mechanism for controlling the ow of data into the storage cells while the storage cell stores the data after the transfer gate is deactivated. Two examples of ip-ops are explained in this section, the master-slave ip-op and the pulsed ip-op. The master-slave D ip-op (MS DFF), which is the most widely used ip-op in CMOS ASICs, is comprised of two storage elements and two transfer gates. Fig. 1(a) shows the block-level diagram of the master-slave ip-op. In almost all implementations the storage cells are implemented using two back-toback connected inverters. The signal waveforms are shown in Fig. 1(b) in order to illustrate the behavior of this circuit. When the clock signal (clk) is low, the master storage cell is transparent to the input while the slave storage cell drives the output. Accordingly a radiation induced SEU at the slave storage cell has the potential to cause computational errors in the subsequent logic stages, making an SEU in the slave latch is the most detrimental situation. A pulsed ip-op is more accurately named a pulsed-latch, as there is only a single storage cell [6]. The block level diagram

0018-9499/$26.00 2011 IEEE

RENNIE AND SACHDEV: NOVEL SOFT ERROR ROBUST FLIP-FLOPS IN 65nm CMOS

2471

Fig. 3. Vulnerable nodes in a DFF when the slave latch is active.

Fig. 1. Symbolic diagram and waveforms of a master-slave ip-op.

Fig. 4. Schematic of the (a) DICE latch and (b) Quatro latch.

Fig. 2. Symbolic diagram and waveforms of pulsed latch.

of a pulsed ip-op is shown in Fig. 2(a). A pulse generator creates a small pulse which allows the incoming data to write into the storage cell. For the rest of the clock period the data is electrically disconnected from the storage cell, which must hold the data. As such, a radiation induced SEU at this storage cell has a high potential of causing computational errors in the subsequent logic stages. The block-level diagram of a simple pulse generator is shown in Fig. 2(b) and the signal waveforms are shown in Fig. 2(c) illustrate the behavior of this ip-op. As can be seen, the waveforms for the output Q2 in Figs. 1(b) and 2(c) are identical. Assuming that the incoming data signal does not change during the brief period the pulse signal is active (typically a reasonable assumption), the logical behavior of these ip-ops is identical. B. Soft Error Fundamentals A soft error can occur when a cosmic ray interacts with the silicon substrate to generate a large number of electron-hole pairs. If this occurs near the drain of an off transistor the carriers are

collected via two mechanisms: drift and diffusion. For a very brief instant effect the depletion region between the drain and substrate is distorted, and the large electric eld causes the free electrons drift to the drain [1], [2].The depletion region quickly reforms, preventing further drift, however the large number of free carriers in the substrate may still diffuse to the drain and be collected, resulting in a further ow of current. If the current is large enough it can cause a voltage transient which changes the logical state of the node. If the node is part of a standard dual-inverter latch the intrinsic feedback of the latch will change the state of the second node and therefore the change of state will be stored by the latch. Fig. 3 shows the schematic of a DFF when the slave latch is active. In this situation N2 and P1 are off and hence a strike on the drain of these transistors has the highest potential to upset the state of the ip-op. C. Hardened Storage Cells One HBD-based soft error mitigation technique which can be implemented for either memory or logic involves replacing the standard back-to-back inverter latch with a storage cell which is intrinsically hardened against soft errors. Calin et. al. [3] proposed the 8T DICE latch which has four storage nodes, as shown in Fig. 4(a). For an SEU at any single node of the DICE latch there are always unaffected nodes which work against a change of state and thus enable the recovery of the affected node, thereby preventing the SEU. A second hardened storage cell which can be used is the eight transistor Quatro cell, the schematic of which is shown in Fig. 4(b). The Quatro storage cell has been previously used to implement a soft-error robust SRAM array [5] and other soft-error robust ip-ops. The Quatro cell has four storage nodes, labeled A, B, C and D. Nodes A and B are the primary storage nodes and nodes C and D are redundant storage nodes. Each

2472

IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 58, NO. 5, OCTOBER 2011

of these nodes is driven by an NMOS and a PMOS transistor, their gates being connected to two different nodes. As a result, if an SET pulls down (up) a node voltage, the node voltage is restored by the ON PMOS (NMOS) transistor connected to the node and driven by an unaffected node. If the SET turns on a PMOS (NMOS) transistor, the transistor has to work against an unaffected ON NMOS (PMOS) transistor to pull up (down) its drain voltage. In this way negative feedback acts against any SET, helping prevent any accidental ipping of the cell. This paper presents two SEU-tolerant ip-ops based around the Quatro storage cell. D. Proposed Flip-Flops By combining different transfer gates with the Quatro latch, a variety of ip-ops can be realized. In Fig. 5 the schematics of two such ip-ops are shown, one based on the clocked CMOS (i.e., ) transfer gate and the other on the pulsed transfer gate [6]. The operation of the proposed ip-op matches that of the master-slave ip-op shown in Fig. 1, and the operation of the proposed pulsed latch matches the operation shown in Fig. 2. These two circuits have very different application domains. The Quatro ip-op is power efcient, but relatively slow, whereas the Quatro pulsed op-op is very fast, but relatively power hungry. It should be emphasized that these are only two possible implementations of Quatro based ip-ops. The transfer gate is the mechanism to move data in and out of the storage element, and while this will play a large role in determining the performance, it plays a relatively small role in determining the robustness of the ip-op to soft-errors. The pulse generator in the pulsed latch does present an opportunity for soft-errors to affect the soft-error robustness of pulsed-latch, as a soft error here would result in a window of transparency from the input to the output. However, the pulse generator is a combinational circuit lacking regenerative feedback, meaning any effect on the pulse generator would be transitory. In addition, to ensure high speed operation the pulse generator is sized up and as such has a large capacitance. It would take a large amount of charge to affect this circuit, which in turn would result in only a small window of transparency, making it unlikely that an error would be latched. III. PERFORMANCE SIMULATIONS Spice simulations were performed in order to characterize the performance of the various ip-op architectures. While Spice simulations cannot accurately determine the soft-error robustness, they are important for characterizing transient based gures of merit, such as C-Q delay and power. A. Performance Characterization Testbench The proposed ip-ops were implemented and optimized in the ST Microelectronics 65nm CMOS process with a supply voltage of 1 V. In order to accurately characterize the timing performance of the ip-ops a detailed testbench was developed. First, the C-Q delay of the ip-op was simulated under

Fig. 5. Schematics of the proposed ip-ops (a) C2MOS and (b) pulsed.

relaxed timing conditions. Next the setup time was measured by moving the data transition edge towards the clocks rising edge until the C-Q delay begins to rise. The setup time is dened here as the point where the C-Q delay is 20% greater than the nominal C-Q delay. This point was extracted using an OCEAN script which automatically varied the clock and data edges. The D-Q delay is the summation of the nominal C-Q delay and the setup

RENNIE AND SACHDEV: NOVEL SOFT ERROR ROBUST FLIP-FLOPS IN 65nm CMOS

2473

TABLE I COMPARISON OF THE SIMULATED DELAY OF THE FLIP-FLOPS IN PS

TABLE II COMPARISON OF THE TOTAL POWER DISSIPATION OF THE FLIP-FLOPS IN

Fig. 6. Normalized comparison of PDP for a data activity of 25%.

time. The ip-op timing is determined for both high-low and low-high data transitions and the results are given in Table I. Once the timing performance of the ip-ops is characterized, the power consumption is measured. In order to take into account the loading on the clock and data signals, the currents through the nal inverters in the clock and data buffers are measured. These currents are summed with the current into the ip-op itself in order to to calculate the total power of the ip-op, . The ip-op power varies with the clock frequency and the data activity. In these simulations the clock frequency was set to 2 GHz and was extracted for data activities from 100% to 0%. The simulated power for the ip-ops is given in Table II. B. Performance Comparison The performance of the proposed and pulsed ip-ops is compared with several reference ip-ops. The MS DFF is used as the reference unprotected ip-op while two DICE-based ip-ops are used as reference SEU-robust ip-ops. The rst reference SEU-robust ip-op is a DICE based ip-op master-slave proposed by Hazuha et al. [7]. We refer to this ip-op as DICE MS. The second reference SEU-robust ip-op is based on a pulsed transfer gate combined with the DICE storage cell [8]. We refer this second ip-op as DICE Pulsed. Table I compares the timing performance of the proposed ip-ops with that of these reference ip-ops. The D-Q delay of the MS DFF is good, however it is larger than the proposed Quatro pulsed ip-op due to the large negative setup time of the latter. Fig. 6 clearly shows that the two ip-ops with the worst D-Q delay are the master-slave DICE and the Quatro ip-op. The C-Q delay for all

SEU robust ip-ops is larger than that of the MS DFF, as SEU robust storage cells are by nature more difcult to ip. The power consumption for all ip-ops is shown in Table II. As can be seen, the SEU robust ip-ops generally consume more power than the MS DFF. The only exception is the ip-op for data activities less than 15%, however, it is important to note that this op is slower than the MS DFF. Unsurprisingly the pulsed ip-ops consume the most power, and moreover their power consumption does not scale with data activity as gracefully as other ip-ops. Using the D-Q delay and power consumption data, the power-delay product (PDP) of each ip-op was calculated and normalized with respect to the PDP of the MS DFF; this is shown in Fig. 6. As can be seen, the PDP of the Quatro ip-op is 15% better than the DICE MS ip-op, while the Quatro pulsed ip-op outperform the previously reported pulsed DICE- ip-op by approximately 50%. The Quatro pulsed ip-op has the best PDP of all SEU tolerant ip-ops, especially when the data activity is high. However, the data activity in an IC is generally less than 20%, and unless the highest performance is required it would be difcult to accept the high power consumption of a pulsed-ip-op. For applications where performance is not critical the Quatro ip-op has the lowest power consumption of all the SEU-tolerant ip-ops, and for sub 15% data activity, its power consumption is even lower than the MS DFF. IV. IMPLEMENTATION AND RADIATION TESTING While schematic simulations are important to quantify the transient behavior of the circuits, to properly validate the soft error robustness of a circuit silicon results are needed. As such, a test chip was designed and fabricated in the ST Microelectronics 65nm CMOS process. A. Layout Schematic simulations provide a useful tool to quickly investigate soft-errors in a circuit, however it is difcult to account for the effects of spatial locality using schematic simulations. In silicon the nodes of the storage cells are not isolated, but rather exist in close proximity to the other nodes. As such, the layout

2474

IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 58, NO. 5, OCTOBER 2011

Fig. 7. Storage cell layouts (a) Quatro latch and (b) DICE latch.

Fig. 9. Measured spectrum of various neutron test facilities [9].

Fig. 10. TRIUMF radiation testing setup.

Fig. 8. Test chip die photo.

of the storage cells has a signicant effect on the soft-error robustness of the ip-ops. By increasing the distance between sensitive nodes the robustness of the cell can be increased at the expense of area. In this design the ip-ops were implemented without any such techniques, rather the emphasis was placed on maximizing the density and minimizing the power consumption. The layouts of the Quatro and DICE storage cells are shown in Fig. 7. In the Quatro cell the most sensitive nodes are on the PMOS side [5], and the layout has a separation of . The DICE cell is more sensitive to strikes on the NMOS transistors, and the separation of these nodes in the layout is . It would be possible to create layouts of these storage cells which would be more robust by increasing the distance between sensitive nodes, however in this work we are most interested in a comparative analysis. These layouts do not favor one storage cell over the other and as such the comparison is fair. B. Implementation In order to measure the sensitivity of the proposed ip-ops to neutron radiation a shift-register test structure was utilized. A shift register is the densest array of ip-ops, and as such is commonly used to validate the SEU robustness of ip-ops in an area-efcient manner [7]. Three shift registers were created, one with the standard DFF ip-op, one with a DICE ip-op and one with the Quatro ip-op. Each shift register contained 7500 ip-ops. The cells were optimized for area and

their pitch was matched to the standard cells of the ST kit. Compared with the DFF the area penalty of the Quatro ip-op was approximately 20% while that of the DICE ip-op was more than 50%. Fig. 8 shows the die photo of the fabricated test chip. C. Radiation Testing Setup Accelerated neutron radiation testing on the test chip was performed at TRIUMF in Vancouver, BC, Canada. Fig. 9 illustrates the natural energy of neutrons at sea level, as well as the measured spectrum of various neutron test facilities, including TRIUMF. As can be seen, no test facility is able to perfectly match the actual spectrum. At TRIUMF the ux for most neutron energies is, in general, somewhat higher the ideal and higher than other test facilities. Higher energy particles can cause errors in circumstances when lower energy particles would not have caused errors. As such the spectrum of TRIUMF might have the effect of increasing the measured error rate of ip-op beyond that what would have been seen in other test facilities. While the absolute level of robustness of the ip-ops may increase or decrease depending on which test facility is used, the relative hardness of the ip-ops should remain consistent. During the performed experiments the average neutron beam uence was , which is approximately times the neutron uence at sea level in New York City. Fig. 10 shows the test environment at the TRIUMF facility. The ICs are afxed to a board which is lowered down a shaft in order to intersect the beam. Data loggers read the data out of the IC every ve minutes and store the values on a ash card. The data

RENNIE AND SACHDEV: NOVEL SOFT ERROR ROBUST FLIP-FLOPS IN 65nm CMOS

2475

TABLE III MEASURED PERFORMANCE IN THE PRESENCE OF NEUTRON RADIATION

loggers were located well away from the beam and run off a 3.3 V supply, making them robust against soft errors. Moreover, the data which was recorded was stored in several locations on the ash card. No differences in the data values were observed on any of these les. D. Measured Accelerated SER Test Results In order to enhance the sensitivity of the circuits, measurements were taken for reduced supply voltages, as well as the standard 1.0 V supply voltage. The supply voltage was reduced due to limitations in beam time access. Reducing the supply voltage has the effect of reducing the critical charge of the cell, and hence enhancing the cells sensitivity to soft errors [10], [11]. This is essentially a further acceleration factor used to get results within a limited time frame. Under these stressed conditions the actual numbers of errors recorded are less important than the trends. Scaling the supply voltage down provides a glimpse at the error rate which would be seen given a sufciently long test time. Table III shows a complete summary of the radiation testing results. While a reasonable number of errors were recorded for the unhardened DFF, virtually no errors were recorded for the hardened ip-op. It is difcult to accurately quantify the SER performance for the hardened ip-ops due to the fact that there were so few failures. This leads to issues such as can be seen at a supply voltage 0.9 V, where a single failure of the Quatro cell leads to a larger cross-section at 0.9 V than at 0.8 V. With sufcient test time these anomalies would correct themselves. The low number of failures makes quantifying the performance difcult; however the use of bounds to show a limit on the soft-error performance is a known technique [12]. By adding an error to the measured count one can observe the change in performance, and get a sense as to the error range. Using this technique bounds on the cross section and SER values were calculated and are shown in Table III. As expected, both hardened ip-ops show a signicantly higher robustness to neutron radiation, compared with the standard DFF. After 16 hours of exposure with a supply voltage of 0.8 V the DFF had 28 failures, the DICE ip-op one failure and Quatro ip-op had no failures. At the full supply voltage

Fig. 11. TRIUMF testing: measured (a) SER bound and (b) cross section.

the DFF had a measured SER of less than 508 FIT/Mbit. This matches well with other references, such as [13], where a FIT rate of approximately 500 FIT/Mbit is reasonable in this technology. At a supply voltage of 0.8 V the SER bound of the DFF shows a modest increase to approximately 650 FIT/Mbit. Even with a lowered supply voltage both the Quatro ip-op and the DICE ip-op showed virtually no failures. The Quatro ip-op had no errors at 1.0 V and 0.8 V, and only a single error at 0.9 V. The DICE ip-op showed no errors at 1.0 V, two errors at 0.9 V, and one error at 0.8 V. The DICE ip-op has an SER bound is less than 45 FIT/Mbit and the the Quatro ip-op has an SER bound of less than 22 FIT/Mbit. Fig. 11(a) shows the measured SER bound in FIT/Mb and Fig. 11(b) shows the measured cross section, for the three supply voltages tested, 1.0 V, 0.9 V and 0.8 V. The larger bound at the 1.0 V supply voltage compared with lower supply voltage is due to the difference in test time. There is a level of uncertainty regarding the absolute measure of performance hardened ip-ops should provide. One reference point from literature shows approximately 650 FIT/Mbit for a DICE ip-op in a 40nm process [13], however in recent years some research indicates that the level of robustness of the DICE based ip-ops does not scale well [4]. While the level of robustness from the DICE cell in various references differs, there are several possible reasons for this. As previously mentioned the spectrum of the test facility can play a role. Also as previously mentioned, design techniques such as increasing the

2476

IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 58, NO. 5, OCTOBER 2011

spacing between sensitive nodes will improve the soft-error robustness of the hardened ip-op. Whatever techniques are used to enhance the robustness of DICE based ip-ops there is every reason to believe that similar strategies would yield similar robustness improvements to Quatro-based ip-ops. In this work both hardened ip-ops showed improved SER robustness compared with the standard DFF. In addition, as revealed in the performance characterization simulations, the proposed Quatro based ip-ops have attractive power-delay tradeoffs compared with the existing DICE based ip-ops. V. CONCLUSION Two soft-error robust ip-ops have been introduced based on the Quatro storage cell. These ip-ops exhibit attractive power-delay performance compared with existing SEU-robust ip-ops. In accelerated neutron radiation testing a Quatro based ip-op demonstrated improved robustness compared with the standard DFF. When the supply voltage was lowered to 0.8 V and the ip-ops were tested for over 16 hours, the DFF shift-register array had 28 failures while the Quatro based shift-register array had no failures. ACKNOWLEDGMENT The authors would like to thank the Canadian Microelectronics Corporation (CMC) for fabricating the test chip, Shah Jahinuzzaman for his invaluable contribution and Ewart Blackmore of TRIUMF for his assistance during radiation testing. REFERENCES

[1] T. Karnik, P. Hazucha, and J. Patel, Characterization of soft errors caused by single event upsets in CMOS processes, IEEE Trans. Depend. Secure Comput., vol. 1, pp. 128143, Apr.Jun. 2004.

[2] R. C. Baumann, Radiation-induced soft errors in advanced semiconductor technologies, IEEE Trans. Device Mater. Rel., vol. 5, pp. 305316, 2005. [3] T. Calin, M. Nicolaidis, and R. Velazco, Upset hardened memory design for submicron CMOS technology, IEEE Trans. Nucl. Sci., vol. 43, no. 6, pp. 28742878, Dec. 1996. [4] N. Seifert, V. Ambrose, B. Gill, Q. Shi, R. Allmon, C. Recchia, S. Mukherjee, N. Nassif, J. Krause, J. Pickholtz, and A. Balasubramanian, On the radiation-induced soft error performance of hardened sequential elements in advanced bulk CMOS technologies, in Proc. IEEE Int. Reliability Physics Symp., 2010, pp. 188197. [5] S. M. Jahinuzzaman, D. J. Rennie, and M. Sachdev, A soft error tolerant 10T SRAM bit-cell with differential read capability, IEEE Trans. Nucl. Sci., vol. 56, no. 6, pp. 37683773, Dec. 2009. [6] J. Tschanz, S. Narendra, Z. Chen, S. Borkar, M. Sachdev, and V. De, Comparative delay and energy of single edge-triggered & dual edge triggered pulsed FFs for high performance microprocessors, in Proc. Int. Symp. Low Power Electronics and Design, Aug. 2001, pp. 147152. [7] P. Hazucha et al., Measurements and analysis of SER-tolerant latch in a 90-nm dual-VT CMOS process, IEEE J. Solid-State Circuits, vol. 39, pp. 15361543, Sep. 2004. [8] D. Krueger, E. Francom, and J. Langsdorf, Circuit design for voltage scaling and SER immunity on a quad-core itanium processor, in Proc. ISSCC Digest Technical Papers, 2008, pp. 9495. [9] C. Slayman, Accuracy of Various Broad Spectrum Neutron Sources for Accelerated Soft Error Testing, SELSE, 2010. [10] S. M. Jahinuzzaman, M. Sharifkhani, and M. Sachdev, An analytical model for soft error critical charge of nanometric SRAMs, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., pp. 11871195, 2009. [11] V. Chandra and R. Aitken, Impact of technology and voltage scaling on the soft error susceptibility in nanoscale CMOS, in Proc. IEEE Int. Symp. Defect and Fault Tolerance of VLSI Systems, 2008, pp. 114122. [12] J. Warnock, L. Sigal, D. Wendel, K. P. Muller, J. Friedrich, V. Zyuban, E. Cannon, and A. J. KleinOsowski, POWER7 local clocking and clocked storage elements, in Proc. ISSCC Digital Technical Papers, 2010, pp. 178179. [13] T. D. Loveless, S. Jagannathan, T. Reece, J. Chetia, B. L. Bhuva, M. W. McCurdy, L. W. Massengill, S.-J. Wen, R. Wong, and D. Rennie, Neutron and proton-induced single event upsets for D- and DICEFlip/Flop designs at a 40 nm technology node, IEEE Trans. Nucl. Sci., vol. 58, no. 3, pp. 10081014, Jun. 2011.

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- XII Bahasa Inggris No. 16-18Документ3 страницыXII Bahasa Inggris No. 16-18Auryn AnastashaОценок пока нет

- Colleg Fee StructureДокумент1 страницаColleg Fee StructureSriram SaiОценок пока нет

- Applichem Case-SCM Sec B Group-2Документ11 страницApplichem Case-SCM Sec B Group-2Ayush RanjanОценок пока нет

- Chapter 2 GTAWДокумент72 страницыChapter 2 GTAWDevrath Bangalore Bangalore100% (1)

- CATALO VetivДокумент240 страницCATALO VetivHữu CôngОценок пока нет

- Thermodynamics Nozzle 1Документ19 страницThermodynamics Nozzle 1waseemjuttОценок пока нет

- Acord and IAAДокумент4 страницыAcord and IAABHASKARA_20080% (1)

- TractionBatteries Technical WebДокумент20 страницTractionBatteries Technical WebnarakribОценок пока нет

- Manual Bombas Pozo e ImpulsionДокумент112 страницManual Bombas Pozo e ImpulsionFernando PuentesОценок пока нет

- Lecture02 WindLoadingДокумент53 страницыLecture02 WindLoadingMongkol JirawacharadetОценок пока нет

- p2 A2 Weekend Homework Week 1-KeyДокумент4 страницыp2 A2 Weekend Homework Week 1-KeyaysegulokrОценок пока нет

- 334387bet777 - Everything About Bet777 CasinoДокумент2 страницы334387bet777 - Everything About Bet777 Casinoz7xsdpn047Оценок пока нет

- Scan 0001Документ1 страницаScan 0001ochiroowitsОценок пока нет

- Adicionando Mais Um Disco (VG) HPUXДокумент4 страницыAdicionando Mais Um Disco (VG) HPUXVinicius SantosОценок пока нет

- Kuhlmann DigiTherm Digital Controller Manual ENДокумент12 страницKuhlmann DigiTherm Digital Controller Manual ENLuis SantosОценок пока нет

- 26-789 Eng Manual Pcd3Документ133 страницы26-789 Eng Manual Pcd3Antun KoricОценок пока нет

- Heavy Industry Taxila ReportДокумент25 страницHeavy Industry Taxila ReportMuhammad UmairОценок пока нет

- CL21C650MLMXZD PDFДокумент45 страницCL21C650MLMXZD PDFJone Ferreira Dos SantosОценок пока нет

- NGO-CSR Internship Report TemplateДокумент4 страницыNGO-CSR Internship Report TemplatePriyanka Singh100% (1)

- Boeing Defence Australia LimitedДокумент16 страницBoeing Defence Australia LimitedMitchОценок пока нет

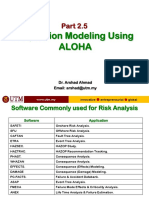

- PLSP 2 6 Aloha PDFДокумент35 страницPLSP 2 6 Aloha PDFKajenОценок пока нет

- Second Invitation OriginalДокумент4 страницыSecond Invitation Originalsudhakar80Оценок пока нет

- The Organization & Structure of Banks & Their IndustryДокумент19 страницThe Organization & Structure of Banks & Their Industryrachim04Оценок пока нет

- JUNOS Cheat SheetДокумент2 страницыJUNOS Cheat SheetJaeson VelascoОценок пока нет

- Proposal Tripurainfo Job PortalДокумент10 страницProposal Tripurainfo Job PortalEkta DevОценок пока нет

- Graphics in C LanguageДокумент8 страницGraphics in C LanguagePattabhi RamaraoОценок пока нет

- ES Service Transition PlanДокумент7 страницES Service Transition PlanShamsher Singh BainsОценок пока нет

- PBL BrochureNov04Документ26 страницPBL BrochureNov04Pedro Antonio Lea Plaza Rico100% (1)

- Segmentation - Ipynb - ColaboratoryДокумент8 страницSegmentation - Ipynb - ColaboratoryManjot KaurОценок пока нет