Академический Документы

Профессиональный Документы

Культура Документы

x86 64

Загружено:

Manuel Zamora GonzalezОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

x86 64

Загружено:

Manuel Zamora GonzalezАвторское право:

Доступные форматы

x86-64

x86-64 es una extensin del conjunto de instrucciones x86 utilizado en la microarquitectura de CPU. Contempla mejoras adicionales, como duplicar el nmero y el tamao de los registros de uso general y de instrucciones !. ndice

" #isin general

o o

"." $escripcin de la arquitectura ".% &odos de 'uncionamiento

".%." !xplicacin del modo de 'uncionamiento

".%."." &odo (argo ".%.".% &odo de )erencia

".* +&$6,

".*." !studio de mercado ".*.% -mplementaciones

"., -ntel 6,

".,." )istoria ".,.% -mplementaciones

".. $i'erencias entre +&$6, e -ntel 6,

% #/ase tam0i/n * !nlaces externos

Visin general e trata de una arquitectura desarrollada originalmente por +&$ a partir de la arquitectura x86, e implementada 0ajo el nom0re de AMD64. !l primer procesador 1para computadoras personales2 con soporte para este conjunto de instrucciones 'ue el 3pteron, lanzado en a0ril de %44*. Posteriormente 5a sido implementado en mltiples 6ariantes del +t5lon 6, y posteriores. (a empresa -ntel desarroll una arquitectura compati0le 0ajo el nom0re Intel 64 1antes EM64T2. (a cual 5a sido utilizada en el Pentium , y posteriores microprocesadores de la compaia. Descripcin de la arquitectura

!l conjunto de instrucciones del +&$ x8676, 1renom0rado posteriormente como +&$6,2 es una extensin directa de la arquitectura del x86 a una arquitectura de 6, 0its, moti6ado por el 5ec5o de que los ,89 de memoria que son direcciona0les directamente por una CPU de *% 0its ya no es su'iciente para todas las aplicaciones. +lgunos de los cam0ios:

Nuev s registr s. !l nmero de registros de propsito general se 5a incrementado de 8 en los procesadores x867*% a "6, y el tamao de todos estos registros se 5a incrementado de *% 0its a 6, 0its. +dicionalmente, el nmero de registros &&; de "%8 0its 1usados para las instrucciones extendidas -&$2 se 5a incrementado de 8 a "6. (os registros adicionales incrementan el rendimiento. !egistr s MM" #$$E% adici nales& -gualmente el nmero de registros de "%8 0its 1usados para las instrucciones !2 5an aumentado de 8 a "6. Espaci de direcci nes 'a( r. $e0ido a la arquitectura de 6, 0its, la arquitectura +&$6, puede direccionar 5asta "6 exa0ytes de memoria. (as implementaciones 'uturas de la arquitectura del +&$6, puede proporcionar 5asta % exa0ytes de memoria disponi0le. i la paginacin de memoria se utiliza correctamente, los sistemas operati6os de *% 0its podr<an tener acceso a algunas de las extensiones de direccin '<sicas sin tener que realizar la ejecucin en modo largo 1long2. Instruccin de acces a dat s relativa al punter & (as instrucciones a5ora pueden 5acer re'erencias relati6as al puntero de instrucciones 1registro =-P2. !sto permite crear cdigo independiente de la posicin que permite un cdigo muc5o m>s e'iciente en 0i0liotecas din>micas y cdigo cargado en tiempo de ejecucin. )la'adas al siste'a '*s r*pidas. $e0ido a que la segmentacin no est> soportada en el modo de 6, 0its, las llamadas al sistema no tienen las latencias asociadas con almacenar y recuperar la in'ormacin de segmentacin ni tienen que realizar las compro0aciones necesarias de proteccin a ni6el de segmentacin. Por lo tanto, +&$ 5a introducido una nue6a inter'az de llamadas al sistema, al que se accede utilizando solamente la instruccin ? @ C+((?. +unque los sistemas operati6os toda6<a pueden utilizar el sistema de interrupciones para las llamadas al sistema, en el modo de 6, 0its utilizar ? @ C+((? es m>s r>pido. Instrucci nes $$E. (a arquitectura +&$ 6, incluye las extensiones de -ntel ! y !%, las ltimas cpus incluyen las instrucciones !* y algunos tam0i/n las !,. Aam0i/n est>n soportadas las instrucciones del x86 y &&;.

+it N". !l 0it B; es una caracter<stica del procesador que permite al sistema operati6o pro5i0ir la ejecucin del cdigo en >rea de datos, mejorando la seguridad. !sta caracter<sticas est> disponi0le en los modos de *% y 6, 0its, y est> soportada por (inux, olaris, CindoDs ;P P%, CindoDs er6er %44* P".

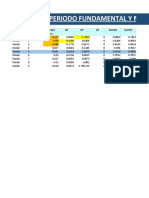

M d s de ,unci na'ient Ta'a. !equer id p r el $iste' a -perati v Es necesaria Ta'a. p r la de,ect del rec 'pila direcci na' cin de la ient aplicacin Ta'a. t/pic p r del Extensi de,ect !egistr nes del de l s de registr peran 0r ps d s it 1enera l s< 6, *% "6 *% "6 no "6 *%

M d de ,unci na'ient

s< 3 &odo nue6os &odo de largo de 6, compati0ili 0its no dad 3 de *% 0it &odo &odo 8486 5eredad os de 6irtual no )eren 3 de cia "6 0it &odo real 5eredad os &odo protegido

&odo 6, 0its

6, *% "6 *% "6

*%

no "6 "6 "6

Explicacin del ' d de ,unci na'ient )ay dos modos primarios de operacin para esta arquitectura:

M d )arg !s el utilizado por algunos 9 $s, 8BUE(inux 1x86F6,2, olaris "4, CindoDs ;P Pro'essional 1edicin x6,2, CindoDs #ista 1edicin x6,2 y CindoDs G 1edicin 6, 0its2.

$ado que el conjunto de instrucciones es el mismo, no 5ay una penalizacin importante en la ejecucin del cdigo x86. !sto no sucede en la arquitectura de -ntel -+76,, donde las di'erencias en el - + su0yacente implican que la ejecucin de cdigo de *% 0its equi6ale a utilizar un procesador completamente di'erente. !n todo caso, en +&$ 6,, las aplicaciones de *% 0its del x86 podr<an toda6<a 0ene'iciarse de una recompilacin a 6, 0its. (os registros adicionales disponi0les en el cdigo de 6, 0its, pueden ser utilizados por un compilador de alto ni6el para la optimizacin. Usando el modo largo, un sistema operati6o de 6, 0its puede ejecutar aplicaciones de *% 0its y 6, 0its simult>neamente. Aam0i/n un x8676, incluye un soporte nati6o para ejecutar las aplicaciones de "6 0its del x86. &icroso't 5a excluido expl<citamente el soporte para aplicaciones de "6 0its en la edicin x6, de CindoDs ;P Pro'essional de0ido a los pro0lemas de conseguir que el cdigo de "6 0its del x86 pueda 'uncionar con su emulador CoC6,. M d de 2erencia !l modo utilizado por los sistemas operati6os de "6 0its, como & 7$3 , y los sistemas operati6os de *% 0its, como CindoDs ;P. !n este modo, slo se puede ejecutar cdigo de "6 0its o de *% 0its. (os sistemas operati6os de 6, 0its como CindoDs ;P Pro'essional x6, y CindoDs er6er %44* x6, no se ejecutar>n. AMD64 Estudi de 'ercad +&$6, representa un cam0io con el pasado de +&$ cuyo comportamiento era seguir los est>ndares de -ntel, aunque mantiene los comportamientos anteriores de -ntel extendiendo la arquitectura del x86, desde los "6 0its 8486 5asta los *% 0its 84*86, siempre sin eliminar compati0ilidad 5acia atr>s. (a arquitectura del +&$6, la arquitectura de *% 0its del x86 1-+7*%2 aadiendo registros de 6, 0its, con modos de total compati0ilidad de *% 0its y "6 0its para so'tDare ya existente. -ncluso el modo de 6, 0its permite compati0ilidad 5ac<a atr>s, 'acilitando a las 5erramientas del x86, como los compiladores ser modi'icados a la arquitectura +&$6, con un es'uerzo m<nimo. (a arquitectura del +&$6, dispone de caracter<sticas como el 0it B;. I'ple'entaci nes (os procesadores siguientes implementan la arquitectura +&$6,:

+&$ 6, 1H8 7 Hryptonite2

o o

+&$ P5enom 6, Iuad +&$ +t5lon 6,

o o o o o o o o o o

+&$ +t5lon 6, ;% +&$ +t5lon 6, J; +&$ 3pteron +&$ Aurion 6, ;% +&$ Aurion 6, +&$ empron 1todos los que utilizan socKets G.,, L*L y +&%2 +&$ P5enom 1H"42 +&$ P5enom -+&$ +t5lon -+&$ J; 19ulldozer, Piledri6er, teamroller, !xca6ator2

Intel 64 Intel 64 1antes conocida como EM64T2 es la implementacin -ntel de la tecnolog<a x8676,. 2ist ria $urante muc5o tiempo de la 5istoria, +&$ 5a producido y distri0uido procesadores 0asados en los diseos originales de -ntel, pero en un giro de la 5istoria, -ntel, al 6er la oportunidad, adopt la arquitectura x8676, de +&$, creada como una extensin de la l<nea de procesadores x86 propios de -ntel. Como +&$ luego renom0r su arquitectura a +&$6,, -ntel de igual manera renom0r la suya a -ntel 6,. I'ple'entaci nes !sta arquitectura procesadores:

est>

implementada

en

los

siguientes

modelos

de

Core iG Core i. Core i* Core % Iuad Core % !xtreme Core % $uo

Pentium , G%4 !xtreme !dition erie 6xx Pentium , .%, erie .x6 erie .x" Celeron $ *..

-ntel Pentium $ual Core -ntel +tom ;eon erie Gxxx ;eon erie .xxx ;eon (# erie Lxxiop erie 8xx Pentium $ Celeron & serie .xx

Celeron $ **" erie *x6 erie *x"

Di,erencias entre AMD64 e Intel 64 +unque existe un alto ni6el de compati0ilidad a ni6el 0inario, se pueden encontrar pequeas di'erencias entre los dos conjuntos de instrucciones. Un ejemplo menor es el aadido de la instruccin C&P;C)8"69 1que intercam0ia dos pala0ras de 6, 0its2, una extensin de la instruccin C&P;C)889 presente en la mayor<a de los procesadores x86 del mercadoM los primeros procesadores +&$ no dispon<an de esta instruccin, por lo tanto todos los procesadores !&6,A la incluyeron.

Вам также может понравиться

- Armando Un WispДокумент9 страницArmando Un WispManuel Zamora GonzalezОценок пока нет

- Apertura Ruy LopezДокумент6 страницApertura Ruy LopezManuel Zamora Gonzalez100% (1)

- Taller de Seguridad InalambricaДокумент260 страницTaller de Seguridad InalambricaManuel Zamora GonzalezОценок пока нет

- Manual ERW 2 1 9Документ23 страницыManual ERW 2 1 9Manuel Zamora GonzalezОценок пока нет

- Ejemplo Completo de Power Builder para PrincipiantesДокумент154 страницыEjemplo Completo de Power Builder para Principiantesanro_1982100% (5)

- Matriz de Consistencia BitelДокумент2 страницыMatriz de Consistencia BitelkhchapeluzaОценок пока нет

- Balanza Ohaus TravelerДокумент2 страницыBalanza Ohaus Travelerluc1902Оценок пока нет

- Plan de Tesis CivilДокумент21 страницаPlan de Tesis Civilmiqueas100% (1)

- Certificación It en Microsoft PowerPoint 2016 + VBA para PowerPoint: Macros and Graphics ExpertДокумент14 страницCertificación It en Microsoft PowerPoint 2016 + VBA para PowerPoint: Macros and Graphics ExpertJesús MorenoОценок пока нет

- Vampire Spanish ManualДокумент88 страницVampire Spanish ManualMonica Laura Mena Martinez100% (2)

- Estela Leonor Arce Portilla: Entel Perú S.A. Ruc: 20106897914 AV. República de Colombia 791 Piso 14 San Isidro LimaДокумент2 страницыEstela Leonor Arce Portilla: Entel Perú S.A. Ruc: 20106897914 AV. República de Colombia 791 Piso 14 San Isidro LimaJOSE YEP ARCEОценок пока нет

- 104b-Diseño de Minas A Tajo AbiertoДокумент5 страниц104b-Diseño de Minas A Tajo AbiertoAnderson Marcos CastroОценок пока нет

- Análisis Sísmico EstáticoДокумент13 страницAnálisis Sísmico EstáticoGerardo SalvadorОценок пока нет

- Programación Dinámica DeterministaДокумент19 страницProgramación Dinámica DeterministaJean Paul PereaОценок пока нет

- Taller Tp2 Prog I Martes - 1ero - 2018Документ5 страницTaller Tp2 Prog I Martes - 1ero - 2018Sebastian Rafael ZambranoОценок пока нет

- Agenda de Muñequitos (Recuperado Automáticamente)Документ92 страницыAgenda de Muñequitos (Recuperado Automáticamente)Alis AmarОценок пока нет

- Sumador Completo 1 Y4 BitsДокумент9 страницSumador Completo 1 Y4 BitsNelson López100% (1)

- Contrato de TeletrabajoДокумент7 страницContrato de TeletrabajoRocio Sarabia PavonОценок пока нет

- Cómo Imprimir Un Documento de La Computadora en Ambas Caras Del Papel - EHow en EspañolДокумент4 страницыCómo Imprimir Un Documento de La Computadora en Ambas Caras Del Papel - EHow en EspañolJuan Carlos Vera MaqueraОценок пока нет

- Examen de Algebra 2 SecДокумент4 страницыExamen de Algebra 2 SecAnonymous 3QrKLHv3EОценок пока нет

- Informe Iso20000Документ30 страницInforme Iso20000YumikoArambuloFabianОценок пока нет

- Algoritmo de ConcretoДокумент3 страницыAlgoritmo de ConcretoGary GomezОценок пока нет

- Cuestionario de Computación e Informatica para El Segundo Grado de SecundariaДокумент2 страницыCuestionario de Computación e Informatica para El Segundo Grado de SecundariaLenin Jorge Villanueva Duran100% (3)

- PROPUESTAS DE TRABAJO DE GRADO ELECTRONICA DE POTENCIA - Junio - 2019Документ4 страницыPROPUESTAS DE TRABAJO DE GRADO ELECTRONICA DE POTENCIA - Junio - 2019Nelson Daniel BragaОценок пока нет

- 2518 - G10S UV Vis - UG - En.es TraducidoДокумент140 страниц2518 - G10S UV Vis - UG - En.es TraducidoEddy SucОценок пока нет

- Auditoria ComprasДокумент9 страницAuditoria ComprasBlanca Rivera MarianoОценок пока нет

- Manual para La Generación de Contingentes y Absentismos de HCMДокумент13 страницManual para La Generación de Contingentes y Absentismos de HCMDuck-petОценок пока нет

- Francisco Ramon Perez Arias 28 26 4 7 0 0 1-6 6 70 6 - 26 Masculino Sin So Licitud Médica 1/1Документ1 страницаFrancisco Ramon Perez Arias 28 26 4 7 0 0 1-6 6 70 6 - 26 Masculino Sin So Licitud Médica 1/1Juan LuisОценок пока нет

- Curso VFP 5 Formularios SencillosДокумент18 страницCurso VFP 5 Formularios SencillosMarco MadridОценок пока нет

- Cotizacion Fluke-373 DeliziaДокумент1 страницаCotizacion Fluke-373 DeliziarudypqОценок пока нет

- Fin TechsДокумент20 страницFin TechsJoselinnОценок пока нет

- Comandos de Guerra Juego de Rol PDFДокумент2 страницыComandos de Guerra Juego de Rol PDFAmber0% (1)

- Diametro de Melones 270223Документ2 страницыDiametro de Melones 270223albertoОценок пока нет

- 7.3.2.9 Packet Tracer - Troubleshooting IPv4 and IPv6 Addressing - ILMДокумент5 страниц7.3.2.9 Packet Tracer - Troubleshooting IPv4 and IPv6 Addressing - ILMJUAN SEBASTIAN CABRERA MUNOZОценок пока нет