Академический Документы

Профессиональный Документы

Культура Документы

VMAX Architecture: Enclosure (MIBE) .Each Director Has Two Connection To MIBE Via System Interface

Загружено:

Uma SekharОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

VMAX Architecture: Enclosure (MIBE) .Each Director Has Two Connection To MIBE Via System Interface

Загружено:

Uma SekharАвторское право:

Доступные форматы

VMAX Architecture

Currently there are 3 types of EMC Vmax available EMC Vmax 10K,EMC Vmax 20K and EMC Vmax 40K

!he main ar"hite"tural differen"e bet#een $M% and Vmax model is that vmax has engine "on"ept &n $M% model,#e have different hard#are for front end'() dire"tor*,ba"+ end'$) dire"tor* and memory modules ,ut in Vmax all these hard#ares are inte-rated to-ether and is +no#s as Vmax Engine

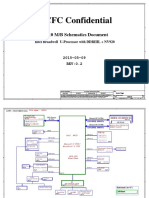

) EMC Vmax stora-e array support from 1 to maximum of . Vmax en-ines Ea"h en-ines "ontains t#o dire"tors Ea"h dire"tor in"ludes - . multi/"ore C01s 'total 12 per en-ine* 3 Ca"he memory'-lobal memory* 3 (ront end &45 modules 3 ,a"+ end &45 modules 3 6ystem &nterfa"e Module'6&,* )part from this,ea"h en-ine has redundant po#er supplies,"oolin- fans,standby po#er supplies'606* and environmental modules )ll these en-ines are inter"onne"ted usin-Vmax Matrix Interface Board Enclosure(MIBE).Ea"h dire"tor has t#o "onne"tion to M&,E via system interfa"e module'6&,* ports as sho#n belo#

Multi-core CPUs: Multi/Core C01s deliver ne# levels of performan"e and fun"tionality in a smaller footprint #ith redu"ed po#er and "oolin- re7uirements Ea"h dire"tor has . multi "ore C01s and a total of 12 C01s per en-ine Cache memor (glo!al memor ): Ea"h dire"tor "an be "onfi-ured #ith 12, 32 or 24 8, of physi"al memory 5f this, a small portion '4 8,* is reserved for lo"al pro"essin-, and the rest "onstitutes 8lobal Memory 8lobal Memory on any -iven dire"tor is al#ays mirrored to another dire"tor in the system 6o the minimum usable memory #ill be 12 8,'total 328,, on a sin-le en-ine "onfi-uration* and maximum #ill be 9128, 'total 10248,,fully loaded ei-ht VM)% En-ines system* Memory is a""essible by any dire"tor #ithin the system: &f a system has a sin-le VM)% En-ine, physi"al memory mirrors are internal to the en"losure &f a system has multiple VM)% En-ines, physi"al memory mirrors are provided bet#een en"losures "ront End I#$ Module : "ront end modules are used for host connecti%it .;ost "onne"tivity via (ibre Channel, i6C6& and (&C5< are supported Bac& End I#$ Module : ,a"+ end module provide a""ess to the dis+ drives $is+s drives are "onfi-ured under these &45 modules ' stem Interface Module('IB): 6&,s are responsible for inter"onne"tin- the Vmax en-ine=s dire"tors throu-h Matrix Interface Board Enclosure(MIBE).Ea"h Vmax en-ine has t#o 6&,s and ea"h has t#o ports 'imilar to (M)* and (M)+ arra s,Vmax has t-o t .es of !a s /. ' stem !a : 6ystem bay "ontains all Vmax en-ines )part from Vmax en-ines,it "ontains system bay standby po#er supplies('P'), 1ninterrupted 0o#er 6upply(UP'),Matrix &nterfa"e ,oard En"losure (MIBE), and a 6erver ('er%ice Processor) #ith Keyboard/ Video/ Mouse (0VM) assembly 1. 'torage !a : !he 6ymmetrix V/Max array 6tora-e ,ay is similar to the 6tora-e ,ay of the $M%/3 and $M%/4 systems &t "onsists of ei-ht to sixteen $rive En"losures, 4. to 240 drives, ei-ht '.* 606 modules, and uni7ue "ablin- #hen "ompared #ith the $M% 6eries !he 6ymmetrix V/Max array 6tora-e ,ay is "onfi-ured #ith "apa"ities of up to 120 dis+ drives for a half populated bay or 240 dis+ drives for a fully populated bay $rives, >CCs, po#er supplies, and blo#er modules are fully redundant and hot s#appable and are en"losed inside $is+ )rray En"losure'$)E* 5ne $)E holds 19 physi"al dis+ drives and one stora-e bay has total 12 $)Es'hen"e a stora-e bay has maximum of 240 dis+, 12?19* Vmax Engine "ront Vie- : ,elo# is a Vmax en-ine front vie# )s des"ribed above,Vmax en-ines are lo"ated in

Vmax system bay @e "an see the po#er supplies lo"ated at t#o sides and "oolin- fan module lo"ated in middle

Vmax Engine 2ear Vie- : !his example displays the rear vie# of the V/Max En-ine

)s explained earlier ea"h V/Max En-ine "ontains t#o dire"tor boards named here as 5dd and Even dire"tor, four (ront End &45 Modules, four ,a"+ End &45 Modules and t#o 6ystem &nterfa"e ,oards '6&,* !he ,a"+ End &45 Modules are numbered as Module

3 and Module / !he 6ystem &nterfa"e ,oards are named as Modules 1 and * !he (ront End &45 Modules are numbered as Module + and Module 4 !he top dire"tor board "ombined #ith the left (ront End &45 Modules 4 and 9 represents the even numbered dire"tor !he bottom dire"tor board "ombined #ith the ri-ht (ront End &45 Modules 4 and 9 represents the odd numbered dire"tor (or example, if this is en-ine 4 the top dire"tor #ould be dire"tor number . and the bottom dire"tor #ould be dire"tor number A Vmax Engine Port 5ssignment : !his is a typi"al Vmax port assi-nment dia-ram

)bove dia-ram "ontains port assi-nment of 6ystem &nterfa"e ,oard, the ,a"+ End &45 Modules, and the (ront End &45 Modules )s & explained earlier Vmax en-ines are inter"onne"ted usin- M&,E usin- 6ystem &nterfa"e ,oard ports 0ort ) and 0ort , 1sin- these ports all dire"tors "ommuni"ate throu-h the Virtual Matrix via redundant "onne"tions Ea"h dire"tor #ithin a V/Max En-ine "ontains t#o ,a"+ End &45 Modules Ea"h ,a"+ End &45 Module has a sin-le port, #hi"h holds a sin-le 6uad 'mall "orm-"actor Plugga!le (6'"P) connector !he B6(0 "onne"tor "able "ontains 4 smaller "ables ,ea"h have a "onne"tion to four $rive En"losures, providin- ,a"+ End (ibre Channel "onne"tivity to the dis+ drives 5n ,a"+ End &45 Module 0 these "onne"tions are desi-nated as 53, 5/, B3, and B/ 5n ,a"+ End &45 Module 1, these "onne"tions are desi-nated as C3, C/, (3, and (/. Ea"h dire"tor also "ontains t#o (ront End &45 Modules !he port desi-nations on the (ront End &45 Module #ill vary based on the interfa"e type !his example represents four (ibre Channel (ront End &45 Modules &n this ,"onfi-uration module 4 #ill "ontain ports E3, E/, "3, and "/ Module 9 #ill "ontain ports 73, 7/, 83, and 8/

)s #e dis"ussed previously, the left t#o (ront End &45 Modules are "onne"ted to the even numbered dire"tor &f it is En-ine 4'dire"tor number asso"iated #ith en-ine 4 is dire"tor A and .*, then the first port on the left most module 4 #ould be dire"tor . port E0 !his is a si-nifi"ant departure from other 6ymmetrix systems and is a result of the overall in"reased port "ount in the 6ymmetrix V/Max array Vmax Engine Configuration -ith 'torage Ba s: <o# lets have a loo+ at ho# the vmax en-ine "onfi-ures alon- #ith stora-e bay & am -ivin- pi"torial representation, from one vmax en-ine to . vmax en-ine "onfi-uration alon- #ith stora-e bays !his is the standard EMC re"ommended "onfi-uration layout /. $ne Vmax engine -ith storage !a :

!he 6ymmetrix V/Max array re7uires at least one V/Max En-ine in the 6ystem ,ay )s sho#n, the first engine in the ' stem Ba -ill al-a s !e Engine + as counted starting at / from the !ottom of the ' stem Ba &n this example,En-ine 4 has t#o half populated 6tora-e ,ays 5ne bay isdirectl attached and the se"ond is a dais chain attached 6tora-e ,ay !his allo#s for a total of 240 drives !o populate the upper half of these 6tora-e ,ays #ith drives you #ill need to add another V/Max En-ine 2 9-o Vmax engine -ith storage !a :

&n this example, the system has been expanded to in"lude En-ine 9 !his allo#s the top half of both 6tora-e ,ays to be populated #ith drives !his represents the "orre"t order for addin- V/Max En-ines to the 6ystem ,ay V/Max En-ines are added from the middle, startin- #ith 4, then 9, then 3 3 9hree Vmax engine -ith storage !a :

)-ain, #or+in- from the middle out the system has been expanded !he next V/Max En-ine is 3, allo#in- the atta"hment of t#o additional 6tora-e ,ays !his allo#s for a total of A20 drives + "our Vmax engine -ith storage !a :

4 "i%e Vmax engine -ith storage !a :

: 'ix Vmax engine -ith storage !a :

; 'e%en Vmax engine -ith storage !a :

< Eight Vmax engine -ith storage !a : ("ull .o.ulated)

<o# that #e have the -eneral idea, let=s ta+e a loo+ at ho# a system -ets fully populated 6till #or+in- from the inside,out alternatin- above and belo# En-ine 4, ea"h en-ine is added until the 6ystem ,ay is fully populated #ith . V/Max En-ines )s more en-ines are added the "orrespondin- 6tora-e ,ays are added &n this example, the "olor "odinindi"ates the relationship bet#een the en-ines and their asso"iated 6tora-e ,ays (ully populated, this "onfi-uration allo#s for a total of 2,400 Cou #ill noti"e that En-ines 1, 2, A, and . ea"h mana-e t#o daisy "hain atta"hed 6tora-e ,ays !his represents a supported system implementation, not a desi-n limitation @e have "overed only the EMC Vmax ar"hite"tural part in this post,not all Vmax features & #ill be #ritin- more post related to Vmax features later ;ope no# you -ot an idea about Vmax ar"hite"ture

======================================================

VM5) architecture

The Symmetrix V-Max family includes 2 options for scalability and growth. The V-Max series scales from 48 to 2 4!! dis"s and pro#ides 2 $eta bytes of usable protected capacity when configuring all %T& S'T' dis"s. The V-Max S( scales from 48 to )*! dis"s and is intended for smaller capacity needs that re+uire Symmetrix performance a#ailability and functionality. The V-Max architecture is comprised of up to 8 engines. (ach engine is a pair of directors. (ach director is a 2-

way +uad-core ,ntel -eon .4!! system with up to *4/& memory.,t pro#ides support for 0ibre 1hannel iS1S, /igabit (thernet and 0,123 connected hosts. 0ront-end and bac"-end connecti#ity has doubled o#er the 4M--4 with up to %28host ports and %28 dis" channels. The V-Max also le#erages 2.) /igahert5 multi-core processors. The new Virtual Matrix pro#ides the interconnect that enables resources to be shared across all V-Max engines to enable massi#e scale out The Virtual Matrix 'rchitecture replaces indi#idual function-specific directors with Symmetrix V-Max (ngines each containing a portion of /lobal Memory and two directors capable of managing front end bac" end and remote connections simultaneously.. Scalability has impro#ed in all aspects6 frontend connecti#ity /lobal Memory bac"-end connecti#ity and usable capacity. The increased usable dis" capacity is the result of an increase in /lobal Memory combined with a significant reduction in metadata o#erhead allowing 24!! de#ices to be configured with 7',4 types other than 7',4 % resulting in a dramatic increase in usable capacity. The Virtual Matrix is redundant and dual acti#e and supports all /lobal Memory references allmessaging and all management operations including internal disco#ery and initiali5ation path management load balancing fail o#er and fault isolation within the array. The Symmetrix VMax array is comprised of % to 8 V-Max (ngines. (ach V-Max (ngine contains two integrated directors .(ach director has two connections to the V-Max Matrix ,nterface &oard (nclosure 8M,&(9 #ia the System ,nterface &oard or S,& ports. Since e#ery director has two separate physical paths to e#ery other director #ia the Virtual Matrix this is a highly a#ailable interconnect with no single point of failure

(ach director also has 8 bac"-end 4/b:s 01 ports 8comprised of +uad-port ;&'s9 and #arious options for the front-end including 8 4/b:s 01 ports. ,n the full configuration of %28 4/b:s 01 ports on the front and bac" ends the expectation is that this system could deli#er 4!/&:s if there a no bottlenec"s in the system architecture.

V-Max Engine Architecture

The full VMax system comprises %% rac"s<

The center rac" is for the VMax engines the other %! are storage bays. (ach storage bay can hold up to 24! dri#es. There are %*! dis" array enclosures *4 directly connected and =* daisy chained. There are 8 VMax engines as denoted by each color. >hen configuring the Symmetrix there are different types of ;yper de#ices that can be configured.0or example6 Standard de#ices 8ST49 are configured for normal production operations &usiness 1ontinuance 8&1V9 de#ices are configured for Time0inder:Mirror replication Virtual 4e#ices 8V4(V9 are configured for Time0inder:S3'$ local pointer-based replication 4ynamic 7eallocation Volumes 847V9 de#ices are configured for Symmetrix 2ptimi5er hyper re-location

T4(V de#ices are #irtual cache-only de#ices that can grow in capacity Sa#e 4e#ices are configured for Time 0inder:S3'$ and:or T4(V de#ices 7% and 72 for remote replication Virtual de#ices can reduce wasted dis" space because the actual data is "ept in a common pool ?only what is used is allocated in the common pool and the pool is shared by many T4(V de#ices. (g6 the host has a %!! /& Virtual T4(V de#ice the T4(V de#ice uses no dis" space the Sa#e pool contains the actual data and only 2! /& is allocated until more space is re+uired. The allocated capability is managed by (M1 software

Вам также может понравиться

- Build your own Blockchain: Make your own blockchain and trading bot on your pcОт EverandBuild your own Blockchain: Make your own blockchain and trading bot on your pcОценок пока нет

- EMC Vmax ArchitectureДокумент12 страницEMC Vmax Architectureravimars2250% (2)

- VMAX ArchitectureДокумент9 страницVMAX Architecturebobbili84Оценок пока нет

- EMC Vmax Architecture: Detailed ExplanationДокумент9 страницEMC Vmax Architecture: Detailed Explanationnaidu88Оценок пока нет

- EMC Vmax ArchitectureДокумент11 страницEMC Vmax ArchitectureParthiban AsparОценок пока нет

- Basic Stuff InterviewДокумент19 страницBasic Stuff InterviewVamsi BonamОценок пока нет

- Vmax Family Student GuideДокумент323 страницыVmax Family Student GuideAdnan Javaid50% (2)

- SymmetrixДокумент133 страницыSymmetrixsandeepmrajuОценок пока нет

- Virtualization & Storage: David RingДокумент47 страницVirtualization & Storage: David RingParthiОценок пока нет

- VMAX3 Configuration Management Student GuideДокумент336 страницVMAX3 Configuration Management Student Guidesbabups7767% (3)

- VMAX3 Configuration Management OverviewДокумент40 страницVMAX3 Configuration Management OverviewSudheer Ch100% (1)

- Module 1 VMAX Performance WorkshopДокумент38 страницModule 1 VMAX Performance WorkshopVijay0% (1)

- Installation and Maintenamce - Student - Guide PDFДокумент323 страницыInstallation and Maintenamce - Student - Guide PDFसंतोष शर्मा100% (1)

- Symmetrix Basic Handbook V1.0Документ76 страницSymmetrix Basic Handbook V1.0chengabfbОценок пока нет

- Basic Differences-DMX Vs VMAXДокумент5 страницBasic Differences-DMX Vs VMAXuniversemohanОценок пока нет

- VMAX3 HW Fundamentals 2015Документ82 страницыVMAX3 HW Fundamentals 2015utochkОценок пока нет

- Max Luns To FA in EMC VmaxДокумент6 страницMax Luns To FA in EMC VmaxKinnu VinodОценок пока нет

- Session 9Документ26 страницSession 9theresa.painterОценок пока нет

- 8086 Microprocessor Trainer Kit - PDF 2Документ116 страниц8086 Microprocessor Trainer Kit - PDF 2Aviraj Ghanekar0% (1)

- Microprocessor 8086 ConfigurationДокумент1 страницаMicroprocessor 8086 Configurationvinotd1Оценок пока нет

- Aix UnixДокумент3 страницыAix UnixBenigno D. AquinoОценок пока нет

- Third-Party Switch Link-Aggregation ConfigurationДокумент22 страницыThird-Party Switch Link-Aggregation ConfigurationaleksrjОценок пока нет

- Siemens (s7 300)Документ6 страницSiemens (s7 300)imdebarshiОценок пока нет

- SIMD TutorialДокумент17 страницSIMD Tutorialzzal119911Оценок пока нет

- David Ring: Virtualization & StorageДокумент10 страницDavid Ring: Virtualization & StorageBen Cheikh Ali MohsenОценок пока нет

- 15th Lecture 6. Future Processors To Use Coarse-Grain ParallelismДокумент35 страниц15th Lecture 6. Future Processors To Use Coarse-Grain ParallelismArchana RkОценок пока нет

- CX4 Installing Storage-System Hardware - Master 1424645 PDFДокумент57 страницCX4 Installing Storage-System Hardware - Master 1424645 PDFKike TapiaОценок пока нет

- Array SensorsДокумент32 страницыArray SensorsPhani KumarОценок пока нет

- Assembly Programming Journal 3Документ55 страницAssembly Programming Journal 3AmineBenali100% (2)

- Vmax 3 Notes UdemyДокумент26 страницVmax 3 Notes UdemySrinivas GollanapalliОценок пока нет

- Unix/Linux NotesДокумент1 157 страницUnix/Linux Notesvrbala100% (114)

- Tornado BSP Manual2Документ335 страницTornado BSP Manual2za_wizardОценок пока нет

- IntelДокумент8 страницIntelrajasekarkprОценок пока нет

- Codes PracticeДокумент46 страницCodes PracticePhani KumarОценок пока нет

- Using Block Ram For High Performance Read/Write Cams: Cam16X8 MacroДокумент19 страницUsing Block Ram For High Performance Read/Write Cams: Cam16X8 MacroHariPrasanth GovindarajuОценок пока нет

- Sysvwaix Lpar PDFДокумент50 страницSysvwaix Lpar PDFdbf4mailОценок пока нет

- Microprocessor Manual NewДокумент26 страницMicroprocessor Manual NewVirendra KumarОценок пока нет

- NanosimДокумент4 страницыNanosimRammohan Reddy KalamОценок пока нет

- 371 1Документ60 страниц371 1CyphFalconОценок пока нет

- ESX Qupdate 1.5Документ8 страницESX Qupdate 1.5muralisripadaОценок пока нет

- Vmax 3 ArchitectureДокумент16 страницVmax 3 ArchitecturePhani KumarОценок пока нет

- AS400 Administration Training ProgramДокумент51 страницаAS400 Administration Training ProgramVasanth KumarОценок пока нет

- Microprocessor: Navigation SearchДокумент15 страницMicroprocessor: Navigation SearchSreedhar PugalendhiОценок пока нет

- VmwareДокумент53 страницыVmwarepkkumar1209Оценок пока нет

- Build Your Own Oracle Rac 10G Release 2 Cluster On Linux and Firewire (Continued)Документ20 страницBuild Your Own Oracle Rac 10G Release 2 Cluster On Linux and Firewire (Continued)Balvinder Singh RawatОценок пока нет

- CX4 Installing Storage-System Hardware - Master 1424705Документ58 страницCX4 Installing Storage-System Hardware - Master 1424705ravimars22Оценок пока нет

- E ddVME PDFДокумент28 страницE ddVME PDFMohammad Mohsen AmiriОценок пока нет

- Cache Coherency SДокумент20 страницCache Coherency Skamal.vlsi7997Оценок пока нет

- GNU AssemblerДокумент122 страницыGNU AssemblerRaja RoutОценок пока нет

- Unit Iii - AcaДокумент13 страницUnit Iii - AcaAnitha DenisОценок пока нет

- Université de Bordj Bou ArréridjДокумент12 страницUniversité de Bordj Bou ArréridjRafik OucheneОценок пока нет

- The 80c196 ArchitectureДокумент27 страницThe 80c196 ArchitectureSai Sreekar100% (1)

- Introduction To The Atmel Atmega16 Microcontroller: Learning ObjectivesДокумент13 страницIntroduction To The Atmel Atmega16 Microcontroller: Learning Objectivesraj4110640Оценок пока нет

- S97 RamscriptДокумент1 страницаS97 RamscriptarietilangОценок пока нет

- ManualEnsamblador ASДокумент146 страницManualEnsamblador ASManuelОценок пока нет

- Mat PowerДокумент6 страницMat PowerJavier Pancho Bautista GarciaОценок пока нет

- Pro6 3 12Документ16 страницPro6 3 12Manikanta Raja MedapatiОценок пока нет

- Dynamic Kernel Patching: How You Could Add Your Own System-Calls To Linux Without Editing and Recompiling The KernelДокумент30 страницDynamic Kernel Patching: How You Could Add Your Own System-Calls To Linux Without Editing and Recompiling The KernelVishal MishraОценок пока нет

- Unix Shell Programming Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesОт EverandUnix Shell Programming Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesОценок пока нет

- SRDF S LabДокумент9 страницSRDF S LabUma SekharОценок пока нет

- Vmax DecoomДокумент4 страницыVmax DecoomUma SekharОценок пока нет

- Sun Cluster CommandsДокумент29 страницSun Cluster CommandsUma SekharОценок пока нет

- Sol SVM Best PracticesДокумент14 страницSol SVM Best Practicesapi-3706953Оценок пока нет

- USB3300 USB HS Board SchematicДокумент1 страницаUSB3300 USB HS Board Schematicvm anon100% (2)

- Assignment 3Документ1 страницаAssignment 3Robert Tatenda ZataОценок пока нет

- MySQL - Correct Way To Use The UNIQUE KEY - Stack OverflowДокумент2 страницыMySQL - Correct Way To Use The UNIQUE KEY - Stack Overflowcalin_1Оценок пока нет

- Lenovo IdeaPad 100-15IBD CG410 - CG510 NM-A681 Rev0.2 PDFДокумент59 страницLenovo IdeaPad 100-15IBD CG410 - CG510 NM-A681 Rev0.2 PDFAriciuAdrian100% (1)

- Sinamics DCM: The Innovative DC Converter: Scalable and With Integrated IntelligenceДокумент12 страницSinamics DCM: The Innovative DC Converter: Scalable and With Integrated IntelligenceCharoon SuriyawichitwongОценок пока нет

- Android For Hackers: How To Turn An Android Phone Into A Hacking Device Without Root Null Byte :: WonderHowToДокумент12 страницAndroid For Hackers: How To Turn An Android Phone Into A Hacking Device Without Root Null Byte :: WonderHowToMike Rohrich100% (1)

- Ats-F20Standalone Face Recognition Access SystemДокумент3 страницыAts-F20Standalone Face Recognition Access SystemShrijendra ShakyaОценок пока нет

- DevelopersGuide InstantIDQA94Документ269 страницDevelopersGuide InstantIDQA94jayaramanitОценок пока нет

- RTN 905 S Product Description (V100R020C10 - 02) (PDF) - ENДокумент90 страницRTN 905 S Product Description (V100R020C10 - 02) (PDF) - ENJuanОценок пока нет

- Viper SC User Manual PDFДокумент207 страницViper SC User Manual PDFOllin RodriguezОценок пока нет

- Cdac Exam TopicsДокумент6 страницCdac Exam TopicsVivek WagheОценок пока нет

- Nagios Enable NRPEДокумент2 страницыNagios Enable NRPEMartin RuswandaОценок пока нет

- Cellular CommunicationДокумент15 страницCellular CommunicationSerin AnurajОценок пока нет

- Business Class 802.11a/b/g Outdoor Dual Radio Concurrent AP/Bridge/RepeaterДокумент2 страницыBusiness Class 802.11a/b/g Outdoor Dual Radio Concurrent AP/Bridge/RepeaterAlejandro C OyОценок пока нет

- Social Media Marketing PlanДокумент5 страницSocial Media Marketing PlanGeeli Topain100% (8)

- Cisco Broadband SolutionsДокумент11 страницCisco Broadband SolutionsSamah ElshariefОценок пока нет

- 8 Channel Scanner: Channel 8N - Channel 8ANДокумент1 страница8 Channel Scanner: Channel 8N - Channel 8ANCesar PomposoОценок пока нет

- Lab 1-1 Testing The ConnectivityДокумент3 страницыLab 1-1 Testing The ConnectivityEric ResuelloОценок пока нет

- RajkotДокумент29 страницRajkotNikunj VaghasiyaОценок пока нет

- Nport NP 301 - 3onedataДокумент24 страницыNport NP 301 - 3onedataNguyễn Tuấn ViệtОценок пока нет

- SIP FraudDetection WeDo 13.11.2018Документ41 страницаSIP FraudDetection WeDo 13.11.2018KaplyaОценок пока нет

- 323-1853-201 (6110 R5.0 Install Commissioning) Issue 3Документ242 страницы323-1853-201 (6110 R5.0 Install Commissioning) Issue 3TimeslotОценок пока нет

- TQM FP7 d4 1 2-1 PDFДокумент89 страницTQM FP7 d4 1 2-1 PDFIrene DiamantopoulouОценок пока нет

- IQMedia StimuluДокумент2 страницыIQMedia Stimululuki123456Оценок пока нет

- Sa Training Course GuideДокумент36 страницSa Training Course GuideJonathan SantiagoОценок пока нет

- Countable and Uncountable Nouns - QuizДокумент14 страницCountable and Uncountable Nouns - Quizsekhar100% (1)

- Data Gathering Instrument For TraineeДокумент5 страницData Gathering Instrument For TraineeArvincent Geronimo OlatanОценок пока нет

- Music in The Digital Age PDFДокумент12 страницMusic in The Digital Age PDFMiguel Arturo Rivero ArandaОценок пока нет

- ITT420 - Kuiz 2Документ5 страницITT420 - Kuiz 2Hafiz Blm'ersОценок пока нет

- Aditya Sharma CVДокумент3 страницыAditya Sharma CVAditya SharmaОценок пока нет