Академический Документы

Профессиональный Документы

Культура Документы

Aislamiento compuerta y excitadores

Загружено:

Leonard KevОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Aislamiento compuerta y excitadores

Загружено:

Leonard KevАвторское право:

Доступные форматы

AISLAMIENTO DE COMPUERTA Y EXCITADORES DE BASE

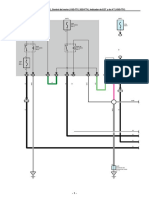

La terminal g1 que tiene un voltaje Vg1 con respecto a la terminal c, no se puede conectar en forma directa con la terminal de compuerta G1. La seal Vg1 se debera aplicar entre la terminal G1 de la compuerta y la terminal S1 del transistor M1. Hay necesidad de tener circuitos de aislamiento e interconexin entre el circuito lgico y los transistores de potencia.

La importancia de controlar la compuerta de un transistor entre su compuerta y su fuente, en lugar de aplicar el voltaje de compuerta entre la compuerta y la tierra comn se puede demostrar con la figura 17.9, donde la resistencia de carga se conecta entre la alimentacin y la tierra. El voltaje efectivo de la fuente a la compuerta es

donde ID(VGS) vara con VGS. El valor efectivo de VGS disminuye cuando el transistor se activa, y VGS llega a un valor de estado permanente que se necesita para balancear la corriente de carga o de drenaje. El valor efectivo de VGS es impredecible, y ese arreglo no es adecuado.

En forma bsica hay dos maneras de flotar o aislar la seal de controlo de compuerta con respecto a tierra.

Transformadores de pulsos

Los transformadores de pulsos slo tienen un devanado primario, y pueden tener uno o ms devanados secundarios. Con varios devanados secundarios se pueden tener seales simultneas de compuerta para transistores conectados en serie o en paralelo. La figura 17.10 muestra un arreglo de excitacin de compuerta aislado por transformador. El transformador deber tener una inductancia de fuga muy pequea, y el tiempo de subida del pulso de salida deber ser muy pequeo. Con un pulso relativamente largo y con baja frecuencia de conmutacin, el transformador se saturara y su salida se distorsionara.

Optoacopladores

En los optoacopladores se combina un diodo emisor de luz infrarroja (ILED, de infrared lightemitting diode) y un fototransistor de silicio. La seal de entrada se aplica al ILED y la seal de salida se toma del fototransistor. Los tiempos de subida y bajada de los fototransistores son muy pequeos; los valores tpicos de tiempo de encendido ton son de 2 a 5 fLS, y de tiempo de apagado toff son de 300 ns. Estos tiempos de encendido y apagado limitan las aplicaciones en alta frecuencia. En la figura 17.11 se muestra un circuito de aislamiento de compuerta donde se usa un fototransistor. Este fototransistor podra ser un par Darlington. Los fototransistores requieren suministro de potencia separado, y aumentan la complejidad, el costo y el peso de los circuitos excitadores.

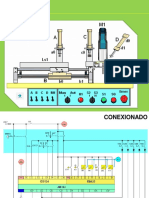

CIRCUITOS DE DISPARO PARA TIRISTORES En los convertidores con tiristor, existen diferencias de potencial entre las diversas terminales. El circuito de potencia est sujeto a un alto voltaje, por lo general mayor que 100 V, Y el circuito de compuerta se mantiene a un voltaje bajo, de 12 a 30 V en forma tpica. Se requiere un circuito de aislamiento entre un tiristor individual y su circuito generador de pulsos de compuerta. El aislamiento se puede lograr mediante transformadores de pulsos o con optoacopladores. Un Optoacoplador podra ser un fototransistor, o un rectificador fotocontrolado de silicio (fotoSCR), como el de la figura 17.12. Un pulso corto a la entrada de un ILED D1, activa al foto-SCR T1 y se dispara el tiristor de potencia TL' Este tipo de aislamiento requiere una fuente de alimentacin Separada, Vcc y aumenta el costo y el peso del circuito de disparo.

Un arreglo sencillo de aislamiento con transformadores de pulso, se ve en la figura 17.13a. Cuando se aplica un pulso de voltaje adecuado a la base del transistor de conmutacin Q1, el transistor se satura, y aparece el voltaje cd, Vcc, travs del primario del transformador, induciendo un voltaje pulsante en el secundario del transformador, que se aplica entre las terminales de compuerta y de ctodo del tiristor. Cuando el pulso se retira de la base del transistor Q1, el transistor se apaga y se induce un voltaje de polaridad contraria a travs del primario, y conduce el diodo Dm de corrida libre. La corriente debida a la energa magntica disminuye hasta cero a travs de Dm' Durante esta disminucin transitoria, se induce el correspondiente voltaje inverso en el secundario. Se puede alargar el ancho de pulso conectando un capacitor C en paralelo con el resistor R, como se ve en la figura 17.13b. El transformador conduce corriente unidireccional, y el ncleo magntico se puede saturar, limitando as el ancho de pulso. Esta clase de aislamiento de pulso es adecuada en forma tpica para pulsos de 50 a 100 us. En muchos convertidores de potencia con cargas inductivas, el periodo de conduccin de un tiristor depende del factor de potencia (FP) de la carga; por consiguiente, no est bien definido el inicio de la conduccin del tiristor. En este caso con frecuencia es necesario disparar en forma continua a los tiristores. Sin embargo, con un disparo continuo aumentan las prdidas en el tiristor. En la figura 17.13c se ve un tren de pulsos que es preferible y se puede obtener con un devanado auxiliar, como se ve en la figura 17.13c. Cuando se enciende el transistor Q1 tambin se induce un voltaje en el devanado auxiliar N3 en la base del transistor Q1, de tal modo que el diodo D1 se polariza en sentido inverso y Ql se apaga. Entre tanto, el capacitor el se carga a travs de R1 y enciende de nuevo a Q1' Este proceso de encendido y apagado contina mientras haya una seal de entrada V al aislador. En lugar de usar el devanado auxiliar como oscilador de bloqueo, se podra generar un tren de pulsos con una compuerta lgica AND, como se ve en la figura 17.13d. En la prctica, la compuerta AND no puede encender en forma directa al transistor Q1, y se conecta una etapa de acoplamiento, en el caso normal, antes del transistor.

La salida de los circuitos de compuerta en la figura 17.12 o en la figura 17.13 se conecta, en el caso normal, entre la compuerta y el ctodo junto con otros componentes protectores de compuerta, como se ve en la figura 17.14. El resistor Rg de la figura 17.14a aumenta la capacidad de la tasa dv/dt del tiristor, reduce el tiempo de apagado y aumenta las corrientes de sujecin y de enganche. El capacitor Cg de la figura 17.14b elimina los componentes de ruido de alta frecuencia, y aumenta la capacidad de la tasa dv/dt y el tiempo de retardo de la compuerta. El diodo Dg de la figura 17.14c protege a la compuerta contra voltaje negativo. Sin embargo, para los rectificadores asimtricos controlados de silicio, SCR, es preferible tener cierta cantidad de voltaje negativo en la compuerta para mejorar la capacidad de dv/dt y tambin para reducir el tiempo de apagado. Todas estas funciones se pueden combinar como se ve en la figura 17.14d, donde el diodo D1 permite slo pulsos positivos y R1 amortigua toda oscilacin transitoria, y limita la corriente de compuerta.

Вам также может понравиться

- Transformadores de PulsosДокумент3 страницыTransformadores de PulsoscradrianОценок пока нет

- OptoacopladorДокумент4 страницыOptoacopladorErnesto Sotelo GarciaОценок пока нет

- Aislacion y Amplificacion de Los Circuitos de DisparoДокумент15 страницAislacion y Amplificacion de Los Circuitos de DisparoLuis de los SantosОценок пока нет

- Osciladores Ejercicios ResueltosДокумент8 страницOsciladores Ejercicios ResueltosJohann Ivan AldahirОценок пока нет

- Disparo de Triacs y TiristoresДокумент21 страницаDisparo de Triacs y TiristoresJuanito PanchoОценок пока нет

- Osciladores-Ejercicios ResueltosДокумент8 страницOsciladores-Ejercicios ResueltosRenato Albarran AguirreОценок пока нет

- Manual técnico de servicio de Grundig SatéliteДокумент29 страницManual técnico de servicio de Grundig Satélitenaupas007100% (1)

- Osciladores-Ejercicios ResueltosДокумент8 страницOsciladores-Ejercicios ResueltosOmarОценок пока нет

- Osciladores-Ejercicios ResueltosДокумент8 страницOsciladores-Ejercicios ResueltosDaniel Perez MoralesОценок пока нет

- 1.2 Alexis Giovanni Sanchez LopezДокумент15 страниц1.2 Alexis Giovanni Sanchez LopezEdgar IsmaelОценок пока нет

- Osciladores - García Vasquez Jorge BernardoДокумент16 страницOsciladores - García Vasquez Jorge BernardoJorge B. García VasquezОценок пока нет

- Fuentes ConmutadasДокумент6 страницFuentes Conmutadasjaver9006Оценок пока нет

- Circuito Integrado 555Документ5 страницCircuito Integrado 555Ruben Patricio AvilaОценок пока нет

- DETECCION DE FALLAS EN FUENTES DE TVДокумент4 страницыDETECCION DE FALLAS EN FUENTES DE TValdoОценок пока нет

- Rectificador de onda completaДокумент18 страницRectificador de onda completaEsteban SmithОценок пока нет

- Curso de Fuentes ConmutadasДокумент11 страницCurso de Fuentes Conmutadasjose273Оценок пока нет

- Dispositivos Semiconductores de PotenciaДокумент66 страницDispositivos Semiconductores de PotenciaJoseMartinezОценок пока нет

- Fuente ConmutadaДокумент12 страницFuente ConmutadaAlan RedОценок пока нет

- Circuitos SnubberДокумент11 страницCircuitos SnubberJuanito Chandia100% (1)

- Generadores de SeñalДокумент9 страницGeneradores de SeñalRolling76Оценок пока нет

- El Temporizador 555Документ14 страницEl Temporizador 555adrian_kppОценок пока нет

- Circuitos de DisparoДокумент17 страницCircuitos de DisparoYrbyng Pb100% (1)

- Examen Parcial 1 DimmerДокумент12 страницExamen Parcial 1 DimmermetalpcОценок пока нет

- Circuitos SintonizadosДокумент9 страницCircuitos SintonizadosJorge Deza ConcoriОценок пока нет

- El Generador de Forma de Onda Es Una ICL8038 Integrado MonolíticoДокумент8 страницEl Generador de Forma de Onda Es Una ICL8038 Integrado MonolíticoAlfonso AndersonОценок пока нет

- Circuitos de DisparoДокумент12 страницCircuitos de DisparoEvi Perez80% (5)

- Circuitos de disparo analógicos para semiconductores de potenciaДокумент11 страницCircuitos de disparo analógicos para semiconductores de potenciaGeovanny SatamaОценок пока нет

- El Ci 555 Temporizador y Gen FrecuenciaДокумент12 страницEl Ci 555 Temporizador y Gen Frecuenciaenriquevazquez27Оценок пока нет

- Introduccion A Las Fuentes ConmutadasДокумент9 страницIntroduccion A Las Fuentes ConmutadasJuan Jimenez Gomez100% (1)

- Circuitos de Ayuda A La Conmutación de TransistoresДокумент6 страницCircuitos de Ayuda A La Conmutación de TransistoresPatricio GarciaОценок пока нет

- U2 Act 2 Garcia Inocencio Juan CarlosДокумент17 страницU2 Act 2 Garcia Inocencio Juan CarlosJuan CarlosОценок пока нет

- Tarea 2 Unidad 2 Funcionamineto y AplicacionesДокумент24 страницыTarea 2 Unidad 2 Funcionamineto y AplicacionespakoОценок пока нет

- Operación y FallasДокумент26 страницOperación y Fallascien.mandoОценок пока нет

- Proyecto de Electronica de Potencia-1Документ7 страницProyecto de Electronica de Potencia-1Elias herreraОценок пока нет

- Ci 555Документ11 страницCi 555perrogiОценок пока нет

- Funcionamiento del oscilador UJT y circuito temporizadorДокумент11 страницFuncionamiento del oscilador UJT y circuito temporizadorRay VazquezОценок пока нет

- Fuente de Poder Regulada 13Документ25 страницFuente de Poder Regulada 13Ivan MoraОценок пока нет

- Circuitos de Ayuda A La Conmutación de TransistoresДокумент8 страницCircuitos de Ayuda A La Conmutación de TransistoresAmy WatsonОценок пока нет

- REPARACIÓN FUENTES PHILIPS JVCДокумент10 страницREPARACIÓN FUENTES PHILIPS JVCOvanio MolinaОценок пока нет

- Circuitos PotenciaДокумент5 страницCircuitos PotenciamrjhuankyОценок пока нет

- Convertidor de CukДокумент7 страницConvertidor de CukAndres GuerreroОценок пока нет

- 1.2 Circuitos de DisparoДокумент12 страниц1.2 Circuitos de DisparoEdgar IsmaelОценок пока нет

- TPN°4-SEA-Exequiel BurgosДокумент8 страницTPN°4-SEA-Exequiel BurgosKevin TangoОценок пока нет

- Generador triangular ajustable 555Документ2 страницыGenerador triangular ajustable 555Gaston SolorzaОценок пока нет

- Circuitos de PotenciaДокумент16 страницCircuitos de PotenciaJosué GarcíaОценок пока нет

- Fuente Positiva y Fuente AltaДокумент7 страницFuente Positiva y Fuente Altajose gomezОценок пока нет

- TRIAC Y DIAC: Dispositivos controlados por voltaje para manejo de corriente alternaДокумент20 страницTRIAC Y DIAC: Dispositivos controlados por voltaje para manejo de corriente alternaThiago Brito Osinaga0% (1)

- DIACTTRTIACДокумент37 страницDIACTTRTIACeddy_maxОценок пока нет

- TiristoresДокумент14 страницTiristoresF.W.100% (7)

- Disparo SCR oscilador relajación UJTДокумент14 страницDisparo SCR oscilador relajación UJTJoel Delarosa100% (1)

- Preguntas N1 PDFДокумент35 страницPreguntas N1 PDFHernan Camilo ContrerasОценок пока нет

- Informe Previo 1 y 2 - Electronicos 2Документ8 страницInforme Previo 1 y 2 - Electronicos 2Natalia PilarОценок пока нет

- Circuitos de disparo para MOSFET y BJT de menos deДокумент8 страницCircuitos de disparo para MOSFET y BJT de menos deMarianoОценок пока нет

- Circuito de Disparo Con AislamientoДокумент23 страницыCircuito de Disparo Con Aislamientomiketronik0% (2)

- Circuitos DerivadoresДокумент17 страницCircuitos DerivadoresArtemio Harold Perlacios LuqueОценок пока нет

- Fet CTHДокумент5 страницFet CTHGonzalo ViñamaguaОценок пока нет

- Armónicas en Sistemas Eléctricos IndustrialesОт EverandArmónicas en Sistemas Eléctricos IndustrialesРейтинг: 4.5 из 5 звезд4.5/5 (12)

- 02wgss Motor CajaДокумент315 страниц02wgss Motor CajaCC1203Оценок пока нет

- Ecs 1GDДокумент31 страницаEcs 1GDJorge Luis Garcia Arevalo83% (6)

- Ecs 1GDДокумент31 страницаEcs 1GDJorge Luis Garcia Arevalo83% (6)

- ECP Uncp - Came VBДокумент60 страницECP Uncp - Came VBLeonard KevОценок пока нет

- Ciclo ConvertidoresДокумент7 страницCiclo ConvertidoresGerardo del BosqueОценок пока нет

- Centrales IIДокумент10 страницCentrales IILeonard KevОценок пока нет

- Procedimiento de TrabajoДокумент8 страницProcedimiento de TrabajoLeonard KevОценок пока нет

- Pruebas Reles UNCP - CAME (1) ViДокумент52 страницыPruebas Reles UNCP - CAME (1) ViLeonard Kev100% (1)

- Guia Constitucion EmpresasДокумент136 страницGuia Constitucion EmpresasValencia Quispe CesarОценок пока нет

- Transmision de Datos Por Fibra OpticaДокумент42 страницыTransmision de Datos Por Fibra OpticachapanitaОценок пока нет

- Automatizacion de La Soldadura Por Plasma PawДокумент31 страницаAutomatizacion de La Soldadura Por Plasma PawLeonard Kev100% (1)

- Manual para Ado de MotoresДокумент60 страницManual para Ado de MotoresJorge Eduardo González Martínez100% (2)

- Automatización Industrial Con PLC SДокумент19 страницAutomatización Industrial Con PLC SLeonard KevОценок пока нет

- Arranque de MotoresДокумент15 страницArranque de MotoresLeonard KevОценок пока нет

- Fundamentos de ArrancadoresДокумент16 страницFundamentos de ArrancadoresLeonard KevОценок пока нет

- TrabajoДокумент22 страницыTrabajoLeonard KevОценок пока нет

- Arrancadores ElectrónicosДокумент10 страницArrancadores ElectrónicosLeonard KevОценок пока нет

- Variadores de VelocidadДокумент15 страницVariadores de VelocidadLeonard KevОценок пока нет

- 1.3.-Compens en Paralelo Dom Del Tiempo PDFДокумент13 страниц1.3.-Compens en Paralelo Dom Del Tiempo PDFLeonard KevОценок пока нет

- Sistema NeumaticoДокумент24 страницыSistema NeumaticoLeonard KevОценок пока нет

- Tipos de DatosДокумент4 страницыTipos de DatosLeonard KevОценок пока нет

- Manual Curso-Elcad - 1Документ68 страницManual Curso-Elcad - 1Leonard KevОценок пока нет

- Especificaciones Tecnicas de Montaje AcraquiaДокумент34 страницыEspecificaciones Tecnicas de Montaje AcraquiaLeonard KevОценок пока нет

- Politica EstadoДокумент22 страницыPolitica EstadocaballeroruizОценок пока нет

- Diseño de motores de inducciónДокумент22 страницыDiseño de motores de inducciónLeonard KevОценок пока нет

- Ejer Cici o SledsДокумент2 страницыEjer Cici o SledsLeonard KevОценок пока нет

- Fiscalizacion AmbientalДокумент32 страницыFiscalizacion AmbientalLeonard KevОценок пока нет

- Sistemas NuméricosДокумент96 страницSistemas NuméricosFSaul LazaroОценок пока нет

- Análisis de Fallas en El Sep Tarma-ChanchamayoДокумент20 страницAnálisis de Fallas en El Sep Tarma-ChanchamayoLeonard KevОценок пока нет

- Sociedad Comercial Agrícola Lomas Del Valle Limitada R.U.T.:76.698.605-6 Factura Electronica Nº412Документ2 страницыSociedad Comercial Agrícola Lomas Del Valle Limitada R.U.T.:76.698.605-6 Factura Electronica Nº412estefyОценок пока нет

- Carta de Presentación 2014 FAДокумент7 страницCarta de Presentación 2014 FAmcsecОценок пока нет

- CIII-S10-MSPROJECT-Und 02-ACTIVIDAD APRENDIZAJE 2Документ2 страницыCIII-S10-MSPROJECT-Und 02-ACTIVIDAD APRENDIZAJE 2jhoshuaОценок пока нет

- TIC Eneducacion 2019Документ37 страницTIC Eneducacion 2019Arturo MovilОценок пока нет

- Monografia de Las ProteínasДокумент23 страницыMonografia de Las ProteínasGerson Escalante TrujilloОценок пока нет

- Proyecto de vida DOFAДокумент3 страницыProyecto de vida DOFAMauricio CharresОценок пока нет

- Acuerdo 017 2009 E.O.T.Документ166 страницAcuerdo 017 2009 E.O.T.Anderson SierraОценок пока нет

- Distribución Por Edades y Por Sexos en Una PoblaciónДокумент17 страницDistribución Por Edades y Por Sexos en Una PoblaciónSara JimenezОценок пока нет

- Hans HaackeДокумент2 страницыHans HaackeleninОценок пока нет

- Jane Green - Lios, Libros y Mas LiosДокумент149 страницJane Green - Lios, Libros y Mas LiosKumphala LuahrОценок пока нет

- Informe LacrimógenasДокумент23 страницыInforme LacrimógenasAnibal Vivaceta100% (1)

- Signos VitalwsДокумент21 страницаSignos VitalwsMaeva OlveraОценок пока нет

- Resolución STJCH 116-21 - IURE FUERO CIVILДокумент2 страницыResolución STJCH 116-21 - IURE FUERO CIVILRenacerОценок пока нет

- E-Mon Medidor Clase Verde: Medidor de Demanda/Kwh Y de KWHДокумент60 страницE-Mon Medidor Clase Verde: Medidor de Demanda/Kwh Y de KWHandresОценок пока нет

- Procedimiento Control de Documentos y RegistrosДокумент10 страницProcedimiento Control de Documentos y RegistrosEcolodge AlmejalОценок пока нет

- Anexo 01-Especificaciones Tecnicas-Epp de SeguridadДокумент2 страницыAnexo 01-Especificaciones Tecnicas-Epp de SeguridadCesar Rojas PintoОценок пока нет

- Locue CeruléusДокумент3 страницыLocue CeruléusEri BertronsОценок пока нет

- HuamantangaДокумент41 страницаHuamantangaJorgeLuisAvilaCedronОценок пока нет

- La CuentaДокумент2 страницыLa CuentaGabriel Aquino RamirezОценок пока нет

- Articulo Banco Latino KreativaДокумент4 страницыArticulo Banco Latino KreativaCarlos FrancoОценок пока нет

- Manual de VendajesДокумент75 страницManual de VendajesRuth Marisol Lopez Morales50% (2)

- Metodología Cualitativa TipeoДокумент23 страницыMetodología Cualitativa Tipeorocio gutierrez camposОценок пока нет

- Actividad 8 - Segunda Entrega Diario de CampoДокумент2 страницыActividad 8 - Segunda Entrega Diario de CampoKatherine Tovar Mora100% (1)

- Digestivo 11ed-2019Документ148 страницDigestivo 11ed-2019Monkey D Nando100% (2)

- Estado Cosmico Planetario - Astrologia GeneralДокумент5 страницEstado Cosmico Planetario - Astrologia GeneralLuis VerenzuelaОценок пока нет

- Spsu-865 Ejercicio T001.Документ12 страницSpsu-865 Ejercicio T001.Valeria Prieto YsmiñoОценок пока нет

- Certificado de Pozo A Tierra (Av. Prolongación Tacna 117) Rimac 09122019Документ2 страницыCertificado de Pozo A Tierra (Av. Prolongación Tacna 117) Rimac 09122019Eduardo Garagundo HuancaОценок пока нет

- Nuevasntendenciasnseleccionndenpersonal 3362d575a46a094Документ18 страницNuevasntendenciasnseleccionndenpersonal 3362d575a46a094Shirli DanielaОценок пока нет

- Rosca JFEДокумент36 страницRosca JFEDante AparОценок пока нет

- Solicitud de prácticas en Secretaría de Carrera de IngenieríaДокумент3 страницыSolicitud de prácticas en Secretaría de Carrera de IngenieríaEdwin JSОценок пока нет