Академический Документы

Профессиональный Документы

Культура Документы

JFET

Загружено:

alexepn23Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

JFET

Загружено:

alexepn23Авторское право:

Доступные форматы

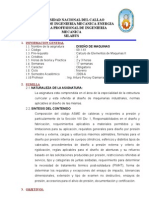

Facultad de Ingeniera Elctrica y Electrnica

Circuitos Electrnicos IEE544

Ricardo LLugsi Caar 1

JFET (Junction Field Effect Transistor)

Fig. 1. Simbolo circuital del JFET: (a) canal-n y (b) canal-p

Existen dos catergorias de transistores de juntura de efecto de campo (J FET): pn J FET y el

MESFET (Transistor de efecto de campo de metal-semiconductor). La corriente en el caso de un

J FET pasa a travs de la regin del semiconductor conocido como canal, ver Fig. 2 .

Fig. 2. Seccin lateral de un JFET con canal-n simtrico

Nota: En un J FET con canal-p las regiones p y n estn invertidas de las mostradas en la figura

anterior.

En la Fig. 3(a), se aprecia un J FET canal-n con 0 voltios aplicados a la compuerta. Si la fuente

est fijada a un potencial de tierra, y si un pequeo voltaje positivo de drenaje es aplicado se

tiene que un corriente de drenaje ( )

D

i es producida entre los terminales de la fuente y el drenaje

(siendo laconstante de proporcionalidad la conductancia del canal). Se tiene que el canal-n acta

como una resistencia, la caracterstica

D

i versus

DS

v para pequeo voltaje

DS

v es

Facultad de Ingeniera Elctrica y Electrnica

Circuitos Electrnicos IEE544

Ricardo LLugsi Caar 2

aproximadamente lineal como se muestra en la figura. Si se aplica un voltaje ms grande en la

compuerta del J FET pn se produce un cambio en la conductancia del canal. Si en vez de aplicar

un voltaje positivo, se aplica un voltaje negativo en el mismo punto, se tiene que la juntura pn se

polariza inversamente. El ancho de la regin espacio-carga se ensancha, la regin del canal se

estrangula, la resistencia del canal-n incrementa y la pendiente de la curva

D

i versus

DS

v para

pequeos valores de

DS

v decrece (ver Fig. 3(b)). Esta contraccin del canal no es uniforme, sino

que tiene lugar en las proximidades del drenador, por ser dichos puntos los que estn sometidos a

un mayor potencial y, por tanto, a una mayor polarizacin inversa

Si se sigue aumentando

DS

v , llegar un momento en el que el canal se ha contrado por

completo en las proximidades del drenaje y, por lo tanto, la conexin entre la fuente y el drenaje

desaparece, por lo tanto se dice que el canal se ha estrangulado. La tensin

DS

v a la que se

produce este fenmeno se denomina tensin de drenaje de saturacin ( ) sat v

DS

. En este caso, la

pendiente de la curva

D

i versus

DS

v se hace cero, ver Fig. 3(c).

Para el caso de ( ) sat v v

DS DS

> la porcin estrangulada del canal avanza un poco hacia la fuente

y la caracterstica

D

i versus

DS

v se satura, es decir, la

D

i permanece aproximadamente constante

e igual al valor ( ) sat i

D

.

Se puede decir que el control de la corriente en una parte del dispositivo se da por voltaje

mientras que en otra parte del dispositivo se tiene el comportamiento de transistor. En este

momento el J FET pn est en un estado encendido o de modo de deplexin, para que este

dispositivo se apage es necesario que un voltaje sea aplicado al terminal de compuerta.

Facultad de Ingeniera Elctrica y Electrnica

Circuitos Electrnicos IEE544

Ricardo LLugsi Caar 3

Fig. 3. Regiones compuerta a canal y de espacio-carga y caracterstica de corriente-voltaje para cero voltaje de

compuerta y para: (a) bajo voltaje de drenaje, (b) alto voltaje de drenaje, y (c) voltaje de drenaje que consigue el

pinchoff en el terminal de drenaje.

Si es que el voltaje de drenaje se incrementa ms an se puede alcanzar la condicin mostrada en

la Fig. 3(c). El canal es cortado (pinched off) en el terminal de drenaje. Cualquier incremento en

el voltaje de drenaje no incrementar la corriente de drenaje. La caracteristica

D

i versus

DS

v para

esta condicin se muestra en la misma figura. El voltaje de drenaje para corte (pinchoff) es

conocida como ( ) sat v

DS

. Por lo que para ( ) sat v v

DS DS

> el transistor es polarizado en la regin

de saturacin, y la corriente de drenaje para el caso ideal es independiente de

DS

v .

Contradiccin?

Cmo es posible que el estrangulamiento del canal en las proximidades del drenaje no elimine

por completo cualquier flujo de corriente por el mismo? Supongamos que al alcanzar el

estrangulamiento 0 =

D

i . Si 0 =

D

i , por lo tanto no existira corriente en ningn punto del canal,

por lo tanto, el potencial a lo largo del canal ser el mismo que con 0 =

DS

v v, es decir, cero en

todos los puntos del canal. Si fuera as, el canal debera estar totalmente abierto, lo cual

contradice la suposicin inicial de estrangulamiento del canal. Por lo tanto, en un J FET, para

( ) sat v v

DS DS

> , debe circular una corriente para inducir y mantener la condicin de

estrangulamiento del canal. Concretamente, los electrones que circulan desde la fuente al drenaje

Facultad de Ingeniera Elctrica y Electrnica

Circuitos Electrnicos IEE544

Ricardo LLugsi Caar 4

son acelerados por el campo elctrico de la zona de deplexin al alcanzar el punto de

estrangulamiento

Caracterstica de voltaje-corriente

Cuando el transistor es polarizado en la regin de saturacin se puede decir que la caracteristica

de voltaje puede ser descrita como:

2

1

|

|

.

|

\

|

=

P

GS

DSS D

V

V

I i (1.1)

Donde:

:

DSS

I Corriente de saturacin cuando 0 =

GS

v

:

P

V Voltaje de corte (pinchoff).

La caracterstica de voltaje para un J FET de canal-n y canal-p se muestra en la Fig. 4. Ntese que

el voltaje de corte

P

V para un J FET de canal-n es negativo y el voltaje compuerta a fuente

GS

v es

negativo, se puede decir que por lo tanto la relacin

P

GS

V

v

es positiva. Para el caso del J FET de

canal-p el voltaje de corte

P

V es positivo y el voltaje compuerta a fuente

GS

v es positivo, se

puede decir que por lo tanto la relacin

P

GS

V

v

es como en el caso anterior tambin positiva.

Fig. 4. Caracterstica de corriente-voltaje para: (a) J FET canal-n y (b) J FET canal-p

Para el dispositivo de canal-n, la regin de saturacin ocurre cuando ( ) sat v v

DS DS

> , donde:

( )

P GS DS

V v sat v = (1.2)

Facultad de Ingeniera Elctrica y Electrnica

Circuitos Electrnicos IEE544

Ricardo LLugsi Caar 5

Para el dispositivo de canal-p la regin de saturacin se produce cuando ( ) sat v v

SD SD

> , donde:

( )

GS P SD

v V sat v = (1.3)

La caracterstica de voltaje de transferencia de

D

i versus

GS

v , cuando el transistor es polarizado

en la regin de saturacin se muestra en la Fig. 5.

Fig. 5. Caracterstica de corriente de drenaje versus voltaje compuerta a fuente para el transistor polarizado en la

regin de saturacin para (a) JFET canal-n y (b) J FET canal-p.

Saturacin en FET

Es necesario entender que el trmino saturacin en el FET no es el mismo tratado en el caso de

BJ Ts, ya que en el caso del BJ T la saturacin implica que la corriente en el colector no se

incrementar al existir un aumento en corriente de base y que el voltaje colector emisor ha

alcanzado el valor mnimo, mientras que en el caso de un FET, la regin de saturacin implica

que la corriente de drenaje es independiente del voltaje de drenaje para un voltaje constante

compuerta a fuente.

Ejercicio

Asumase que la corriente de saturacin es mA I

DSS

2 = y que el voltaje de pinchoff es

V V

P

5 . 3 = . Calcule la corriente de drenaje

D

i y el voltaje de saturacin de drenaje a fuente

( ) sat v

DS

para: 0 =

GS

v ,

4

P

GS

V

v = y

2

P

GS

V

v = .

Facultad de Ingeniera Elctrica y Electrnica

Circuitos Electrnicos IEE544

Ricardo LLugsi Caar 6

Bibliografa:

[1] Donald E. Neamen. Microelectronics: Circuit analysis and design. 4

th

edition. Mc Graw Hill.

[2] El transistor J FET. http://de.scribd.com/doc/8241546/J FET.

Вам также может понравиться

- Agenda InformáticaДокумент4 страницыAgenda InformáticaPedro HerreraОценок пока нет

- Laboratorio 4 - HoneypotДокумент7 страницLaboratorio 4 - HoneypotDayana DayОценок пока нет

- La Seguridad Publica en MexicoДокумент11 страницLa Seguridad Publica en MexicoHugo Hernandez100% (2)

- Informe2 Beltran DonosoДокумент7 страницInforme2 Beltran Donosoalexepn23Оценок пока нет

- Imagenes para ColorearДокумент15 страницImagenes para Colorearalexepn23Оценок пока нет

- Administracion de RRHHДокумент3 страницыAdministracion de RRHHalexepn23Оценок пока нет

- Resumen de La Filosofia Gnu/linuxДокумент3 страницыResumen de La Filosofia Gnu/linuxalexepn23Оценок пока нет

- Regla de TresДокумент1 страницаRegla de Tresalexepn23Оценок пока нет

- 1er Piso IluminacionДокумент20 страниц1er Piso Iluminacionalexepn23Оценок пока нет

- Prácticas AvidemuxДокумент4 страницыPrácticas Avidemuxalexepn23Оценок пока нет

- CombinatorioДокумент1 страницаCombinatorioalexepn23Оценок пока нет

- CertificadoДокумент1 страницаCertificadoalexepn23Оценок пока нет

- Arh EpnДокумент5 страницArh Epnalexepn23Оценок пока нет

- Resumen Del Codigo ASCIIДокумент2 страницыResumen Del Codigo ASCIIalexepn23Оценок пока нет

- AssemblerДокумент85 страницAssembleralexepn23100% (1)

- Memoria DescriptivaДокумент2 страницыMemoria Descriptivaalexepn23Оценок пока нет

- Calculo de Instalaciones ElectricasДокумент9 страницCalculo de Instalaciones Electricasalexepn23Оценок пока нет

- Prueba de aptitud académica politécnica (2 horas sin calculadoraДокумент10 страницPrueba de aptitud académica politécnica (2 horas sin calculadoraromeofabianОценок пока нет

- Capitulo 12 LuminotecniaДокумент25 страницCapitulo 12 LuminotecniacorazonpuroОценок пока нет

- Actitud VerbalДокумент87 страницActitud Verbalalexepn23Оценок пока нет

- Instalaciones ElectricasДокумент80 страницInstalaciones ElectricasalexandlyОценок пока нет

- Prueba 2Документ14 страницPrueba 2alexepn23Оценок пока нет

- Ebook Tutorial Linux 6.0 0Документ170 страницEbook Tutorial Linux 6.0 0Hugo100% (1)

- La Contaminación y La GuerraДокумент2 страницыLa Contaminación y La Guerraalexepn23Оценок пока нет

- Prepa8.1 Sistemas MicroprocesadosДокумент7 страницPrepa8.1 Sistemas Microprocesadosalexepn23Оценок пока нет

- Analisis de Multietapa PDFДокумент15 страницAnalisis de Multietapa PDFalexepn23Оценок пока нет

- Prepa8.1 Sistemas MicroprocesadosДокумент7 страницPrepa8.1 Sistemas Microprocesadosalexepn23Оценок пока нет

- Informe 7Документ7 страницInforme 7alexepn23Оценок пока нет

- Funciones de E-S Alex Beltran PDFДокумент4 страницыFunciones de E-S Alex Beltran PDFalexepn23Оценок пока нет

- Marta Harnecker - El Capital - Conceptos FundamentalesДокумент119 страницMarta Harnecker - El Capital - Conceptos FundamentalesaalmunozОценок пока нет

- Cap7 MosfetДокумент51 страницаCap7 MosfetAldo SalazarОценок пока нет

- Funciones de E-S Alex Beltran PDFДокумент4 страницыFunciones de E-S Alex Beltran PDFalexepn23Оценок пока нет

- Karen Camino Control5Документ4 страницыKaren Camino Control5Karen CaminoОценок пока нет

- Instalación de Unit4 Ekon Platform 2015Документ15 страницInstalación de Unit4 Ekon Platform 2015jesus_zgzОценок пока нет

- Lab #7temperaturaДокумент5 страницLab #7temperaturaMegaVector21Оценок пока нет

- Operación de Lectura - Operación de EscrituraДокумент2 страницыOperación de Lectura - Operación de EscrituraMicaela MartinezОценок пока нет

- Procedimiento General de Estimacion de Factores de Emisión de La EpaДокумент1 страницаProcedimiento General de Estimacion de Factores de Emisión de La EpaAndres MorenoОценок пока нет

- Paquetes 1Документ10 страницPaquetes 1Ariel MoretaОценок пока нет

- Manual de Un Administrador de Base de DatosДокумент6 страницManual de Un Administrador de Base de DatosJohn Fredy Calderon GarciaОценок пока нет

- Sistemas de AlmacenajeДокумент15 страницSistemas de Almacenajekatherine linaresОценок пока нет

- Metro Conceptos BasicosДокумент33 страницыMetro Conceptos BasicosOsmar Adolfo Davila SoriaОценок пока нет

- Syllabus de Curso - Logística y Cadenas de SuministroДокумент15 страницSyllabus de Curso - Logística y Cadenas de SuministroJose Luis Cortes GuzmanОценок пока нет

- Matriz de ConsistenciaДокумент2 страницыMatriz de ConsistenciaREMI Q. TOLAОценок пока нет

- Ensayo - Teorías de ColasДокумент4 страницыEnsayo - Teorías de ColasVanessa La RosaОценок пока нет

- Artículo Sistema de Diagnostico OBD IIДокумент10 страницArtículo Sistema de Diagnostico OBD IILuis Gustavo PalomoОценок пока нет

- Intro 2Документ6 страницIntro 2ADA LINDA RUIZ MENESESОценок пока нет

- Evaluacion Practica Procesos Constructivos Integrales y AcabadosДокумент45 страницEvaluacion Practica Procesos Constructivos Integrales y Acabadosjahtner paez morgadoОценок пока нет

- SILABUS D (1) ..Документ4 страницыSILABUS D (1) ..mekalokoОценок пока нет

- Circuitos lógicos secuenciales práctica 3Документ3 страницыCircuitos lógicos secuenciales práctica 3Eliseo Pillaca SichaОценок пока нет

- Scada Holcim Ecuador PDFДокумент12 страницScada Holcim Ecuador PDFAnonymous PDEpTC4Оценок пока нет

- Herramientas de Power PointДокумент3 страницыHerramientas de Power PointManuel Isaac Parra ElkhouriОценок пока нет

- 2 Tarea1 Ejercicios de Modulacion DigitalДокумент4 страницы2 Tarea1 Ejercicios de Modulacion DigitalJose Morales0% (1)

- Diseño de curso virtual de Química 11Документ116 страницDiseño de curso virtual de Química 11Miguel FloresОценок пока нет

- Módulo de Comunicaciones Serie RS-232 y RS-485 PDFДокумент5 страницMódulo de Comunicaciones Serie RS-232 y RS-485 PDFAnonymous tCin8XОценок пока нет

- CriptografiaДокумент12 страницCriptografiaDesconocidoОценок пока нет

- Cap 14Документ28 страницCap 14Emil AcevedoОценок пока нет

- Práctica CompuДокумент1 страницаPráctica CompuRenzo CortezОценок пока нет

- Ingenieria Grafica IIДокумент4 страницыIngenieria Grafica IIwillmanfcОценок пока нет

- Manual de UsuarioДокумент15 страницManual de UsuarioRONALD MEZAОценок пока нет