Академический Документы

Профессиональный Документы

Культура Документы

Chapter#6 Datapath Subsystems: CS-403 VLSI Design Course Teacher: GUL MUNIR UJJAN BE (CIS) Session-2009 Handout - 7

Загружено:

achuu1987Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Chapter#6 Datapath Subsystems: CS-403 VLSI Design Course Teacher: GUL MUNIR UJJAN BE (CIS) Session-2009 Handout - 7

Загружено:

achuu1987Авторское право:

Доступные форматы

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Chapter#6 Datapath Subsystems

Datapath definition Addition/ Subtraction Bit wise PG logic (Generate, Propagate and Kill) Half adder and Full adder review with PG logic Carry propagation example Carry Ripple Adder Group PG logic Carry Skip/Bypass Adder Carry Select Adder Carry Look Ahead Adder Adder Variants v Subtraction v Multiple Input Addition PRSG (LFSR Linear Feedback Shift Register) One/ Zero detectors Comparators Equality Comparator Magnitude Comparator

Page - 1 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Datapath Definition

A collection of functional units such as ALUs or multipliers is called as datapath. It consists of an interconnection of basic combinational functions, such as arithmetic operators (Addition, subtraction ) or logic (AND, OR, and XOR, comparison, shifts etc).

Addition/ Subtraction

PG Logic

To get rid of carry propagate adders like carry ripple adder in which carry must ripple through all stages to calculate Cout, and to speed up the process of addition, we use PG Logic. The PG logic is specifically used to predict the Cout of any intermediate stage so that the next high order bits or group of bits may be added simultaneously.

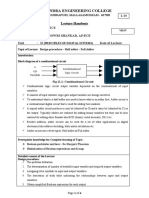

Bitwise PG Logic

Generate: (G): The adder generates (G) a carry i.e. Cout=1 when Cout is true independent of Cin. G = AB Propagate: (P): An adder propagates (P) a carry i.e. Cout = Cin when exactly one input is high. P = A B Kill: (K): The adder kills (K) a carry i.e. Cout = 0 independent of Cin. K = A B = (A + B)

Half adder and Full adder

Figure (a) : Half Adder A 0 0 1 1 B 0 1 0 1

Figure (b) : Full Adder Cout 0 0 0 1 S 0 1 1 0

Truth Table for Half Adder S = A B Cout = AB

Page - 2 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

Cin 0 1 0 1 0 1 0 1

G 0 0 0 0 0 0 1 1

P 0 0 1 1 1 1 0 0

K 1 1 0 0 0 0 0 0

Cout 0 0 0 1 0 1 1 1

S 0 1 1 0 1 0 0 1

Truth Table for Full Adder S = A B Cin Cout = AB + BCin + ACin Assume that we have not calculated Cout column in the truth table for Full adder by using above logic expression for Cout, instead we have calculated it by observing G,P and K columns. That is if K = 1 then Cout =0 if P = 1 then Cout =Cin and if G = 1 then Cout=1. At this level PG logic seems to be time consuming because of calculating PGK signals instead of calculating Cout directly. But when number of bits or group of bits in adder input increases, the understood advantages of PG logic may also increase. This is because of the fact that none of the PGK signals depend on Cin. At any stage Cout can then be calculated by just observing the bit values of a and b instead of long time waiting for Cout to be generated from previous low order bits or group of bits. S = A B Cin S = P Cin because P = A B

Cout = AB + BCin + ACin Cout = AB + Cin ( B + A ) Or Cout = (AB + Cin ( B + A )) using De-Morgans Law Or it can be written as Cout = MAJ [A, B, Cin] where, Majority Function returns 1 if it exists in majority among the input bits combination of A, B and Cin otherwise it returns 0. This can easily be observed by viewing the column Cout for inputs A,B and Cin.

Page - 3 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 4 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 5 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 6 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 7 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 8 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 9 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 10 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 11 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 12 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 13 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 14 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 15 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 16 - of 17

CS-403 VLSI Design Handout_7

Course Teacher: GUL MUNIR UJJAN

BE (CIS) Session-2009

Page - 17 - of 17

Вам также может понравиться

- As 00001030Документ32 страницыAs 00001030Akshat soniОценок пока нет

- Half and Full Adder Circuit ReportДокумент19 страницHalf and Full Adder Circuit ReportNatasha Parti50% (8)

- Unit 04 English Sentence To Boolean EquationsДокумент30 страницUnit 04 English Sentence To Boolean EquationsJhill-Jhill Jimenez Dela PeñaОценок пока нет

- Verilog Lab Instructor ManualДокумент90 страницVerilog Lab Instructor Manualbizzarevenus100% (1)

- Parallel Prefix Adders PresentationДокумент35 страницParallel Prefix Adders PresentationYermakov Vadim IvanovichОценок пока нет

- Systemverilog - Lecture 1Документ62 страницыSystemverilog - Lecture 1Shilpa ReddyОценок пока нет

- CMPUT329 - Fall 2003: Topic 4: Cost of Logic Circuits and Karnaugh MapsДокумент88 страницCMPUT329 - Fall 2003: Topic 4: Cost of Logic Circuits and Karnaugh MapsPrasad MullappillyОценок пока нет

- Comparison Among Different AddersДокумент6 страницComparison Among Different AddersIOSRjournalОценок пока нет

- Badass Tutorial Unit 6 Adders SubtractorsДокумент23 страницыBadass Tutorial Unit 6 Adders SubtractorsdjpsychoscientzОценок пока нет

- Cominational and Sequential CircuitsДокумент28 страницCominational and Sequential CircuitsKennedy MutaiОценок пока нет

- ALUДокумент21 страницаALUprathabapandianОценок пока нет

- Mahendra Engineering College L-13 Mahendhirapuri, Mallasamudram - 637503Документ4 страницыMahendra Engineering College L-13 Mahendhirapuri, Mallasamudram - 637503Gowri ShankarОценок пока нет

- 02 SystemVerilogLecture1Документ31 страница02 SystemVerilogLecture1Mihaela ScanteianuОценок пока нет

- Module - 2 DSDV (Bec302)Документ16 страницModule - 2 DSDV (Bec302)h.s.surabhi2005Оценок пока нет

- Implementation of 1-Bit Full Adder Circuit Using Pass Transistor LogicДокумент11 страницImplementation of 1-Bit Full Adder Circuit Using Pass Transistor LogicIJRASETPublicationsОценок пока нет

- Data - User - 0 - Org - Mozilla.firefox - App - Tmpdir - Full Adder in Digital Logic - GeeksforGeeks PDFДокумент3 страницыData - User - 0 - Org - Mozilla.firefox - App - Tmpdir - Full Adder in Digital Logic - GeeksforGeeks PDFSuleiman Abubakar AuduОценок пока нет

- Math L15Документ85 страницMath L15Rajendra Kumar DixitОценок пока нет

- Avionics Lecture Handouts (L-14)Документ4 страницыAvionics Lecture Handouts (L-14)Gowri ShankarОценок пока нет

- Module 2Документ42 страницыModule 2DhananjayaОценок пока нет

- Kogge-Stone AdderДокумент6 страницKogge-Stone AdderVijay Dhar MauryaОценок пока нет

- September 29, 2003 Addition and Multiplication 1Документ24 страницыSeptember 29, 2003 Addition and Multiplication 1Kaivan WadiaОценок пока нет

- Vlsi Implementation For High Speed AddersДокумент6 страницVlsi Implementation For High Speed AddersPardha Saradhi Damarla100% (1)

- Full AdderДокумент4 страницыFull AdderSuleiman Abubakar AuduОценок пока нет

- DE Unit-4Документ31 страницаDE Unit-4Dheeraj GoswamiОценок пока нет

- Introduction To Cmos Vlsi Design: AddersДокумент44 страницыIntroduction To Cmos Vlsi Design: AddersThamisetty Kranthi KumarОценок пока нет

- 09-Addition MultiplicationДокумент27 страниц09-Addition MultiplicationJbanfulОценок пока нет

- Ee101 DGTL 3Документ123 страницыEe101 DGTL 3PECMURUGANОценок пока нет

- Tutorial 5Документ10 страницTutorial 5ツ A P A C H Eツ A P A C H EОценок пока нет

- DDCA Ch5Документ101 страницаDDCA Ch5Dheer MehrotraОценок пока нет

- 1 - Bit ALUДокумент13 страниц1 - Bit ALUSouvik BasuОценок пока нет

- Courses in Electrical Engineering: Digital Electronics Chapter Three: Boolean AlgebraДокумент14 страницCourses in Electrical Engineering: Digital Electronics Chapter Three: Boolean AlgebraNGOUNEОценок пока нет

- Carry-Propagate AdderДокумент6 страницCarry-Propagate AddersaurabhОценок пока нет

- 1 - Simplification Using Theorems (DLP-2021-22)Документ12 страниц1 - Simplification Using Theorems (DLP-2021-22)bharadwaj RSSОценок пока нет

- Chapter 5: Combinational Logic Circuit: August 2020Документ24 страницыChapter 5: Combinational Logic Circuit: August 2020hahalollolОценок пока нет

- Parallel Binary AdderДокумент2 страницыParallel Binary Adderengr_467856898Оценок пока нет

- Theory: Design of Ripple Carry AddersДокумент2 страницыTheory: Design of Ripple Carry AddersMamata swainОценок пока нет

- Unit 2: 18CSC203J-Computer Organization and ArchitectureДокумент106 страницUnit 2: 18CSC203J-Computer Organization and ArchitectureJEEVAA K G (RA1911043010060)Оценок пока нет

- Paper ADDERДокумент5 страницPaper ADDERKAVIYA DIASОценок пока нет

- DE - UNIT 2 - Dec 2018 UpdatedДокумент41 страницаDE - UNIT 2 - Dec 2018 UpdatedsampritiОценок пока нет

- Design of AddersДокумент32 страницыDesign of AddersBharath DОценок пока нет

- Arithmetic Logic Unit (ALU) : CSE320 Lecture 6Документ5 страницArithmetic Logic Unit (ALU) : CSE320 Lecture 6Richie ChanОценок пока нет

- Vlsi Implementation of High Speed Adders in Fpga-SaranyaДокумент5 страницVlsi Implementation of High Speed Adders in Fpga-SaranyaSARANYA,Mba2021 Vel Tech, ChennaiОценок пока нет

- Half Adder BAsics, Full Adder BAsicsДокумент15 страницHalf Adder BAsics, Full Adder BAsicsz33sha9Оценок пока нет

- Goals of This Chapter: Designing For Performance, Area, or PowerДокумент74 страницыGoals of This Chapter: Designing For Performance, Area, or PowerRajesh BathijaОценок пока нет

- AdderДокумент5 страницAdderRutuja KakadeОценок пока нет

- Number Arithmetic p2Документ8 страницNumber Arithmetic p2manishbhardwaj8131Оценок пока нет

- 4-Bit Carry Look Ahead AdderДокумент5 страниц4-Bit Carry Look Ahead AdderluqmansulymanОценок пока нет

- DE LAB MANUAL Finalised PDFДокумент55 страницDE LAB MANUAL Finalised PDFOmkar MutalikОценок пока нет

- Dayalbagh Educational Institute: Experiment 1-To Implement Half Adder by Using Basic and UniversalДокумент41 страницаDayalbagh Educational Institute: Experiment 1-To Implement Half Adder by Using Basic and UniversalKhushi GuptaОценок пока нет

- 6.1 Addition and Subtraction of Signed Numbers:: Unit - 6 ArithmeticДокумент48 страниц6.1 Addition and Subtraction of Signed Numbers:: Unit - 6 ArithmeticTameem AhmedОценок пока нет

- LOGARITHMIC LOOK AHEAD ADDER WriteupДокумент5 страницLOGARITHMIC LOOK AHEAD ADDER WriteupshwetabhagatОценок пока нет

- Unit-Iv Adders:: Binary Adder Notations and OperationsДокумент33 страницыUnit-Iv Adders:: Binary Adder Notations and OperationsRene DevОценок пока нет

- ARM Arithmetic Part3Документ18 страницARM Arithmetic Part3ee22b059Оценок пока нет

- Pi - ChudnovskyДокумент9 страницPi - Chudnovskyzoszl1Оценок пока нет

- Csci 136 Computer Architecture IIДокумент28 страницCsci 136 Computer Architecture IIcristopherОценок пока нет

- Chapter 4 (Complete)Документ91 страницаChapter 4 (Complete)Muhammad Abbas ZaidiОценок пока нет

- Comb CircДокумент63 страницыComb Circm.sangeethjaОценок пока нет

- Range Updates With BIT - Fenwick Tree - Everything Under The SunДокумент11 страницRange Updates With BIT - Fenwick Tree - Everything Under The SunShubham KumarОценок пока нет

- Lab10 RegularДокумент12 страницLab10 RegularTyron BiggumsОценок пока нет

- What Should Never Be Done?Документ1 страницаWhat Should Never Be Done?achuu1987Оценок пока нет

- Telephone Etiquette MeansДокумент1 страницаTelephone Etiquette Meansachuu1987Оценок пока нет

- Hall: S No Item Name Quantity Required Brand Price TV Stabilizer Diwana Cott FridgeДокумент1 страницаHall: S No Item Name Quantity Required Brand Price TV Stabilizer Diwana Cott Fridgeachuu1987Оценок пока нет

- Monthly Kirana: S No Item Name Preferred Brand Quantity Kgs/LitresДокумент1 страницаMonthly Kirana: S No Item Name Preferred Brand Quantity Kgs/Litresachuu1987Оценок пока нет

- Experience SummaryДокумент1 страницаExperience Summaryachuu1987Оценок пока нет

- Step #1: Login To Application Life Cycle Management Into With Valid User Name and PasswordДокумент1 страницаStep #1: Login To Application Life Cycle Management Into With Valid User Name and Passwordachuu1987Оценок пока нет

- Data Warehousing Concepts: Database ReportingДокумент1 страницаData Warehousing Concepts: Database Reportingachuu1987Оценок пока нет

- E.F Codds RulesДокумент20 страницE.F Codds Rulesachuu1987Оценок пока нет

- Real-Time Pedestrian Detection and Tracking at Nighttime For Driver-Assistance SystemsДокумент1 страницаReal-Time Pedestrian Detection and Tracking at Nighttime For Driver-Assistance Systemsachuu1987Оценок пока нет

- Metric and Revenue CalculationДокумент1 страницаMetric and Revenue Calculationachuu1987Оценок пока нет

- Database: What Is Dimensional ModellingДокумент1 страницаDatabase: What Is Dimensional Modellingachuu1987Оценок пока нет

- Level Metrics: All Item SalesДокумент1 страницаLevel Metrics: All Item Salesachuu1987Оценок пока нет

- Transformations: Expression Based TransformationДокумент2 страницыTransformations: Expression Based Transformationachuu1987Оценок пока нет

- Intoduction To MSTRДокумент11 страницIntoduction To MSTRachuu1987Оценок пока нет

- 10 Laws of Love: Principles That Will Transform Your Life!Документ72 страницы10 Laws of Love: Principles That Will Transform Your Life!rammohan2bОценок пока нет

- 4th Periodical Test in Math 2022 2023 1Документ8 страниц4th Periodical Test in Math 2022 2023 1Jasmin Ibarra VillaflorОценок пока нет

- (Intelligent Systems, Control and Automation_ Science and Engineering 72) B. S. Goh, W. J. Leong, K. L. Teo (Auth.), Honglei Xu, Xiangyu Wang (Eds.)-Optimization and Control Methods in Industrial EngiДокумент300 страниц(Intelligent Systems, Control and Automation_ Science and Engineering 72) B. S. Goh, W. J. Leong, K. L. Teo (Auth.), Honglei Xu, Xiangyu Wang (Eds.)-Optimization and Control Methods in Industrial EngiVu Duc TruongОценок пока нет

- Active & Passive Voice Lesson Plan: Create A Cartoon in Active or Passive VoiceДокумент3 страницыActive & Passive Voice Lesson Plan: Create A Cartoon in Active or Passive VoiceHanie Balmedina-RazoОценок пока нет

- A High Voltage HalloweenДокумент84 страницыA High Voltage HalloweenAntony BurgersОценок пока нет

- Sans Nom 2Документ320 страницSans Nom 2khalidОценок пока нет

- GulfSea HT Oil 32 PDFДокумент1 страницаGulfSea HT Oil 32 PDFObydur RahmanОценок пока нет

- Vessel Nozzle PDFДокумент30 страницVessel Nozzle PDFEugenia LorenzaОценок пока нет

- Ariba Supplier Lifecycle and PerformanceДокумент2 страницыAriba Supplier Lifecycle and PerformancealanchungОценок пока нет

- Lecture 1 - Surveying FieldworkДокумент16 страницLecture 1 - Surveying FieldworkArchitect ArchitectОценок пока нет

- Viltam User Manual enДокумент13 страницViltam User Manual enszol888Оценок пока нет

- Wahs 1 PDFДокумент12 страницWahs 1 PDFKadek Deddy TaraОценок пока нет

- Bqs PDFДокумент14 страницBqs PDFMiguel ColinaОценок пока нет

- Rpi CM V1 - 1 Schematic PDFДокумент4 страницыRpi CM V1 - 1 Schematic PDFStephen J. RobertsОценок пока нет

- Rohingya Poems in RohingyalishДокумент32 страницыRohingya Poems in RohingyalishMohammed Siddique Basu100% (7)

- Why There Has Been No Brandies Brief in India? Challenges To Socio-Legal Research in IndiaДокумент2 страницыWhy There Has Been No Brandies Brief in India? Challenges To Socio-Legal Research in IndiaSubhaprad MohantyОценок пока нет

- Werewere FelaДокумент17 страницWerewere FelaStacy HardyОценок пока нет

- CDP MCQs - Child Development & Pedagogy (CDP) MCQ Questions With AnswerДокумент4 страницыCDP MCQs - Child Development & Pedagogy (CDP) MCQ Questions With AnswerPallav JainОценок пока нет

- An Overview On Co-Operative Societies in BangladeshДокумент11 страницAn Overview On Co-Operative Societies in BangladeshAlexander DeckerОценок пока нет

- Solucionario Capitulo 13 Física Serway and FaughnДокумент13 страницSolucionario Capitulo 13 Física Serway and FaughnRafael Colindres100% (1)

- Mechanics of Deformable Bodies Module 6Документ65 страницMechanics of Deformable Bodies Module 6stephaniejeancortez522Оценок пока нет

- Maxwell's EquationsДокумент1 страницаMaxwell's EquationsAlemKomićОценок пока нет

- Oracle Rman Duplicate Database FeatureДокумент3 страницыOracle Rman Duplicate Database Featuremartin_seaОценок пока нет

- Chemistry 102 Experiment 8 ColorimetryДокумент7 страницChemistry 102 Experiment 8 ColorimetryDaniel MedeirosОценок пока нет

- Ôn HSG - P5-HandoutДокумент4 страницыÔn HSG - P5-HandoutMinh ChâuОценок пока нет

- Evacuated Flat Plate Collector PDFДокумент2 страницыEvacuated Flat Plate Collector PDFMattОценок пока нет

- 18 SSBДокумент162 страницы18 SSBapi-3806887Оценок пока нет

- ESE 18 Cut Offs English PDFДокумент1 страницаESE 18 Cut Offs English PDFkishan singhОценок пока нет

- Redshift C4D Material Pack 3 Helpful TipsДокумент21 страницаRedshift C4D Material Pack 3 Helpful TipsDreck FresseОценок пока нет

- Concept MappingДокумент26 страницConcept Mappingdbryant0101100% (16)