Академический Документы

Профессиональный Документы

Культура Документы

46GDP QPSKDigitalClockRecoveryandChannelEqualization

Загружено:

hcdung18Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

46GDP QPSKDigitalClockRecoveryandChannelEqualization

Загружено:

hcdung18Авторское право:

Доступные форматы

Single Chip 46 Gb/s DP-QPSK Digital Clock Recovery and Channel Equalization Performance in the Presence of CD, PMD,

and Ultra-fast SOP Rotation Rates Exceeding 20 krad/s

S.M. R. Motaghiannezam, J. Cho, D. Tauber, M. Hueda, D. Crivelli, O. Agazzi, and N. Swenson

ClariPhy Communications,7585 Irvine Center Drive, Irvine, CA 92618 Reza.Motaghian@clariphy.com

Abstract: We demonstrate performance of a single chip 46 Gb/s coherent DP-QPSK transceiver. An OSNR penalty <0.9 dB is shown for 56,862 ps/nm CD, and up to 100 ps DGD, 4000 ps2 SOPMD, and 22,000 rad/s polarization rotation rate.

OCIS codes: (060.2330) Fiber optics communications; (060.1660) Coherent communications

1. Introduction Recent progress in coherent optical communications technology has opened new horizons for ultra-long haul transmission and high spectral efficiency modulation formats in long-haul and metropolitan links. Advanced digital signal processing (DSP) techniques and coherent detection provide efficient and economic solutions for managing fiber optic impairments such as chromatic dispersion (CD) and polarization mode dispersion (PMD) [1]. However, there is a need for the integration of the optical transceiver functionalities in CMOS technology to realize the cost effective and large-scale installation of coherent systems. Digital timing phase estimation is necessary for continuous operation of the finite impulse response (FIR) filter during channel equalization and initial convergence. It has been shown that the clock tone fades in the presence of half-baud differential group delay (DGD) and certain received states of polarization (SOP) [2,3]. Moreover, the clock tone is highly sensitive to chromatic dispersion [3,4]. In addition, high SOP rotation rates (SRR) generate fast transitions between low and high clock tone energies, causing the clock recovery loop to lose synchronization in the presence of first order PMD (half-baud DGD) [5]. Thus, a high SOP tracking speed is essential for maintaining the phase detector sensitivity in the presence of PMD, CD, and the high SRR values induced by mechanical vibration and maintenance activities [6,7]. The performance of a coherent optical modem has been reported in the presence of DGD and second order PMD (SOPMD) at SRRs of approximately 10 krad/s for 10 hours [8]. However, the pathological failure region inside the 2-dimensional DGD-SOPMD contour at high SRR values has not been reported, nor has the behavior of the digital clock recovery at points inside this region. This paper describes the performance of a 46 Gb/s single chip 40nm CMOS DP-QPSK transceiver in the presence of 56,862 ps/nm CD, up to 100 ps DGD, and 4000 ps2 SOPMD, with 22,000 rad/s SOP rotation rate at the receiver. The chip uses a bulk chromatic dispersion (BCD) equalizer and a 4-dimensional feed-forward equalizer to compensate channel degradations. For the first time, we identify the DGD/SOPMD failure region of the square based-clock recovery that utilizes the wave difference method (WDM) [9]. Our experimental results show that the derived failure region is caused by loss of clock synchronization. We also demonstrate that clock synchronization can be restored in the failure region with digital algorithms, and can track fast SOP variations up to 22,000 rad/s in several soak tests. We report stable long term performance and <0.9 dB OSNR penalty for a 46 Gb/s DP-QPSK system in the presence of 56,862 ps/nm CD, 43.5 ps DGD, and 22,000 rad/s SRR. Stable performance under these conditions is also demonstrated for up to 935 ps/nm of residual dispersion not compensated by the BCD equalizer. 2. Experimental Setup Figure 1(a) shows the experimental setup of a 46 Gb/s DP-QPSK system. The coherent optical transceiver (CL4010) comprises transmitter, receiver, framer, host interface and AFE functionality in a single CMOS chip. The DSP implements the main receiver functions such as CD and PMD equalization, clock and carrier recovery using a local clock frequency of 718.75MHz. A bulk chromatic dispersion equalizer (BCD) is implemented in the frequency domain to compensate CD using a 512-point FFT and inverse FFT [9]. A fiber length estimator (FLE) algorithm automatically determines the fiber length and CD during the startup and sets the BCD equalizer accordingly. PMD and PDL compensation is realized using a 16-tap T/2 MIMO FFE [9]. A laser with linewidth less than 500 kHz was modulated using an integrated Ti:LiNbO3 single drive MachZehnder modulator (MZM) with ~10 GHz 3-dB bandwidth and V of ~3.5-4.0 V. To generate 46 Gb/s DP-QPSK

optical data streams, the horizontal and vertical in-phase (I) and quadrature (Q) branches were driven by four 11.5Gbaud pseudo-random bit sequences (PRBS) of length 231-1, with 7.8 Vpp electrical signals. The signal was transmitted through a highly dispersive channel, consisting of two pairs of fiber bragg grating based chromatic dispersion emulators (CDE) with 20,000 ps/nm CD per pair (40,000 ps/nm total CD), a 1,000 km SMF-28 fiber link, a higher-order polarization mode dispersion emulator (PMDE), a slow polarization scrambler (Agilent 11896A) before the PMDE, and an ultra-fast polarization scrambler (NovOptel EPS 1000) after the PMDE. The 1,000 km fiber link comprised ten 80 km fiber spans and two 100 km fiber spans with twelve repeaters distributed between them. Repeaters include 2-stage erbium doped fiber amplifier (EDFA) with effective gains of 16 dB and 21 dB for 80 km and 100 km spans, respectively. The fiber link CD of ~ 16,862 ps/nm was measured using a CD analyzer. The Agilent 11896A polarization scrambler was adjusted to scan rate 8 with a measured maximum SRR of ~240 rad/s. The ultra-fast scrambler provided a maximum SRR value of 22,477 rad/s. The measured SRR distribution is shown in Fig. 1b. The launched and received optical powers were set to -2 dBm and -14.5 dBm, respectively. In order to investigate the worst case scenario, a 100 ppm offset was generated between the receiver and transmitter reference clocks.

Fig. 1 (a) Schematic of the experimental setup. OTX, optical transmitter; ORX, optical receiver; SW, switch; VOA, variable optical amplifier; PMDE, higher-order polarization mode dispersion emulator (Fiberpro); CDE, chromatic dispersion emulator (Teraxion); R, repeater; OBPF, optical band pass filter; OSA, optical spectrum analyzer, ASE, amplified spontaneous emission noise source; EDFA, erbium doped fiber amplifier; Pol. Scr, polarization scrambler. (b) Measured state of polarization rotation rate (SRR) distribution for the ultra-fast scrambler.

3. Simulation and Experimental Results In order to investigate the effect of higher-order PMD on the digital clock recovery and channel equalization performance, we used the slow and ultra-fast scramblers and the PMDE, without any CD introduced. Figure 2a presents the simulated 2D clock tone energy map as a function of DGD and SOPMD. The black band depicts the region with low clock tone energy for a detected raised cosine pulse (roll-off factor of 0.5). It is clear the black band starts at DGD=T/2=43.5 ps and extends to the right corner with high DGD and SOPMD values. We performed an experimental study for several DGD-SOPMD points (green and solid red circles) over 10 minutes by using the ultrafast scrambler, setting it to a maximum 22,447 rad/s polarization rotation speed (SRR distribution shown in Fig. 2a). Loss of clock synchronization was observed by turning off the implemented controller algorithm that prevents failures. The solid red circles in Fig. 2a represent DGD/SOPMD points where loss of clock synchronization was recorded; each failure occurred less than one minute after the test commenced. No loss of synchronization was captured over the 10 minutes test for the DGD-SOPMD points represented by the green circles on the border of the failure band. To demonstrate the efficacy of the implemented controller algorithm, we ran tests for greater than 10 hours each at DGD/SOPMD values represented by the green circles in Fig. 2b. We also monitored the digital clock recovery and the MIMO FFE performance in these tests. Our experimental results demonstrate the robustness of digital clock recovery in the presence of pathological DGD-SOPMD points up to 100 ps-4000 ps2 and at polarization rotation speeds up to 22,447 rad/s. Q values are also shown over the test duration for all these pathological points in Fig. 2c. Number of Capture on the x-axis represents successive BER captures during each test. The test durations on the Q plots (Fig. 2c) correspond to the time labeled next to the green circles on Fig. 2b. Q fluctuations were less than 0.15 dB for all the DGD-SOPMD values. The results confirm the chip, with controller algorithm enabled, operates successfully in the demonstrated failure band with negligible OSNR penalty compared to back-to-back (DGD=0 ps and SOPMD = 0 ps2).

Fig. 2 (a) Simulated clock tone energies as a function of DGD-SOPMD for detected 11.5-Gbaud raised cosine pulses and observed loss (solid red circles) and lock (green circles) of synchronization when the controller algorithm is disabled in the DSP. (b) Representative DGD-SOPMD values (green circles) for soak tests >10 hours. (c) Measured Q values for the DGD-SOPMD values (green circles) in Fig. 2b when the controller algorithm is on. Number of Capture on the x-axis represents successive BER captures during each test, to a maximum of 17 hours. (d) Measured Q values for different residual CD values and DGD=T/2=43.5 ps (soak tests over 10 hours).

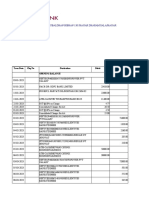

To monitor the digital clock recovery and MIMO FFE performance in a highly dispersive channel, the DP-QPSK modulated signals were transmitted through the experimental link (40,000 ps/nm CD emulation with fiber bragg gratings, 1,000 km SMF-28 fiber (~16862 ps/nm), 43.5 ps DGD, and 22,447 rad/s SRR) shown in Fig. 1a. The automatic FLE calculated the link CD and set the BCD to the calculated value. The measured OSNR penalty was less than 0.9 dB compared to back-to-back. We also introduced residual CD by manually adjusting the BCD so as to leave 170, 340, 510, 680, 850, and 935 ps/nm of CD uncompensated at the MIMO equalizer and at the clock recovery circuit. The Q factors are shown in Fig. 2d. The Q values were calculated using the measured BER (Fig. 2d) and their variations were less than 0.4 dB. These results confirm the CL4010 digital clock recovery and MIMO FFE operate in the presence of ~56,862 ps/nm CD, 43.5 ps (T/2) DGD, up to 935 ps/nm residual CD and greater than 22,000 rad/s polarization rotation rate. 3. References

[1] D. Crivelli, et al., Adaptive Digital Equalization in the Presence of Chromatic Dispersion, PMD, and Phase Noise in Coherent Fiber Optic Systems, Proc. Globecom., pp. 2545-2551, 2004. [2] D. Zibar, et al., Analysis and Dimensioning of Fully Digital Clock Recovery for 112 Gb/s Coherent Polmux QPSK Systems, ECOC 2009, paper 7.3.4. [3] Han Sun and Kuang-Tsan Wu, A Novel Dispersion and PMD Tolerant Clock Phase Detector, OFC 2011, OMJ4. [4] M. Kuschnerov, et al., Joint equalization and timing recovery for coherent fiber optic receivers, ECOC 2008, MO.3.D.3. [5] D. Zibar, et al., Experimental investigation and digital compensation of DGD for 112 Gb/s PDM-QPSK clock recovery, Opt. Express, vol. 19, issue 26, pp. B429-B439, 2011. [6] M. Boroditsky, et al., Polarization Dynamics in Installed Fiberoptic Systems, in Proc LEOS, 2005, paper TuCC1, pp. 414-415. [7] P. Krummrich, et al., Field Trial on statistics of fast polarization changes in long haul WDM transmission systems, in Proc. OFC 2005, paper OThT6. [8] J. Rahn, et al., Real-Time PMD Tolerance Measurements of a PIC-Based 500 Gb/s Coherent Optical Modem, JLT, vol. 30, no. 17, pp. 2907-2912, 2012. [9] T. Suzuki, et al., Line Equalizer for a Digital Subscriber Loop Employing Switched Capacitor Technology, IEEE Trans. on Comm., vol. 30, no. 9, pp. 2074-2082, Sep. 1982. [10] D. Crivelli, et al., A 40nm CMOS single-chip 50Gb/s DP-QPSK/BPSK transceiver with electronic dispersion compensation for coherent optical channels, ISSCC 2012, 328.

Вам также может понравиться

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Digital Communication A Discrete Time ApproachДокумент46 страницDigital Communication A Discrete Time Approachchinmay2882Оценок пока нет

- OFC13 Review Elastic JiaweiДокумент20 страницOFC13 Review Elastic Jiaweihcdung18Оценок пока нет

- Corning® LEAF® Optical Fiber: Product InformationДокумент0 страницCorning® LEAF® Optical Fiber: Product Informationhcdung18Оценок пока нет

- 05032902Документ3 страницы05032902hcdung18Оценок пока нет

- MANET ExtensionsДокумент10 страницMANET ExtensionsSyed Sakil AhmedОценок пока нет

- Blocking Probabilities of Optical Burst Switching Networks Based On Reduced Load Fixed Point ApproximationsДокумент11 страницBlocking Probabilities of Optical Burst Switching Networks Based On Reduced Load Fixed Point Approximationshcdung18Оценок пока нет

- Ant-DSR: Cache Maintenance Based Routing Protocol For Mobile Ad-Hoc NetworksДокумент6 страницAnt-DSR: Cache Maintenance Based Routing Protocol For Mobile Ad-Hoc Networkshcdung18Оценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (120)

- Simple Enzymes Kinetics and Kinetics ModelДокумент14 страницSimple Enzymes Kinetics and Kinetics ModelSidra-tul MuntahaОценок пока нет

- (Polish Journal of Sport and Tourism) The Estimation of The RAST Test Usefulness in Monitoring The Anaerobic Capacity of Sprinters in AthleticsДокумент5 страниц(Polish Journal of Sport and Tourism) The Estimation of The RAST Test Usefulness in Monitoring The Anaerobic Capacity of Sprinters in AthleticsAfizieОценок пока нет

- Chain: SRB Series (With Insulation Grip)Документ1 страницаChain: SRB Series (With Insulation Grip)shankarОценок пока нет

- 2017LR72 - SUMMARY REPORT Final 03052020Документ72 страницы2017LR72 - SUMMARY REPORT Final 03052020Dung PhamОценок пока нет

- Literature Review - Part Time Job Among StudentДокумент3 страницыLiterature Review - Part Time Job Among StudentMarria65% (20)

- University of Ghana: This Paper Contains Two Parts (PART I and PART II) Answer All Questions From Both PARTSДокумент3 страницыUniversity of Ghana: This Paper Contains Two Parts (PART I and PART II) Answer All Questions From Both PARTSPhilip Pearce-PearsonОценок пока нет

- What Is Urban PlanningДокумент33 страницыWhat Is Urban PlanningDivine Grace FernandoОценок пока нет

- The Perception of Luxury Cars MA Thesis 25 03Документ60 страницThe Perception of Luxury Cars MA Thesis 25 03Quaxi1954Оценок пока нет

- 3-Phase Short-Circuit Current (Isc) at Any Point Within A LV Installation - Electrical Installation GuideДокумент6 страниц3-Phase Short-Circuit Current (Isc) at Any Point Within A LV Installation - Electrical Installation GuideYuukinoriОценок пока нет

- HPSC HCS Exam 2021: Important DatesДокумент6 страницHPSC HCS Exam 2021: Important DatesTejaswi SaxenaОценок пока нет

- Zillah P. Curato: ObjectiveДокумент1 страницаZillah P. Curato: ObjectiveZillah CuratoОценок пока нет

- Catalogue - Central Battery SystemДокумент12 страницCatalogue - Central Battery SystemarifzakirОценок пока нет

- Calendar of Activities A.Y. 2015-2016: 12 Independence Day (Regular Holiday)Документ3 страницыCalendar of Activities A.Y. 2015-2016: 12 Independence Day (Regular Holiday)Beny TawanОценок пока нет

- 2023 2024 Syllabus PDFДокумент23 страницы2023 2024 Syllabus PDFRika DianaОценок пока нет

- Macros and DirectiveДокумент7 страницMacros and DirectiveAbdul MoeedОценок пока нет

- XXXX96 01 01 2023to28 08 2023Документ18 страницXXXX96 01 01 2023to28 08 2023dabu choudharyОценок пока нет

- Unilever PakistanДокумент26 страницUnilever PakistanElie Mints100% (3)

- Su Poder en El Espiritu Santo Your Power in The Holy Spirit Spanish Edition by John G Lake PDFДокумент4 страницыSu Poder en El Espiritu Santo Your Power in The Holy Spirit Spanish Edition by John G Lake PDFRodrigo MendezОценок пока нет

- Unit 3: Theories and Principles in The Use and Design of Technology Driven Learning LessonsДокумент5 страницUnit 3: Theories and Principles in The Use and Design of Technology Driven Learning Lessons서재배Оценок пока нет

- HAF350A User ManualДокумент14 страницHAF350A User ManualUEEОценок пока нет

- Lecture BouffonДокумент1 страницаLecture BouffonCarlos Enrique GuerraОценок пока нет

- General Return Service Agreement (RSA) GuidelinesДокумент2 страницыGeneral Return Service Agreement (RSA) GuidelinesJune Francis AngОценок пока нет

- Handout Waste Catch BasinДокумент2 страницыHandout Waste Catch BasinJonniel De GuzmanОценок пока нет

- Corrosion Performance of Mild Steel and GalvanizedДокумент18 страницCorrosion Performance of Mild Steel and GalvanizedNarasimha DvlОценок пока нет

- Gold Loan Application FormДокумент7 страницGold Loan Application FormMahesh PittalaОценок пока нет

- The Sandbox Approach and Its Potential For Use inДокумент13 страницThe Sandbox Approach and Its Potential For Use invalentina sekarОценок пока нет

- 835 (Health Care Claim PaymentAdvice) - HIPAA TR3 GuideДокумент306 страниц835 (Health Care Claim PaymentAdvice) - HIPAA TR3 Guideअरूण शर्माОценок пока нет

- Oracle SOA Suite Oracle Containers For J2EE Feature Overview OC4JДокумент10 страницOracle SOA Suite Oracle Containers For J2EE Feature Overview OC4JLuis YañezОценок пока нет

- Construction Claims and Contract Admin CPDДокумент40 страницConstruction Claims and Contract Admin CPDCraig FawcettОценок пока нет

- Richardson ResumeДокумент3 страницыRichardson Resumeapi-549248694Оценок пока нет