Академический Документы

Профессиональный Документы

Культура Документы

Prac 1

Загружено:

Cristhian Garcia VillarroelОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Prac 1

Загружено:

Cristhian Garcia VillarroelАвторское право:

Доступные форматы

DISEO DE SISTEMAS DIGITALES II CONCVERCIN AD/DA OBJETIVO: Disear un programa para el pic 18f4550 encargado de realizar la medicin del

periodo y la amplitud de una seal senoidal. DESARROLLO: CIRCUITTO. Para poder utilizar de una manera optima el rango de conversin de pic (0-5V) es necesario realizar una adaptacin de nivel de tencin, ya que el pic solo reconoce magnitudes positivas; para este propsito utilizamos un circuito desplazador de nivel con un amplificador operacional Para la parte del conversor analgico-digital utilizamos una configuracin R-2R

La onda senoidal que se ve a la par de la digitalizada (seal de salida del conversor A/D) es la seal original, la seal senoidal que se ve en la parte superior es la seal de salida del circuito desplazador de nivel.

CODIGO. #include <p18F4550.h> #include <adc.h> #include <stdlib.h> #include <delays.h> int result; void main( void ) { OpenADC( ADC_FOSC_64 & ADC_RIGHT_JUST & ADC_0TAD, ADC_CH0 & ADC_INT_OFF,ADC_VREFPLUS_VDD,15 ); while(1){ Delay10TCYx( 5 ); // Delay for 50TCY ConvertADC(); // Start conversion while( BusyADC() ); // Wait for completion result = ReadADC(); // Read result PORTD=result; } }

CUESTIONARIO: Explicar detalladamente el comportamiento del circuito.

En la entrada se tiene una fuente senoidal que genera una seal, la cual es desplazada en nivel por medio de un circuito sumador entre la fuente senoidal y un voltaje continuo utilizando un amplificador operacional como base de esta etapa, a la salida del amplificador la seal tambin senoidal sufre un desplazamiento en magnitud de modo tal que todos los valores que puede tomar la seal son positivos. Esta seal resultante es implantada en el canal de conversin AN0 del pic el cual realiza internamente la conversin de los datos regulados por medio de un conjunto de resistencias. Explicar detalladamente la configuracin del pic18f4550 necesaria para la conversin AD

Se hace uso de los registros de funcin especial (SFRs) como; Convertidor A/D: ADRESH, ADRESL, ADCON0, ADCON1, etc... Junto con los sistemas de interrupcin.

ADIF: Flag de la interrupcin del convertidor A/D

* ADIF=0: No se ha completado la conversin A/D * ADIF=1: Se ha se ha completado una conversin

ADIE: Bit de habilitacin de la interrupcin del convertidor A/D

* ADIE=0: Interrupcin del convertidor A/D no habilitada * ADIE=1: Interrupcin del convertidor A/D habilitada

ADIP: Bit de seleccin de prioridad de la interrupcin del convertidor A/D

* ADIE=0: Prioridad baja para la interrupcin del convertidor A/D * ADIE=1: Prioridad alta para la interrupcin del convertidor A/D

PCFG3..PCFG0: Bits configuracin de los puertos de conversin A/D. Mediante estos bits se establecen que lneas fsicas (RA5..RA0, RB4..RB0, RE1 y RE0) van a trabajar como entradas del convertidor A/D (Ver Tabla de configuracin de lneas de conversin A/D).

CHS3..CHS0: Bits seleccin del canal de conversin A/D (13 canales) GO/DONE: Bit de inicio y de monitorizacin del estado de la conversin A/D:

* GO/DONE=0: Proceso de conversin parado * GO/DONE=1: Proceso de conversin en marcha

ADON: Bit de habilitacin del convertidor A/D

* ADON=0: Convertidor A/D desactivado * ADON=1: Convertidor A/D activado

VCFG1: Bit de configuracin de la tensin de referencia VREF-:

* VCFG1=0: VREF- se conecta a VSS * VCFG1=1: VREF- se conecta a la lnea fsica RA2

VCFG0: Bit de configuracin de la tensin de referencia VREF+:

* VCFG1=0: VREF+ se conecta a VDD * VCFG1=1: VREF+ se conecta a la lnea fsica RA3 PCFG3..PCFG0: Bits configuracin de los puertos de conversin A/D. Mediante estos bits se establecen las lneas fsicas (RA5..RA0, RB4..RB0, RE1 y RE0) que van a trabajar como entradas del convertidor A/D.

ADFM: Bit de configuracin del tipo de almacenamiento del resultado de la conversin en los registros ADRESH y ADRESL: * ADFM=0: El resultado de la conversin se almacena con justificacin a izquierdas * ADFM=1: El resultado de la conversin se almacena con justificacin a derechas ACQT2..ACQT0: Bits de configuracin del tiempo de adquisicin ADCS2..ADCS0: Bits seleccin de la seal de reloj del convertidor A/D

ADFM: Bit de configuracin del tipo de almacenamiento del resultado de la conversin en los registros ADRESH y ADRESL:

* ADFM=0: El resultado de la conversin se almacena con justificacin a izquierdas * ADFM=1: El resultado de la conversin se almacena con justificacin a derechas

ACQT2..ACQT0: Bits de configuracin del tiempo de adquisicin ADCS2..ADCS0: Bits seleccin de la seal de reloj del convertidor A/D Seleccin del canal de conversin: Para que uno de los 13 canales pueda ser seleccionado, previamente debe haber sido configurado como entrada analgica mediante los bits PCFG3..PCFG0 del registro ADCON1 (A: analgico / D: digital).

Mencionar los tipos de conversores DA que se conoce, con una breve descripcin.

La estructura general que presenta un convertidor D/A es la siguiente:

En donde el LATCH es necesario para que el valor digital de la entrada permanezca en sta el tiempo necesario para que la conversin se lleve a cabo con normalidad. Sin embargo, no siempre es sta la estructura necesaria. En algunas ocasiones los convertidores no poseen el LATCH, o por el contrario no tienen el amplificador de salida, o la red de resistencias no tiene fuente de alimentacin de referencia, etc., en esos casos habr que colocrselo externamente. Veamos ahora algunas redes de resistencias concretas. En general estn compuestas de resistencias e interruptores analgicos colocados en una forma concreta:

RED DE RESISTENCIAS PONDERADAS

Es la estructura ms simple que se puede dar. Como se aprecia fcilmente se trata de un sumador con un interruptor analgico en cada entrada de suma que permite aadirla o no. Dependiendo de que el valor de VREF sea positivo o negativo, obtendremos a la salida una tensin - +. Cada bit del dato digital actuar sobre un interruptor del circuito. As Dn acta sobre SW1, Dn-1 sobre SW2, ....., y D1 sobre SWn. Con ello, la tensin a la salida V0 se obtiene como -IR, el signo - es debido a que hemos supuesto en el dibujo que la tensin de referencia es positiva, y la intensidad I ser la suma de las intensidades que circulen por cada rama...

RED DE RESISTENCIAS R-2R

La estructura mostrada presenta una gran simetra en el conjunto de resistencias slo roto por ambos extremos. En el izquierdo aparece una resistencia 2R y el derecho una fuente de tensin Vref. Es importante resaltar el hecho de que todos los extremos de las resistencias de 2R conectados a un interruptor, poseen tensin nula (tierra), tanto si el interruptor est abierto como si est cerrado: si est abierto (0) ==> est conectado a tierra directamente y si est a cerrado (1) ==> est conectado a una barra que llega al terminal inversor del amplificador que por tierra virtual, tambin est a 0V. Con esto podemos ver que las dos primeras resistencias de 2R (las de ms a la izquierda) se encuentran en paralelo, siendo la resistencia equivalente igual a R. Esta

resistencia equivalente (R) est en serie con la siguiente resistencia, cuyo valor tambin es R. Por tanto el conjunto ser de 2R. Esta resistencia de 2R vuelve a estar en paralelo con la siguiente resistencia de 2R y con ello se repite el proceso hasta llegar al final del circuito.

Вам также может понравиться

- Inf Tec 2020 0005 00Документ2 страницыInf Tec 2020 0005 00Cristhian Garcia VillarroelОценок пока нет

- Inf Tec 2021 0010 00Документ2 страницыInf Tec 2021 0010 00Cristhian Garcia VillarroelОценок пока нет

- Inf Tec 2020 0003 00Документ3 страницыInf Tec 2020 0003 00Cristhian Garcia VillarroelОценок пока нет

- Inf Tec 2020 0004 00Документ2 страницыInf Tec 2020 0004 00Cristhian Garcia VillarroelОценок пока нет

- Inf Tec 2021 0014 00Документ2 страницыInf Tec 2021 0014 00Cristhian Garcia VillarroelОценок пока нет

- Procedimiento de Manejo Del Chimango Horizontal # 1Документ4 страницыProcedimiento de Manejo Del Chimango Horizontal # 1Cristhian Garcia VillarroelОценок пока нет

- Inf Tec 2021 0011 00Документ2 страницыInf Tec 2021 0011 00Cristhian Garcia VillarroelОценок пока нет

- Procedimiento de Manejo Del Chimango Horizontal # 3Документ4 страницыProcedimiento de Manejo Del Chimango Horizontal # 3Cristhian Garcia VillarroelОценок пока нет

- Inf Tec 2021 0013 00Документ2 страницыInf Tec 2021 0013 00Cristhian Garcia VillarroelОценок пока нет

- EX2.100 NS 1566 Manual TécnicoДокумент80 страницEX2.100 NS 1566 Manual TécnicoCristhian Garcia VillarroelОценок пока нет

- Inf Tec 2021 0009 00Документ2 страницыInf Tec 2021 0009 00Cristhian Garcia VillarroelОценок пока нет

- Procedimiento de Manejo Del Chimango Horizontal # 2Документ4 страницыProcedimiento de Manejo Del Chimango Horizontal # 2Cristhian Garcia VillarroelОценок пока нет

- 1742848Документ25 страниц1742848Cristhian Garcia VillarroelОценок пока нет

- Encajonadora Automática EX2.100Документ28 страницEncajonadora Automática EX2.100Cristhian Garcia VillarroelОценок пока нет

- Secuencia CleanerДокумент1 страницаSecuencia CleanerCristhian Garcia VillarroelОценок пока нет

- FraganciaДокумент2 страницыFraganciaCristhian Garcia VillarroelОценок пока нет

- Encajonadora Automática EX2.100Документ28 страницEncajonadora Automática EX2.100Cristhian Garcia VillarroelОценок пока нет

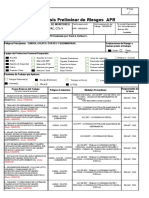

- APR Sistema de Monitoreo de Energia (Sentron PAC) - Planta - EnzimaticaДокумент3 страницыAPR Sistema de Monitoreo de Energia (Sentron PAC) - Planta - EnzimaticaCristhian Garcia VillarroelОценок пока нет

- APR Sist UPS (Planta Jabon - Pailas)Документ2 страницыAPR Sist UPS (Planta Jabon - Pailas)Cristhian Garcia VillarroelОценок пока нет

- 1742848Документ25 страниц1742848Cristhian Garcia VillarroelОценок пока нет

- APR Sist UPS (Playa de Tanques - Torre Industrial)Документ2 страницыAPR Sist UPS (Playa de Tanques - Torre Industrial)Cristhian Garcia VillarroelОценок пока нет

- 1742848Документ25 страниц1742848Cristhian Garcia VillarroelОценок пока нет

- Rev I Pa Al 01072019 FinalДокумент8 страницRev I Pa Al 01072019 FinalCristhian Garcia VillarroelОценок пока нет

- FINO HistorianДокумент9 страницFINO HistorianCristhian Garcia VillarroelОценок пока нет

- Apr Cambio Valvulas Deo2Документ2 страницыApr Cambio Valvulas Deo2Cristhian Garcia VillarroelОценок пока нет

- Test de Personalidad: en Bajo Grado en Grado Medio en Alto Grado en El Más Alto GradoДокумент4 страницыTest de Personalidad: en Bajo Grado en Grado Medio en Alto Grado en El Más Alto GradoCristhian Garcia VillarroelОценок пока нет

- Curriculum - José Francisco Orellana GarcíaДокумент13 страницCurriculum - José Francisco Orellana GarcíaCristhian Garcia VillarroelОценок пока нет

- APR Sist UPS (Playa de Tanques - Torre Industrial)Документ2 страницыAPR Sist UPS (Playa de Tanques - Torre Industrial)Cristhian Garcia VillarroelОценок пока нет

- Planta Cochabamba GeneralДокумент1 страницаPlanta Cochabamba GeneralCristhian Garcia VillarroelОценок пока нет

- OMNITREND Center Installation LIT 82.201 012018 EsДокумент32 страницыOMNITREND Center Installation LIT 82.201 012018 EsCristhian Garcia VillarroelОценок пока нет

- Fisica CanДокумент9 страницFisica Canwilfred coboОценок пока нет

- Cálculo de Parámetros en LíneasДокумент128 страницCálculo de Parámetros en Líneaswilsson perezОценок пока нет

- Metodologia de Lineas Energizadas en Mantenimiento PDFДокумент90 страницMetodologia de Lineas Energizadas en Mantenimiento PDFangel jimenezОценок пока нет

- Diseño y Construcción de Una Bobina de Tesla Didáctica Con Arduino .Документ7 страницDiseño y Construcción de Una Bobina de Tesla Didáctica Con Arduino .osmar0% (2)

- Exa Sep 1213 PDFДокумент6 страницExa Sep 1213 PDFHUGASO1Оценок пока нет

- Evidencia Cuadro Comparativo Potencia Activa Reactiva y AparenteДокумент5 страницEvidencia Cuadro Comparativo Potencia Activa Reactiva y Aparentefelipe berrioОценок пока нет

- Conexion de Transformadores Trifasicos PDFДокумент58 страницConexion de Transformadores Trifasicos PDFDENYS ALFREDO SICLLA MACHICAOОценок пока нет

- Protección de Sistemas Eléctricos de PotenciaДокумент59 страницProtección de Sistemas Eléctricos de PotenciaAlejandro Vasquez50% (2)

- Practica 1 Lab Control AutomaticoДокумент9 страницPractica 1 Lab Control Automaticobrianj01Оценок пока нет

- Instalaciones Eléctricas IДокумент62 страницыInstalaciones Eléctricas IYulianaL92% (12)

- Esquemas Eléctricos de Las Centrales de GeneraciónДокумент2 страницыEsquemas Eléctricos de Las Centrales de GeneraciónJuan ChambersОценок пока нет

- Informe Motores MonofasicosДокумент17 страницInforme Motores MonofasicosJuan Cruz CapezioОценок пока нет

- Waira - 553AE (H Q) 22 00 - IMДокумент20 страницWaira - 553AE (H Q) 22 00 - IMEmilio VerónОценок пока нет

- Descargadores de Potencia Funcionamiento EsquemaДокумент3 страницыDescargadores de Potencia Funcionamiento EsquemaFrederic JaimesОценок пока нет

- Transformadores de MedidaДокумент5 страницTransformadores de MedidaRoberto Echeverria AlfaroОценок пока нет

- Proyecto Instalaciones Eléctricas IndustrialesДокумент17 страницProyecto Instalaciones Eléctricas IndustrialesJonathan VeraОценок пока нет

- Resolucion de Calculo de RadioenlaceДокумент5 страницResolucion de Calculo de RadioenlaceJHERY ALEXANDER GARCIA TAIPEОценок пока нет

- Unidad 3 - Practica 3Документ17 страницUnidad 3 - Practica 3MonseОценок пока нет

- CONTADORESДокумент17 страницCONTADORESEnrique Diaz RubioОценок пока нет

- Programa MantenimientoДокумент27 страницPrograma MantenimientoyelisaОценок пока нет

- Solución de Redes Por El Metodo de Corrientes de MallaДокумент1 страницаSolución de Redes Por El Metodo de Corrientes de MallaRené ChapaОценок пока нет

- Tipos de AerogeneradoresДокумент20 страницTipos de AerogeneradoresPablo muñozОценок пока нет

- Mediciones eléctricas con multímetro analógicoДокумент28 страницMediciones eléctricas con multímetro analógicoOmaar Pineapple100% (1)

- Corrientes de InrushДокумент9 страницCorrientes de InrushRoly Pariona SilvaОценок пока нет

- Ejercicios de TransistoresДокумент5 страницEjercicios de TransistoresGabriel FerrarioОценок пока нет

- Recuperativa 5aДокумент2 страницыRecuperativa 5adannyОценок пока нет

- Constante de PlankДокумент5 страницConstante de PlankAlex MazariegosОценок пока нет

- Derecho de Via y Distancias Eléctricas de Seguridad en Líneas Electricas de Alta TensiónДокумент3 страницыDerecho de Via y Distancias Eléctricas de Seguridad en Líneas Electricas de Alta TensiónRenzo RochaОценок пока нет

- Medidor multifunción DM9200 instructivoДокумент258 страницMedidor multifunción DM9200 instructivoOscar EduardoОценок пока нет

- Mapas Conceptuales DiodosДокумент5 страницMapas Conceptuales DiodosBrayan Sanchez100% (1)