Академический Документы

Профессиональный Документы

Культура Документы

X86 Opcode Reference 64-Bit Edition: General, System, x87 FPU, MMX, SSE (1), SSE2, SSE3, SSSE3 Opcodes

Загружено:

Stewart HendersonОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

X86 Opcode Reference 64-Bit Edition: General, System, x87 FPU, MMX, SSE (1), SSE2, SSE3, SSSE3 Opcodes

Загружено:

Stewart HendersonАвторское право:

Доступные форматы

imul unpcklps inc repnz sbb bswapcmovna sysenter pmaxsw mov jnle psubq stccmp subss fsqrt stosd

fincstp fstp outsw mfence leave retn phaddsw psadbwidiv cmovpe str smsw fxam finit fcmovnbe out jnle push verr ror shrd mulss cvtpi2pd rdtsc daa sal fiadd bts sgdt fnsave nop cwde int fbld psllq add pushad movsxd emms hlt xor fldlg2 sub phaddd pmovmskb fldz aaa wait cvttss2si fnclex movq movntpd setnge fsubrbsf xlatb movlhps fstenv addsubpd cdq movddup lsl haddpd subps fabs comisd jp lidt jnae scasw movntdq clflush not divps pmuludq lss rcl jrcxz rcpps xchg pop sar orpd

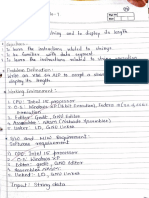

X86 Opcode Reference 64-bit Edition

general, system, x87 FPU, MMX, SSE(1), SSE2, SSE3, SSSE3 opcodes

ref.x86asm.net

Advertisement

X86 Opcode Reference, 64-bit Edition general, system, x87 FPU, MMX, SSE(1), SSE2, SSE3, SSSE3 opcodes Copyright MazeGen First Edition, July 2008 Errata: http://ref.x86asm.net/errata/64/opcode Karel Lejska Bayerova 8 Brno 60200 Czech Republic Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation, without intent to infringe. For comments, suggestions, questions or bug reports, please contact mazegen@gmail.com For booking a computer-related ad in this reference, please contact mazegen@gmail.com

Quick Guide mnemonic: Instruction mnemonic itself. If the mnemonic is set up using italic, there is no oficial mnemonic and the present one is just a suggested one op1op4: Up to four instruction operands. Implicate operands are set up using italic. Modified operands are bold. Implicate [RSP] operand is not indicated. If the op4 column contains only three dots '...', there are more than four operands pf: Prefix value, or if Primary opcode is present, fixed extraordinary prefix 0F: Dedicated for 0x0F two-byte prefix po: Primary opcode. Second opcode byte in case of multi-byte opcodes. +r means a register code, from 0 through 7, added to the value so: Secondary opcode. Fixed appended value to the primary opcode o: Register/Opcode field. Either the value of an opcode extension (values from 0 through 7) or r indicates that the ModR/M byte contains a register operand and an r/m operand proc: Indicates the instruction's introductory processor. If the column is empty, it means that the instruction is supported since first implementation of Intel EM64T architecture. st: Indicates how is the instruction documented in the Intel manuals. D means fully documented. M means documented only marginally. U undocumented at all. Empty column means D m: Indicates the mode in which is the instruction valid. Virtual-8086 Mode and SMM is not taken into account. R applies for real , protected and 64-bit mode. P applies for protected and 64-bit mode. E applies for 64-bit mode. If this column is empty, it means R rl: The ring level, which is the instruction valid from (3 or 0). f indicates that the level depends on further flag(s) x: For general instructions, L indicates that the instruction is basically valid with LOCK (0xF0) prefix. For x87 FPU instructions, s incidates that the opcode performs additional push of a value to the register stack, p incidates that the opcode performs additional pop of the register stack, P pops twice iext: The instruction extension group, which was the opcode released on tested f, modif f, def f, undef f: For RFlags register, indicates these flags using odiszapc pattern. Present flag fits in with the appropriate group. For x87 FPU flags, indicates these flags using 1234 x87 FPU flag pattern. Present flag fits in with the appropriate group. f values: For RFlags register, indicates the values of flags, which are always set or cleared, using casesensitive odiszapc flag pattern. Lowercase flag means cleared flag, uppercase means set flag. For x87 FPU flags, indicates these flags using 1234 x87 FPU flag pattern. Present flag holds its value description, notes: Generic description

Credits: Christian Ludloff, Martin Mocko (vid), Anthony Lopes, Aquila, EliCZ, Cephexin ISBN 978-80-254-2350-9

ref.x86asm.net

Visit http://ref.x86asm.net for detailed guide.

One-byte General and System Instructions

pf 0F po so o proc st m rl x mnemonic 00 01 02 03 04 05 08 09 0A 0B 0C 0D 0F 10 11 12 13 14 15 18 19 1A 1B 1C 1D 20 21 22 23 24 25 26 28 29 2A 2B 2C 2D 2E 2E 30 31 r r E E r r r r E r r r r r r r r r r r r r r r r r r r r L ADD L ADD ADD ADD ADD ADD L OR L OR OR OR OR OR r/m8, r/m16/32/64, r8, r16/32/64, AL, rAX, r/m8, r/m16/32/64, r8, r16/32/64, AL, rAX, op1 r8 r16/32/64 r/m8 r/m16/32/64 imm8 imm16/32 r8 r16/32/64 r/m8 r/m16/32/64 imm8 imm16/32 op2 op3 op4 iext tested f modif f def f undef f f values description, notes Add Add Add Add Add Add o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc

o..szapc o..sz.pc .....a.. o......c Logical Inclusive OR o..szapc o..sz.pc .....a.. o......c Logical Inclusive OR o..szapc o..sz.pc .....a.. o......c Logical Inclusive OR o..szapc o..sz.pc .....a.. o......c Logical Inclusive OR o..szapc o..sz.pc .....a.. o......c Logical Inclusive OR o..szapc o..sz.pc .....a.. o......c Logical Inclusive OR

Two-byte Instructions L ADC L ADC ADC ADC ADC ADC L SBB L SBB SBB SBB SBB SBB L AND L AND AND AND AND AND null L SUB L SUB SUB SUB SUB SUB r/m8, r/m16/32/64, r8, r16/32/64, AL, rAX, r8 r16/32/64 r/m8 r/m16/32/64 imm8 imm16/32 o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc r/m8, r/m16/32/64, r8, r16/32/64, AL, rAX, r/m8, r8 r16/32/64 r/m8 r/m16/32/64 imm8 imm16/32 .......c o..szapc o..szapc .......c o..szapc o..szapc .......c o..szapc o..szapc .......c o..szapc o..szapc .......c o..szapc o..szapc .......c o..szapc o..szapc Add with Carry Add with Carry Add with Carry Add with Carry Add with Carry Add with Carry

r/m16/32/64, r8,

r16/32/64, AL, rAX, r/m8,

ref.x86asm.net

r8 .......c o..szapc o..szapc Integer Subtraction with Borrow r16/32/64 r/m8 .......c o..szapc o..szapc Integer Subtraction with Borrow .......c o..szapc o..szapc Integer Subtraction with Borrow r/m16/32/64 imm8 imm16/32 r8 r16/32/64 r/m8 r/m16/32/64 imm8 imm16/32 .......c o..szapc o..szapc Integer Subtraction with Borrow .......c o..szapc o..szapc .......c o..szapc o..szapc Integer Subtraction with Borrow Integer Subtraction with Borrow o..szapc o..sz.pc .....a.. o......c Logical AND o..szapc o..sz.pc .....a.. o......c Logical AND o..szapc o..sz.pc .....a.. o......c Logical AND o..szapc o..sz.pc .....a.. o......c Logical AND o..szapc o..sz.pc .....a.. o......c Logical AND o..szapc o..sz.pc .....a.. o......c Logical AND Null Prefix in 64-bit Mode Subtract Subtract Subtract Subtract Subtract Subtract (branch hint prefixes have no effect in 64-bit mode) Null Prefix in 64-bit Mode

r/m16/32/64, r8, r16/32/64, AL, rAX,

undefined null L XOR L XOR r/m8, r/m16/32/64, r8 r16/32/64

o..szapc o..sz.pc .....a.. o......c Logical Exclusive OR o..szapc o..sz.pc .....a.. o......c Logical Exclusive OR

pf 0F po so o proc st m rl x mnemonic 32 33 34 35 36 38 39 3A 3B 3C 3D 3E 3E 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50+r 58+r 63 64 65 65 66 66 67 68 69 6A 6B 6C f1 M r E E E E E E E E E E E E E E E E E E E E E E r r r r E r r XOR XOR XOR XOR null CMP CMP CMP CMP CMP CMP r/m8, r8,

op1 r/m8 r16/32/64, AL, rAX,

op2

op3

op4 iext tested f modif f

def f

undef f f values description, notes

o..szapc o..sz.pc .....a.. o......c Logical Exclusive OR o..szapc o..sz.pc .....a.. o......c Logical Exclusive OR o..szapc o..sz.pc .....a.. o......c Logical Exclusive OR o..szapc o..sz.pc .....a.. o......c Logical Exclusive OR Null Prefix in 64-bit Mode

r/m16/32/64 imm8 imm16/32

r8 r16/32/64 r/m8 r/m16/32/64 imm8 imm16/32

o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc o..szapc

Compare Two Operands Compare Two Operands Compare Two Operands Compare Two Operands Compare Two Operands Compare Two Operands (branch hint prefixes have no effect in 64-bit mode) Null Prefix in 64-bit Mode Access to new 8-bit registers Extension of the r/m field, base field, or opcode reg field Extension of the SIB index field REX.X and REX.B combination Extension of the ModR/M reg field REX.R and REX.B combination REX.R and REX.X combination REX.R, REX.X and REX.B combination

r/m16/32/64, r8, r16/32/64, AL, rAX,

undefined null REX REX.B REX.X REX.XB REX.R REX.RB REX.RX REX.RXB REX.W REX.WB REX.WX REX.WXB REX.WR REX.WRB REX.WRX REX.WRXB PUSH POP MOVSXD r64/16 r64/16 r32/64, r/m32

ref.x86asm.net

64 Bit Operand Size REX.W and REX.B combination REX.W and REX.X combination REX.W and REX.R combination Pop a Value from the Stack Move with Sign-Extension GS GS segment override prefix Operand-size override prefix sse2 Precision-size override prefix Address-size override prefix imm16/32 r16/32/64, imm8 r16/32/64, m8, m8, r/m16/32/64, imm8 DX DX .d...... o..szapc o......c ...szap. r/m16/32/64, imm16/32 o..szapc o......c ...szap.

REX.W, REX.X and REX.B combination

REX.W, REX.R and REX.B combination REX.W, REX.R and REX.X combination REX.W, REX.R, REX.X and REX.B combination Push Word, Doubleword or Quadword Onto the Stack

undefined GS

(branch hint prefixes have no effect in 64-bit mode)

undefined no mnemonic no mnemonic no mnemonic PUSH IMUL PUSH IMUL INS INSB

(used only with Jcc instructions)

Push Word, Doubleword or Quadword Onto the Stack Signed Multiply Push Word, Doubleword or Quadword Onto the Stack Signed Multiply Input from Port to String

Вам также может понравиться

- Opcode32 PreviewДокумент4 страницыOpcode32 PreviewStewart HendersonОценок пока нет

- Instruction32 PreviewДокумент4 страницыInstruction32 PreviewSafiq RosadОценок пока нет

- X86 Opcode and Instruction ReferenceДокумент16 страницX86 Opcode and Instruction Referencebeta2009Оценок пока нет

- Instruction64 PreviewДокумент4 страницыInstruction64 PreviewSafiq RosadОценок пока нет

- MP Practical 7Документ7 страницMP Practical 7C1 314 Krishna GavaneОценок пока нет

- LapackeДокумент10 страницLapackeMario ZamoraОценок пока нет

- MSFencode - Metasploit UnleashedДокумент7 страницMSFencode - Metasploit UnleashedHuols4mОценок пока нет

- La4-Largest NumberДокумент7 страницLa4-Largest NumberVidya Ashok NemadeОценок пока нет

- Micro Topic 6 PDFДокумент17 страницMicro Topic 6 PDFroshaanОценок пока нет

- Name Value DescriptionДокумент35 страницName Value Descriptionyashdoshi89Оценок пока нет

- Programacion Pic en Pascal InglesДокумент210 страницProgramacion Pic en Pascal InglesRamon Garcia PrietoОценок пока нет

- Dwnload Full Atmel Avr Microcontroller Mega and Xmega in Assembly and C 1st Edition Han Way Huang Test Bank PDFДокумент36 страницDwnload Full Atmel Avr Microcontroller Mega and Xmega in Assembly and C 1st Edition Han Way Huang Test Bank PDFkeeling.grownzqrhqv100% (16)

- "%S:%D %D - " "" "Request Method:"Документ8 страниц"%S:%D %D - " "" "Request Method:"Jean PierreОценок пока нет

- Smack The StackДокумент16 страницSmack The StackMarcos Paulo FerreiraОценок пока нет

- Pep 8 PaperДокумент5 страницPep 8 PaperBrent ButlerОценок пока нет

- Pcre 2 TestДокумент33 страницыPcre 2 TestAhmed HassanОценок пока нет

- Computer ArchitectureДокумент16 страницComputer ArchitectureJerika Marie Valdez MartinezОценок пока нет

- 8086 Instruction Set by MeДокумент9 страниц8086 Instruction Set by MeSourav GangulyОценок пока нет

- ANSI C Reserved WordsДокумент17 страницANSI C Reserved WordsJeff BrownОценок пока нет

- Part 2: Benchmarks and Case Studies of Forth Kernels: by Brad RodriguezДокумент1 страницаPart 2: Benchmarks and Case Studies of Forth Kernels: by Brad Rodriguezmichael0richt-880205Оценок пока нет

- SNORT Cheat SheetДокумент10 страницSNORT Cheat Sheetfalfyha75% (4)

- Assemply 2Документ6 страницAssemply 2Ahmed RamadanОценок пока нет

- Introduction To TI MSP430Документ9 страницIntroduction To TI MSP430hickimse1Оценок пока нет

- Register Usage in MIPS ABI: Inf3 Computer Architecture - 2007-2008Документ24 страницыRegister Usage in MIPS ABI: Inf3 Computer Architecture - 2007-2008danej8909Оценок пока нет

- Selected 8086 Instructions: Quick Reference ListДокумент9 страницSelected 8086 Instructions: Quick Reference ListAlvin PestovicОценок пока нет

- Experiment 11 Implementation of Pass 1 of 2 Pass Assembler: Description of The ProblemДокумент4 страницыExperiment 11 Implementation of Pass 1 of 2 Pass Assembler: Description of The Problemahmad ahmadОценок пока нет

- CTF Series Binary ExploitationДокумент51 страницаCTF Series Binary ExploitationPhilemon SundayОценок пока нет

- 05 FpgaДокумент54 страницы05 Fpgasoh_vakili100% (1)

- PS1Документ20 страницPS1Jerome Salazar CaballeroОценок пока нет

- Libro Dspic CompletoДокумент250 страницLibro Dspic CompletoRemigio Clemente Guevara Baculima100% (4)

- Final Exam: 15-213 Introduction To Computer SystemsДокумент17 страницFinal Exam: 15-213 Introduction To Computer SystemsAmina YahayaОценок пока нет

- Block Diagram of Processor (Harvard)Документ48 страницBlock Diagram of Processor (Harvard)Nichita IonutОценок пока нет

- PaX PresentationДокумент37 страницPaX PresentationInevitable Downfall-OfОценок пока нет

- Reference For Lab 1-Assembly Language ProgrammingДокумент15 страницReference For Lab 1-Assembly Language ProgrammingMichel LuОценок пока нет

- Register File: ARM Programmer's ModelДокумент6 страницRegister File: ARM Programmer's ModelRajdeep SiddhapuraОценок пока нет

- PaX PresentationДокумент37 страницPaX PresentationInevitable Downfall-OfОценок пока нет

- R 2 LibcДокумент26 страницR 2 LibcMal ObОценок пока нет

- Lab 4Документ18 страницLab 4Vuong PhạmОценок пока нет

- The ARC ProcessorДокумент10 страницThe ARC ProcessorDaniel LoveraОценок пока нет

- x86-64 Intel Cheat Sheet SummaryДокумент10 страницx86-64 Intel Cheat Sheet SummaryJОценок пока нет

- Signal and Image Processing On The TMS320C54x DSP: Prof. Brian L. EvansДокумент38 страницSignal and Image Processing On The TMS320C54x DSP: Prof. Brian L. EvansPreetham SaigalОценок пока нет

- GDC 2012 March 5-9: Runtime CPU Performance Spike Detection Using Manual and Compiler Automated InstrumentationДокумент9 страницGDC 2012 March 5-9: Runtime CPU Performance Spike Detection Using Manual and Compiler Automated InstrumentationMarkОценок пока нет

- Arquivo: /Home/Spellsinger/Alephone/Alephone97.Txt Página 1 de 24Документ24 страницыArquivo: /Home/Spellsinger/Alephone/Alephone97.Txt Página 1 de 24dont4getОценок пока нет

- Final 8051 PrintoutДокумент78 страницFinal 8051 PrintoutArun JyothiОценок пока нет

- RANCM Param SDR FDD WahyudialiP844023 20230913141059Документ2 056 страницRANCM Param SDR FDD WahyudialiP844023 20230913141059Zulfikar SyariefОценок пока нет

- COMT AssignmentДокумент13 страницCOMT AssignmentKekWОценок пока нет

- Example: Array Scanning SearchingДокумент5 страницExample: Array Scanning SearchingYaikob KebedeОценок пока нет

- Alph Smashing SecurityДокумент28 страницAlph Smashing Securityj4sonlyОценок пока нет

- Microprocessor NotesДокумент8 страницMicroprocessor NotesMerin JesurajОценок пока нет

- Atmel Avr Microcontroller Mega and Xmega in Assembly and C 1st Edition Han-Way Huang Test BankДокумент2 страницыAtmel Avr Microcontroller Mega and Xmega in Assembly and C 1st Edition Han-Way Huang Test Banktestbankloo50% (2)

- LTE MO CommandsДокумент31 страницаLTE MO CommandskumarОценок пока нет

- CPE 185 TestДокумент16 страницCPE 185 TestPaul DyeОценок пока нет

- Assembly Programming Journal 6Документ79 страницAssembly Programming Journal 6AmineBenaliОценок пока нет

- MIPS Reference CardДокумент2 страницыMIPS Reference CardJosé R. BecerraОценок пока нет

- PP User GuideДокумент5 страницPP User GuideAntonio RojasОценок пока нет

- 04 AVR ALU and SREG SetДокумент12 страниц04 AVR ALU and SREG SetDerbendeОценок пока нет

- 2-1 Internal Miaasd: Increment or DecrementДокумент3 страницы2-1 Internal Miaasd: Increment or DecrementscouttypeОценок пока нет

- VIMP Micro QuestionsДокумент68 страницVIMP Micro QuestionsayushnaleОценок пока нет

- IP Routing Protocols All-in-one: OSPF EIGRP IS-IS BGP Hands-on LabsОт EverandIP Routing Protocols All-in-one: OSPF EIGRP IS-IS BGP Hands-on LabsОценок пока нет

- Thiel On Progress and StagnationДокумент102 страницыThiel On Progress and StagnationStewart HendersonОценок пока нет

- Alamos: Nuclear Weapon Fundamentals (U)Документ39 страницAlamos: Nuclear Weapon Fundamentals (U)Stewart HendersonОценок пока нет

- Alamos: Nuclear Weapon Fundamentals (U)Документ39 страницAlamos: Nuclear Weapon Fundamentals (U)Stewart HendersonОценок пока нет

- Alamos: Nuclear Weapon Fundamentals (U)Документ39 страницAlamos: Nuclear Weapon Fundamentals (U)Stewart HendersonОценок пока нет

- Jeffrey Dean CSE Summa Sum1990Документ34 страницыJeffrey Dean CSE Summa Sum1990Stewart HendersonОценок пока нет

- Azure Cosmos DB 2-Cheat Sheet V4-LetterДокумент4 страницыAzure Cosmos DB 2-Cheat Sheet V4-LetterStewart HendersonОценок пока нет

- International Journal of Forecasting: Nassim Nicholas Taleb, Yaneer Bar-Yam, Pasquale CirilloДокумент10 страницInternational Journal of Forecasting: Nassim Nicholas Taleb, Yaneer Bar-Yam, Pasquale CirilloStewart HendersonОценок пока нет

- Cyclic Test Performance MeasurementДокумент99 страницCyclic Test Performance MeasurementStewart HendersonОценок пока нет

- ManualДокумент38 страницManualPham CongОценок пока нет

- The Max Min Hill Climbing Bayesian Network Structure Learning AlgorithmДокумент48 страницThe Max Min Hill Climbing Bayesian Network Structure Learning AlgorithmStewart HendersonОценок пока нет

- Climbing The Density Functional Ladder: Non-Empirical Meta-Generalized Gradient Approximation Designed For Molecules and SolidsДокумент4 страницыClimbing The Density Functional Ladder: Non-Empirical Meta-Generalized Gradient Approximation Designed For Molecules and SolidsStewart HendersonОценок пока нет

- Cooperative Control of Mobile Sensor Networks: Adaptive Gradient Climbing in A Distributed EnvironmentДокумент11 страницCooperative Control of Mobile Sensor Networks: Adaptive Gradient Climbing in A Distributed EnvironmentStewart HendersonОценок пока нет

- Optimizing Sleep To Maximize Performance: Implications and Recommendations For Elite AthletesДокумент9 страницOptimizing Sleep To Maximize Performance: Implications and Recommendations For Elite AthletesStewart HendersonОценок пока нет

- Effect of Green Tea Catechins On Plasma Cholesterol Level in Cholesterol-Fed RatsДокумент10 страницEffect of Green Tea Catechins On Plasma Cholesterol Level in Cholesterol-Fed RatsStewart HendersonОценок пока нет

- A Climbing Image Nudged Elastic Band Method For Finding Saddle Points and Minimum Energy PathsДокумент4 страницыA Climbing Image Nudged Elastic Band Method For Finding Saddle Points and Minimum Energy PathsStewart HendersonОценок пока нет

- ROOT - A C++ Framework For Petabyte Data Storage, Statistical Analysis and VisualizationДокумент33 страницыROOT - A C++ Framework For Petabyte Data Storage, Statistical Analysis and VisualizationStewart HendersonОценок пока нет

- Meta Optimization: Improving Compiler Heuristics With Machine LearningДокумент14 страницMeta Optimization: Improving Compiler Heuristics With Machine LearningStewart HendersonОценок пока нет

- Why You Shouldn't Use Set (And What You Should Use Instead)Документ5 страницWhy You Shouldn't Use Set (And What You Should Use Instead)Stewart HendersonОценок пока нет

- FSA: An Efficient and Flexible C++ Toolkit For Finite State Automata Using On-Demand ComputationДокумент8 страницFSA: An Efficient and Flexible C++ Toolkit For Finite State Automata Using On-Demand ComputationStewart HendersonОценок пока нет

- ws3 1 HundtДокумент10 страницws3 1 HundtColin CarrОценок пока нет

- OpenCL Static C++ Kernel Language ExtensionДокумент12 страницOpenCL Static C++ Kernel Language ExtensionStewart HendersonОценок пока нет

- RCPP IntroductionДокумент19 страницRCPP IntroductionfadfОценок пока нет

- Algorithm 871: A C/C++ Precompiler For Autogeneration of Multiprecision ProgramsДокумент20 страницAlgorithm 871: A C/C++ Precompiler For Autogeneration of Multiprecision ProgramsStewart HendersonОценок пока нет

- s18 DasДокумент20 страницs18 DasStewart HendersonОценок пока нет

- Topographica: Building and Analyzing Map-Level Simulations From Python, C/C++, MATLAB, NEST, or NEURON ComponentsДокумент9 страницTopographica: Building and Analyzing Map-Level Simulations From Python, C/C++, MATLAB, NEST, or NEURON ComponentsStewart HendersonОценок пока нет

- A Practical Flow-Sensitive and Context-Sensitive C and C++ Memory Leak DetectorДокумент14 страницA Practical Flow-Sensitive and Context-Sensitive C and C++ Memory Leak DetectorStewart HendersonОценок пока нет

- ET++ - An Object-Oriented Application Framework in C++Документ12 страницET++ - An Object-Oriented Application Framework in C++Stewart HendersonОценок пока нет

- Order Notation in PracticeДокумент66 страницOrder Notation in PracticeStewart HendersonОценок пока нет

- AT89S52Документ20 страницAT89S52Bhargav GoudОценок пока нет

- History of C Programming LanguageДокумент9 страницHistory of C Programming LanguageRahul LavhandeОценок пока нет

- At91sam7s64 PDFДокумент775 страницAt91sam7s64 PDFManuel Alexandro Alaniz LechugaОценок пока нет

- PSmarkup Plag CheckДокумент5 страницPSmarkup Plag CheckRahul ShindeОценок пока нет

- Interrupts in 8051: Microprocessor Laboratory EE-337Документ11 страницInterrupts in 8051: Microprocessor Laboratory EE-337Ayandev BarmanОценок пока нет

- Atmel 8386 8 and 16 Bit AVR Microcontroller ATxmega64A3U 128A3U 192A3U 256A3U DatasheetДокумент337 страницAtmel 8386 8 and 16 Bit AVR Microcontroller ATxmega64A3U 128A3U 192A3U 256A3U DatasheetBurning XiaoОценок пока нет

- Internal Register DefinitionДокумент3 страницыInternal Register DefinitionAzizul LauОценок пока нет

- About Assemblers - Assembler Algorithm and Data Structures PDFДокумент3 страницыAbout Assemblers - Assembler Algorithm and Data Structures PDFrituraj69Оценок пока нет

- Sap 2 130624231520 Phpapp02Документ23 страницыSap 2 130624231520 Phpapp02Ian RobisoОценок пока нет

- Dalvik BytecodeДокумент11 страницDalvik BytecodeFrann W. ZerosixОценок пока нет

- 8085 Microprocessor UNIT 5Документ5 страниц8085 Microprocessor UNIT 5Er SarbeshОценок пока нет

- Cs1358 Ece Computer ArchitectureДокумент8 страницCs1358 Ece Computer ArchitectureMarimuthu MuthaiyanОценок пока нет

- Texas Placement Paper2011Документ7 страницTexas Placement Paper2011Sangam JindalОценок пока нет

- Computer Organization CS1403: Mayank Pandey, MNNIT, Allahabad, IndiaДокумент76 страницComputer Organization CS1403: Mayank Pandey, MNNIT, Allahabad, IndiaAmit Kumar YadavОценок пока нет

- Software: Computer Software, or Just Software, IsДокумент7 страницSoftware: Computer Software, or Just Software, IsMickyFoleyОценок пока нет

- 12K502 Programmable Logic Controller: Microcontrollers andДокумент6 страниц12K502 Programmable Logic Controller: Microcontrollers andsivaeeinfoОценок пока нет

- Microprocessor FileДокумент93 страницыMicroprocessor FileHarshal AmbatkarОценок пока нет

- Chapter 9 Notes: 9.1 Binary Decoders - Acts Much Like A Switch Statement in The C LanguageДокумент12 страницChapter 9 Notes: 9.1 Binary Decoders - Acts Much Like A Switch Statement in The C LanguageRahul SinghОценок пока нет

- Diagram 1. A Simplified Diagram of The CPUДокумент19 страницDiagram 1. A Simplified Diagram of The CPUutaroОценок пока нет

- Intel 8086 Microprocessor: Microprocessors Have Two Major ComponentsДокумент13 страницIntel 8086 Microprocessor: Microprocessors Have Two Major ComponentsAnonymous L7XrxpeI1zОценок пока нет

- MPMC Course FileДокумент41 страницаMPMC Course FileSetlam Tarun KrishnaОценок пока нет

- Unit 3Документ46 страницUnit 3Vinod Srinivasan100% (1)

- Chapter 8Документ24 страницыChapter 8Syed Ejaz Hussain Abidi100% (1)

- EDSAC2Документ2 страницыEDSAC2Msika AloyceОценок пока нет

- Vliw Processor: Submitted By, Manjiri Phadnis. Neha Naik. Guided By, Prof. M.S. NagmodeДокумент23 страницыVliw Processor: Submitted By, Manjiri Phadnis. Neha Naik. Guided By, Prof. M.S. NagmodeRiyuk Diki StayonthelineОценок пока нет

- 80c196 Users Guide PDFДокумент98 страниц80c196 Users Guide PDFGoutam Biswas100% (1)

- MtechsyllabusДокумент22 страницыMtechsyllabusvirendra_verma5Оценок пока нет

- Architecture and Programming of 8051 MCUДокумент111 страницArchitecture and Programming of 8051 MCUbbshir0Оценок пока нет

- System Software and Machine Architecture: Department of Computer Science National Tsing Hua UniversityДокумент31 страницаSystem Software and Machine Architecture: Department of Computer Science National Tsing Hua UniversitymonajosephjustinОценок пока нет

- PIC16C54Документ84 страницыPIC16C54Wasang Juwi PracihnoОценок пока нет