Академический Документы

Профессиональный Документы

Культура Документы

PIC16F627A/628A/648A: 4.0 Memory Organization

Загружено:

Andrés Gilberto Catalán HernándezИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

PIC16F627A/628A/648A: 4.0 Memory Organization

Загружено:

Andrés Gilberto Catalán HernándezАвторское право:

Доступные форматы

2002 Microchip Technology Inc.

Preliminary DS40044A-page 15

PIC16F627A/628A/648A

4.0 MEMORY ORGANIZATION

4.1 Program Memory Organization

The PIC16F627A/628A/648A has a 13-bit program

counter capable of addressing an 8K x 14 program

memory space. Only the first 1K x 14 (0000h - 03FFh)

for the PIC16F627A, 2K x 14 (0000h - 07FFh) for the

PIC16F628A and 4K x 14 (0000h - 0FFFh) for the

PIC16F648A are physically implemented. Accessing a

location above these boundaries will cause a wrap-

around within the first 1K x 14 space (PIC16F627A), 2K

x 14 space (PIC16F628A) or 4K x 14 space

(PIC16F648A). The RESET vector is at 0000h and the

interrupt vector is at 0004h (Figure 4-1).

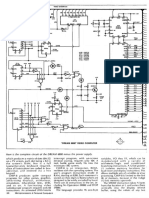

FIGURE 4-1: PROGRAM MEMORY MAP

AND STACK

4.2 Data Memory Organization

The data memory (Figure 4-2 and Figure 4-3) is

partitioned into four banks, which contain the general

purpose registers and the Special Function Registers

(SFR). The SFRs are located in the first 32 locations of

each Bank. There are general purpose registers imple-

mented as static RAM in each Bank. Table 4-1 lists the

general purpose register available in each of the four

banks.

TABLE 4-1: GENERAL PURPOSE STATIC

RAM REGISTERS

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are

implemented as common RAM and mapped back to

addresses 70h-7Fh.

Table 4-2 lists how to access the four banks of registers

via the STATUS Register bits RP1 and RP0.

TABLE 4-2: ACCESS TO BANKS OF

REGISTERS

4.2.1 GENERAL PURPOSE REGISTER

FILE

The register file is organized as 224 x 8 in the

PIC16F627A/628A and 256 x 8 in the PIC16F648A.

Each is accessed either directly or indirectly through

the File Select Register (FSR), See Section 4.4.

PC<12:0>

13

000h

0004

0005

03FFh

1FFFh

Stack Level 1

Stack Level 8

RESET Vector

Interrupt Vector

On-chip Program

Memory

CALL, RETURN

RETFIE, RETLW

Stack Level 2

07FFh

PIC16F627A,

PIC16F628A and

PIC16F648A

On-chip Program

Memory

PIC16F628A and

PIC16F648A

On-chip Program

Memory

PIC16F648A only

0FFFh

PIC16F627A/628A PIC16F648A

Bank0 20-7Fh 20-7Fh

Bank1 A0h-FF A0h-FF

Bank2 120h-14Fh, 170h-17Fh 120h-17Fh

Bank3 1F0h-1FFh 1F0h-1FFh

RP1 RP0

Bank0 0 0

Bank1 0 1

Bank2 1 0

Bank3 1 1

PIC16F627A/628A/648A

DS40044A-page 16 Preliminary 2002 Microchip Technology Inc.

FIGURE 4-2: DATA MEMORY MAP OF THE PIC16F627A AND PIC16F628A

Indirect addr.

(1)

TMR0

PCL

STATUS

FSR

PORTA

PORTB

PCLATH

INTCON

PIR1

TMR1L

TMR1H

T1CON

TMR2

T2CON

CCPR1L

CCPR1H

CCP1CON

OPTION

PCL

STATUS

FSR

TRISA

TRISB

PCLATH

INTCON

PIE1

PCON

PR2

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Fh

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

9Dh

9Eh

9Fh

20h

A0h

7Fh FFh

Bank 0 Bank 1

Unimplemented data memory locations, read as '0'.

Note 1: Not a physical register.

File

Address

Indirect addr.

(1)

Indirect addr.

(1)

PCL

STATUS

FSR

PCLATH

INTCON

PCL

STATUS

FSR

PCLATH

INTCON

100h

101h

102h

103h

104h

105h

106h

107h

108h

109h

10Ah

10Bh

10Ch

10Dh

10Eh

10Fh

180h

181h

182h

183h

184h

185h

186h

187h

188h

189h

18Ah

18Bh

18Ch

18Dh

18Eh

18Fh

17Fh 1FFh

Bank 2 Bank 3

Indirect addr.

(1)

TMR0 OPTION

RCSTA

TXREG

RCREG

CMCON

TXSTA

SPBRG

VRCON

General

Purpose

Register

1EFh

1F0h

accesses

70h - 7Fh

EFh

F0h

accesses

70h-7Fh

16Fh

170h

accesses

70h-7Fh

80 Bytes

EEDATA

EEADR

EECON1

EECON2

(1)

General

Purpose

Register

80 Bytes

General

Purpose

Register

48 Bytes

11Fh

120h

14Fh

150h

6Fh

70h

16 Bytes

PORTB TRISB

1Ch

1Dh

1Eh

Вам также может понравиться

- PIC16F627A/628A/648A: 4.0 Memory OrganizationДокумент7 страницPIC16F627A/628A/648A: 4.0 Memory OrganizationDarilho Batista IgnacioОценок пока нет

- PIC Microcontrollers: A Guide to Their Architecture and ApplicationsДокумент3 страницыPIC Microcontrollers: A Guide to Their Architecture and ApplicationsSaurabh RastogiОценок пока нет

- Unit 1 Architecture of Pic 16cXXДокумент41 страницаUnit 1 Architecture of Pic 16cXXKapilachander Thangavel100% (1)

- PIC MicrocontrollersДокумент35 страницPIC Microcontrollersanbuelectrical100% (1)

- Unit Ii: PIC MicrocontrollersДокумент59 страницUnit Ii: PIC MicrocontrollersbalaОценок пока нет

- PIC16F877AДокумент10 страницPIC16F877ABhaskar Rao PОценок пока нет

- An Introduction To The PIC Microcontroller: EE2801 - Lecture 19Документ9 страницAn Introduction To The PIC Microcontroller: EE2801 - Lecture 19Reddy BabuОценок пока нет

- Chapter 2Документ41 страницаChapter 2Lavanya GowdaОценок пока нет

- Pic 23Документ15 страницPic 23girush100% (1)

- Datasheet 16f627aДокумент22 страницыDatasheet 16f627aDan RizanОценок пока нет

- Flash Memory Programming Specification: PIC12F609/12F615/12F617/16F610/16F616 AND PIC12HV609/12HV615/16HV610/16HV616Документ26 страницFlash Memory Programming Specification: PIC12F609/12F615/12F617/16F610/16F616 AND PIC12HV609/12HV615/16HV610/16HV616roscribОценок пока нет

- Introdution To The DsPIC30FДокумент17 страницIntrodution To The DsPIC30Fboyluca100% (1)

- Unit-5 PIC18 Architecture PDFДокумент26 страницUnit-5 PIC18 Architecture PDFMohammed AbdulAziz100% (1)

- Dspic33F/Pic24H Flash Programming SpecificationДокумент84 страницыDspic33F/Pic24H Flash Programming SpecificationSobhi MahОценок пока нет

- 16f877a Programming SpecificationsДокумент22 страницы16f877a Programming SpecificationsJose Antonio Chocano SequeirosОценок пока нет

- Hardware SpecificationsДокумент3 страницыHardware Specificationsminuck12Оценок пока нет

- 80c51 Family ArchitectureДокумент15 страниц80c51 Family Architectureenriquebadajoz5659Оценок пока нет

- PIC Microcontrollers ExplainedДокумент18 страницPIC Microcontrollers ExplainedKrishna BoreddyОценок пока нет

- Bai2 MemoryДокумент27 страницBai2 MemoryDương ThịnhОценок пока нет

- PIC16F84XДокумент33 страницыPIC16F84XSofi Caballero MestraОценок пока нет

- PIC16F627A/628A/648A: 3.0 Architectural OverviewДокумент4 страницыPIC16F627A/628A/648A: 3.0 Architectural OverviewAndrés Gilberto Catalán HernándezОценок пока нет

- TALKING ELECTRONICS PIC Theory Page 33Документ6 страницTALKING ELECTRONICS PIC Theory Page 33palurdo2Оценок пока нет

- Pic18f IntroДокумент25 страницPic18f IntroElena Gilbert100% (1)

- 16 F 506Документ22 страницы16 F 506Kavin SengodanОценок пока нет

- Micro II and Embedded Systems: Introduction To PIC MicrocontrollerДокумент22 страницыMicro II and Embedded Systems: Introduction To PIC Microcontrollerxkurt358792Оценок пока нет

- PIC18F MCU Architecture and Memory OrganizationДокумент41 страницаPIC18F MCU Architecture and Memory OrganizationEliezer Silverio Acosta100% (1)

- PIC18F458 Microcontroller Architecture and Embedded CДокумент64 страницыPIC18F458 Microcontroller Architecture and Embedded CSakshi WaniОценок пока нет

- Embedded System LEC #04: © Dr. Ahmed MahrousДокумент24 страницыEmbedded System LEC #04: © Dr. Ahmed MahrousThafer MajeedОценок пока нет

- Macros For Page and Bank Switching: 'xxx0 XXXX'BДокумент23 страницыMacros For Page and Bank Switching: 'xxx0 XXXX'BGuillermo HernandezОценок пока нет

- Introduction 89C51/8051 Microcontroller Kit of Vi MicrosystemsДокумент20 страницIntroduction 89C51/8051 Microcontroller Kit of Vi MicrosystemsAssini Hussain83% (6)

- The 8-bit 8051 Microcontroller - A Guide to its Architecture and ApplicationsДокумент140 страницThe 8-bit 8051 Microcontroller - A Guide to its Architecture and ApplicationsNisha Verma100% (1)

- Pic Programming TutorialДокумент18 страницPic Programming TutorialKerem AktuğОценок пока нет

- At89lp2052 PDFДокумент93 страницыAt89lp2052 PDFRisnoHamidОценок пока нет

- 16f8x Serial ProgДокумент16 страниц16f8x Serial ProgIgnacio MartiОценок пока нет

- Rev 2Документ3 страницыRev 2Abilash GowdaОценок пока нет

- E4160 - Microprocessor & Microcontroller SystemДокумент48 страницE4160 - Microprocessor & Microcontroller SystemHarish Gunasekaran100% (2)

- ES Chapter6Документ41 страницаES Chapter6anses1000Оценок пока нет

- PIC16F87XA: NotesДокумент5 страницPIC16F87XA: Notesvitor valeОценок пока нет

- Pic16f84 IntroДокумент2 страницыPic16f84 IntroManish KumarОценок пока нет

- Arquitetura 12F509Документ21 страницаArquitetura 12F509ifmatosОценок пока нет

- PIC12F629/675/PIC16F630/676Документ24 страницыPIC12F629/675/PIC16F630/676Romel Ranin CalangОценок пока нет

- PIC16F54: Memory Programming SpecificationДокумент14 страницPIC16F54: Memory Programming SpecificationLahatem AbdulОценок пока нет

- PIC Introduction PDFДокумент46 страницPIC Introduction PDFPeeyush Kp100% (1)

- PIC16F54Документ14 страницPIC16F54mejmakОценок пока нет

- PIC Practical Project0470694610Документ54 страницыPIC Practical Project0470694610Alex MassОценок пока нет

- 18f14k22 ProgrammingДокумент36 страниц18f14k22 Programmingarturo53Оценок пока нет

- PIC microcontroller family overviewДокумент27 страницPIC microcontroller family overviewTol Man Shrestha100% (1)

- EE6008 MICROCONTROLLER TITLEДокумент12 страницEE6008 MICROCONTROLLER TITLETakeItEasyDude TIEDОценок пока нет

- Chapter 2 - Microcontroller Architecture & Assembly LanguageДокумент41 страницаChapter 2 - Microcontroller Architecture & Assembly LanguageJiachyi Yeoh100% (1)

- PicДокумент71 страницаPicSanthosh SachithananthamОценок пока нет

- Emb PIC Charles Kim Chap2Документ2 страницыEmb PIC Charles Kim Chap2subiОценок пока нет

- 8085 PDFДокумент74 страницы8085 PDFGorla Ramu100% (1)

- PICmicro Migration PathДокумент48 страницPICmicro Migration PathDragan ManojlovicОценок пока нет

- PIC Ch2Документ41 страницаPIC Ch2PeaceОценок пока нет

- Introduction to Microcontrollers and PIC16F877AДокумент48 страницIntroduction to Microcontrollers and PIC16F877AMuhd Muhd Hasif100% (1)

- PIC10F200/202/204/206 - Memory Programming Specification - 41228BДокумент18 страницPIC10F200/202/204/206 - Memory Programming Specification - 41228BGuillermo HernandezОценок пока нет

- ARM Microcontrollers Programming for Embedded SystemsОт EverandARM Microcontrollers Programming for Embedded SystemsРейтинг: 5 из 5 звезд5/5 (1)

- Marcha ImperialДокумент3 страницыMarcha ImperialAndrés Gilberto Catalán HernándezОценок пока нет

- Draftsigth Getting Started GuideДокумент186 страницDraftsigth Getting Started GuideAndrés Gilberto Catalán HernándezОценок пока нет

- PIC16F627A/628A/648A: 16.0 Development SupportДокумент2 страницыPIC16F627A/628A/648A: 16.0 Development SupportAndrés Gilberto Catalán HernándezОценок пока нет

- PIC16F627A/628A/648A: 3.0 Architectural OverviewДокумент4 страницыPIC16F627A/628A/648A: 3.0 Architectural OverviewAndrés Gilberto Catalán HernándezОценок пока нет

- Cora-Treboles ModelДокумент1 страницаCora-Treboles ModelAndrés Gilberto Catalán HernándezОценок пока нет

- Getting Started With NI Circuit Design SuiteДокумент139 страницGetting Started With NI Circuit Design SuiteAndrés Gilberto Catalán HernándezОценок пока нет

- PIC16F627A/628A/648A: 19.0 Packaging InformationДокумент5 страницPIC16F627A/628A/648A: 19.0 Packaging InformationAndrés Gilberto Catalán HernándezОценок пока нет

- SmpcbookДокумент460 страницSmpcbookAndrés Gilberto Catalán HernándezОценок пока нет

- The Art & Science of Protective Relaying - C. Russell Mason - GEДокумент357 страницThe Art & Science of Protective Relaying - C. Russell Mason - GEAasim MallickОценок пока нет

- Cora-Treboles ModelДокумент1 страницаCora-Treboles ModelAndrés Gilberto Catalán HernándezОценок пока нет

- Watfor 77Документ49 страницWatfor 77Andrés Gilberto Catalán HernándezОценок пока нет

- Operating Systems Scheduling Criteria ExplainedДокумент21 страницаOperating Systems Scheduling Criteria ExplainedElangovan GuruvaReddyОценок пока нет

- Ic-751 745 RamДокумент2 страницыIc-751 745 RamArnaud GarnierОценок пока нет

- Intel Smart Response Cache + Windows On Same SSDДокумент2 страницыIntel Smart Response Cache + Windows On Same SSDs0d0m1z3dОценок пока нет

- Manual For Ricoh 2001L CopierДокумент68 страницManual For Ricoh 2001L Copiersyaora100% (1)

- Coreboot Tutorial - OSCON 2013Документ81 страницаCoreboot Tutorial - OSCON 2013Dacaen DanОценок пока нет

- 04 Processes SlidesДокумент33 страницы04 Processes SlidesWaqas AhmedОценок пока нет

- MacBook Pro 15Документ9 страницMacBook Pro 15jdpardo100% (1)

- CCSE Hardware, Software, Network and Security CapabilitiesДокумент4 страницыCCSE Hardware, Software, Network and Security CapabilitiesnikzperaltaОценок пока нет

- The 8051 Microcontroller and Embedded Systems: 8051 Assembly Language ProgrammingДокумент29 страницThe 8051 Microcontroller and Embedded Systems: 8051 Assembly Language Programminganand787Оценок пока нет

- 101 Wacky Computer Jokes (1998)Документ51 страница101 Wacky Computer Jokes (1998)Pk LalОценок пока нет

- VIDEO INTERFACE: A CONCISE LOOK AT THE DREAM 6800 COMPUTER'S VIDEO CIRCUITRYДокумент1 страницаVIDEO INTERFACE: A CONCISE LOOK AT THE DREAM 6800 COMPUTER'S VIDEO CIRCUITRYHernan BenitesОценок пока нет

- Computer Awareness - Computer Awareness-1Документ12 страницComputer Awareness - Computer Awareness-1samskruti speaksОценок пока нет

- Setting Up Multiple USB3 CamerasДокумент11 страницSetting Up Multiple USB3 CamerasSebastian GómezОценок пока нет

- Geh 6407 Control System Solutions (Maintenance and Diagnostics Applications)Документ79 страницGeh 6407 Control System Solutions (Maintenance and Diagnostics Applications)SupolОценок пока нет

- Crop Monitoring System With Atmega 64 AVR MicrocontrollerДокумент87 страницCrop Monitoring System With Atmega 64 AVR Microcontrollerchakradhar_jalla100% (1)

- Flyer CybTouch 8 PS ENДокумент2 страницыFlyer CybTouch 8 PS ENFathi FathiОценок пока нет

- Esys Vs IntelДокумент30 страницEsys Vs IntelpbОценок пока нет

- Final Lecture Chapter 2 2 Intro To Asml Memory SegmentationДокумент28 страницFinal Lecture Chapter 2 2 Intro To Asml Memory SegmentationAman BazeОценок пока нет

- Introduction To MIMD ArchitecturesДокумент17 страницIntroduction To MIMD ArchitecturesLinh PhamОценок пока нет

- Computer Registers: Maninder KaurДокумент15 страницComputer Registers: Maninder Kaurraghu84taduriОценок пока нет

- Module 2 Embedded SystemsДокумент77 страницModule 2 Embedded SystemsnpottiОценок пока нет

- TR-2000 Final Test Procedure Setup GuideДокумент9 страницTR-2000 Final Test Procedure Setup GuideJose Luis ZIMICОценок пока нет

- HP EVA P6000 Disk Drive Firmware SupportДокумент9 страницHP EVA P6000 Disk Drive Firmware SupportMehdi KheirandishОценок пока нет

- XII CS Project FileДокумент9 страницXII CS Project Fileankur88834Оценок пока нет

- Manual HP 1022Документ163 страницыManual HP 1022Javier MoralesОценок пока нет

- Impresora EPSON WF600-BX600-SX600-TX600-OFF700Документ175 страницImpresora EPSON WF600-BX600-SX600-TX600-OFF700Javier Davalos NettoОценок пока нет

- Ir32xx Code ArticleДокумент1 страницаIr32xx Code ArticleTony ChangОценок пока нет

- Classic RISC PipelineДокумент10 страницClassic RISC PipelineShantheri BhatОценок пока нет

- DFS Fusion V3 Brochure (EN)Документ8 страницDFS Fusion V3 Brochure (EN)controlyfuerzamotrizОценок пока нет

- SFF Time P-ATX v0.1 ManualДокумент22 страницыSFF Time P-ATX v0.1 ManualBruno Pérez GarcíaОценок пока нет