Академический Документы

Профессиональный Документы

Культура Документы

Los PIC de Gama Media

Загружено:

ElTioOblongoАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Los PIC de Gama Media

Загружено:

ElTioOblongoАвторское право:

Доступные форматы

LOS PIC DE LA GAMA MEDIA.

ARQUITECTURA Y TCNICAS DE

PROGRAMACIN.

Santiago Salamanca Mio

David Arroyo Muoz

Octubre de 2002

Este libro es el resultado del Proyecto Fin de Carrera realizado por el alumno David

Arroyo Muoz y dirigido por Santiago Salamanca Mio. Est basado en los apuntes de

clase de la asignatura Informtica Industrial de la Titulacin de Ingeniero Tcnico

Industrial, especialidad Electrnica Industrial, que se imparte en la Escuela de

Ingenieras Industriales de la Universidad de Extremadura.

Si encuentras alguna errata o quieres hacer algn comentario, puedes escribir al

siguiente correo electrnico:

ssalaman@unex.es

Microcontroladores PIC de la Gama Media. NDICE GENERAL.

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

I

NDICE GENERAL

1 Introduccin a los Microcontroladores. ..................................................................... 1

1.1 Qu es un microcontrolador? ................................................................. 1

1.2 Aplicaciones............................................................................................. 3

1.3 Los microcontroladores PIC. ................................................................... 3

1.4 Las Gamas de los PIC. ............................................................................. 5

1.5 Los PIC de la Gama Media...................................................................... 6

2 La Arquitectura de los PIC de la Gama Media. ........................................................ 11

2.1 Introduccin. ........................................................................................... 11

2.2 Organizacin de la memoria. .................................................................. 13

2.2.1 Organizacin de la memoria de programa. ..................... 13

2.2.2 Organizacin de la memoria de datos............................. 16

2.2.3 Registros y recursos comunes......................................... 19

2.2.3.1 Registro de Estado. ....................................... 19

2.2.3.2 Registro de Opciones. ................................... 20

2.2.3.3 Palabra de configuracin. ............................. 21

2.3 Oscilador. ................................................................................................ 22

2.4 Reset........................................................................................................ 26

2.5 Temporizador y Perro Guardin. ............................................................ 34

2.6 Puertas E/S. ............................................................................................. 36

2.7 Modo de reposo o SLEEP....................................................................... 37

3 Juego de Instrucciones de los PIC de la Gama Media. ............................................. 39

3.1 Introduccin. ........................................................................................... 39

3.2 Flujo de instrucciones. Segmentacin. ................................................... 40

3.3 El formato de las instrucciones. .............................................................. 41

3.4 Juego de instrucciones. ........................................................................... 43

3.4.1 Descripcin detallada de las instrucciones

por orden alfabtico. ....................................................... 45

4 Los Perifricos de los PIC de la Gama Media. ......................................................... 63

4.1 Introduccin. ........................................................................................... 63

Microcontroladores PIC de la Gama Media. NDICE GENERAL.

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

II

4.2 Interrupciones. ........................................................................................ 63

4.2.1 Registros de control. ....................................................... 65

4.2.1.1 Registro INTCON......................................... 65

4.2.1.2 Registros PIE. ............................................... 66

4.2.1.3 Registros PIR. ............................................... 67

4.2.2 Fases de una interrupcin. .............................................. 70

4.3 Puertas de E/S. ........................................................................................ 72

4.3.1 Puerta A. ......................................................................... 73

4.3.2 Puerta B. ......................................................................... 75

4.3.3 Puerta C. ......................................................................... 77

4.3.4 Puerta D. ......................................................................... 78

4.3.5 Puerta E........................................................................... 78

4.3.6 Puertas F y G. ................................................................. 79

4.3.7 Puerta GPIO.................................................................... 80

4.3.8 Operaciones sucesivas en un Puerto E/S. ....................... 81

4.4 Puerto Paralelo Esclavo. ......................................................................... 83

4.5 Temporizadores ...................................................................................... 86

4.5.1 TMR0.............................................................................. 86

4.5.2 TMR1.............................................................................. 90

4.5.3 TMR2.............................................................................. 92

4.6 Mdulos CCP.......................................................................................... 93

4.6.1 Modo de captura. ............................................................ 94

4.6.2 Modo de comparacin. ................................................... 96

4.6.3 Modo PWM. ................................................................... 97

4.7 Mdulo de Tensin de Referencia. ........................................................ 100

4.8 Mdulo Comparador Analgico. ........................................................... 102

4.9 Convertidor A/D. ................................................................................... 106

4.10 Mdulos de comunicacin serie. ......................................................... 112

4.10.1 Puerto Serie Sncrono (SSP). .......................................... 112

4.10.1.1 Modo SPI. .................................................................... 115

4.10.1.2 Modo I

2

C. .................................................................... 117

Microcontroladores PIC de la Gama Media. NDICE GENERAL.

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

III

4.10.2 USART. .......................................................................... 125

4.10.2.1 Modo asncrono. ................................... 128

4.10.2.2 Modo sncrono...................................... 133

5 Programacin con PIC. ............................................................................................ 137

5.1 Introduccin. .......................................................................................... 137

5.2 Directivas del ensamblador MPASM. ................................................... 137

5.3 Creacin de programas. ......................................................................... 156

5.3.1 Un solo cdigo fuente (ensamblador). ........................... 156

5.3.2 Varios cdigos fuente (linkador). .................................. 157

5.3.3 Utilizacin de libreras................................................... 158

5.4 Estructuras bsicas de programacin. .................................................... 160

5.4.1 Estructuras iterativas...................................................... 160

5.4.1.1 While............................................................ 160

5.4.1.2 Do while....................................................... 161

5.4.1.3 For. ............................................................... 161

5.4.2 Estructuras condicionales. ............................................. 162

5.4.2.1 If................................................................... 162

5.4.2.2 If ... else........................................................ 163

5.4.3 Cdigos de condicin..................................................... 164

5.4.3.1 Igual. ............................................................ 164

5.4.3.2 Distinto......................................................... 164

5.4.3.3 Mayor........................................................... 164

5.4.3.4 Mayor o igual............................................... 165

5.4.3.5 Menor........................................................... 165

5.4.3.6 Menor o igual............................................... 165

5.4.3.7 Condiciones ms complejas......................... 165

5.5 Ejemplo de libreras: librera matemtica. ............................................. 166

5.5.1 Rutinas de coma flotante................................................ 166

5.5.1.1 Manejo de excepciones................................ 168

5.5.1.2 Redondeo. .................................................... 168

5.5.1.3 Conversin de entero a flotante. .................. 168

Microcontroladores PIC de la Gama Media. NDICE GENERAL.

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

IV

5.5.1.4 Normalizacin.............................................. 168

5.5.1.5 Conversin de flotante a entero. .................. 169

5.5.1.6 Suma/Resta. ................................................. 169

5.5.1.7 Multiplicacin.............................................. 169

5.5.1.8 Divisin........................................................ 170

5.5.2 Rutinas en coma fija. ..................................................... 171

5.5.2.1 Multiplicacin.............................................. 171

5.5.2.2 Divisin........................................................ 172

5.5.3 Funciones matemticas en coma flotante. ..................... 173

5.5.3.1 Funcin raz cuadrada.................................. 174

5.5.3.2 Funciones exponenciales. ........................... 175

5.5.3.3 Funciones logartmicas. ............................... 176

5.5.3.4 Funcione trigonomtricas. ........................... 178

5.5.3.5 Funcin potencia.......................................... 179

5.5.3.6 Funcin parte entera por defecto. ................ 182

5.5.3.7 Comparacin lgica en coma flotante. ........ 182

5.5.3.8 Generador aleatorio de nmeros enteros. .... 183

5.5.4 Conversin de coma flotante a ASCII. .......................... 183

5.5.4.1 Conversin de coma flotante

a ASCII en base 10. ..................................... 184

5.5.4.2 Personalizacin de la rutina. ........................ 184

5.5.4.3 Resumen. ..................................................... 185

APNDICE A: Protocolo I

2

C........................................................................................ 187

A.1 Introduccin......................................................................................... 187

A.2 Inicializacin y fin de transferencia de datos....................................... 187

A.3 Direccionamiento de dispositivos en I

2

C............................................. 188

A.4 Reconocimiento de transferencia......................................................... 189

Microcontroladores PIC de la Gama Media. 1. Introduccin a los Microcontroladores

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

1

Captulo 1. Introduccin a los microcontroladores.

1.1 Qu es un microcontrolador?

Hace unos aos, los sistemas de control se implementaban usando exclusivamente lgica de

componentes, lo que haca que fuesen dispositivos de gran tamao y muy pesados. Para

facilitar una velocidad ms alta y mejorar la eficiencia de estos dispositivos de control, se

trat de reducir su tamao, apareciendo as los microprocesadores. Siguiendo con el proceso

de miniaturizacin, el siguiente paso consisti en la fabricacin de un controlador que

integrase todos sus componentes en un slo chip. A esto es a lo que se le conoce con el

nombre de microcontrolador, un computador dentro de un slo chip.

Las principales caractersticas que diferencian a un microcontrolador de un microprocesador

son:

1. Son sistemas cerrados, ya que contiene todos los elementos de un computador en

un solo chip, frente a los microprocesadores que son sistemas abiertos, ya que

sacan las lneas de los buses de datos, direcciones y control al exterior, para la

conexin de memorias, interfaces de E/S, etc.

2. Son de propsito especfico, es decir, son programados para realizar una nica

tarea, mientras que los microprocesadores son de propsito general.

La historia de los microcontroladores surge desde dos vas de desarrollo paralelas; una desde

Intel y otra desde Texas Instruments. Los primeros microcontroladores son el 4004 y 4040 de

Intel que dieron lugar al 8048, a su vez predecesor del 8051. An as el primer

microcontrolador fue el TMS1000 de Texas Instruments. ste integraba un reloj, procesador,

ROM, RAM, y soportes de E/S en un solo chip.

Microcontroladores PIC de la Gama Media. 1. Introduccin a los Microcontroladores

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

2

Un microcontrolador, tpicamente consta de:

-CPU o procesador.- Es el cerebro del sistema que procesa todos los datos que viajan a

lo largo del bus.

-Memorias.- Est formada por una no voltil (ROM, EEPROM, FLASH) donde se

almacenan los programas y una voltil (RAM) donde se almacenan los datos.

-Reloj principal.- Normalmente todos los microcontroladores tienen incorporados

circuitos osciladores para el funcionamiento de stos.

-Puertos E/S (Entrada/Salida).- Soportan las lneas que comunican al microcontrolador

con los perifricos externos.

-Perro guardin o Watchdog.- Contador que resetea al microcontrolador cada vez que

rebosa. Sirve para evitar fallos de funcionamiento, por lo que hay que

inicializarlo peridicamente antes de que rebose.

-Proteccin ante fallo de alimentacin o Browout.- Circuito que resetea al

microcontrolador cuando la tensin de alimentacin baja de un cierto lmite.

-Temporizadores.- Para controlar periodos de tiempo.

-Convertidores A/D y D/A. (Analgico/Digital y Digital/Analgico)

-Comparadores analgicos

-Moduladores de anchura de impulsos.

-Puertos de comunicacin.- Tanto serie como paralelo.

-Control de interrupciones

Debido a que los microcontroladores slo incluyen las caractersticas especficas para una

tarea, su coste es relativamente bajo. Un microcontrolador tpico realiza funciones de

manipulacin de instrucciones, posee E/S de accesos fciles y directos, y un proceso de

interrupciones rpido y eficiente. Adems tambin reducen de manera notable los costes de

diseo. Hay gran variedad de microcontroladores. Dependiendo de la potencia y

caractersticas que se necesiten, se pueden elegir microcontroladores de 4, 8, 16 32 bits.

Adems existen versiones especializadas que incluyen mdulos especiales para

comunicaciones, teclados, procesamiento de seales, procesamiento de video, y otras tareas.

Microcontroladores PIC de la Gama Media. 1. Introduccin a los Microcontroladores

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

3

1.2 Aplicaciones

El mercado de los microcontroladores est creciendo cada ao y parece no tener barreras. Los

microcontroladores a menudo se encuentran en aplicaciones domsticas ( microondas,

refrigeradores, televisin, equipos de msica), ordenadores con sus componentes (impresoras,

mdems, lectores de discos), coches (ingeniera de control, diagnostico, control de

climatizacin), control medioambiental (invernaderos, fabricas, casas), instrumentacin,

aeronutica, y miles de usos ms. En muchos podemos encontrar ms de un microcontrolador.

Los microcontroladores son muy usados en robtica, donde la comunicacin entre

controladores es una gran ventaja. Esto hace posible muchas tareas especficas al distribuir un

gran nmero de microcontroladores por todo el sistema. La comunicacin entre cada

microcontrolador y uno central permitira procesar la informacin por un ordenador central, o

transmitirlo a otros microcontroladores del sistema.

Otro ejemplo de aplicacin de los microcontroladores, es la de utilizarlos para monitorizar y

gravar parmetros medioambientales (temperatura, humedad, precipitaciones, etc.). Pequeo

tamao, bajo consumo de potencia, y flexibilidad hacen de este dispositivo ideal para este tipo

de aplicaciones.

1.3 Los microcontroladores PIC (Microchip)

Los microcontroladores PIC fueron los primeros microcontroladores RISC, es decir,

microcontroladores con un juego de instrucciones reducido. El hecho de ser procesadores de

tipo RISC generalmente implica simplicidad en los diseos, permitiendo ms caractersticas a

bajo coste.

Los principales beneficios de esta simplicidad en el diseo son que los microcontroladores se

implementan en chip muy pequeos, con pocos pines, y tienen un consumo de potencia muy

bajo.

Microcontroladores PIC de la Gama Media. 1. Introduccin a los Microcontroladores

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

4

Los microcontroladores PIC ganaron popularidad rpidamente. Aparecan con frecuencia en

revistas de ocio, y su uso era cada vez mayor en gran nmero de diseos. Debido a su bajo

costo, pequeo tamao, y bajo consumo, estos microcontroladores pueden ahora ser usados en

reas en las que previamente no habran sido apropiados (tal como circuitos lgicos).

Las principales caractersticas de los PIC son:

-Arquitectura Harvard.- Consiste en la existencia de dos memorias independientes,

una de datos y otra de instrucciones, con sus respectivos buses. Esto permite el

acceso simultaneo al programa y los datos, y solapar algunas operaciones para

mejorar el proceso.

-Segmentacin de instrucciones.- Consiste en dividir la ejecucin de las

instrucciones en varias fases, en el caso concreto de los PIC dos fases, de

manera que se realizan simultneamente distintas fases de distintas

instrucciones. As cada instruccin se ejecuta en un ciclo de instruccin (4

ciclos de reloj), excepto las de salto que ocupan tantos ciclos de instruccin

como necesite para calcular la direccin de salto.

-Formato de instrucciones de longitud constante.- Permite optimizar la memoria de

instrucciones y el diseo de ensambladores y compiladores.

-RISC (computador de reducido juego de instrucciones)

-Instrucciones ortogonales.- Todas las instrucciones pueden manejar cualquier

elemento de la arquitectura como fuente o destino.

-Arquitectura basada en un banco de registros.- Todos los objetos del sistema se

encuentran implementados fsicamente como registros.

-Gran variedad de microcontroladores y muchas herramientas de soporte.

Microcontroladores PIC de la Gama Media. 1. Introduccin a los Microcontroladores

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

5

1.4 Las gamas de los PIC

La forma de designacin de los PIC en general obedece a la siguiente estructura:

PIC nn LLL xxx

Siendo :

nn un nmero propio de la gama del PIC.

LLL cdigo de letras donde la primera indica la tensin de alimentacin y las otras

dos el tipo de memoria que utiliza. En la tabla 1.1 se puede ver las distintas

opciones que se pueden dar.

TABLA 1.1 Nomenclatura de los PIC.

LETRAS ALIMENTACIN MEMORIA

C Standard (4.5-6.0 V) EPROM

CR Standard (4.5-6.0 V) ROM

F Standard (4.5-6.0 V) FLASH

LC Extendida (2.5-6.0 V) EPROM

LCR Extendida (2.5-6.0 V) ROM

LF Extendida (2.0-6.0 V) FLASH

xxx nmero que indica el modelo.

Los PIC se clasifican en distintas gamas atendiendo a los recursos disponibles en cada uno de

ellos. Las gamas son:

a) Gama Enana (PIC12Cxxx): La principal caracterstica es que son muy pequeos,

con encapsulados de 8 pines, y un juego de 33 instrucciones de 12 bits.

b) Gama Baja (PIC16C5xx): Los encapsulados son de 18, 20 28 pines. Al igual

que en los anteriores el nmero de instrucciones es de 33 con un ancho de 12 bits.

La memoria de programa es de 512 palabras, 1K 2K, y la de datos est

comprendida entre 25 y 73 bytes. No permite interrupciones.

Microcontroladores PIC de la Gama Media. 1. Introduccin a los Microcontroladores

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

6

c) Gama Media (PIC16Cxxx): Es la gama ms variada y completa de los PIC, con

encapsulados desde 18 a 68 pines. Tiene un conjunto de 35 instrucciones de 14

bits de ancho. Permite adems caractersticas importantes que no soportaban los

anteriores como son:

- Interrupciones

- Pila de 8 niveles que permite anidamiento de subrutinas.

Esta familia a su vez se puede dividir en subfamilias en funcin de los recursos de

que se dispongan.

d) Gama Alta (PIC17Cxxx): Tienen unas caractersticas muy diferentes a las

anteriores, ya que son microcontroladores de arquitectura abierta, es decir, que

sacan sus buses al exterior.

El nmero de instrucciones es de 58 con una anchura de 16 bits. Tienen

instrucciones vectorizadas.

e) Gama Mejorada (PIC18Cxxx): Es la ltima gama que ha salido. Tiene memoria

de programa de hasta 1M palabras. La mayora de las instrucciones son de 16 bits,

aunque las hay tambin de 32 bits. El nmero total de instrucciones es de 76.

Esta gama est diseada para aplicaciones de control. Todos ellos tienen

convertidores A/D y, por ejemplo, estn en fase de desarrollo algunos modelos que

tienen interface para el bus CAN.

1.5 Los PIC de la gama media.

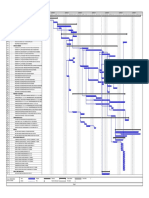

A lo largo de este proyecto slo se hablar de los PIC de la Gama Media, siendo esta la ms

variada y completa. En la tabla 1.2 se muestran las caractersticas que definen a cada modelo

de los PIC de la Gama Media. Aparecen slo los ms significantes, ya que la variedad es muy

amplia.

Microcontroladores PIC de la Gama Media. 1. Introduccin a los Microcontroladores

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

7

TABLA 1.2 Principales caractersticas de los PIC de la Gama Media.

Reloj Memoria Perifricos Caractersticas

M

e

m

o

r

i

a

d

e

p

r

o

g

r

a

m

a

C

p

s

u

l

a

s

M

x

i

m

a

f

r

e

c

u

e

n

c

i

a

d

e

t

r

a

b

a

j

o

E

P

R

O

M

E

E

R

O

M

M

e

m

o

r

i

a

d

e

d

a

t

o

s

(

b

y

t

e

s

)

E

E

P

R

O

M

d

e

d

a

t

o

s

(

b

y

t

e

s

)

M

d

u

l

o

s

d

e

t

e

m

p

o

r

i

z

a

c

i

n

M

d

u

l

o

s

C

C

P

P

u

e

r

t

o

s

s

e

r

i

e

P

u

e

r

t

o

P

a

r

a

l

e

l

o

C

o

n

v

e

r

t

i

d

o

r

A

/

D

d

e

8

b

i

t

s

C

o

m

p

a

r

a

d

o

r

e

s

T

e

n

s

i

n

i

n

t

e

r

n

a

d

e

r

e

f

e

r

e

n

c

i

a

F

u

e

n

t

e

s

d

e

i

n

t

e

r

r

u

p

c

i

n

P

a

t

i

l

l

a

s

d

e

E

/

S

R

a

n

g

o

d

e

v

o

l

t

a

j

e

(

v

o

l

t

i

o

s

)

D

e

t

e

c

t

o

r

d

e

f

a

l

l

o

e

n

V

D

D

B

r

o

w

n

-

o

u

t

P

i

n

e

s

D

I

P

P

i

n

e

s

P

L

C

C

P

i

n

e

s

Q

F

P

PIC16C61 20 1K --- 36 --- TMR0 -- --- -- -- -- -- 3 13

3,0-

6,0

--- 18 18 --

PIC16C62 20 2K --- 128 ---

TMR0,TMR1

,TMR2

2 SPI/I

2

C/SCI -- -- -- -- 10 22

2,5-

6,0

--- 28 28 --

PIC16C63 20 4K --- 192 ---

TMR0,TMR1

,TMR2

2 SPI/I

2

C/SCI --- -- -- -- 10 22

3,0-

6,0

--- 28 28 --

PIC16C64 20 2K --- 128 ---

TMR0,TMR1

,TMR2

1 SPI/I

2

C Si -- -- -- 8 33

3,0-

6,0

--- 40 44 44

PIC16C65 20 4K --- 192 ---

TMR0,TMR1

,TMR2

2 SPI/I

2

C/SCI Si -- -- -- 11 33

3,0-

6,0

--- 40 44 44

PIC16C620 20 512 --- 80 --- TMR0 -- ---- -- -- 2 Si 4 13

3,0-

6,0

Si 18 18 20

PIC16C621 20 1K --- 80 --- TMR0 -- ---- -- -- 2 Si 4 13

3,0-

6,0

Si 18 18 20

PIC16C622 20 2K --- 128 --- TMR0 -- ---- -- -- 2 Si 4 13

3,0-

6,0

Si 18 18 20

PIC16C71 20 1K --- 36 --- TMR0 -- ---- -- 4ch -- -- 4 13

3,0-

6,0

--- 18 18 --

PIC16C73 20 4K --- 192 ---

TMR0,TMR1

,TMR2

2 SPI/I

2

C/SCI -- 5ch -- -- 11 22

3,0-

6,0

--- 28 28 --

PIC16C74 20 4K --- 192 ---

TMR0,TMR1

,TMR2

2 SPI/I

2

C/SCI Si 8ch -- -- 12 33

3,0-

6,0

--- 40 44 44

PIC16C76 20 8K --- 368 ---

TMR0,TMR1

,TMR2

2 SPI/I

2

C/SCI -- 5ch -- -- 11 22

2,5-

6,0

Si 28 28 --

PIC16C84 20 -- 1K 36 64 TMR0 -- ---- -- -- -- -- 4 13

3,0-

6,0

--- 18 18 --

A continuacin en la figura 1.1 se muestran algunos de los encapsulados utilizados en los PIC

de la Gama Media. Como ya se ha dicho anteriormente, stos van desde los 18 a 68 pines.

Microcontroladores PIC de la Gama Media. 1. Introduccin a los Microcontroladores

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

8

Figura 1.1 Principales diagramas de patillas.

La descripcin de las funciones de las distintas patillas del microcontrolador son:

RA0/AN0-RA2/AN2: Lneas de E/S digitales del Puerto A, o entradas analgicas.

RA3/AN3/V

REF

: E/S digital, analgica o entrada externa de V

REF

.

RA4/T0CKI: E/S digital o entrada de reloj externo para TMR0.

RA5/AN4/ SS : E/S digital, analgica o seleccin del puerto sncrono.

RB0/INT-RB7: E/S digitales del Puerto B. RB0/INT puede actuar como entrada de

interrupcin externa. RB4-Rb7 pueden provocar una interrupcin cuando cambian de

estado.

RC0/T1OSO/T1CKI: E/S digital del Puerto C. Conexin del oscilador externo para

el temporizador TMR1 o entrada de reloj para el TMR1.

Microcontroladores PIC de la Gama Media. 1. Introduccin a los Microcontroladores

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

9

RC1/T1OSI/CCP2: E/S digital. Conexin del oscilador externo para el TMR1 o

salida del mdulo 2 de captura/comparacin.

RC2/CCP1: E/S digital. Salida del mdulo 1 de captura/comparacin.

RC3/SCK/SCL: E/S digital. E/S de reloj para el Puerto Serie Sncrono (SSP) en los

mdulos SPI o I

2

C.

RC4/SDI/SDA: E/S digital. Entrada de datos serie en el modo SPI. E/S de datos serie

en el modo I

2

C.

RC5/SDO: E/S digital. Salida de datos serie en el modo SPI.

RC6/TX/CK: E/S digital. Transmisin serie asncrona. Entrada de reloj para

comunicacin serie sncrona.

RC7/RX/DT: E/S digital. Recepcin serie asncrona. Lnea de datos en la

comunicacin serie sncrona.

RD0/PSP0-RD7/PSP7: E/S digitales del Puerto D. Este puerto puede trabajar como

puerto paralelo esclavo para interconexin con un bus de datos de 8 bits de otro

microprocesador.

RE0/ RD/AN5: E/S digital del Puerto E. Seal de lectura del puerto paralelo esclavo.

Entrada analgica.

RE1/ WR/AN6: E/S digital. Seal de escritura del puerto paralelo esclavo. Entrada

analgica.

RE2/ CS /AN7: E/S digital. Seal de activacin del puerto paralelo esclavo. Entrada

analgica.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

11

Captulo 2. La Arquitectura de los PIC de la Gama Media.

2.1 Introduccin

Desde el punto de vista de la arquitectura, la caracterstica ms importante de los PIC es que

utilizan la Harvard, frente a la Von Neumann que es la habitual.

La arquitectura Harvard tiene la memoria de programa y la memoria de datos separadas y se

accede a ellas mediante buses distintos. Esto mejora el ancho de banda sobre la tradicional

arquitectura secuencial, en la cual los programas y datos son buscados en la misma memoria,

utilizando el mismo bus. En la arquitectura Harvard mientras se accede a la memoria de

programa, sobre la memoria de datos se puede estar leyendo o escribiendo, lo que permite

ejecutar una instruccin a la vez que se busca la siguiente.

En la figura 2.1 se muestra el esquema de la arquitectura general de los PIC de la Gama

Media.

Adems de las caractersticas antes mencionadas, otras caractersticas que poseen los PIC de

la Gama Media son:

a) Memoria no voltil de programa de hasta 8K x 14 de tamao, direccionada por el

contador de programa (PC) de 13 bits.

b) Memoria RAM de datos de hasta 368 x 8 de tamao, direccionada por el cdigo de

operacin o por el registro FSR y parte del registro STATUS.

c) Unidad aritmtico-lgica de 8 bits con un registro acumulador de trabajo asociado

tambin de 8 bits. Realiza operaciones aritmticas y lgicas utilizando siempre

como operando el registro acumulador y otro dato perteneciente a cualquier

registro. Realiza operaciones de suma, resta y desplazamiento. Opera en

complemento a 2 (C2). Dependiendo del resultado, afecta a algunos bits del

registro de estado.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

12

Figura 2.1 Diagrama de bloques general de los PIC de la gama media.

Nota 1: Los bits de mayor orden en el direccionamiento directo de la RAM se obtienen del Registro de Estado.

2: No todos los dispositivos tienen estas caractersticas, habr que consultar las hojas de caractersticas.

3: Muchos de los pines de las puertas E/S de propsito general estn multiplexadas con una o ms

funciones de los mdulos perifricos. La combinacin de las funciones multiplexadas dependen del

dispositivo.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

13

d) Oscilador encargado de las generaciones de tiempo del sistema.

e) Circuitos controladores del RESET.

f) Puertos E/S. Existen hasta 7 puertos de E/S, aunque no existe ningn dispositivo

que los implemente todos. Adems se multiplexan con distintos elementos del

sistema.

g) Mdulos perifricos. Son la caracterstica que diferencia a los distintos

microcontroladores. stos facilitan la comunicacin con el mundo exterior, tal

como las E/S de propsito general, y tareas internas tal como puede ser la

generacin de las distintas bases de tiempo. Los perifricos sobre los que se est

hablando son; E/S de propsito general, hasta tres temporizadores, mdulo de

captura, comparacin, y PWM (CCP), puerto serie sncrono (SSP), USART (SCI),

mdulo para generacin de voltajes de referencia, mdulos comparadores

analgicos, conversores analgico digital (A/D), mdulo para control de Display

de cristal lquido (LCD) y puerto paralelo esclavo (PSP).

h) Registros generales del sistema.

2.2 Organizacin de la memoria.

La memoria de los PIC est dividida en dos bloques; la memoria de programa y la memoria

de datos. Cada uno de los bloques tiene su propio bus, pudiendo tener acceso a ambos bloques

de memoria en el mismo ciclo de reloj.

2.2.1 Organizacin de la memoria de programa.

En los PIC de la gama media el contador de programa es de 13 bits, con lo que se puede

direccionar una capacidad de memoria de 8K x 14 palabras. El ancho de la memoria de

programa va a ser la longitud de una instruccin que es de 14 bits, por lo se podrn almacenar

hasta 8K instrucciones. De esta forma es fcil determinar si el dispositivo tiene suficiente

memoria de programa para una aplicacin deseada.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

14

Esta memoria de programa a su vez est dividida en cuatro pginas de 2K palabras cada una

(0h 7FFh, 800h FFFh, 1000h 17FFh, y 1800h 1FFFh). En la figura 2.2 se muestra el

mapa de memoria con la pila de 8 niveles. No todos los dispositivos tienen implementados

estos cuatro bancos.

Figura 2.2 Organizacin de la memoria de programa y la pila.

Para realizar los saltos entre las pginas de la memoria de programa se utilizan los tres bits

ms altos del contador de programa (PC <11:12>), los cuales son implementados fsicamente

en la memoria de datos en el registro PCLATCH <4:3>. Si el programa se ejecuta

secuencialmente no es necesario modificarlo.

Dentro de la memoria de programa existen dos direcciones reservadas:

1. Vector de Reset .- En un dispositivo, un reset pone el contador de programa (PC)

a cero. A esta direccin se la denomina Direccin del Vector de Reset, donde

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

15

est la direccin de inicio para la ejecucin del programa. Cualquier reset borrar

tambin el contenido del registro PCLATH, de modo que cuando se produzca un

reset la direccin inicial a de estar localizada en la pgina 0 de la memoria de

programa.

2. Vector de Interrupcin .- Cuando una interrupcin es reconocida el PC es

forzado a la direccin 0004h. A esto es a lo que se le llama Direccin del Vector

de Interrupcin. Cuando el PC es forzado con la direccin del vector de

interrupcin, el PCLATH no es modificado. Por eso mismo en la direccin del

vector de interrupcin, el registro PCLATH debera ser escrito con el valor que

especificar la localizacin deseada en la memoria de programa. Antes de realizar

esta operacin, el PCLATH debera ser salvado para volverlo a restaurar al

terminar el tratamiento de la rutina de interrupcin.

El contador de programa (PC) es un registro que especifica la direccin de la instruccin que

ha de ser ejecutada. El PC tiene un ancho de 13 bits, correspondiendo el byte ms bajo con el

registro de lectura-escritura PCL, implementado en la memoria de datos, y el byte ms alto

con el registro PCH. Este ltimo contiene slo los bits <12:8> del PC y no se puede leer ni

escribir directamente, sino que son cargados a travs del PCLATH.

Existen varias instrucciones que modifican el flujo normal del sistema, y por tanto afectan al

PC. Estas instrucciones son:

1. Instrucciones de salto relativo: Son aquellas instrucciones que usan como

operando destino al PC. En estas instrucciones se cargan los 8 bits menos

significativos desde la UAL. El resto de los bits que coinciden con los del

PCLATH, habra que modificarlos manualmente.

2. Instruccin GOTO de salto incondicional: Carga desde el cdigo de operacin

los 11 bits menos significativos. Los dos que quedan se cargan desde el PCLATH

<4:3>. Si se hace un GOTO a una direccin que est en una pgina distinta,

primero hay que modificar estos bits del PCLATH.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

16

3. Instruccin CALL de salto a subrutina: Es igual que la anterior con la diferencia

de que antes de modificar el PC, el valor que tuviese se lleva a la pila.

4. Instrucciones RETURN, RETLW y RETFIE de retornos de subrutinas y rutinas

de tratamiento de interrupcin: Cargan directamente en el PC el valor que se halla

guardado anteriormente en la pila. No es necesario modificar el PCLATH.

Los PIC de la Gama Media poseen una pila de 8 niveles con un ancho de 13 bits, la cual nos

permite guardar las direcciones de retorno a un programa, cuando en ste se produce un salto

a una subrutina. Esto nos da capacidad para anidar hasta 8 subrutinas producidas por

programa o mediante interrupciones. Si en la pila ya se han almacenado 8 valores, el nuevo

valor se cargar sobre el primer nivel de la pila, de modo que puede dar problemas en el

funcionamiento de un programa.

2.2.2 Organizacin de la memoria de datos.

La memoria de datos (figura 2.3) est dividida en dos partes:

a) Memoria de registros especiales (FSR Memory): Est formada por aquellos

registros que son usados por la CPU y los perifricos para controlar una operacin.

b) Memoria de propsito general: Est formada por la memoria que puede usar el

programador.

En ambos casos, est dividida hasta en 4 bancos de memoria de hasta 128 bytes, aunque

muchos de los modelos no traen implementados estos dos ltimos bancos. En algunos

modelos de PIC la memoria de propsito general, est slo implementado fsicamente en el

banco0, estando el resto de los bancos mapeados en ste.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

17

Figura 2.3 Organizacin de la memoria de datos.

Nota 1: Los registros en negrita estn presentes en todos los dispositivos.

2: Puede que no todas las posiciones estn implementadas. Las localizaciones no implementadas se

leen como 0.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

18

El modo de acceso a cada uno de los bancos depender del tipo de direccionamiento que se

use.

Estos tipos de direccionamiento son:

1. Direccionamiento directo: La direccin final se obtiene con:

a. Los bits IRP1-IRP0 del registro de estado (STATUS), los cuales

seleccionan el banco de memoria.

b. Los 7 bits del cdigo de operacin, los cuales indican la posicin del dato

dentro del banco.

2. Direccionamiento indirecto: Con este tipo de direccionamiento lo que se da es la

direccin donde se encuentra la direccin del dato. Para ello se usa el registro

INDF. Al usar este registro (que no est implementado fsicamente), lo que se hace

es acceder al registro de datos FSR de 8 bits. Los 7 bits con menos peso del FSR

seleccionan la posicin dentro del banco, y el bit de mayor peso junto con el bit

IRP del registro de estado, seleccionan el banco.

Un programa que borra una zona de memoria puede ser un ejemplo de aplicacin

de direccionamiento indirecto. El programa sera como el siguiente:

BCF STATUS,IRP ; Seleccin del banco 0 de memoria.

MOVLW 0X20 ; Mueve el valor 20h al registro W

MOVWF FSR ; Carga valor de W en FSR

SIGUIENTE CLRF INDF ; Borra la posicin de memoria que marca FSR

INCF FSR,1 ; Incrementa valor del FSR

BTFSS FSR,4 ; Test del bit 4 del FSR, si es 1, no ejecuta la

; siguiente instruccin y salta.

GOTO SIGUIENTE ; Vuelve a SIGUIENTE.

Este programa ejemplo borrara la memoria de datos desde la posicin h20 hasta

h2F.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

19

2.2.3 Registros y recursos comunes.

2.2.3.1 Registro de Estado.

Es un registro formado por 8 bits, que contiene el estado de la UAL, del RESET y selecciona

el banco de la memoria de datos sobre la que queremos trabajar.. Por esta ltima causa, el

registro de estado se encuentra en todos los bancos, y en la misma posicin.

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

IRP RP1

RP0 TO

PD Z DC

C

bit7 bit0

A continuacin se muestra la funcin de cada bit del registro de estado.

bit 7 IRP: Seleccin de bancos para el direccionamiento indirecto.

1 = Banco 2,3 (100h 1FFh)

0 = Banco 0,1 (00h FFh)

bit 6:5 RP1:RP0: Seleccin del banco de la memoria de datos para el

direccionamiento directo.

11 = Banco 3 (180h 1FFh)

10 = Banco 2 (100h 17Fh)

01 = Banco 1 (80h FFh)

00 = Banco 0 (00h 7Fh)

bit 4 TO: Timer Out.

1 = Tras conectar Vdd o ejecutar CLRWDT o SLEEP.

0 = Al rebasar el WDT

bit 3 PD: Power Down

1 = Tras conectar Vdd o ejecutar CLRWDT.

0 = Al ejecutar la instruccin SLEEP".

bit 2 Z: Bit de cero.

1 = El resultado de una operacin es 0.

0 = El resultado es distinto de 0.

bit 1 DC: Acarreo en el 4 bit de menos peso.

1 = Acarreo en la suma y no en la resta.

0 = Acarreo en la suma y no en la resta.

bit 0 C: Acarreo en el 8 bit.

1 = Acarreo en la suma y no en la resta.

0 = Acarreo en la suma y no en la resta.

Estos dos ltimos bits, en la suma representan lo que se conoce comnmente con acarreo, sin

embargo en la resta realizan la funcin de bit de signo (bit de Borrow), indicando que el

resultado es negativo si Borrowes 0, y positivo si es 1.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

20

2.2.3.2 Registro de Opciones.

El registro de opciones es un registro de lectura-escritura, que contiene los bits de

configuracin del divisor de frecuencia del TMR0/WDT, de las interrupciones externas, del

TMR0, y la configuracin de las Puerta B con cargas Pull-Up.

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

RBPU INTEDG T0CS T0SE

PSA

PS2 PS1

PS0

bit7 bit0

bit 7 RBPU: Conexin de cargas Pull-Up para la Puerta B.

1 = Todas las cargas Pull-Up desconectadas.

0 = Todas las cargas Pull-Up conectadas.

bit 6 INTEDG: Tipo de flanco para la interrupcin.

1 = RB0/INT sensible a flanco ascendente.

0 = RB0/INT sensible a flanco descendente.

bit 5 T0CS: Fuente de reloj para el TMR0.

1 = Pulsos introducidos por T0CKI (contador).

0 = Pulsos de reloj interno Fosc/4 (temporizador).

bit 4 T0SE: Tipo de flanco activo del T0CKI.

1 = Incremento del TMR0 cada flanco descendente.

0 = Incremento del TMR0 cada flanco ascendente.

bit 3 PSA: Asignacin del divisor de frecuencia.

1 = Se le asigna al WDT.

0 = Se le asigna al TMR0.

bit 2-0 PS2:PS0: Valor del divisor de frecuencia.

Valor Divisin del TMR0 Divisin del WDT

000 1:2 1:1

001 1:4 1:2

010 1:8 1:4

011 1:16 1:8

100 1:32 1:16

101 1:64 1:32

110 1:128 1:64

111 1:256 1:128

Para conseguir asignar 1:1 al divisor de frecuencia en el TMR0, se le asigna el

divisor al WDT.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

21

2.2.3.3 Palabra de configuracin.

La Palabra de Configuracin est formada por 14 bits. Se utiliza para la seleccin de distintos

aspectos de la configuracin del dispositivo segn las necesidades de la aplicacin. Su

localizacin en la memoria de programa es la 2007h. Esta posicin no es accesible durante el

modo de funcionamiento normal, por lo que estos registros debern ser configurados en la

fase de programacin.

CP1 CP0 CP1

CP0 CP1

CP0 - BODEN CP1 CP0

PWRTE

WDTE FOSC1 FOSC0

bit13 bit0

bit 13-8 CP<1:0>: Bits de proteccin de cdigo.

5-4:

bit 7 No implementado: Su lectura es 1.

bit 6 BODEN: Deteccin del Brown-Out (Fallo de alimentacin)

1 = deteccin activada.

0 = Deteccin desactivada.

bit 3 PWRTE: Activacin del temporizador Power-Up

1 = Desactivado.

0 = Activado.

bit 2 WDTE: Activacin del Watchdog (perro guardin)

1 = Activado

0 = Desactivado.

bit 1-0 FOSC1-FOSC0: Seleccin del tipo de oscilador.

11 = Oscilador RC.

10 = Oscilador HS

01 = Oscilador XT

00 = Oscilador LP

512 1k 2k

11 Off Off Off

10 Off Off alta On

01 Off alta On alta On

00 On On On

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

22

2.3 Oscilador.

El circuito de oscilacin se utiliza para generar las seales de reloj en el sistema necesarias

para la ejecucin de instrucciones y para el funcionamiento de los perifricos.

Existen hasta ocho tipos de osciladores. Los distintos tipos permiten mayor flexibilidad del

dispositivo segn las necesidades, as los hay de muy bajo coste, como las redes RC, y otros

de bajo consumo como son los cristales de cuarzo del modo LP.

La configuracin de un oscilador u otro se realiza mediante los bits FOSC2, FOSC1 Y

FOSC0 de la palabra de configuracin. No todos los modelos poseen la posibilidad de

configurar cualquier tipo de oscilador, en estos casos slo tienen los bit FOSC1 Y FOSC0 en

la palabra de configuracin. Los valores de estos bits para la configuracin de los distintos

osciladores son los que se pueden ver en las tablas 2.1 y 2.2.

TABLA 2.1 Seleccin del modo de oscilacin con FOSC1:FOSC0.

Bits de

configuracin

FOSC1:FOSC0

Modo

OSC

Ganancia de los

inversores internos

Comentarios

11 RC

Solucin ms barata (slo requiere una resistencia y

un condensador). Mxima variacin del tiempo

base.

Modo del dispositivo por defecto

10 HS Ganancia alta

Cristal de cuarzo para aplicaciones de alta

frecuencia. Es el modo que ms potencia consume

de los tres cristales.

01 XT Ganancia media

Cristal de cuarzo para un rango de frecuencias

estndar.

00 LP Ganancia baja

Cristal de cuarzo para aplicaciones de baja

frecuencia. Es el modo que menos potencia

consume de los tres cristales.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

23

TABLA 2.2 Seleccin del modo de oscilacin con FOSC2:FOSC0.

Bits de

configuracin

FOSC2:FOSC0

Modo

OSC

Ganancia de

los

inversores

internos

Comentarios

111

EXTRC con

CLKOUT

Red RC externa sacando la seal de oscilacin por la

patilla CLKOUT. Solucin barata. Mxima variacin

en el tiempo base. Modo del dispositivo por defecto

110 EXTRC

Red RC externa. Barata solucin. Mxima variacin

en el tiempo base. La seal de oscilacin no sale al

exterior.

101

INTRC con

CLKOUT

Red RC interna sacando la seal de oscilacin por la

patilla CLKOUT. Es la solucin ms barata.

Oscilador de 4MHz.

100 INTRC

Red RC interna. La seal de oscilacin no sale al

exterior. Solucin ms barata. Oscilador de 4MHz.

011 Reservado

10 HS Ganancia alta

Cristal de cuarzo para aplicaciones de alta frecuencia.

Es el modo que ms potencia consume de los tres

cristales.

01 XT

Ganancia

media

Cristal de cuarzo para un rango de frecuencias

estndar.

00 LP

Ganancia

baja

Cristal de cuarzo para aplicaciones de baja frecuencia.

Es el modo que menos potencia consume de los tres

cristales.

La diferencia entre los tres ltimos viene dada por la ganancia de los inversores internos, que

son los que modifican la frecuencia. En general siempre se opta por la opcin con menor

ganancia posible que cumpla las especificaciones. Esto implicar menores corrientes y con

ello menor consumo de potencia.

En la figura 2.4 se ve el modo de conexin para resonadores de cristal o de cuarzo. En este

caso se conectan a las patillas OSC1 y OSC2, usando esta ltima como realimentacin.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

24

Figura 2.4 Operacin de osciladores en los modos HS, XT o LP.

Nota 1: La resistencia en serie, R

S,

es necesaria para cristales de alta tecnologa.

2: La resistencia de realimentacin, R

F

, vara entre 2 y 10 M.

3: Dependiendo del dispositivo, el buffer de la lgica interna puede estar tanto antes

como despus del inversor.

Para una red RC el modo de conexin utilizar nicamente la patilla OSC1. La frecuencia de

oscilacin depender de V

DD

, R

EXT

y de C

EXT

(figura 2.5). El fabricante recomienda que R

EXT

tenga un valor de entre 3K y 100K y que C

EXT

sea mayor de 20pF. Adems la frecuencia

del oscilador/4 se obtiene a travs de la patilla OSC2, en caso de que est configurada en los

modos EXTRC o INTRC con CLKOUT, se puede usar para sincronizacin de otras lgicas.

Figura 2.5 Operacin en modo RC.

Nota 1: Esta patilla tambin puede ser configurada como una E/S de propsito general.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

25

Como un dispositivo incrementa su voltaje de alimentacin desde 0 hasta V

DD

, el oscilador

tardar un tiempo en funcionar correctamente. Este tiempo de comienzo o Start-Up depende

de muchos factores:

a) Para los osciladores RC depende del valor de la resistencia y condensador usado,

tiempo de subida de V

DD

, y temperatura del sistema.

b) Para los osciladores de cristales los factores que intervienen son la frecuencia del

cristal, los valores de la resistencia en serie, R

S

y de los condensadores C1 y C2, el

tiempo de subida de V

DD

, la temperatura del sistema, la seleccin del modo de

oscilador, la composicin del circuito oscilador, y el ruido del sistema.

En la figura 2.6 se muestra un ejemplo de StartUp. Se puede ver que la seal de oscilacin

est centrada en V

DD

/2, siendo el valor pico a pico durante el arranque del oscilador bastante

bajo (menos del 50% de V

DD

).

Figura 2.6 Caracterstica Start-Up de un oscilador.

Siempre que se quiera grabar un PIC es necesario consultar las hojas de caractersticas para la

configuracin del oscilador.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

26

2.4 Reset

La funcin del reset es la de dejar al sistema en un estado conocido. Existen varias fuentes de

RESET:

a) Power On Reset (POR).

b) Activacin de MCLR durante funcionamiento normal.

c) Activacin de MCLR en el modo de reposo

d) Desbordamiento del WDT durante funcionamiento normal.

e) Reset de Brown-Out (BOR).

f) Reset por error de paridad (PER).

La figura 2.7 se muestra un bloque simplificado de la lgica que gobierna el reset del sistema,

para un caso general.

En esta figura se puede ver una zona denominada OST/PWRT, que consiste en:

a) Power-up Timer (PWRT): Es un temporizador que proporciona un retardo de

72ms a partir de un reset de tipo POR o BOR, de tal forma que el PIC se mantiene

reseteado durante este tiempo, as al finalizar la temporizacin la tensin de

alimentacin tendr un valor aceptable. Este temporizador se habilita mediante el

bit PWRT de la palabra de configuracin. Para generar este retardo existe un

circuito interno RC dedicado.

b) Oscilador Start-Up Timer (OST): Este oscilador proporciona un retardo de 1024

veces el periodo de oscilacin (desde OSC1) despus del retardo PWRT. De esta

forma se asegura que el oscilador cristal o cermico es estable cuando el PIC

empieza a funcionar. Este retardo slo funciona cuando el PIC se ha configurado

para usar un oscilador XT, HS o LP y el reset es tipo POR, BOR o de wake-up

desde el modo de reposo (sleep).

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

27

Figura 2.7 Lgica que gobierna el Reset de un sistema.

Nota 1: Este es un oscilador distinto al oscilador del pin CLKIN o al oscilador interno INTRC.

2: Las caractersticas que estn encerrados en cuadros no estn disponibles en todos los modelos,

ver hoja de caractersticas del dispositivo.

3: En algunos modelos, este pin puede estar configurado como entrada de propsito general.

4: En los primeros microcontroladores PIC tenan la configuracin de modo que para PWRTE =1

estuviera habilitado, mientras que el resto de los modelos, la configuracin estaba definida

para PWRTE =0.

A continuacin (tabla 2.3) se muestran los distintos retardos para las posibles situaciones en

las que se puede ver el sistema.

TABLA 2.3 Retardos tpicos segn las situaciones.

TIEMPO DE POWER-UP

CONFIGURACIN

DEL OSCILADOR

Habilitado Deshabilitado

BROWN-OUT

RESET

WAKE-UP

DESDE SLEEP

XT, HS, LP 72 ms + 1024T

OSC

1024T

OSC

72 ms + 1024T

OSC

1024T

OSC

RC 72 ms

(1)

72 ms

(1)

Nota 1: Dispositivos con oscilador Interno/Externo RC tienen un retardo de 250s.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

28

El Power-on Reset consiste en la activacin del reset cuando se detecta la conexin de la

alimentacin al dispositivo. Dos topologas para el circuito de POR se pueden ver en la figura

2.8, siendo la primera para el caso general y la segunda para el caso en que V

DD

crezca de

forma lenta.

Nota 1: La resistencia es opcional.

Figura 2.8 Topologas para el circuito de POR.

En el segundo caso el diodo ayuda a la descarga del condensador cuando V

DD

disminuye su

valor.

Las siguientes figuras (2.9 2.12) muestran el comportamiento temporal de las seales segn

el caso.

Figura 2.9 Secuencia de Time-out en subida de alimentacin. MCLRconectado a V

DD

.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

29

Figura 2.10 Secuencia de Time-out en subida de alimentacin. MCLRno conectado a V

DD

.

(Caso1).

Figura 2.11 Secuencia de Time-out en subida de alimentacin. MCLRno conectado a V

DD

.

(Caso2).

Figura 2.12 Secuencia de Time-out en subida de alimentacin. MCLRconectado a V

DD

(tiempo de subida lento).

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

30

El Brown-out Reset consiste en producir un reset en el sistema cuando la tensin de

alimentacin V

DD

cae por debajo de un determinado valor, especfico para cada PIC. Los que

tengan implementados el BOR, tienen un parmetro (35), que es el tiempo mnimo que debe

estar V

DD

por debajo de la tensin de reset, para que ste se produzca. Esto asegura que el

elemento no continua la ejecucin del programa fuera de los rangos vlidos de operacin.

Este tipo de reset se puede habilitar con el bit BODEN de la Palabra de Configuracin. Una

vez que el nivel de la alimentacin se restablezca, hay un retardo de 72ms en desactivarse el

reset interno.

Algunas de las situaciones de Brown-Out Reset se muestran en la figura 2.13.

Figura 2.13 Situaciones de Brown-out Reset.

Posibles circuitos usados para un BOR, cuando el circuito no tiene internamente el detector

implementado, o cuando la tensin que venga configurada no nos interesa, se muestran en las

figuras 2.14 y 2.15.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

31

Figura 2.14 Circuito externo 1 de Brown-out.

Este circuito activar el reset cuando V

DD

est por debajo de (Vz + 0.7V), donde Vz

es el voltaje Zener del diodo.

Nota 1: El circuito de Brown-out Reset interno debe de estar deshabilitado

cuando se use esta configuracin.

2: Los valores de las resistencias dependen de las caractersticas del

transistor.

Figura 2.15 Circuito externo 2 de Brown-out.

Nota 1: Este circuito de BOR es ms barato, pero menos exacto. El transistor Q1 se

corta cuando V

DD

baja de cierto nivel tal como:

V 7 . 0

R2 R1

R1

VDD =

+

2: El circuito de Brown-out Reset interno debe de estar deshabilitado cuando

se use esta configuracin.

3: Los valores de las resistencias dependen de las caractersticas del

transistor.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

32

Debido a que existen distintas fuentes de reset, es necesario en determinadas ocasiones, saber

que tipo de reset se ha producido. Esto se hace consultando los bits POR y BOR del registro

PCON, y PD del Registro de Estado (tabla 2.4). La tabla 2.5 muestra la forma en que afecta

el Reset a los distintos registros.

TABLA 2.4 Bits de estado y su significado.

POR BOR TO PD

Tipo de Reset

0 x 1 1 Power-On Reset.

0 x 0 x

Incorrecto, TO est a 1 en POR .

0 x x 0

Incorrecto, PD est a 1 en POR .

1 0 1 1 Brown-Out Reset.

1 1 0 1 WDT Reset.

1 1 0 0 WDT Wake-Up.

1 1 u u

MCLR reset en funcionamiento normal.

1 1 1 0

MCLR reset durante SLEEP.

Legenda: u: valor anterior. x: desconocido.

TABLA 2.5 Condiciones de inicializacin de los registros especiales.

Registro

Power-On Reset

Brown-Out Reset

MCLR durante:

-funcionamiento normal

-SLEEP

WDT Reset

Wake-up desde SLEEP

mediante:

-Interrupciones

-Temporizador del WDT

ADCAPL 0000 0000 0000 0000 uuuu uuuu

ADCAPH 0000 0000 0000 0000 uuuu uuuu

ADCON0 0000 00-0 0000 00-0 uuuu uu-u

ADCON ---- -000 ---- -000 ---- -uuu

ADRES xxxx xxxx uuuu uuuu uuuu uuuu

ADTMRL 0000 0000 0000 0000 uuuu uuuu

ADMRH 0000 0000 0000 0000 uuuu uuuu

CCP1CON --00 0000 --00 0000 --uu uuuu

CCP2CON 0000 0000 0000 0000 uuuu uuuu

CCPR1L xxxx xxxx uuuu uuuu uuuu uuuu

CCPR1H xxxx xxxx uuuu uuuu uuuu uuuu

CCPR2L xxxx xxxx uuuu uuuu uuuu uuuu

CCPR2H xxxx xxxx uuuu uuuu uuuu uuuu

CMCON 00-- 0000 000000 uu-- uuuu

EEADR xxxx xxxx uuuu uuuu uuuu uuuu

EECON1 ---0 x000 ---0 q000 ---0 uuuu

EECON2 - - -

EEDATA xxxx xxxx uuuu uuuu uuuu uuuu

FSR xxxx xxxx uuuu uuuu uuuu uuuu

GPIO --xx xxxx --uu uuuu --uu uuuu

I2CADD 0000 0000 0000 0000 uuuu uuuu

I2CBUF xxxx xxxx uuuu uuuu uuuu uuuu

I2CCON 0000 0000 0000 0000 uuuu uuuu

I2CSTAT --00 0000 --00 0000 --uu uuuu

INDF - - -

INTCON 0000 000x 0000 000u uuuu uuuu

LCDCON 00-0 0000 00-0 0000 uu-u uuuu

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

33

Registro

Power-On Reset

Brown-Out Reset

MCLR durante:

-funcionamiento normal

-SLEEP

WDT Reset

Wake-up desde SLEEP

mediante:

-Interrupciones

-Temporizador del WDT

LCDD00 a LCDD15 xxxx xxxx uuuu uuuu uuuu uuuu

LCDPS ---- 0000 ---- 0000 ----uuuu

LCDPS 1111 1111 1111 1111 uuuu uuuu

OPTION_REG 1111 1111 1111 1111 uuuu uuuu

OSCCAL 0111 00-- uuuu uu-- uuuu uu--

PCL 0000 0000 0000 0000 PC+1

(2)

PCLATH ---0 0000 ---0 0000 ---u uuuu

PCON ---- --0u ---- --uu ---- --uu

PIE1 0000 0000 0000 0000 uuuu uuuu

PIE2 ---- ---0 ---- ---0 ---- ---u

PIR1 0000 0000 0000 0000 uuuu uuuu

PIR2 ---- ---0 ---- ---0 ---- ---u

PORTA --xx xxxx --uu uuuu --uu uuuu

PORTB xxxx xxxx uuuu uuuu uuuu uuuu

PORTC xxxx xxxx uuuu uuuu uuuu uuuu

PORTD xxxx xxxx uuuu uuuu uuuu uuuu

PORTE ---- -xxx ---- -uuu ---- -uuu

POTF 0000 0000 0000 0000 uuuu uuuu

PORTG 0000 0000 0000 0000 uuuu uuuu

PR2 1111 1111 1111 1111 1111 1111

PREFA 0000 0000 0000 0000 uuuu uuuu

PREFB 0000 0000 0000 0000 uuuu uuuu

RCSTA 0000 --00x 0000 --00x uuuu uuu

RCREG 0000 0000 0000 0000 uuuu uuuu

SLPCON 0011 1111 0011 1111 uuuu uuuu

SPBRG 0000 0000 0000 0000 uuuu uuuu

SSPBUF xxxx xxxx uuuu uuuu uuuu uuuu

SSPCON 0000 0000 0000 0000 uuuu uuuu

SSPADD 0000 0000 0000 0000 uuuu uuuu

SSPSTAT 0000 0000 0000 0000 uuuu uuuu

STATUS 0001 1xxx 000q quuu

uuuq quuu

T1CON --00 0000 --uu uuuu --uu uuuu

T2CON -000 0000 -000 0000 -uuu uuuu

TMR0 xxxx xxxx uuuu uuuu uuuu uuuu

TMR1L xxxx xxxx uuuu uuuu uuuu uuuu

TMR1H xxxx xxxx uuuu uuuu uuuu uuuu

TMR2 0000 0000 0000 0000 uuuu uuuu

TRIS --11 1111 --11 1111 --uu uuuu

TRISA --11 1111 --11 1111 --uu uuuu

TRISB 1111 1111 1111 1111 uuuu uuuu

TRISC 1111 1111 1111 1111 uuuu uuuu

TRISE 0000 111 0000 111 uuuu uuu

TRISF 1111 1111 1111 1111 uuuu uuuu

TRISG 1111 1111 1111 1111 uuuu uuuu

TXREG 0000 0000 0000 0000 uuuu uuuu

TXSTA 0000 010 0000 010 uuuu uuu

VRCON 000- 0000 000- 0000 uuu- uuuu

W xxxx xxxx uuuu uuuu uuuu uuuu

Legenda: u = valor anterior x = desconocido = no implementado q = depende de las condiciones

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

34

2.5 Temporizador y Perro Guardin.

En este apartado se tratar el funcionamiento del TMR0 en conjuncin con el Perro Guardin

o Watchdog.

El TMR0 en su forma general tiene las siguientes caractersticas:

a) Contador/Temporizador de 8 bits.

b) Permite su lectura y escritura.

c) La fuente de reloj se puede seleccionar, pudiendo ser externa (contador) o interna

(temporizador).

d) La fuente externa puede ser seleccionada para que acte cuando aparezca un flanco

de bajada o un flanco de subida.

e) Se puede seleccionar que se produzca una interrupcin cuando haya rebose, es

decir, pase de FFh a 00h.

f) Se le puede asignar un divisor de frecuencia de 8 bits programable.

Por otro lado el perro guardin o Watchdog (WDT) es un temporizador con un oscilador RC,

que no requiere ningn elemento externo, funcionando incluso cuando el oscilador principal

del sistema no lo hace (modo de reposo).

La habilitacin del perro guardin se realiza con el bit WDTE de la palabra de configuracin.

Si el WDT est funcionando, cuando ste rebose se producir un reset del PIC. En caso de que

el PIC en el momento del rebose del WDT se encuentre en modo de reposo, lo que se

producir es el despertar de ste, continuando la ejecucin del programa.

El periodo nominal del WDT es de 18 ms, que puede variar en funcin de la temperatura,

V

DD

, etc. (habr que ver las caractersticas elctricas). Adems si se quieren tiempos mayores

se le puede asignar el divisor de frecuencia que lo puede aumentar hasta 1:128.

Este divisor de frecuencia es el mismo que funcionar con el TMR0, con lo cual, o acta

sobre el TMR0 o sobre el WDT, pero nunca puede hacerlo sobre los dos a la vez.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

35

La forma de programar el divisor es con el registro de opciones:

bit 3 PSA: Asignacin del divisor de frecuencia.

1 = Se le asigna al WDT.

0 = Se le asigna al TMR0.

bit 2-0 PS2:PS0: Valor del divisor de frecuencia.

Valor Divisin del TMR0 Divisin del WDT

000 1:2 1:1

001 1:4 1:2

010 1:8 1:4

011 1:16 1:8

100 1:32 1:16

101 1:64 1:32

110 1:128 1:64

111 1:256 1:128

Para conseguir asignar 1:1 al divisor de frecuencia en el TMR0, se le asigna el

divisor al WDT.

En la figura 2.16 se puede ver el diagrama de bloques del funcionamiento del WDT y el

TMR0, con el divisor de frecuencias.

Figura 2.16 Diagrama de bloques del TMR0/WDT con el predivisor.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

36

Como se puede ver, para el TMR0, el divisor de frecuencia acta como un prescaler, es decir,

primero divide la fuente de reloj y luego esta fuente dividida acta sobre el TMR0. Para el

WDT, sin embargo, es al revs, primero cuenta y luego acta sobre la seal, es decir, lo hace

como postscaler.

Cuando tenemos habilitado el perro guardin, para que el sistema no se resetee, se ha de

inicializar peridicamente el WDT. Esto se consigue con las instrucciones CLRWDT o

SLEEP. Adems se recomienda por parte del fabricante, que antes de modificar el postscaler

se debe ejecutar la instruccin CLRWDT, ya que si no, se puede producir el reset del PIC.

2.6 Puertas E/S.

Las puertas de E/S digital son el perifrico ms simple de todos los que aparecen en los PIC y

nos servirn para leer o escribir valores digitales desde o hacia el exterior. En algunos puertos

estos pines estn multiplexados con otras funciones alternativas (convertidores A/D, E/S

serie, etc.). En el caso que lo tengamos para esa funcin, el pin no podr funcionar como E/S

digital.

Los pines de las puertas E/S pueden ser seleccionados de forma individual para que acten

como pines de entrada o de salida, a travs de los registros TRIS, de tal forma que si

TRISX<n> es:

0 => Pin n de la puerta X acta como salida.

1 => Pin n de la puerta X acta como entrada.

Cuando se produce un reset TRIS se pone a 1, configurando as las puertas como entradas y

evitando que se active indebidamente algn dispositivo externo que estuviera conectado al

PIC.

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

37

La configuracin tpica para las puertas E/S se ve en la figura 2.17.

Figura 2.17 Diagrama de bloques tpico de una puerta E/S.

2.7 Modo de reposo o SLEEP.

El modo de reposo o SLEEP, hace entrar al dispositivo en el estado de menor consumo de

potencia. En este modo deja de funcionar el oscilador principal, as como los temporizadores

del dispositivo, salvo el Watchdog, y adems las lneas E/S mantienen su estado. Para acceder

al modo de reposo se utiliza la instruccin SLEEP.

Para obtener el mnimo consumo habra que desconectar los perifricos y las lneas E/S

deberan conectarse a V

DD

o V

SS

.

Las formas de salir del modo de reposo son:

1. Cualquier reset del dispositivo.

2. Rebose del Watchdog (si ste est activado).

Microcontroladores PIC de la Gama Media. 2. La Arquitectura de los PIC de la Gama Media

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

38

3. Mediante cualquier interrupcin producida mientras el dispositivo est en el modo

de reposo, tal como:

a. Flanco en el pin RB0/INT.

b. Cambio de estado en lneas de puerta.

c. Comparadores.

d. Conversores A/D.

e. Overflow en TMR1.

f. LCD.

g. Interrupcin por puerto serie sncrono, SSP.

h. Mdulos de captura.

Al salir del modo de reposo se ejecuta la siguiente instruccin a SLEEP.

Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

39

Captulo 3. Juego de instrucciones de los PIC de la Gama

Media.

3.1 Introduccin.

Las caractersticas del juego de instrucciones vienen determinadas por el tipo de arquitectura

que tienen los PIC:

La arquitectura Harvard,

Conjunto de instrucciones reducido (RISC).

Esto implica que:

a) Normalmente el bus de instrucciones es mayor que el de datos. De esta forma se

obtiene una mayor eficiencia adaptando los anchos de los buses a los

requerimientos de la arquitectura y, por tanto, se optimiza el funcionamiento.

b) Las instrucciones son de una nica palabra. Debido a lo anterior se disearn

memorias de un ancho igual al cdigo de operacin de las instrucciones, pudiendo

acceder a su lectura en un solo ciclo. Adems el tamao de la memoria coincidir

con el nmero de instrucciones que podemos almacenar, a diferencia de la

arquitectura Von Neumann, en donde suele existir, de forma general, un ratio de

2:1 (siendo la memoria de 4Kbytes, aproximadamente 2Kbytes son instrucciones).

c) Segmentacin de instrucciones. Esto consiste en ejecutar las instrucciones en

distintas fases, unas con acceso a memoria de instrucciones y otras con acceso a

memoria de datos. Al poder realizarse accesos simultneos a ambas memorias,

podemos ejecutar las instrucciones en un nico ciclo de instruccin.

d) El hecho de tener pocas instrucciones facilita el aprendizaje.

e) Arquitectura basada en registros. Todos los elementos de la arquitectura, incluido

el contador de programa (PC), se encuentran mapeados en la memoria de datos,

que a su vez est implementada fsicamente como registros.

Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

40

f) Instrucciones ortogonales: Son aquellas que permiten trabajar con todos los

registros del sistema y con todos los direccionamientos existentes. Esta simetra

permite una programacin ms eficiente. En la gama media existen nicamente

dos instrucciones no orientadas a registros, que son las instrucciones CLRWDT y

SLEEP.

3.2 Flujo de instrucciones. Segmentacin.

La entrada de reloj, se divide internamente por cuatro, obtenindose cuatro seales de reloj

denominadas Q1, Q2, Q3 y Q4. Internamente, el PC se incrementa cada Q1, la instruccin es

leda de la memoria de instrucciones y almacenada en el registro de instrucciones en Q4. Esa

instruccin es decodificada y ejecutada durante los siguientes Q1-Q4.

El flujo de instrucciones y el reloj se muestran en las figuras 3.1 y 3.2. Adems, estos ciclos

son los que denominaremos periodos de oscilacin del PIC (T

osc

).

Figura 3.1 Flujo de instrucciones y reloj.

Un ciclo de instruccin consiste precisamente en estos 4 ciclos de reloj Q1-Q4, y cada una de

las fases de la instruccin ocupa un ciclo.

Microcontroladores PIC de la Gama Media. 3. Juego de instrucciones de los PIC de la Gama Media.

Santiago Salamanca Mio Escuela de Ingenieras Industriales

David Arroyo Muoz Universidad de Extremadura

41

Estas dos fases son:

Fase de bsqueda (Fetch): Se incrementa en Q1 el PC, se lee y se lleva en Q4 a

registro de instrucciones.

Fase de ejecucin: En Q2 se lee la memoria de datos para los operandos y en Q4 se

almacena en la memoria de datos el resultado.

Debido a que en cada una de las fases se accede a una memoria, y que los accesos a memoria

pueden solaparse, aparece la segmentacin, es decir, se ejecuta una instruccin por ciclo de

instruccin, excepto las instrucciones de salto incondicional, ya que es en la fase de ejecucin

donde se calcula la direccin destino. En este caso tarda dos ciclos de instruccin.

T

OSC

0 T

OSC

1 T

OSC

2 T

OSC

3 T

OSC

4

T

OSC

5

Buscar 1 Ejecutar 1 1. MOVLW 55h

2. MOVWF PORTB Buscar 2 Ejecutar 2

Buscar 3 Ejecutar 3 3. CALL SUB_1

4. BSF PORTA,3

Buscar 4 Detencin

Buscar SUB_1 Ejecutar SUB_1

Buscar SUB_1+1

Figura 3.2 Segmentacin de instrucciones

Existen adems las instrucciones de salto condicional, que pueden durar 1 2 ciclos en

funcin del resultado (btfss, btfsc, decfsz y incfsz).

3.3 El formato de las instrucciones.

Las instrucciones de los PIC se pueden dividir en cuatro categoras: