Академический Документы

Профессиональный Документы

Культура Документы

DSP Integrated Circuits 4

Загружено:

brindkowsi0 оценок0% нашли этот документ полезным (0 голосов)

112 просмотров3 страницыdspic univ qp

Оригинальное название

Dsp Integrated Circuits 4

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документdspic univ qp

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

112 просмотров3 страницыDSP Integrated Circuits 4

Загружено:

brindkowsidspic univ qp

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 3

84

01

Reg. No. :

Question Paper Code :

20107

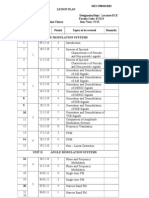

M.E./M.Tech. DEGREE EXAMINATION, JANUARY 2011.

First Semester

VLSI Design

(Common to Applied Electronics)

252101 DSP INTEGRATED CIRCUITS

(Regulation 2010)

Maximum : 100 marks

Time : Three hours

84

0

Answer ALL questions.

PART A (10 2 = 20 marks)

1.

List few applications of ASICs?

2.

Draw the two input NAND gate using MOS logic.

3.

Calculate the % reduction in computation via FFT when N = 512. Assume

radix - 2 DIT algorithm.

4.

Write the discrete cosine transform pair.

5.

If x(n ) = { 0,1, 2, 7, 6.5, 2.5, 7.5}, find x (3n ) .

Define first order coefficient sensitivity of digital system.

7.

What are the characteristics of ideal DSP architecture?

8.

State the advantages of Bitserial system (DSP).

9.

Name the FFT processor, IC No.

10.

Compare Conventional number system with residue number system.

01

6.

(a)

Describe with the help of block diagram DSP system, design from first

principles.

Or

(b)

Write short notes on

84

11.

PART B (5 16 = 80 marks)

(i)

CMOS circuit of two input XOR gate and its working principle and

VLSI layout.

(ii)

VLSI process technologies.

(a)

84

01

12.

Explain the least mean square (LMS) method of finding optimal weight

vector for stationary random signals. (Assume Adaptive transversal

filter)

Or

(b)

(i)

Find the DFT of the following sequences.

(1)

x (n ) = (0.75) n , n = 0,1, 2, 7

= 0, n = 8,9, 15

(2)

(ii)

(a)

State and explain the sampling process of analog signals.

Describe a rational sampling rate converter with frequency conversion

(i)

(ii)

84

0

factor L/M = 0.8

13.

x (n ) = (n 1) + (n 2), n = 0,1, 2, 7.

Sketch a block diagram of sampling rate converter.

Find the difference equation for the sampling rate converter.

Or

(b)

(i)

Draw the three different structure for H(z)

H ( z ) = ( z 1 + 1) ( z 2 + 0.5 z 1 + 0.06) ( z 1 + 0.6)

(ii)

Explain a method of measurement of round off noise in digital

system.

(a)

(i)

Differentiate between multiprocessors with multicomputers.

(ii)

Explain systolic and wave front arrays and its applications.

01

14.

84

(b)

Or

What is complex PE? Discuss the hardware implementation based on

complex PE? What are its merits and demerits of such system?

20107

(a)

Design a complex multiplier using two different techniques and compare

their performance.

Or

(b)

84

01

15.

Write short notes on

(i)

Residue number system.

(ii)

Layout of VLSI circuit by taking an example.

84

01

84

0

20107

Вам также может понравиться

- Computer Processing of Remotely-Sensed Images: An IntroductionОт EverandComputer Processing of Remotely-Sensed Images: An IntroductionОценок пока нет

- DSP Integrated Circuits 3Документ3 страницыDSP Integrated Circuits 3brindkowsiОценок пока нет

- Digital Signal Processing Question PaperДокумент2 страницыDigital Signal Processing Question PaperMehul SolankiОценок пока нет

- CS331 Digital Signal Processing Nov Dec 2003Документ3 страницыCS331 Digital Signal Processing Nov Dec 2003Chandru SekarОценок пока нет

- DSPQNANSДокумент16 страницDSPQNANSEmmanuel Aron JoshuaОценок пока нет

- Question Paper Code:: Reg. No.Документ3 страницыQuestion Paper Code:: Reg. No.DhariniJeevanandamОценок пока нет

- r05320201 Digital Signal ProcessingДокумент8 страницr05320201 Digital Signal ProcessingSRINIVASA RAO GANTAОценок пока нет

- Digital Signal ProcessingДокумент7 страницDigital Signal ProcessingJagadeesh KumarОценок пока нет

- JNTU Old Question Papers 2007Документ8 страницJNTU Old Question Papers 2007Srinivasa Rao G100% (1)

- DSP QuestionsДокумент8 страницDSP Questionsjjshree79Оценок пока нет

- r05320201 Digital Signal ProcessingДокумент8 страницr05320201 Digital Signal ProcessingBharath LudiОценок пока нет

- EC2314Документ3 страницыEC2314Rakesh Kumar DОценок пока нет

- DSP Previous PapersДокумент8 страницDSP Previous PapersecehodaietОценок пока нет

- rr311102 Digital Signal ProcessingДокумент8 страницrr311102 Digital Signal ProcessingSRINIVASA RAO GANTAОценок пока нет

- Set No: 1: Code No: V3218/R07Документ6 страницSet No: 1: Code No: V3218/R07Viswa ChaitanyaОценок пока нет

- Set No: 1: Code: V3218/R07 Digital Signal Processing Time: 3 Hours Max. Marks: 80Документ4 страницыSet No: 1: Code: V3218/R07 Digital Signal Processing Time: 3 Hours Max. Marks: 80Manam Sundeep YadavОценок пока нет

- DSPДокумент95 страницDSPAbdulhafeez ShaikОценок пока нет

- 7Документ2 страницы7049 Narendran KОценок пока нет

- Reg. No: B.Tech. Degree Examination, June 2011: (For The Candidates Admitted From The Academic Year 2007-2008 Onwards)Документ3 страницыReg. No: B.Tech. Degree Examination, June 2011: (For The Candidates Admitted From The Academic Year 2007-2008 Onwards)abhinavch26Оценок пока нет

- Nr320402-Digital Signal ProcessingДокумент8 страницNr320402-Digital Signal ProcessingSRINIVASA RAO GANTAОценок пока нет

- Digital Signal ProcessingДокумент2 страницыDigital Signal ProcessingSreedeviRajithaОценок пока нет

- Signals & Systems EC403Документ3 страницыSignals & Systems EC403Shashank M ChanmalОценок пока нет

- B.E Degree Examinations: April/May 2016Документ3 страницыB.E Degree Examinations: April/May 2016PRAVEEN O.KОценок пока нет

- 07a51101 Digital Signal ProcessingДокумент8 страниц07a51101 Digital Signal ProcessingSRINIVASA RAO GANTAОценок пока нет

- DTSPДокумент4 страницыDTSPmonisa kannanОценок пока нет

- DSP (Ee8591) - Model 2Документ2 страницыDSP (Ee8591) - Model 2EEE DEPTОценок пока нет

- Euree 701Документ2 страницыEuree 701swaroop0309Оценок пока нет

- Cs2403 DSP Nov 2011 QPДокумент3 страницыCs2403 DSP Nov 2011 QPvijayshankar743Оценок пока нет

- Code - No: 07A6EC01: HN Eun HT e Btut HT Te Ut HN e UnДокумент8 страницCode - No: 07A6EC01: HN Eun HT e Btut HT Te Ut HN e UnSai SivaОценок пока нет

- Digital Signal Processing Question BankДокумент4 страницыDigital Signal Processing Question BanksharlisreeОценок пока нет

- r05320201 Digital Signal ProcessingДокумент8 страницr05320201 Digital Signal ProcessingSri LalithaОценок пока нет

- IT6502-Digital Signal ProcessingДокумент10 страницIT6502-Digital Signal ProcessingAnonymous 5rejZkKgОценок пока нет

- SCS6105200904 Digital Signals ProcessingДокумент5 страницSCS6105200904 Digital Signals ProcessingAmkelani Damian SikosanaОценок пока нет

- DSPДокумент2 страницыDSPSyed NajeebОценок пока нет

- IT6502-Digital Signal ProcessingДокумент10 страницIT6502-Digital Signal ProcessingMadhumitha RajasekaranОценок пока нет

- Digital Signal Processing QUESTION BANKДокумент5 страницDigital Signal Processing QUESTION BANKSaran SekaranОценок пока нет

- Digital Signal ProcessingДокумент7 страницDigital Signal ProcessingAhsan MalikОценок пока нет

- TE 2003 InstrumentationControlДокумент4 страницыTE 2003 InstrumentationControlShaharukh NadafОценок пока нет

- TE1Документ498 страницTE1Smith KashidОценок пока нет

- PART A (10 X 2 20 Marks)Документ5 страницPART A (10 X 2 20 Marks)dhakaruОценок пока нет

- Gujarat Technological University: InstructionsДокумент1 страницаGujarat Technological University: InstructionsMehul SolankiОценок пока нет

- Question Paper Code:: Reg. No.Документ2 страницыQuestion Paper Code:: Reg. No.Naveen KumarОценок пока нет

- X (N) (1,2,1) H (N) (1, - 2,2)Документ2 страницыX (N) (1,2,1) H (N) (1, - 2,2)mugaao8Оценок пока нет

- SOLDSPX06Документ16 страницSOLDSPX06Shafayet UddinОценок пока нет

- Question Paper Code:: Reg. No.Документ2 страницыQuestion Paper Code:: Reg. No.Nithiya MaharajanОценок пока нет

- Cusat DSP Question PaperДокумент14 страницCusat DSP Question PaperSabith PockerОценок пока нет

- EC2314 DSP Nov 2010 PDFДокумент3 страницыEC2314 DSP Nov 2010 PDFSyed MusthafaОценок пока нет

- Question Bank: Subject Code: Subject NameДокумент5 страницQuestion Bank: Subject Code: Subject NamemsurendiranОценок пока нет

- DSP Important Questions Unit-WiseДокумент6 страницDSP Important Questions Unit-WiseRasool Reddy100% (4)

- X (N) (F U (N)Документ2 страницыX (N) (F U (N)049 Narendran KОценок пока нет

- nr320402 Digital Signal ProcessingДокумент2 страницыnr320402 Digital Signal ProcessingSRINIVASA RAO GANTAОценок пока нет

- Signal Processing Architectures, 2008Документ2 страницыSignal Processing Architectures, 2008Rajesh KetОценок пока нет

- NR 410201 Digital Signal ProcessingДокумент8 страницNR 410201 Digital Signal ProcessingSrinivasa Rao GОценок пока нет

- Sixth Semester B Tech (Enginee Ing) Degree Examination December 2 10Документ2 страницыSixth Semester B Tech (Enginee Ing) Degree Examination December 2 10Abhishek EkОценок пока нет

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionОт EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionОценок пока нет

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsОт EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikОценок пока нет

- Analytical Modeling of Wireless Communication SystemsОт EverandAnalytical Modeling of Wireless Communication SystemsОценок пока нет

- LP - CT - Iv Sem EceДокумент5 страницLP - CT - Iv Sem EcebrindkowsiОценок пока нет

- ECE ARR Time TableДокумент59 страницECE ARR Time TablebrindkowsiОценок пока нет

- Mod 1-CT QPДокумент1 страницаMod 1-CT QPbrindkowsiОценок пока нет

- LP DPSD (It)Документ4 страницыLP DPSD (It)brindkowsiОценок пока нет

- DSP 1Документ2 страницыDSP 1Tina PrakashОценок пока нет

- For AwpДокумент65 страницFor AwpbrindkowsiОценок пока нет

- Model Exam - I Ns (IV Ece A&b)Документ2 страницыModel Exam - I Ns (IV Ece A&b)brindkowsiОценок пока нет

- Ece 5-8th Sem SyllabusДокумент113 страницEce 5-8th Sem SyllabusSanthosh KarthiОценок пока нет

- Fundamental AntennasДокумент147 страницFundamental Antennasbrindkowsi100% (1)

- POM SyllabusДокумент1 страницаPOM SyllabusbrindkowsiОценок пока нет

- Sap Retail Two Step PricingДокумент4 страницыSap Retail Two Step PricingShams TabrezОценок пока нет

- AS400 RPG400 BasicsДокумент148 страницAS400 RPG400 Basicscharaviz84100% (1)

- ZTE V4 RNC Commissioning and Integration TrainingДокумент2 страницыZTE V4 RNC Commissioning and Integration TrainingBeena SinghОценок пока нет

- Inglês - Degrees of ComparisonДокумент4 страницыInglês - Degrees of ComparisonVersehgi IIОценок пока нет

- Wearable BiosensorsДокумент16 страницWearable BiosensorsShreehari Haridasan100% (1)

- Shear and Diagonal Tension in BeamДокумент16 страницShear and Diagonal Tension in BeamMouy PhonThornОценок пока нет

- Samsung Galaxy Watch 5 Pro User ManualДокумент131 страницаSamsung Galaxy Watch 5 Pro User Manualzyron100% (1)

- Bibliography and FootnotesДокумент2 страницыBibliography and FootnotesHannah de VeraОценок пока нет

- 1.rle Rubrics For Case PresentationДокумент2 страницы1.rle Rubrics For Case PresentationKhristine EstosoОценок пока нет

- Executive Summary Report Julio13Документ8 страницExecutive Summary Report Julio13exxgineОценок пока нет

- Term Test Pointers For Review - 1st TermДокумент2 страницыTerm Test Pointers For Review - 1st Termjessica holgadoОценок пока нет

- 1506a E88tag3 PDFДокумент5 страниц1506a E88tag3 PDFmohammad javad golОценок пока нет

- FINAL ReportДокумент48 страницFINAL ReportMythri RangaswamyОценок пока нет

- Instruction Manual: Slit Lamp Bon SL-EДокумент20 страницInstruction Manual: Slit Lamp Bon SL-EVladimir LevchenkoОценок пока нет

- Blockchain Disruption in The Forex Trading MarketДокумент64 страницыBlockchain Disruption in The Forex Trading MarketVijayKhareОценок пока нет

- Differential Settlement at Bridge ApproaДокумент5 страницDifferential Settlement at Bridge ApproaVictor De los ReyesОценок пока нет

- The First-Fourth Books of The HitopadésaДокумент116 страницThe First-Fourth Books of The HitopadésaMiguel RosaОценок пока нет

- FДокумент102 страницыFTop channelОценок пока нет

- Pearson Letter To ParentsДокумент2 страницыPearson Letter To ParentsPatricia WillensОценок пока нет

- Anger Management: Gaurav Sharma 138Документ21 страницаAnger Management: Gaurav Sharma 138gaurav_sharma_19900Оценок пока нет

- 2021 3 AbstractsДокумент168 страниц2021 3 AbstractsLong An ĐỗОценок пока нет

- NeedScope On TechnologyДокумент22 страницыNeedScope On TechnologyNguyen Ngo Dinh PhuongОценок пока нет

- Solution PDFДокумент20 страницSolution PDFVard FarrellОценок пока нет

- Mecanica MD - AZG-UДокумент29 страницMecanica MD - AZG-UStefanoViganóОценок пока нет

- Motion in One Dimension QuestionДокумент6 страницMotion in One Dimension Questionabh_omega33% (3)

- Safety Data SheetДокумент7 страницSafety Data SheetJivendra KumarОценок пока нет

- Motorola Talkabout T82 PDFДокумент184 страницыMotorola Talkabout T82 PDFAlex TamayoОценок пока нет

- Researchpaper Should Removable Media Be Encrypted - PDF - ReportДокумент15 страницResearchpaper Should Removable Media Be Encrypted - PDF - ReportSakshi Dhananjay KambleОценок пока нет

- Stripper EZ-range US v3 Web-1Документ2 страницыStripper EZ-range US v3 Web-1irwin kurniadiОценок пока нет

- Centralized PurchasingДокумент2 страницыCentralized PurchasingbiyyamobulreddyОценок пока нет