Академический Документы

Профессиональный Документы

Культура Документы

AP9212

Загружено:

shankarАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

AP9212

Загружено:

shankarАвторское право:

Доступные форматы

DOC/LP/01/28.02.

02

LESSON PLAN LP AP9212

LP Rev. No: 00

Date: 07/09/12

Page 01 of 06

Sub Code Na!e: AP9212 Adva"#ed D$g$ta% S&'te! De'$g"

("$t : ) *+a"#, : -E.-AE Se!e'te+: )

(N)/ ) SE0(EN/)AL C)RC()/ DES)1N 9

Analysis of clocked synchronous sequential circuits and modelin! "tate diaram# state

ta$le# state ta$le assinment and reduction!Desin of synchronous sequential circuits!

desin of iterati%e circuits!A"& chart and reali'ation usin A"&.

Se''$o"

No.

/o2$#' to be #ove+ed /$!e Ref

/ea#,$"g

-et,od

1. Analysis of clocked sequential circuits! (ntroduction )0m 1 **

2.

Desin of an "equential +arity checker# Analysis of &oore

and &ealy sequential circuit $y sinal tracin and timin

charts

)0m 1 **

3.

ðod of constructin state ta$le and state ra+hs for

&oore and &ealy machines

)0m 1 **

4.

,eneral &odels for a clocked &ealy and &oore sequential

circuits.

)0m 1 **

5.

Desin of a sequence detector for &ealy and &oore

machines

)0m 1 **

6. -eduction of state ta$le usin state assinment )0m 1 **

7.

Determination of state equi%alence and circuit equi%alence

usin an im+lication ta$le

)0m 1 **

6.

(ncom+letely "+ecified "tate ta$les and deri%ation of fli+!

flo+ in+ut equations

)0m 1 **

9. ,uidelines for state assinments# one hot state assinment )0m 1 **

10. Desin of it.rati%e circuits# Desin of a com+arator )0m 1 **

11.

"tate &achine /"&0 Charts! D.ri%ation and reali'ation of

"& charts

)0m 1 **

DOC/LP/01/28.02.02

LESSON PLAN LP AP9212

LP Rev. No: 00

Date: 07/09/12

Page 02 of 06

Sub Code Na!e: AP9212 Adva"#ed D$g$ta% S&'te! De'$g"

("$t : )) *+a"#, : -E.-AE Se!e'te+: )

(N)/ )) AS7NC8RONO(S SE0(EN/)AL C)RC()/ DES)1N 9

Analysis of asynchronous sequential circuit 1 flo2 ta$le reduction!races!state

assinment!transition ta$le and +ro$lems in transition ta$le! desin of asynchronous

sequential circuit!"tatic# dynamic and essential ha'ards 1 data synchroni'ers 1 mi3ed

o+eratin mode asynchronous circuits 1 desinin %endin machine controller.

Se''$o"

No.

/o2$#' to be #ove+ed /$!e Ref

/ea#,$"g

-et,od

12. Analysis of Asynchronous sequential circuit ! Desin of

4undamental mode sequential circuit ! Primiti%e state

ta$le# state ta$le reduction and state assinment

)0m 1#2 **

15. Desin of Pulse mode sequential circuit! Primiti%e state

ta$le# state ta$le reduction and state assinment

)0m 1#2 **

16. Pro$lems in Asynchronous sequential circuits 1Cycles#

Critical race and 7on! Critical race

)0m 1#2 **

1). 8a'ards! "tatic# Dynamic and 9ssential 8a'ards )0m 1#2 **

1:. Desin of 8a'ard free s2itchin circuits! "tatic 8a'ard

and 9ssential 8a'ard elimination

)0m 1#2 **

1;. Pro$lems on 8a'ard free circuit 1 "tatic and 9ssential

8a'ard

)0m 1#2 **

18. <orkin +rinci+le of Data synchroni'er )0m 1#2 **

1=. Desin of mi3ed o+eratin mode asynchronous circuit )0m 1#2 **

20. Desin of >endin machine controller! Descri+tion/

"+ecification# 4"& desin ste+s# "tate diaram and state

ta$le

)0m 1#2 **

CA? 1 ( ;)m ! !

DOC/LP/01/28.02.02

LESSON PLAN LP AP9212

LP Rev. No: 00

Date: 07/09/12

Page 03 of 06

Sub Code Na!e: AP9212 Adva"#ed D$g$ta% S&'te! De'$g"

("$t : ))) *+a"#, : -E.-AE Se!e'te+: )

(N)/ ))) 9A(L/ D)A1NOS)S AND /ES/A*)L)/7 AL1OR)/8-S 9

4ault ta$le method!+ath sensiti'ation method 1 *oolean difference method!D alorithm

!?olerance techniques 1 ?he com+act alorithm 1 4ault in PLA 1 ?est eneration!D4?

schemes 1 *uilt in self test.

Se''$o"

No.

/o2$#' to be #ove+ed /$!e Ref

/ea#,$"g

-et,od

21. 4ault &odels! "tuck!at fault# *ridin fault# stuck!o+en fault

and ?em+orary faults

)0m 5 **

22. 4ault Dianosis of Diital systems! ?est eneration for

com$inational loic circuits! one dimensional +ath

sensiti'ation

)0m 5 **

25. *oolean Difference method )0m 5 **

26. D!Alorithm! "inular co%er# Pro+aation D!cu$es# Primiti%e

D!cu$e of a fault# D! intersection

)0m 5 **

2).

?olerance techniques! "tatic redundancy# Dynamic redundancy#

and 8y$rid redundancy

)0m 5 **

2:. "elf! +urin redundancy# "ift!out modular redundancy )0m 5 **

2;. 4ault in PLA and totally self!checkin PLA desin )0m 5 **

28. ?est eneration! Controlla$ility and o$ser%a$ility# Desin of

testa$le com$inational loic circuits

)0m 5 **

2=. Desin of testa$le sequential circuits )0m 5 **

50. *uilt in self test! *uilt!in Diital circuit O$ser%er /*(DCO0#

*uilt in test for >L"( chi+s

)0m 5 **

DOC/LP/01/28.02.02

LESSON PLAN LP AP9212

LP Rev. No: 00

Date: 07/09/12

Page 04 of 06

Sub Code Na!e: AP9212 Adva"#ed D$g$ta% S&'te! De'$g"

("$t : ): *+a"#, : -E.-AE Se!e'te+: )

(N)/): S7NC8RONO(S DES)1N (S)N1 PRO1RA--A*LE DE:)CES 9

Prorammin loic de%ice families 1 Desinin a synchronous sequential circuit usin

PLA/PAL 1 -eali'ation of finite state machine usin PLD 1 4P,A 1 @ilin3 4P,A!

@ilin3 6000.

Se''$o"

No.

/o2$#' to be #ove+ed /$!e Ref

/ea#,$"g

-et,od

51. Proramma$le Loic De%ices /PLD0! 7otations for

PLD# Desin methodoloy usin PLDAs

)0m 6 **

52. Desin of sequential PLA de%ices )0m 6 **

55. Desin of sequential PAL de%ices! 6!$it $inary

counter! state ta$le# B!ma+ and PAL diaram

)0m 6 **

56. 8!$it Parallel Cyclic -edundancy Check /C-C0

enerator! *lock diaram and PAL diaram

)0m 6 **

5). 4ield! Proramma$le ,ate Array /4P,A0! PL" 1)1#

PL"105

)0m 6 **

5:. Asynchronous "tate &achine Desin )0m 6 **

5;. "tate &achine Desin! Proram for the loic $locks#

B ma+s# im+lementation of the state ta$le

)0m 6 **

58. @ilin3 4P,A and @ilin3 6000 $lock diaram

e3+lanation

)0m 6 **

CA? (( 180m ! !

DOC/LP/01/28.02.02

LESSON PLAN LP AP9212

LP Rev. No: 00

Date: 07/09/12

Page 05 of 06

Sub Code Na!e: AP9212 Adva"#ed D$g$ta% S&'te! De'$g"

("$t : : *+a"#, : -E.-AE Se!e'te+: )

(N)/ : S7S/E- DES)1N (S)N1 :8DL 9

>8DL o+erators 1 Arrays 1 concurrent and sequential statements 1 +ackaes! Data flo2

1 *eha%ioral 1 structural modelin 1 com+ilation and simulation of >8DL code 1?est

$ench ! -eali'ation of com$inational and sequential circuits usin 8DL 1 -eisters 1

counters 1 sequential machine 1 serial adder 1 &ulti+lier! Di%ider 1 Desin of sim+le

micro+rocessor.

Se''$o"

No.

/o2$#' to be #ove+ed /$!e Ref

/ea#,$"g

-et,od

5=. (ntroduction to >8DL# Arrays and >8DL o+erators )0m )#: **

60.

Concurrent #"equential statements and Packaes!

Declaration# Deferred constants# Packae $ody

)0m )#: **

61.

(ntroduction to 2rite a +roram in Data flo2#

*eha%ioral and structural model

)0m )#: **

62.

Com+ilation and simulation of >8DL code # ?est

$ench! "timulus only# 4ull test $ench# "imulator

s+ecific# 8y$rid and 4ast test $ench

)0m

)#:

**

65.

"tructural >8DL code! 4ull Adder# &ulti+le3er#

Demulti+le3er# 9ncoder and Decoder

)0m )#: **

66.

*eha%ioral and Dataflo2 >8DL code! CB# ?# D fli+!

flo+

)0m )#: **

6).

Desin of "hift reisters 1 "("O# "(PO# P("O and

P(PO usin >8DL

)0m )#: **

6:. Desin of Counters and "erial adder usin >8DL )0m

)#:

**

6;.

Desin of &ulti+lier! *ooth# &odified *ooth and

Di%ider usin >8DL

)0m )#: **

68.

Desin of &icro+rocessor 2ith sim+le arithmetic

o+eration usin >8DL

)0m

)#:

**

CA? ((( ;)m ! !

DOC/LP/01/28.02.02

LESSON PLAN LP AP9212

LP Rev. No: 00

Date: 07/09/12

Page 06 of 06

Sub Code Na!e: AP9212 Adva"#ed D$g$ta% S&'te! De'$g"

*+a"#, : -E.-AE Se!e'te+: )

Cou+'e De%$ve+& P%a":

<eek

1 2 5 6 ) : ; 8 = 10 11 12 15

( (( ( (( ( (( ( (( ( (( ( (( ( (( ( (( ( (( ( (( ( (( ( (( (

Dnits

1 1 1 1 1

2 2

2 2

2 5 5 5

5 5 6 6 6 6 6 ) ) )

) )

CAT I CAT II

CAT III

RE9ERENCES

1 Charles 8.-oth Cr E4undamentals of Loic DesinF ?homson Learnin 2006

2 7ri+endra 7 *is2as ELoic Desin ?heoryF Prentice 8all of (ndia#2001

5 Para B.Lala E4ault ?olerant and 4ault ?esta$le 8ard2are DesinF * "

Pu$lications#2002

6 Para B.Lala EDiital system Desin usin PLDF * " Pu$lications#2005

) Charles 8 -oth Cr.FDiital "ystem Desin usin >8DLF ?homson learnin# 2006

: Doulas L.Perry E>8DL +rorammin $y 93am+leF ?ata &c,ra2.8ill ! 200:

P+e2a+ed b& A22+oved b&

S$g"atu+e

Na!e -.At,a22a" D+.S.1a"e', :a$d&a"at,a"

De'$g"at$o" A''$'ta"t P+ofe''o+/EC 8OD/EC

Date 07.09.2012 07.09.2012

Вам также может понравиться

- KONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY TERMINAL EXAMINATION-I ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITSДокумент2 страницыKONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY TERMINAL EXAMINATION-I ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITSshankarОценок пока нет

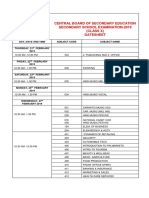

- Central Board of Secondary Education Secondary School Examination-2019 (Class X) DatesheetДокумент4 страницыCentral Board of Secondary Education Secondary School Examination-2019 (Class X) DatesheetPriyanka SharmaОценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (894)

- Ex05 - Question Paper Adaic - ModelДокумент2 страницыEx05 - Question Paper Adaic - ModelshankarОценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Ex06 - Answer Key Adaic Te-2Документ8 страницEx06 - Answer Key Adaic Te-2shankarОценок пока нет

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- Digital Signal Processing Introduction PartДокумент13 страницDigital Signal Processing Introduction Partshankar100% (1)

- Zero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyДокумент5 страницZero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyshankarОценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Introduction To MATLABДокумент36 страницIntroduction To MATLABViju JigajinniОценок пока нет

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- M.E. Applied Electronics - R2017Документ47 страницM.E. Applied Electronics - R2017Mr.R.Ragumadhavan ecestaffОценок пока нет

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- KONGUNADU COLLEGE M.E ECE I/I TIME TABLE 2018-19Документ1 страницаKONGUNADU COLLEGE M.E ECE I/I TIME TABLE 2018-19shankarОценок пока нет

- Design of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsДокумент11 страницDesign of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsshankarОценок пока нет

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Ec 6502 Principles of Digital Signal Processing - Question Bank - 2018Документ17 страницEc 6502 Principles of Digital Signal Processing - Question Bank - 2018shankarОценок пока нет

- MATLAB BasicsДокумент24 страницыMATLAB BasicsshankarОценок пока нет

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Kongunadu College of Engineering and TechnologyДокумент2 страницыKongunadu College of Engineering and TechnologyshankarОценок пока нет

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- NBA Modified RF&MW LPДокумент4 страницыNBA Modified RF&MW LPshankarОценок пока нет

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- Adaic TT 2016Документ2 страницыAdaic TT 2016shankarОценок пока нет

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- HTTPДокумент2 страницыHTTPshankarОценок пока нет

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Kongunadu College of Engineering and Technology, ThourpattiДокумент1 страницаKongunadu College of Engineering and Technology, ThourpattishankarОценок пока нет

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- Unit V: Time Varying Fields and Maxwell'S EquationsДокумент12 страницUnit V: Time Varying Fields and Maxwell'S EquationsshankarОценок пока нет

- WN Unit1 and Unit5Документ1 страницаWN Unit1 and Unit5shankar0% (1)

- CH 3 - FeedbackДокумент54 страницыCH 3 - FeedbackshankarОценок пока нет

- RF&MW M 1Документ2 страницыRF&MW M 1shankarОценок пока нет

- Ada Syllabus 2013Документ1 страницаAda Syllabus 2013shankarОценок пока нет

- HTTPДокумент2 страницыHTTPshankarОценок пока нет

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Ada Syllabus 2013Документ1 страницаAda Syllabus 2013shankarОценок пока нет

- Unit 1 Ada 2014Документ22 страницыUnit 1 Ada 2014shankarОценок пока нет

- Ec6802 Wireless NetworksДокумент1 страницаEc6802 Wireless NetworksBritto Ebrington AjayОценок пока нет

- Unit 1 Adsd KncetДокумент46 страницUnit 1 Adsd KncetshankarОценок пока нет

- MultiplierДокумент16 страницMultipliershankarОценок пока нет

- AP9212Документ7 страницAP9212shankarОценок пока нет

- Mercantile - 13 05 2021Документ1 страницаMercantile - 13 05 2021AlexMason100% (1)

- Suprascan QuarzДокумент6 страницSuprascan QuarzSpataruIonОценок пока нет

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- Lecture 6 BigDataДокумент61 страницаLecture 6 BigDataحذيفة فلاحОценок пока нет

- X Sim 2 IntroductionДокумент7 страницX Sim 2 IntroductionDaniel DaniОценок пока нет

- Supply Chain Management For enДокумент14 страницSupply Chain Management For enMario EnriqueОценок пока нет

- Introduction To Cool Edit Pro PDFДокумент2 страницыIntroduction To Cool Edit Pro PDFcristo colmard0% (1)

- The Bootcampers Guide To Web AccessibilityДокумент137 страницThe Bootcampers Guide To Web AccessibilityNguyen Duy HaiОценок пока нет

- The Test On C: PR Attribute ID Marks New Marks C - 2 3 2.5Документ11 страницThe Test On C: PR Attribute ID Marks New Marks C - 2 3 2.5michaelcoОценок пока нет

- Preparing a Highway ModelДокумент4 страницыPreparing a Highway Modelrinlu patilОценок пока нет

- Conceptual Framework-ThesisДокумент3 страницыConceptual Framework-ThesisKristyl PereyeОценок пока нет

- Ip ProjectДокумент41 страницаIp ProjectLIGHT YAGAMIОценок пока нет

- Et200sp Im 155 6 PN ST Manual en-US en-USДокумент50 страницEt200sp Im 155 6 PN ST Manual en-US en-USOmar AbdussaidОценок пока нет

- Computer Studies Form 1 2 3 4 Schemes of Work CombinedДокумент60 страницComputer Studies Form 1 2 3 4 Schemes of Work Combineddesmond mugambi85% (13)

- Merge Dupa Cu Ptype Sa Iti Selectezi PuncteleДокумент4 страницыMerge Dupa Cu Ptype Sa Iti Selectezi PuncteleAndrei LeașuОценок пока нет

- Asus P5B Soporte CPUДокумент12 страницAsus P5B Soporte CPUInfonova RuteОценок пока нет

- E7756v1 3 PDFДокумент82 страницыE7756v1 3 PDFxmieОценок пока нет

- 9590-4002 v5 Wired Control Installation Owners-2Документ32 страницы9590-4002 v5 Wired Control Installation Owners-2Phương LanОценок пока нет

- Microprocessors and Microsystems: Prateek Sikka, Abhijit R. Asati, Chandra ShekharДокумент6 страницMicroprocessors and Microsystems: Prateek Sikka, Abhijit R. Asati, Chandra ShekharBhargav BhatОценок пока нет

- Bulk Carrier Safety ABS RulesДокумент3 страницыBulk Carrier Safety ABS RulesHUNG LE THANHОценок пока нет

- 200-338 - 0.2 Money Controls CcTalk User ManualДокумент226 страниц200-338 - 0.2 Money Controls CcTalk User ManualRonald M. Diaz0% (2)

- Computer Application 1 Practical July 2017 1Документ8 страницComputer Application 1 Practical July 2017 1Samson Oteba100% (1)

- Latest Algorithm Design Using PseudocodeДокумент28 страницLatest Algorithm Design Using PseudocodeArham TamimОценок пока нет

- Bailey DefendingSpacecraft 11052019Документ18 страницBailey DefendingSpacecraft 11052019Ahmed ElОценок пока нет

- Profibus Master - Modbus Plus Slave: 512 Bytes (Max 64 Bytes As Modbus Plus Global Data) Ytes, MaxДокумент1 страницаProfibus Master - Modbus Plus Slave: 512 Bytes (Max 64 Bytes As Modbus Plus Global Data) Ytes, MaxBob YahyaОценок пока нет

- 18VLFCZ1 Research Methodology and IprДокумент2 страницы18VLFCZ1 Research Methodology and Iprkruthikah ap100% (1)

- Umfluxus Wdv2-1enДокумент193 страницыUmfluxus Wdv2-1engelealdo souza ferreiraОценок пока нет

- PHD Thesis Commerce PDFДокумент7 страницPHD Thesis Commerce PDFufagmcgld100% (1)

- Pico Bricks Ebook 15Документ234 страницыPico Bricks Ebook 15PifОценок пока нет

- CS 563-DeepLearning-SentimentApplication-April2022 (27403)Документ124 страницыCS 563-DeepLearning-SentimentApplication-April2022 (27403)Varaprasad DОценок пока нет

- A Novel Blockchain-Based Education Records Verification Solution PDFДокумент6 страницA Novel Blockchain-Based Education Records Verification Solution PDFjrobleslunaОценок пока нет