Академический Документы

Профессиональный Документы

Культура Документы

Capacitor Less Ldo

Загружено:

antharmuki0 оценок0% нашли этот документ полезным (0 голосов)

104 просмотров11 страницCapacitor less LDO by Rohini

Оригинальное название

CAPACITOR LESS LDO

Авторское право

© © All Rights Reserved

Доступные форматы

DOCX, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документCapacitor less LDO by Rohini

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате DOCX, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

104 просмотров11 страницCapacitor Less Ldo

Загружено:

antharmukiCapacitor less LDO by Rohini

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате DOCX, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 11

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 1

CHAPTER 1

INTRODUCTION

The demand for low-voltage, low drop-out (LDO) regulators are increasing because of

the growing demand for portable electronics, i.e., cellular phones, pagers, laptops, etc. LDOs are

used coherently with dc-dc converters as well as standalone parts. In power supply systems, they

are typically cascaded onto switching regulators to suppress noise and provide a low noise

output. The need for low voltage is innate to portable low power devices and corroborated by

lower breakdown voltages resulting from reductions in feature size. Low quiescent current in a

battery-operated system is an intrinsic performance parameter because it partially determines

battery life.

The low drop-out nature of the regulator makes it appropriate for use in many

applications, namely, automotive, portable, industrial, and medical applications. The automotive

industry requires low drop-out (LDO) regulators to power up digital circuits, especially during

cold-crank conditions where the battery voltage can be below 6 V. The increasing demand,

however, is especially apparent in mobile battery operated products, such as cellular phones,

pagers, camera recorders, and laptops. In a cellular phone, for instance, switching regulators are

used to boost up the voltage but LDOs are cascaded in series to suppress the inherent noise

associated with switchers. LDOs benefit from working with low input voltages because power

consumption is minimized accordingly, P = I

load *

V

in

.

Low voltage and low quiescent current are intrinsic circuit characteristics for increased

battery efficiency and longevity. Low voltage operation is also a consequence of process

technology. This is because isolation barriers decrease as the component densities per unit area

increase, thereby exhibiting lower breakdown voltages.Therefore, low power and finer

lithography require regulators to operate at low voltages, produce precise output voltages, and

have characteristically lower quiescent current flow. By the year 2004, the power supply voltage

is expected to be as low as 0.9 V in 0.14m technologies. Drop-out voltages also need to be

minimized to maximize dynamic range within a given power supply voltage. This is because the

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 2

signal-to-noise ratio typically decreases as the power supply voltages decrease while noise

remains constant. Lastly, financial considerations also require that these circuits be realized in

relatively simple processes.

Industry is pushing towards complete System-on-Chip (SOC) design solutions that

include power management. The study of power management techniques has increased

spectacularly within the last few years corresponding to a vast increase in the use of portable,

handheld battery operated devices. Power management seeks to improve the devices power

efficiency resulting in prolonged battery life and operating time for the device. A power

management system contains several subsystems including linear regulators, switching

regulators, and control logic. The control logic changes the attributes of each subsystem; turning

the outputs on and off as well as changing the output voltage levels, to optimize the power

consumption of the device.

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 3

CHAPTER 2

CONVENTIONAL LDO

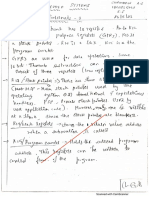

The conventional LDO voltage regulator, for stability requirements, requires a relatively

large output capacitor in the microfarad range. Large microfarad capacitors cannot be realized in

current design technologies, thus each LDO regulator needs an external pin for a board mounted

output capacitor. To overcome this issue, a capacitor less LDO has been proposed in that

topology is, however, unstable at low currents making it unattractive for real applications

(figure.1). Removing the large off-chip output capacitor also reduces the board real estate and the

overall cost of the design and makes it suitable for SoC designs.

Fig 1 Conventional LDO voltage regulator.

Most of the conventional LDO performances are greatly affected when the external

capacitor is reduced by several orders of magnitude. The absence of a large external output

capacitor presents several design challenges both for ac stability and load transient response.

Conventional LDO regulators use a large external capacitor to create the dominant pole and to

provide an instantaneous charge source during fast load transients. Thus, a capacitor-less LDO

requires an internal fast transient path to compensate for the absence of the large external

capacitor. To realize the task at hand, the basic capacitor-less LDO regulator, is revisited in the

following section. One of the most significant side effects in LDOs is stability degradation due to

the several poles embedded in the loop. As shown in Fig. 2(a), the uncompensated capacitor-less

LDO has two major poles: the error amplifier output pole and the load dependent output pole.

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 4

Moreover, the power pMOS transistor in classical LDO must operate in saturation region due to

the stability problem at different input voltages. The change in voltage gain due to different

drainsource voltage is not substantial when the transistor operates in saturation region.

However, if the transistor operates in linear region at dropout, the transistor will operate in

saturation region instead as the input voltage increases. As mentioned previously, when the loop

gain increases, the classical LDO based on dominant-pole compensation may be unstable.

Therefore, the power pMOS transistor needs to operate in saturation region throughout the entire

range of input voltage, so a large transistor size is required to provide a small saturation voltage

at the maximum output current.

Fig 2. (a) Equivalent circuit of LDO voltage regulator and

(b) Pole locations for uncompensated capacitor-less LDO voltage regulator; Cout around 100pF.

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 5

The specifications of the LDO can be classified into three classes: 1) static-state

specification; 2) dynamic-state specification; and 3) high-frequency specification. Line and load

regulations, as well as temperature coefficient, are regarded as static-state specifications, while

line and load transient responses, as well as ripple rejection ratio, are dynamic-state

specifications. The high-frequency specifications are PSRR and output noise. All specifications

are correlated, and they have tradeoffs with the LDO stability when dominant-pole compensation

with pole-zero cancellation is used. Line and load regulations are two important specifications

that relate to the output-voltage accuracy. PSRR depends highly on both loop-gain bandwidth

and ESR. An LDO with a good PSRR and line transient response results in a good ripple

rejection ratio.

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 6

CHAPTER 3

PROBLEM STATEMENT

Output current and input voltage range directly affect the characteristics of the pass

element in the regulator, which defines the current requirements of the error amplifier. As the

maximum load-current specification increases, the size of the pass device necessarily increases.

Consequently, the amplifiers load capacitance, in Fig. 1, increases. This affects the circuits

frequency performance by reducing the value of the parasitic pole present at the output of the

amplifier. Therefore, phase-margin degrades and stability may be compromised unless the output

impedance of the amplifier is reduced accordingly. As a result, more current in the buffer stage

of the amplifier is required, be it a voltage follower or more complicated circuit architecture. In a

similar manner, low input voltages require that MOS pass device structures increase in size and

thus yield the same negative effects on frequency response and quiescent current as just

described. This is because the gate drive decreases as the input voltages decrease, thereby

demanding larger MOS pass elements to drive high output currents.

Further limits to low quiescent current arise from the transient requirements of the

regulator, namely, the permissible output voltage variation in response to a maximum load

current step swing. The output voltage variation is determined by the response time of the circuit,

the specified load-current, and the output capacitor [3]. The worst case response time

corresponds to the maximum output voltage variation. This time limitation is determined by the

closed-loop bandwidth of the system and the output slew-rate current of the error amplifier [9].

These characteristic requirements become more difficult to realize as the size of the parasitic

capacitor at the output of the amplifier increases, which results from low-voltage operation

and/or increased output current specifications. Consequently, the quiescent current of the

amplifiers gain stage is limited by a bandwidth minimum while the quiescent current of the

amplifiers buffer stage is limited by the slew-rate current required to drive.

The classical LDO using dominant- pole compensation, a high loop gain and a wide loop

bandwidth are critical for the improvement of LDO performance, but static power consumption

and stability are tradeoffs. It is further illustrated that classical LDOs cannot be applied

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 7

effectively to system-on-chip designs due to the required large output capacitor for stability.

Therefore, an advanced LDO structure with advanced frequency compensation, which solves the

tradeoff problems of classical LDOs, should be implemented.

For stability requirements, LDO requires a relatively large output capacitor in the

microfarad range. Large microfarad capacitors cannot be realized in current design technologies,

thus each LDO regulator needs an external pin for a board mounted output capacitor. To

overcome this issue, a capacitor less LDO has been proposed in that topology is, however,

unstable at low currents making it unattractive for real applications. Removing the large off-chip

output capacitor also reduces the board real estate and the overall cost of the design and makes it

suitable for SoC designs.

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 8

CHAPTER 4

LITERATURE SURVEY

Due to the emerging need of high-performance low-voltage LDOs for low-voltage

mixed-signal systems, many researchers have recently proposed many advanced methods to

improve the performance of LDOs. Rincon-Mora et al. proposed current-efficient voltage buffer,

forward-biased power transistor, pole-zero doublets for load-regulation enhancement, and

capacitance multiplication [3]. Heisley et al. proposed using a DMOS power transistor.

Chevalerias et al. proposed using an nMOS power transistor with charge-pumped gate drive. The

main aims of all the proposed methods are: 1) to enable low voltage regulation; 2) to reduce

slew-rate limit at the gate drive; and 3) to improve load regulation and transient response.

However, the precision of the above reveals the fact that there are limitations on the structure and

frequency compensation scheme of classical.

The off-chip capacitor, which is the key for stability and high LDO performance, cannot

be eliminated. This off-chip capacitor is the main obstacle to fully integrating LDOs in system-

on-chip designs. As a result, low-voltage high-stability and fast-transient LDOs with, preferably,

capacitor-free operation should be developed. Solving the correlated tradeoffs on stability,

precision, and recovery speed is the main challenge of capacitor-free LDO design [5]. A CMOS

LDO that is targeted for CMOS system-on-chip designs is presented in [1]. The circuit

architecture is based on Capacitor-Less Low-Dropout Voltage Regulator a three-stage amplifier

design [7], and it provides a capacitor-free feature to eliminate the need of bulky off-chip

capacitor. Both fast load transient response and high power-supply rejection ratio (PSRR) are

achieved due to the fast and stable loop gain provided by the proposed LDO Structure and

damping-factor-control (DFC) compensation Scheme. The power pMOS transistor in the

proposed LDO operates in linear region at dropout, and hence, the required transistor size can be

reduced significantly for the ease of integration and cost reduction. In addition, a novel CMOS

voltage reference based on weighted difference of gatesource voltages enables full-CMOS

implementation. LDO regulators are an essential part of the power management system that

provides constant voltage supply rails. They fall into a class of linear voltage regulators with

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 9

improved power efficiency, [1]. Efficiency is improved over conventional linear regulators by

replacing the common-drain pass element with a common-source pass element to reduce the

minimum required voltage drop across the control device. Smaller voltage headroom in the pass

element results in less power dissipation, making LDO regulators more suitable for low-voltage,

on-chip, power management solutions.

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 10

CHAPTER 5

EXPECTED OUTPUT

The targeted LDO has to be implemented using Bandgap reference voltage and Miller

capacitance concept, using LTspice-IV tool for simulation in 130 nm CMOS technology. This

LDO is expected to have good performance on PSRR at high frequencies. Mainly, expected to

reduce the dropout voltage to 300mV from 750mV.

TARGETED SPECIFICATION

Gain Bandwidth ~ 1 MHz

Settling Time < 5 s

Loop Gain ~ 70 dB

GND Current < 150 A

Dropout Voltage 300 mV

Output Current 0 ~ 50 mA

PSRR < 40dB @ 100kHz

Output Noise < 20 V

Line Regulation <= 0.01%

Load Regulation <= 0.02%

Design And Implementation Of Low Dropout Voltage Regulator With On Chip Capacitor

VLSI DESIGN AND EMBEDDED SYSTEMS, SCE Page 11

REFERENCES

1. Sriranganatha Sagar. K. N, Poornima. N and Vijaya Kumar. V, Capacitor-Less Low-

Dropout Voltage Regulator, IEEE J. Solid-State Circuits, pp.25-30, Jan. 2010.

2. G. A. Rincon-Mora and P. E. Allen, A low-voltage, low quiescent current, low drop-out

regulator, IEEE J. Solid-State Circuits, vol. 33, pp.3644, Jan. 1998.

3. G. A. Rincon-Mora, Active multiplier in Miller-compensated circuits, IEEE J. Solid-

State Circuits, vol. 35, pp. 2632, Jan. 2000.

4. Texas Instruments, "Fundamental theory of PMOS low dropout voltage regulators,"

Application Report, Analog and Mixed Signal Products, SL VA068,pp. 1-5,Apr. 1999.

5. K. N. Leung, P. K. T. Mok. A capacitor-free CMOS low-dropout regulator with

damping-factor-control frequency, IEEE J. Solid-State Circuits, vol. 37, pp. 1691-1701,

Oct. 2003.

6. K. N. Leung, P. K. T. Mok, W. H. Ki, and J. K. O. Sin, Three-stage large capacitive load

amplifier with damping-factor-control frequency compensation, IEEE J. Solid-State

Circuits, vol. 35, pp. 221230, Feb.2000.

7. Robert J Milliken Full on-chip CMOS low-dropout voltage regulator, IEEE

transactions on circuits and systems: regular papers, vol. 54, no. 9, September 2007.

8. O. Chevalerias, F. Rodes, K. Salmi, and C. Scarabello, 4-V 5-mA low drop-out

regulator using series-pass N-channel MOSFET, Electron Lett, Vol.35, pp.1214-1215,

July1999.

9. Allen Hustings "The art of analog layout" Prentice hall, 2001.

10. Phillip E. Allen, Douglas R Holberg, CMOS Analog Circuit Design, Oxford University

Press, 2002.

Вам также может понравиться

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- A Low-Voltage, Low Quiescent Current, Low Drop-Out RegulatorДокумент9 страницA Low-Voltage, Low Quiescent Current, Low Drop-Out RegulatorVinayОценок пока нет

- Full On-Chip CMOS Low-Dropout Voltage RegulatorДокумент12 страницFull On-Chip CMOS Low-Dropout Voltage RegulatorashishmanyanОценок пока нет

- Design and Analysis of Low Voltage Low Dropout RegulatorДокумент4 страницыDesign and Analysis of Low Voltage Low Dropout RegulatorIJSTEОценок пока нет

- Design of Cmos Low Drop-Out Regulators: A Comparative Study: Ashvani Kumar Mishra, Rishikesh PandeyДокумент7 страницDesign of Cmos Low Drop-Out Regulators: A Comparative Study: Ashvani Kumar Mishra, Rishikesh PandeyrahmanakberОценок пока нет

- Investigating Buck Converter With Hybrid LDO Mode For Improved Low-Load OperationДокумент4 страницыInvestigating Buck Converter With Hybrid LDO Mode For Improved Low-Load OperationInternational Journal of Innovative Science and Research TechnologyОценок пока нет

- Capless LDO DESIGNДокумент6 страницCapless LDO DESIGNbhasin_hemantОценок пока нет

- A Capacitor-Free CMOS Low-Dropout Regulator With Damping-Factor-Control Frequency CompensationДокумент12 страницA Capacitor-Free CMOS Low-Dropout Regulator With Damping-Factor-Control Frequency Compensationtotoya38Оценок пока нет

- Ultra Low Power Low Dropout Voltage RegulatorДокумент10 страницUltra Low Power Low Dropout Voltage Regulatormikeshinoda2011Оценок пока нет

- Design Analysis of Low Drop-Out Voltage Regulator With Current Buffer CompensationДокумент5 страницDesign Analysis of Low Drop-Out Voltage Regulator With Current Buffer Compensationkhang npОценок пока нет

- Ultra-Low Quiescent Current CMOS LDO with Small Output VariationsДокумент6 страницUltra-Low Quiescent Current CMOS LDO with Small Output VariationsMehanathan Maggie MikeyОценок пока нет

- Eekol 2008dec12 Opt Pow NT 88Документ4 страницыEekol 2008dec12 Opt Pow NT 88Atoui IssamОценок пока нет

- LDO Voltage Regulator by Sanjay Singh NIT KKRДокумент9 страницLDO Voltage Regulator by Sanjay Singh NIT KKRSanjay SinghОценок пока нет

- Analog IC Design With Low-Dropout RegulatorsДокумент374 страницыAnalog IC Design With Low-Dropout Regulatorsberbou100% (2)

- Amplificator Clasa DДокумент4 страницыAmplificator Clasa DelmannОценок пока нет

- Capacitor Less Ldo ThesisДокумент4 страницыCapacitor Less Ldo Thesisevelyndonaldsonbridgeport100% (2)

- Design of ALU Circuits Using Pass Transistor LogicДокумент71 страницаDesign of ALU Circuits Using Pass Transistor LogicVivek GuntumuduguОценок пока нет

- 1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002Документ16 страниц1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002jaigodaraОценок пока нет

- Background of The Study 2. Statement of The Problem 3. Objectives 4. Significance 5. Scope and Limitations 6. Definition of Terms 7. Theoretical Framework RRLДокумент15 страницBackground of The Study 2. Statement of The Problem 3. Objectives 4. Significance 5. Scope and Limitations 6. Definition of Terms 7. Theoretical Framework RRLJoshua KoppinОценок пока нет

- Capless Ldo ThesisДокумент7 страницCapless Ldo Thesisgjaj8vvw100% (1)

- WP HighPerfomanceZVSДокумент10 страницWP HighPerfomanceZVSAdrian TanaseОценок пока нет

- 12-Basic Knowledge of LDO Voltage Regulator enДокумент19 страниц12-Basic Knowledge of LDO Voltage Regulator enKirti Susan VargheseОценок пока нет

- Analog Switches and Multiplexers BasicsДокумент23 страницыAnalog Switches and Multiplexers BasicsOfir CzОценок пока нет

- AN665Документ6 страницAN665VIJAYPUTRAОценок пока нет

- Low Dropout Voltage Regulator Using 130 NM CMOS TechnologyДокумент4 страницыLow Dropout Voltage Regulator Using 130 NM CMOS Technologykhang npОценок пока нет

- Lec14 DTMOSДокумент88 страницLec14 DTMOSSalim SanОценок пока нет

- Gabriel Rincon-Mora-Analog IC Design With Low-Dropout Regulators (LDOs) (Electronic Engineering) (2009) PDFДокумент373 страницыGabriel Rincon-Mora-Analog IC Design With Low-Dropout Regulators (LDOs) (Electronic Engineering) (2009) PDFNguyen HaОценок пока нет

- A Fold-Back Current Limit Circuit With Load-Insensitive Quiescent Current For CMOS Low Dropout RegulatorДокумент4 страницыA Fold-Back Current Limit Circuit With Load-Insensitive Quiescent Current For CMOS Low Dropout Regulatorhjtseng1974Оценок пока нет

- Paper Modulacion PWM With AN-42026Документ16 страницPaper Modulacion PWM With AN-42026DuckTronixОценок пока нет

- An203 - c8051fxxx Printed Circuit Board Design Notes - Silicon - LabsДокумент22 страницыAn203 - c8051fxxx Printed Circuit Board Design Notes - Silicon - LabsEdson PaivaОценок пока нет

- Selecting The Correct IC For Power-Supply Applications: by William HaddenДокумент5 страницSelecting The Correct IC For Power-Supply Applications: by William HaddenLuis AlarconОценок пока нет

- A New Concept of Power Quality Monitoring: AbstractДокумент6 страницA New Concept of Power Quality Monitoring: AbstractlokvisОценок пока нет

- 3-Phase Power Factor Correction, Using Vienna Rectifier ApproachДокумент13 страниц3-Phase Power Factor Correction, Using Vienna Rectifier Approachvdiaz1Оценок пока нет

- Design of A Low-Dropout Linear RegulatorДокумент4 страницыDesign of A Low-Dropout Linear RegulatorParindraОценок пока нет

- Energy-Efficient Low Dropout Regulator With Switching Mechanism and Course Regulator For Internet of Things (Iot) DevicesДокумент11 страницEnergy-Efficient Low Dropout Regulator With Switching Mechanism and Course Regulator For Internet of Things (Iot) DevicesijesajournalОценок пока нет

- 1000w Inverter PURE SINE WAVE Schematic DiagramДокумент153 страницы1000w Inverter PURE SINE WAVE Schematic Diagramjeevapillay100% (4)

- Switched Mode Power SupplyДокумент153 страницыSwitched Mode Power SupplyIvan222244Оценок пока нет

- Chapter 1-3Документ6 страницChapter 1-3Joshua KoppinОценок пока нет

- AN491 - Power Supply Rejection For Low-Jitter ClocksДокумент8 страницAN491 - Power Supply Rejection For Low-Jitter ClocksJohanes SetiawanОценок пока нет

- Low Power Battery DesignДокумент8 страницLow Power Battery DesignAmmulu KondaОценок пока нет

- AN764 Debounce SwitchДокумент15 страницAN764 Debounce Switchd.c.delatorre2200Оценок пока нет

- Basic Switching-Regulator-Layout Techniques: GroundДокумент8 страницBasic Switching-Regulator-Layout Techniques: GroundJonathan JaegerОценок пока нет

- High Efficiency DC-DC Boost Converter Design For LED DrivesДокумент10 страницHigh Efficiency DC-DC Boost Converter Design For LED DriveskowsalyaОценок пока нет

- An-978 HV Floating MOS Gate DriversДокумент21 страницаAn-978 HV Floating MOS Gate DriversPeter RueОценок пока нет

- Design of A Low Voltage Low Drop Out LDO Voltage Cmos RegulatorДокумент6 страницDesign of A Low Voltage Low Drop Out LDO Voltage Cmos Regulatorsantosh kumar gangalaОценок пока нет

- How To Predict Stability in Linear RegulatorsДокумент7 страницHow To Predict Stability in Linear RegulatorssureshchattuОценок пока нет

- An Introduction to Switched Mode Power Supply TopologiesДокумент21 страницаAn Introduction to Switched Mode Power Supply Topologiesseahate100% (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsОт EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsРейтинг: 3.5 из 5 звезд3.5/5 (6)

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsОт EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsРейтинг: 3 из 5 звезд3/5 (2)

- High-Performance D/A-Converters: Application to Digital TransceiversОт EverandHigh-Performance D/A-Converters: Application to Digital TransceiversОценок пока нет

- Analog Circuit Design Volume Three: Design Note CollectionОт EverandAnalog Circuit Design Volume Three: Design Note CollectionРейтинг: 3 из 5 звезд3/5 (2)

- Radio Frequency Transistors: Principles and Practical ApplicationsОт EverandRadio Frequency Transistors: Principles and Practical ApplicationsРейтинг: 4 из 5 звезд4/5 (2)

- Power Systems-On-Chip: Practical Aspects of DesignОт EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardОценок пока нет

- STEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10От EverandSTEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10Оценок пока нет

- European Journal of Operational Research: Antoine Sauré, Mehmet A. Begen, Jonathan PatrickДокумент12 страницEuropean Journal of Operational Research: Antoine Sauré, Mehmet A. Begen, Jonathan PatrickantharmukiОценок пока нет

- 3rd WeekДокумент2 страницы3rd WeekantharmukiОценок пока нет

- B.N.M. Institute of Technology: Department: Electronics and Communication EngineeringДокумент1 страницаB.N.M. Institute of Technology: Department: Electronics and Communication EngineeringantharmukiОценок пока нет

- Scan Jun 10, 2021Документ2 страницыScan Jun 10, 2021antharmukiОценок пока нет

- Warm Greetings EveryoneДокумент1 страницаWarm Greetings EveryoneantharmukiОценок пока нет

- Ia1 Es Chandan A SДокумент11 страницIa1 Es Chandan A SantharmukiОценок пока нет

- Warm Greetings EveryoneДокумент1 страницаWarm Greetings EveryoneantharmukiОценок пока нет

- Grocery Management and Distribution System: Project Work (17ECP78)Документ26 страницGrocery Management and Distribution System: Project Work (17ECP78)antharmukiОценок пока нет

- Jan 2017Документ3 страницыJan 2017antharmukiОценок пока нет

- July 2017Документ2 страницыJuly 2017antharmukiОценок пока нет

- NCC Basic ScienceДокумент10 страницNCC Basic ScienceantharmukiОценок пока нет

- Jan 2018Документ3 страницыJan 2018antharmukiОценок пока нет

- Ecsyll6 PDFДокумент22 страницыEcsyll6 PDFantharmukiОценок пока нет

- LDДокумент26 страницLDantharmukiОценок пока нет

- Alto Ms8ma Ms10ma Ms12maДокумент48 страницAlto Ms8ma Ms10ma Ms12mavictor mogajaneОценок пока нет

- PD Smart PDFДокумент2 страницыPD Smart PDFAriel Leandro Toro MuñozОценок пока нет

- EL 209 Lab-Manual CompleteДокумент113 страницEL 209 Lab-Manual CompleteMistr Irfan KhanОценок пока нет

- Bulb AssignmentДокумент2 страницыBulb AssignmentJamie McGregorОценок пока нет

- Principles of Lighting in A BuildingДокумент21 страницаPrinciples of Lighting in A BuildingGaffur BoliyaОценок пока нет

- Chapter 8 State Space AnalysisДокумент22 страницыChapter 8 State Space AnalysisAli AhmadОценок пока нет

- Chapter 1 Homework SolutionДокумент7 страницChapter 1 Homework SolutionPao JJОценок пока нет

- DataSheet SRM50-HFA0-K21 1037071 enДокумент6 страницDataSheet SRM50-HFA0-K21 1037071 entrinoОценок пока нет

- DatasheetДокумент56 страницDatasheetrajkumarmalathiОценок пока нет

- Gps Final Year ProjectДокумент52 страницыGps Final Year ProjectPramod Niraula100% (1)

- OpAmp - LF451 PDFДокумент8 страницOpAmp - LF451 PDFLodewyk KleynhansОценок пока нет

- Teradyne Hastings Vacuum Gage BrochrureДокумент2 страницыTeradyne Hastings Vacuum Gage Brochrurekp83Оценок пока нет

- Control of Harmonics in 6-Pulse Rectifiers ThesisДокумент116 страницControl of Harmonics in 6-Pulse Rectifiers ThesisAlfredo Lopez CordovaОценок пока нет

- Altec Lansing ADA105Документ7 страницAltec Lansing ADA105Ciara Mae Waldron100% (1)

- Op-Amp Cookbook - Part 4: Electronic Rectifier CircuitsДокумент18 страницOp-Amp Cookbook - Part 4: Electronic Rectifier Circuitsamit281276Оценок пока нет

- AC ScrollДокумент12 страницAC ScrollKamalMuralikumarОценок пока нет

- Teaching Electrodynamic Levitation Theory: (3) - Teaching at University Level RequiresДокумент9 страницTeaching Electrodynamic Levitation Theory: (3) - Teaching at University Level RequiresArda YıldızОценок пока нет

- Clean, low-cost electro-hydraulic actuator guideДокумент5 страницClean, low-cost electro-hydraulic actuator guidevitortelesОценок пока нет

- CapacitorsДокумент10 страницCapacitorsrsrtnj100% (1)

- CQI Feedback ModesДокумент6 страницCQI Feedback ModesravitejagowdaОценок пока нет

- FYP Project 2jkmkДокумент24 страницыFYP Project 2jkmkMarjanОценок пока нет

- SkyAir R410A Inv Cooling EDVN281407 PDFДокумент532 страницыSkyAir R410A Inv Cooling EDVN281407 PDFThinh Nguyen100% (2)

- Safemine Cas 2011Документ56 страницSafemine Cas 2011DEEPAK GOYALОценок пока нет

- 5 Pen PC Technology PDFДокумент8 страниц5 Pen PC Technology PDFNikitha ReddyОценок пока нет

- Pop Bot Lite - Manual PDFДокумент100 страницPop Bot Lite - Manual PDFMinarto AsmaratmoОценок пока нет

- Benefits of Preventive Maintenance PDFДокумент19 страницBenefits of Preventive Maintenance PDFGlendonОценок пока нет

- Presentation On DC MicrogridДокумент9 страницPresentation On DC MicrogridRamesh NaiduОценок пока нет

- f2 Paper 2 Physics Term 3 PractiseДокумент35 страницf2 Paper 2 Physics Term 3 PractiseShepherd W NgwenyaОценок пока нет

- Question Bank Me2401Документ13 страницQuestion Bank Me2401Anonymous p8bHAAxОценок пока нет

- EnergoGlobal EG 22 PДокумент4 страницыEnergoGlobal EG 22 PnebjakОценок пока нет