Академический Документы

Профессиональный Документы

Культура Документы

Nanoelectronics Assignment

Загружено:

Shardul Gaikwad0 оценок0% нашли этот документ полезным (0 голосов)

28 просмотров4 страницыne asg

Авторское право

© © All Rights Reserved

Доступные форматы

DOCX, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документne asg

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате DOCX, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

28 просмотров4 страницыNanoelectronics Assignment

Загружено:

Shardul Gaikwadne asg

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате DOCX, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 4

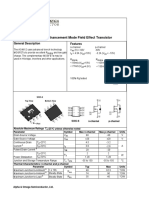

RTBT MUX

The figure above shows a 2:1 multiplexer using RTBT.

The figure above shows a 2:1 mux using logic gates. The working of both of them is exactly the same.

Working

The logic gate above represents the second box represents the first AND gate which has the inverter at

the selection input. The clock is the equivalent of the selection line. When the clock is high, the RTBT 2 is

turned on and the input from a is selected. The clock compliment is low and so the RTBT4 is turned off

and the final output from the second box is 0 and final output from the first box is a. These outputs

are sent to the third circuit which is the OR gate built using RTD and HBT. Since the input at HBT2 is a

and input at HBT1 is 0, the HBT1 is turned off and HBT2 is turned on, thus finally, the final output at

out is a.

When the clock is low, the RTBT2 is turned off and the input from b is selected. The clock is low and

hence the clock compliment is high and the RTBT4 is turned on. The final output form the first box is 0

and from the second box is b. These outputs are sent to the third circuit which is the OR gate built

using RTD and HBT. Since the input at HBT1 is b and input and HBT2 is 0, the HBT2 is turned off and

HBT1 is turned on, thus finally, the final output at out is b.

MOBILE D-Flip flop operation

The above diagram shows a D-flip flop built from MOBILE. MOBILE stands for Monostable BIstable Logic

Element. MOBILE is developed by connecting an RTD with a MODFET in parallel. This structure allows us

to make compact circuits with a flexible design that allows separate optimization of MODFET and RTD.

Working

When the clk is low, there is no bias voltage, hence the output is zero.

When the clk is high, there are two cases: Data is 1 or Data is 0.

Data 1:

When Data is 1, the the MOBILE 1 is switched ON because the clock is high and GATE voltage is 1 and

MOBILE 2 is connected to the ground so the output at MOBILE 2 is 0. Now both these outputs are sent

to the SR flip flop latch. Due to MOBILE 1, the above RTD is turned off. Output of MOBILE2 turns on the

RTD at the bottom. This in total resets the flipflop and and the output at the end of the flipflop is 0, and

the last second FET is turned off as the GATE voltage is 0. Due to this FET being turned off the final FET is

also off, and so the final output is 1 as it is connected to Vdd.

Data 2:

When Data is 0, the the MOBILE 1 is switched OFF because the clock is high but the GATE voltage is 0,

and MOBILE 2 is ON because the GATE voltage is 0, so it is not connected to the ground, hence the

output at MOBILE 2 is 1. Now both these outputs are sent to the SR flip flop latch. Due to MOBILE 1, the

above RTD is turned ON. Output of MOBILE2 turns on the RTD at the bottom and it is connected to the

ground there by making it 0. This in total sets the flipflop and and the output at the end of the flipflop is

1, and the last second FET is turned ON because GATE voltage is applied. Due to this FET being turned

ON the final FET is turned OFF, and so the final output is 0 as it gets connected to the ground.

SRAM cell using RTD

The SRAM cell designed using RTD is in the latch configuration created by two stable voltage levels at

the storage node. The cell sensing capacitance is provided by the RTDs. The latch maintains two stable

low node voltage levels as long as the RTD peak-value current is larger than the cell leakage current.

Operation:

During read operation, the storage node shares charge with the bit line and a clock latching amplifier

which is used to sense this charge and restore data into the cell. When the word line is low that is cell is

not selected, the read output the storage node latches to one of the two stable voltage levels depending

on the previous return bit line level on very short time scales. RTDs action is negligible and the storage

node capacitance dynamically holds the voltage.

For example at bias of 0.45V, two stable voltage levels exist at approximately 0.08 V and 0.36 V.

The characteristics of the SRAM cell depend on the characteristic curves (I-V Curves) of both the RTDs.

The intersection of these curves gives the logic values. V-Lo is the value for LOGIC 0 and V-HI is the value

for logic 1.

Вам также может понравиться

- Viral FormulaДокумент4 страницыViral FormulaShardul GaikwadОценок пока нет

- Notification Phase2Документ2 страницыNotification Phase2Shardul GaikwadОценок пока нет

- Cum Sa Tai Template MicrosimДокумент0 страницCum Sa Tai Template MicrosimrusuclaudiuionutОценок пока нет

- List of FiguresДокумент1 страницаList of FiguresShardul GaikwadОценок пока нет

- DSP Lab ManualДокумент47 страницDSP Lab Manualneelansh88Оценок пока нет

- M74HC595B1 DAta SheetДокумент1 страницаM74HC595B1 DAta SheetShardul GaikwadОценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- 9-165 Data Link Circuit, SAE J1939: General InformationДокумент17 страниц9-165 Data Link Circuit, SAE J1939: General InformationJusto Paniagua ChampaОценок пока нет

- 60V Complementary Enhancement Mode FET FeaturesДокумент9 страниц60V Complementary Enhancement Mode FET FeaturesAhmad MaufiqОценок пока нет

- BD 241Документ4 страницыBD 241MihaiMatacОценок пока нет

- Ducati E900 / Cagiva Elefant Wiring Diagram. Data Source: 1994 - 1995 USA Owners ManualДокумент1 страницаDucati E900 / Cagiva Elefant Wiring Diagram. Data Source: 1994 - 1995 USA Owners ManualPierreОценок пока нет

- Induction Motor Protection Interview Questions Answers - Engineering TutorialДокумент3 страницыInduction Motor Protection Interview Questions Answers - Engineering TutorialPabitra Kumar PatraОценок пока нет

- Joysticks: We Build It So You Can Control ItДокумент5 страницJoysticks: We Build It So You Can Control ItJohnОценок пока нет

- MJ15024G C2730Документ4 страницыMJ15024G C2730naro yamaОценок пока нет

- Sucofeed RF Cables H&SДокумент12 страницSucofeed RF Cables H&SRahul GoudОценок пока нет

- Data Center Design GuidelinesДокумент10 страницData Center Design GuidelinesShankarBevoor100% (1)

- Sk52a L Sk510a L (Do 214ac)Документ4 страницыSk52a L Sk510a L (Do 214ac)Mw KsteОценок пока нет

- MLCF Inventory On-Hand AnalysisДокумент36 страницMLCF Inventory On-Hand AnalysisMuhammad Shoaib Aslam KhichiОценок пока нет

- 311Документ2 страницы311Anonymous cS9UMvhBq100% (2)

- MCB, MCCB, ElcbДокумент3 страницыMCB, MCCB, ElcbMonirul Islam0% (1)

- Crystal Test Oscillators for Determining Unknown FrequenciesДокумент3 страницыCrystal Test Oscillators for Determining Unknown FrequenciesmathurashwaniОценок пока нет

- Study of Variable Frequency Drive Using Pulse Width ModulationДокумент3 страницыStudy of Variable Frequency Drive Using Pulse Width ModulationInternational Journal of Innovative Science and Research TechnologyОценок пока нет

- Yamaha RX V365 Owners ManualДокумент1 страницаYamaha RX V365 Owners ManualandreiОценок пока нет

- Data Sheet: SAK Series KDKS1/35 LD 24VDC 4ZBДокумент7 страницData Sheet: SAK Series KDKS1/35 LD 24VDC 4ZBOLAWALEОценок пока нет

- CDD 3000 HFДокумент100 страницCDD 3000 HFAnders-Pehr GidlundОценок пока нет

- FRIED Model "HДокумент9 страницFRIED Model "HhuulbessemОценок пока нет

- BJT 2Документ14 страницBJT 2Suguna PriyaОценок пока нет

- Ceragon NASPO ValuePoint Pricelist (3!16!16)Документ52 страницыCeragon NASPO ValuePoint Pricelist (3!16!16)Luis SanchezОценок пока нет

- Vergleichsliste Kapazitive SensorenДокумент7 страницVergleichsliste Kapazitive SensorenSerghei BotnaruОценок пока нет

- Protem d404pdf Rele Temperatura de TrafosДокумент16 страницProtem d404pdf Rele Temperatura de TrafosIvan FrancoОценок пока нет

- Mecer ME-1000-WTF Online UPS SeriesДокумент17 страницMecer ME-1000-WTF Online UPS Seriescr33pz1llaОценок пока нет

- Mono Crystalline PERC Silicon Solar PV Modules - 60Документ2 страницыMono Crystalline PERC Silicon Solar PV Modules - 60Ravindra GoyalОценок пока нет

- XG-318 Service Manual PDFДокумент42 страницыXG-318 Service Manual PDFNoe TunОценок пока нет

- BLDC 4Документ7 страницBLDC 4Phạm Ngọc HuyОценок пока нет

- Terasaki Manual Thermal Magnetic TripДокумент3 страницыTerasaki Manual Thermal Magnetic TripTosikur RahmanОценок пока нет

- Tes VCB PG en 031215Документ80 страницTes VCB PG en 031215Anthony BarbachanОценок пока нет