Академический Документы

Профессиональный Документы

Культура Документы

TDA7440D: Tone Control Digitally Controlled Audio Processor

Загружено:

Jimmy R. Calderon GualeИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

TDA7440D: Tone Control Digitally Controlled Audio Processor

Загружено:

Jimmy R. Calderon GualeАвторское право:

Доступные форматы

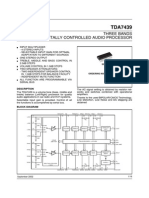

TDA7440D

TONE CONTROL

DIGITALLY CONTROLLED AUDIO PROCESSOR

INPUT MULTIPLEXER

- 4 STEREOINPUTS

- SELECTABLEINPUT GAINFOR OPTIMAL

ADAPTATIONTO DIFFERENT SOURCES

ONE STEREOOUTPUT

TREBLE AND BASS CONTROL IN 2.0dB

STEPS

VOLUMECONTROL IN 1.0dB STEPS

TWOSPEAKERATTENUATORS:

- TWOINDEPENDENTSPEAKERCONTROL

IN 1.0dBSTEPS FOR BALANCEFACILITY

- INDEPENDENT MUTE FUNCTION

ALL FUNCTION ARE PROGRAMMABLE VIA

SERIAL BUS

DESCRIPTION

The TDA7440D is a volume tone (bass and

treble) balance (Left/Right) processor for quality

audio applicationsin Hi-Fi systems.

Selectable input gain is provided. Control of all

the functionsis accomplished by serial bus.

The AC signal setting is obtained by resistor net-

works and switches combined with operational

amplifiers.

Thanks to the used BIPOLAR/CMOSTechnology,

Low Distortion, Low Noise and DC stepping are

obtained

April 1999

0/30dB

2dB STEP

MUXOUTL INL

VOLUME

VOLUME

TREBLE

TREBLE

TREBLE(L)

MUXOUTR INR TREBLE(R)

BOUT(L)

SPKR ATT

LEFT

LOUT

SCL

SDA

DIG_GND

ROUT

D98AU883

I

2

CBUS DECODER + LATCHES

100K

100K

100K

100K

G

L-IN1

L-IN2

L-IN3

L-IN4

100K

100K

100K

100K

R-IN1

R-IN2

R-IN3

R-IN4

G

INPUT MULTIPLEXER

+ GAIN

BASS

BIN(L)

BASS

SPKR ATT

RIGHT

BOUT(R) BIN(R)

SUPPLY

CREF

AGND

V

S

27

4

5

6

7

3

2

1

28

21

22

20

26

24

25

10 11 19 12 13 23

8 9 18 14 15

R

B

R

B

V

REF

BLOCK DIAGRAM

ORDERING NUMBER: TDA7440D

SO28

1/16

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

S

Operating Supply Voltage 10.5 V

T

amb

Operating Ambient Temperature -10 to 85 C

T

stg

Storage Temperature Range -55 to 150 C

THERMAL DATA

Symbol Parameter Value Unit

Rth j-pin Thermal Resistance Junction-pins 85 C/W

L_IN3

L_IN4

MUXOUTL

IN(L)

MUXOUT(R)

BIN(R)

IN(R)

BOUT(R)

BIN(L)

1

3

2

4

5

6

7

8

9

BOUT(L)

N.C.

N.C.

TREBLE(R)

TREBLE(L)

SCL

SDA

DIG-GND

CREF 23

22

21

20

19

17

18

16

15

D98AU884

10

11

12

13

14

28

27

26

25

24

R_IN3

R_IN2

R_IN1

L_IN1

L_IN2 V

S

AGND

ROUT

LOUT

R_IN4

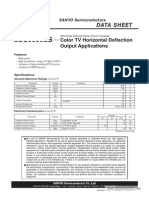

PIN CONNECTION (Top view)

QUICK REFERENCE DATA

Symbol Parameter Min. Typ. Max. Unit

V

S

Supply Voltage 6 9 10.2 V

V

CL

Max. input signal handling 2 Vrms

THD Total Harmonic Distortion V = 1Vrms f = 1KHz 0.01 0.1 %

S/N Signal to Noise Ratio V out = 1Vrms (mode = OFF) 106 dB

S

C

Channel Separation f = 1KHz 90 dB

Input Gain in (2dBstep) 0 30 dB

Volume Control (1dB step) -47 0 dB

Treble Control (2dB step) -14 +14 dB

Bass Control (2dB step) -14 +14 dB

Balance Control 1dB step -79 0 dB

Mute Attenuation 100 dB

TDA7440D

2/16

ELECTRICAL CHARACTERISTICS (refer to the test circuit Tamb = 25C, VS = 9V, RL= 10K,

RG = 600, all controls flat (G = 0dB), unless otherwise specified)

Symbol Parameter Test Condition Min. Typ. Max. Unit

SUPPLY

V

S

Supply Voltage 6 9 10.2 V

I

S

Supply Current 4 7 10 mA

SVR Ripple Rejection 60 90 dB

INPUT STAGE

R

IN

Input Resistance 70 100 130 K

V

CL

Clipping Level THD = 0.3% 2 2.5 Vrms

S

IN

Input Separation The selected input is grounded

through a 2.2 capacitor

80 100 dB

Gi nmin Minimum Input Gain -1 0 1 dB

G

inman

Maximum Input Gain 29 30 31 dB

G

step

Step Resolution 1.5 2 2.5 dB

VOLUMECONTROL

R

i

Input Resistance 20 33 50 K

C

RANGE

Control Range 45 47 49 dB

A

VMAX

Max. Attenuation 45 47 49 dB

A

STEP

Step Resolution 0.5 1 1.5 dB

E

A

Attenuation Set Error A

V

= 0 to -24dB -1.0 0 1.0 dB

A

V

= -24 to -47dB -1.5 0 1.5 dB

E

T

Tracking Error A

V

= 0 to -24dB 0 1 dB

A

V

= -24 to -47dB 0 2 dB

V

DC

DC Step adjacent attenuation steps

from0dB to A

V

max

0

0.5

3 mV

mV

A

mute

Mute Attenuation 80 100 dB

BASS CONTROL (1)

Gb Control Range Max. Boost/cut +12.0 +14.0 +16.0 dB

B

STEP

Step Resolution 1 2 3 dB

R

B

Internal Feedback Resistance 33 44 55 K

TREBLE CONTROL (1)

Gt Control Range Max. Boost/cut +13.0 +14.0 +15.0 dB

T

STEP

Step Resolution 1 2 3 dB

SPEAKERATTENUATORS

C

RANGE

Control Range 70 76 82 dB

S

STEP

Step Resolution 0.5 1 1.5 dB

E

A

Attenuation Set Error A

V

= 0 to -20dB -1.5 0 1.5 dB

A

V

= -20 to -56dB -2 0 2 dB

V

DC

DC Step adjacent attenuation steps 0 3 mV

A

mute

Mute Attenuation 80 100 dB

NOTE1:

1) The device is functionally good at Vs = 5V. a step down, on Vs, to 4V doest reset the device.

2) BASS and TREBLE response: The center frequency and the response quality can be chosen by the external circuitry.

TDA7440D

3/16

ELECTRICAL CHARACTERISTICS (continued.)

Symbol Parameter Test Condition Min. Typ. Max. Unit

AUDIOOUTPUTS

VCLIP Clipping Level d = 0.3% 2.1 2.6 VRMS

R

L

Output Load Resistance 2 K

RO Output Impedance 10 30 50

VDC DC Voltage Level 3.5 3.8 4.1 V

GENERAL

E

NO

Output Noise All gains = 0dB;

BW = 20Hz to 20KHz flat

5 15 V

E

t

Total Tracking Error A

V

= 0 to -24dB 0 1 dB

A

V

= -24 to -47dB 0 2 dB

S/N Signal to Noise Ratio All gains 0dB; VO = 1VRMS ; 95 106 dB

S

C

Channel Separation Left/Right 80 100 dB

d Distortion AV = 0; VI = 1VRMS ; 0.01 0.08 %

BUS INPUT

V

IL

Input Low Voltage 1 V

V

IH

Input High Voltage 3 V

IIN Input Current VIN = 0.4V -5 0 5 A

V

O

Output Voltage SDA

Acknowledge

IO = 1.6mA 0.4 0.8 V

10F 5.6nF

100nF 100nF

5.6K

2.2F

5.6nF

2.2F

100nF 100nF

5.6K

0.47F

0.47F

0.47F

0.47F

0.47F

0.47F

0.47F

0.47F

0/30dB

2dB STEP

MUXOUTL INL

VOLUME

VOLUME

TREBLE

TREBLE

TREBLE(L)

MUXOUTR INR TREBLE(R)

BOUT(L)

SPKR ATT

LEFT

LOUT

SCL

SDA

DIG_GND

ROUT

D98AU885

I

2

CBUS DECODER + LATCHES

100K

100K

100K

100K

G

L-IN1

L-IN2

L-IN3

L-IN4

100K

100K

100K

100K

R-IN1

R-IN2

R-IN3

R-IN4

G

INPUT MULTIPLEXER

+ GAIN

BASS

BIN(L)

BASS

SPKR ATT

RIGHT

BOUT(R) BIN(R)

SUPPLY

CREF

AGND

V

S

27

4

5

6

7

3

2

1

28

21

22

20

26

24

25

10 11 19 12 13 23

8 9 18 14 15

R

B

R

B

V

REF

TEST CIRCUIT

TDA7440D

4/16

APPLICATIONSUGGESTIONS

The first and the last stages are volume control

blocks. The control range is 0 to -47dB (mute) for

the first one, 0 to -79dB (mute) for the last one.

Both of themhave 1dB step resolution.

The very high resolution allows the implementation

of systems freefromany noisy acoustical effect.

The TDA7440D audioprocessor provides 3 bands

tones control.

Bass Stage

Several filter types can be implemented, connect-

ing external components to the Bass IN and OUT

pins.

The fig.1 refers to basic T Type Bandpass Filter

starting from the filter component values (R1 in-

ternal and R2,C1,C2 external) the centre fre-

quency Fc, the gain Av at max. boost and the fil-

ter Q factor are computed as follows:

F

C

=

1

2 R1 R2 C1 C2

A

V

=

R2 C2 + R2 C1 + Ri C1

R2 C1 + R2 C2

Q =

R1 R2 C1 C2

R2 C1 + R2 C2

Viceversa, once Fc, Av, and Ri internal value are

fixed, the external components values will be:

C1 =

A

V

1

2 F

C

R

i

Q

C2 =

Q

2

C1

AV 1 Q

2

R2 =

A

V

1 Q

2

2 C1 F

C

(A

V

1) Q

Treble Stage

The treble stage is a high pass filter whose time

constant is fixed by an internal resistor (25K

typical) and an external capacitor connected be-

tween treble pins and ground

Typical responses are reported in Figg. 10 to 13.

CREF

The suggested 10F reference capacitor (CREF)

value can be reduced to 4.7F if the application

requires faster power ON.

Ri internal

C

2

OUT IN

C

1

R

2

D95AU313

Figure 1.

Figure 2: THD vs. frequency Figure 3: THDvs. RLOAD

TDA7440D

5/16

Figure 4: Channel separationvs. frequency

Figure 6: Treble response

Figure 5: Bass response

R

i

= 44k

C9 = C10 = 100nF (Bout, Bin)

R3 = 5.6k

TDA7440D

6/16

I

2

C BUS INTERFACE

Data transmission from microprocessor to the

TDA7440D and vice versa takes place through

the 2 wires I

2

C BUS interface, consisting of the

two lines SDA and SCL (pull-up resistors to posi-

tive supply voltage must be connected).

Data Validity

As shown in fig. 7, the data on the SDA line must

be stable during the high period of the clock. The

HIGH and LOW state of the data line can only

change when the clock signal on the SCL line is

LOW.

Start and Stop Conditions

As shown in fig.8 a start condition is a HIGH to

LOW transition of the SDA line while SCL is

HIGH. The stop condition is a LOW to HIGH tran-

sition of the SDA line while SCL is HIGH.

Byte Format

Every byte transferred on the SDA line must con-

tain 8 bits. Each byte must be followed by an ac-

knowledge bit. The MSB is transferredfirst.

Acknowledge

The master (P) puts a resistive HIGHlevel on the

SDA line during the acknowledge clock pulse (see

fig. 9). The peripheral (audio processor) that ac-

knowledges has to pull-down (LOW) the SDA line

during this clock pulse.

The audio processor which has been addressed

has to generate an acknowledge after the recep-

tion of each byte, otherwise the SDA line remains

at the HIGH level during the ninth clock pulse

time. In this case the master transmitter can gen-

erate the STOP information in order to abort the

transfer.

Transmissionwithout Acknowledge

Avoiding to detect the acknowledge of the audio

processor, the P can use a simpler transmission:

simply it waits one clock without checking the

slave acknowledging, and sends the new data.

This approach of course is less protected from

misworking.

Figure 7: Data Validity on the I

2

CBUS

Figure 8: Timing Diagramof I

2

CBUS

Figure 9: Acknowledge on the I

2

CBUS

TDA7440D

7/16

SOFTWARE SPECIFICATION

InterfaceProtocol

The interface protocol comprises:

A start condition (S)

A chip address byte, containingthe TDA7440D

address

A subaddressbytes

A sequenceof data (N byte + acknowledge)

A stop condition (P)

ACK = Acknowledge

S = Start

P = Stop

A = Address

B = Auto Increment

S 1 0 0 0 1 0 0 0 ACK ACK DATA ACK P

MSB LSB MSB LSB MSB LSB

CHIP ADDRESS

D96AU420

X DATA

SUBADDRESS DATA 1 to DATA n

X X B

EXAMPLES

No Incremental Bus

The TDA7440D receives a start condition, the

correct chip address, a subaddresswith the B = 0

(no incremental bus), N-data (all these data con-

cern the subaddress selected), a stop condition.

S 1 0 0 0 1 0 0 0 ACK ACK DATA ACK P

MSB LSB MSB LSB MSB LSB

CHIP ADDRESS

D96AU421

X D3

SUBADDRESS DATA

X X 0 D2 D1 D0

Incremental Bus

The TDA7440D receive a start conditions, the

correct chip address, a subaddress with the B = 1

(incremental bus): now it is in a loop condition

with an autoincrease of the subaddress whereas

SUBADDRESS from XXX1000 to XXX1111 of

DATAare ignored.

The DATA 1 concern the subaddress sent, and

the DATA 2 concern the subaddress sent plus

one in the loop etc, and at the end it receivers the

stop condition.

S 1 0 0 0 1 0 0 0 ACK ACK DATA ACK P

MSB LSB MSB LSB MSB LSB

CHIP ADDRESS

D96AU422

X D3

SUBADDRESS DATA 1 to DATA n

X X 1 D2 D1 D0

TDA7440D

8/16

POWERON RESET CONDITION

INPUT SELECTION IN2

INPUT GAIN 28dB

VOLUME MUTE

BASS 0dB

TREBLE 2dB

SPEAKER MUTE

DATA BYTES

Address = 88 HEX (ADDR:OPEN).

FUNCTIONSELECTION: First byte (subaddress)

MSB LSB

SUBADDRESS

D7 D6 D5 D4 D3 D2 D1 D0

X X X B 0 0 0 0 INPUT SELECT

X X X B 0 0 0 1 INPUT GAIN

X X X B 0 0 1 0 VOLUME

X X X B 0 0 1 1 BASS

X X X B 0 1 0 0 NOT USED

X X X B 0 1 0 1 TREBLE

X X X B 0 1 1 0 SPEAKER ATTENUATE R

X X X B 0 1 1 1 SPEAKER ATTENUATE L

B = 1: INCREMENTAL BUS ACTIVE

B = 0: NO INCREMENTAL BUS

X = DONT CARE

INPUT SELECTION

MSB LSB

INPUT MULTIPLEXER

D7 D6 D5 D4 D3 D2 D1 D0

X X X X X X 0 0 IN4

X X X X X X 0 1 IN3

X X X X X X 1 0 IN2

X X X X X X 1 1 IN1

In Incremental Bus Mode, the not used function must be addressed in any case. For example to re-

fresh Volume = 0dB and Speaker_R= -40dB, the following bytes must be sent:

SUBADDRESS XXX10010

VOLUME DATA X0000000

BUS DATA XXXX1111

NOT USED DATA XXXX1111

TREBLE DATA XXXX1111

SPEAKER_R DATA X0000010

TDA7440D

9/16

DATA BYTES (continued)

INPUT GAIN SELECTION

MSB LSB INPUT GAIN

D7 D6 D5 D4 D3 D2 D1 D0 2dB STEPS

0 0 0 0 0dB

0 0 0 1 2dB

0 0 1 0 4dB

0 0 1 1 6dB

0 1 0 0 8dB

0 1 0 1 10dB

0 1 1 0 12dB

0 1 1 1 14dB

1 0 0 0 16dB

1 0 0 1 18dB

1 0 1 0 20dB

1 0 1 1 22dB

1 1 0 0 24dB

1 1 0 1 26dB

1 1 1 0 28dB

1 1 1 1 30dB

GAIN= 0 to 30dB

VOLUMESELECTION

MSB LSB VOLUME

D7 D6 D5 D4 D3 D2 D1 D0 1dB STEPS

0 0 0 0dB

0 0 1 -1dB

0 1 0 -2dB

0 1 1 -3dB

1 0 0 -4dB

1 0 1 -5dB

1 1 0 -6dB

1 1 1 -7dB

0 0 0 0 0dB

0 0 0 1 -8dB

0 0 1 0 -16dB

0 0 1 1 -24dB

0 1 0 0 -32dB

0 1 0 1 -40dB

X 1 1 1 X X X MUTE

VOLUME = 0 to 47dB/MUTE

TDA7440D

10/16

DATA BYTES (continued)

BASS SELECTION

MSB LSB BASS

D7 D6 D5 D4 D3 D2 D1 D0 2dB STEPS

0 0 0 0 -14dB

0 0 0 1 -12dB

0 0 1 0 -10dB

0 0 1 1 -8dB

0 1 0 0 -6dB

0 1 0 1 -4dB

0 1 1 0 -2dB

0 1 1 1 0dB

1 1 1 1 0dB

1 1 1 0 2dB

1 1 0 1 4dB

1 1 0 0 6dB

1 0 1 1 8dB

1 0 1 0 10dB

1 0 0 1 12dB

1 0 0 0 14dB

TREBLE SELECTION

MSB LSB TREBLE

D7 D6 D5 D4 D3 D2 D1 D0 2dB STEPS

0 0 0 0 -14dB

0 0 0 1 -12dB

0 0 1 0 -10dB

0 0 1 1 -8dB

0 1 0 0 -6dB

0 1 0 1 -4dB

0 1 1 0 -2dB

0 1 1 1 0dB

1 1 1 1 0dB

1 1 1 0 2dB

1 1 0 1 4dB

1 1 0 0 6dB

1 0 1 1 8dB

1 0 1 0 10dB

1 0 0 1 12dB

1 0 0 0 14dB

TDA7440D

11/16

DATA BYTES (continued)

SPEAKERATTENUATE SELECTION

MSB LSB SPEAKER ATTENUATION

D7 D6 D5 D4 D3 D2 D1 D0 1dB

0 0 0 0dB

0 0 1 -1dB

0 1 0 -2dB

0 1 1 -3dB

1 0 0 -4dB

1 0 1 -5dB

1 1 0 -6dB

1 1 1 -7dB

0 0 0 0 0dB

0 0 0 1 -8dB

0 0 1 0 -16dB

0 0 1 1 -24dB

0 1 0 0 -32dB

0 1 0 1 -40dB

0 1 1 0 -48dB

0 1 1 1 -56dB

1 0 0 0 -64dB

1 0 0 1 -72dB

1 1 1 1 X X X MUTE

SPEAKERATTENUATION = 0 to -79dB/MUTE

TDA7440D

12/16

20K

20K

CREF

V

S

D96AU430

V

S

PINS: 23

V

S

D96AU434

20A

ROUT 24

LOUT

PINS: 26,27

V

S

D96AU426

20A

V

S

MIXOUT

GND

PINS: 8, 10

20A

V

S

100K

V

REF

D96AU425

IN

PINS: 1, 2, 3, 4, 5, 6, 7, 28

20A

V

S

33K

D96AU427

INL

INR

V

REF

PINS: 19, 11

44K

V

S

BIN(R) D96AU428

20A

BIN(L)

PINS: 12,14

TDA7440D

13/16

50K

V

S

TREBLE(R)

D96AU433

20A

TREBLE(L)

PINS: 18, 19

44K

V

S

BOUT(R) D96AU429

20A

BOUT(L)

PINS: 13, 15

D96AU423

20A

SDA

PINS: 21

D96AU424

20A

SCL

PINS: 20

TDA7440D

14/16

SO28

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.65 0.104

a1 0.1 0.3 0.004 0.012

b 0.35 0.49 0.014 0.019

b1 0.23 0.32 0.009 0.013

C 0.5 0.020

c1 45 (typ.)

D 17.7 18.1 0.697 0.713

E 10 10.65 0.394 0.419

e 1.27 0.050

e3 16.51 0.65

F 7.4 7.6 0.291 0.299

L 0.4 1.27 0.016 0.050

S 8 (max.)

OUTLINE AND

MECHANICAL DATA

TDA7440D

15/16

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parti es which may result from its use. No li cense is

granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are

subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

1999 STMicroelectronics Printed in Italy All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands -

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com

TDA7440D

16/16

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

Вам также может понравиться

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- TDA7442 TDA7442D: Tone Control and Surround Digitally Controlled Audio ProcessorДокумент17 страницTDA7442 TDA7442D: Tone Control and Surround Digitally Controlled Audio ProcessormochuraОценок пока нет

- A Better Kiln CoatingДокумент2 страницыA Better Kiln Coatingamir100% (4)

- Revit Mep Vs Autocad MepДокумент4 страницыRevit Mep Vs Autocad MepAbdelhameed Tarig AlemairyОценок пока нет

- Tda 7440Документ17 страницTda 7440Albert ThomasОценок пока нет

- Tda 7313Документ14 страницTda 7313ClaudiuMaxmiucОценок пока нет

- Tda 7439Документ17 страницTda 7439Arwana ChipmunksОценок пока нет

- Tda 7438Документ18 страницTda 7438sontuyet82Оценок пока нет

- TDA7442Документ16 страницTDA7442gaston30-3@Оценок пока нет

- Hoja de Datos Del TDA 7439Документ20 страницHoja de Datos Del TDA 7439_el_patriarca_Оценок пока нет

- Tda 7468DДокумент22 страницыTda 7468DJohn Keneth Vasquez100% (1)

- Tda 7449Документ18 страницTda 7449Ariel NavarreteОценок пока нет

- Tda 7442Документ17 страницTda 7442Ariel NavarreteОценок пока нет

- 4-Ch Output Stereo Audio Processor With 4 Stereo Inputs and Tone/Volume ControlДокумент13 страниц4-Ch Output Stereo Audio Processor With 4 Stereo Inputs and Tone/Volume ControlRaúl García LópezОценок пока нет

- Tda7317 EcualizadorДокумент13 страницTda7317 EcualizadorRafael AlcazarОценок пока нет

- Tda 7340GДокумент27 страницTda 7340GAndrei PetriciОценок пока нет

- Tda 7313Документ15 страницTda 7313jordachadiОценок пока нет

- Ta 0104 AДокумент18 страницTa 0104 AJump DownОценок пока нет

- Tda 7313Документ14 страницTda 7313Ariel NavarreteОценок пока нет

- THAT 1510/1512Документ6 страницTHAT 1510/1512Jefferson Gutama ValladaresОценок пока нет

- Integrado An5829sДокумент20 страницIntegrado An5829sangelr203619219Оценок пока нет

- Datasheet AN5829S - Sound Multiplex Decoder IC For The U.S. Televisions - Panasonic SemiconductorДокумент17 страницDatasheet AN5829S - Sound Multiplex Decoder IC For The U.S. Televisions - Panasonic Semiconductorfernandog251186Оценок пока нет

- Njw1197a eДокумент15 страницNjw1197a eSava Beljan-SavijaОценок пока нет

- An7316 Idjo3Документ5 страницAn7316 Idjo3Andy Luis Morales GuerraОценок пока нет

- 1395Документ14 страниц1395Aurel-LucianNedaОценок пока нет

- Programmable Quad Bipolar Operational Amplifier: LM146 LM246 LM346Документ6 страницProgrammable Quad Bipolar Operational Amplifier: LM146 LM246 LM346Alejandro Borrego DominguezОценок пока нет

- Ad7730 7730LДокумент52 страницыAd7730 7730LDa Q ShaОценок пока нет

- AK5358A 96kHz 24-Bit ΔΣ ADCДокумент18 страницAK5358A 96kHz 24-Bit ΔΣ ADCAlver TuizaОценок пока нет

- LV1035MДокумент3 страницыLV1035Msudhakar.mrОценок пока нет

- Tda 7339Документ12 страницTda 7339Giovanni Carrillo VillegasОценок пока нет

- 3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LДокумент36 страниц3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858Ljnax101Оценок пока нет

- 60 W Hi-Fi Dual Audio Driver: DescriptionДокумент12 страниц60 W Hi-Fi Dual Audio Driver: DescriptionLenin BabuОценок пока нет

- Quad Power Amplifier With Built-In Voltage Converter: DescriptionДокумент10 страницQuad Power Amplifier With Built-In Voltage Converter: DescriptionbakaninhaОценок пока нет

- AN8806SB: Three-Beam Method Head Amplifier IC For CD PlayerДокумент10 страницAN8806SB: Three-Beam Method Head Amplifier IC For CD PlayeraldoОценок пока нет

- SANYO Semiconductor LA76814 Single-Chip VIF/SIF/Y/C/Deflection ICДокумент35 страницSANYO Semiconductor LA76814 Single-Chip VIF/SIF/Y/C/Deflection ICLeonel MartinezОценок пока нет

- LM4811 Dual 105mW Headphone Amplifier With Digital Volume Control and Shutdown ModeДокумент20 страницLM4811 Dual 105mW Headphone Amplifier With Digital Volume Control and Shutdown ModeBuga BuniciОценок пока нет

- DolbyC DatasheetДокумент63 страницыDolbyC Datasheetsoumya63Оценок пока нет

- Lm6172 Op Amp DobleДокумент19 страницLm6172 Op Amp DobleGREKO_ONEОценок пока нет

- 3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LДокумент32 страницы3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LJodelCamarinОценок пока нет

- Linear - 16-Bit, Ultra Precise, Fast Settling VOUT DACДокумент16 страницLinear - 16-Bit, Ultra Precise, Fast Settling VOUT DACAtakan OzturKОценок пока нет

- TA1270BF: Pal / NTSC Video Chroma and Sync Processing System For Pip / Pop / PapДокумент39 страницTA1270BF: Pal / NTSC Video Chroma and Sync Processing System For Pip / Pop / PapAzmi PlgОценок пока нет

- La 1140Документ15 страницLa 1140Mariano KokoОценок пока нет

- Ssm2120 2 ExpanderДокумент12 страницSsm2120 2 ExpandershirtquittersОценок пока нет

- ssm2165 B PDFДокумент12 страницssm2165 B PDFenzo_60Оценок пока нет

- MC3303 MC3403 - MC3503: Quad Bipolar Operational AmplifiersДокумент10 страницMC3303 MC3403 - MC3503: Quad Bipolar Operational AmplifiersAmirОценок пока нет

- WM9701A Low Power AC'97 Multimedia Audio Codec: Description FeaturesДокумент0 страницWM9701A Low Power AC'97 Multimedia Audio Codec: Description FeaturesJorBS57Оценок пока нет

- High-output 4-channel car audio amplifier with protection circuitsДокумент9 страницHigh-output 4-channel car audio amplifier with protection circuitsban4444Оценок пока нет

- DatasheetДокумент10 страницDatasheetJose SalgueroОценок пока нет

- Datasheet 2Документ10 страницDatasheet 2miguel angel jaramilloОценок пока нет

- TDA7432 BASIC AUDIO PROCESSORДокумент11 страницTDA7432 BASIC AUDIO PROCESSORgreemaxОценок пока нет

- SC 9711Документ14 страницSC 9711dragon-red0816Оценок пока нет

- UTC1018Документ8 страницUTC1018tangbunnaОценок пока нет

- Features Descriptio: Ltc1566-1 Low Noise 2.3Mhz Continuous Time Lowpass FilterДокумент8 страницFeatures Descriptio: Ltc1566-1 Low Noise 2.3Mhz Continuous Time Lowpass Filtergiapy0000Оценок пока нет

- Dvb-S Tuner Max2120Документ21 страницаDvb-S Tuner Max2120Глеб АвдеенкоОценок пока нет

- Max Power 43 W BTL × 4 CH Audio Power IC: FeaturesДокумент12 страницMax Power 43 W BTL × 4 CH Audio Power IC: FeaturesMiloud ChouguiОценок пока нет

- LV23002MДокумент13 страницLV23002Mmister_wОценок пока нет

- Tda 2593Документ6 страницTda 2593Luis Arturo Leiva MonjarasОценок пока нет

- 4 X 45W Quad Bridge Car Radio Amplifier Plus HSD: Multipower BCD TechnologyДокумент11 страниц4 X 45W Quad Bridge Car Radio Amplifier Plus HSD: Multipower BCD TechnologysanlugoОценок пока нет

- Order Confirmation Number #W1098340: Ship To: Bill ToДокумент1 страницаOrder Confirmation Number #W1098340: Ship To: Bill ToJimmy R. Calderon GualeОценок пока нет

- TL-WR841N V9 Ug PDFДокумент111 страницTL-WR841N V9 Ug PDFAndika rasmancaОценок пока нет

- DG K 5120001Документ65 страницDG K 5120001Jimmy R. Calderon GualeОценок пока нет

- 2016 - Folleto Sri PDFДокумент16 страниц2016 - Folleto Sri PDFJimmy R. Calderon GualeОценок пока нет

- Guiafusores MultipartsДокумент4 страницыGuiafusores MultipartsJimmy R. Calderon GualeОценок пока нет

- Folleto Sri 2016Документ16 страницFolleto Sri 2016Jimmy R. Calderon GualeОценок пока нет

- Philips L03 SSДокумент60 страницPhilips L03 SSMarco Antonio100% (12)

- IC-ON-LINE - CN c6090ls 393717Документ4 страницыIC-ON-LINE - CN c6090ls 393717Jimmy R. Calderon GualeОценок пока нет

- Ka3082 Controlador de Motores CCДокумент12 страницKa3082 Controlador de Motores CCshibatoyanОценок пока нет

- TV-Goldstar Chasis NC12JДокумент1 страницаTV-Goldstar Chasis NC12JJimmy R. Calderon GualeОценок пока нет

- Land, Soil, Water, Natural Vegetation& Wildlife ResourcesДокумент26 страницLand, Soil, Water, Natural Vegetation& Wildlife ResourcesKritika VermaОценок пока нет

- Handouts For Semantics GradДокумент8 страницHandouts For Semantics GradPhuong Thao DangОценок пока нет

- 100 Seniman Yang Membentuk Sejarah DuniaДокумент134 страницы100 Seniman Yang Membentuk Sejarah DuniaIBRAHIM S.Sos,IОценок пока нет

- PHY3 BJune 2004Документ1 страницаPHY3 BJune 2004api-3726022Оценок пока нет

- Comparing Means of Two GroupsДокумент8 страницComparing Means of Two GroupsRobert Kier Tanquerido TomaroОценок пока нет

- Educational PlanningДокумент20 страницEducational PlanningedelynОценок пока нет

- CH06 Binding MaterialsДокумент114 страницCH06 Binding MaterialsAbass AwalehОценок пока нет

- Hussam Al-Furqan Ala Mann Haajj Al-Qur'anДокумент34 страницыHussam Al-Furqan Ala Mann Haajj Al-Qur'anNoori al-Qadiri0% (1)

- Corporate Social Responsibility International PerspectivesДокумент14 страницCorporate Social Responsibility International PerspectivesR16094101李宜樺Оценок пока нет

- Plumbing Layout and SpecificationsДокумент1 страницаPlumbing Layout and SpecificationsLiza P. PaculanangОценок пока нет

- AA Practice Problems on Amino Acids and Peptides (less than 40 charsДокумент20 страницAA Practice Problems on Amino Acids and Peptides (less than 40 charsNurlaeli NaelulmunaMajdiyahОценок пока нет

- The Spurgeon Library - Spurgeon's Secret For Raising Godly ChildrenДокумент8 страницThe Spurgeon Library - Spurgeon's Secret For Raising Godly ChildrenGlenn VillegasОценок пока нет

- Villanueva - Taxation and Regulatory ComplianceДокумент8 страницVillanueva - Taxation and Regulatory ComplianceEDRICK ESPARRAGUERRAОценок пока нет

- CHAPTER 8 SULLIVAN MyReviewerДокумент7 страницCHAPTER 8 SULLIVAN MyReviewerFrances LouiseОценок пока нет

- Business Analytics ModuleДокумент22 страницыBusiness Analytics ModuleMarjon DimafilisОценок пока нет

- SAP Untangled: An Introductory Guide To SAP For New HomesДокумент28 страницSAP Untangled: An Introductory Guide To SAP For New HomestempuserОценок пока нет

- MicrotoxOmni Software Version 4Документ12 страницMicrotoxOmni Software Version 4Louise Veronica JoseОценок пока нет

- MirazДокумент1 страницаMirazTatat PatrianiОценок пока нет

- Useful List of Responsive Navigation and Menu Patterns - UI Patterns - GibbonДокумент16 страницUseful List of Responsive Navigation and Menu Patterns - UI Patterns - Gibbonevandrix0% (1)

- A P1qneer 1n Neuroscience: Rita Levi-MontalciniДокумент43 страницыA P1qneer 1n Neuroscience: Rita Levi-MontalciniAntОценок пока нет

- Mr. Sanjeev Nanda - Devoted Son and GrandsonДокумент1 страницаMr. Sanjeev Nanda - Devoted Son and GrandsonSanjeev NandaОценок пока нет

- NRBC-Internship Report - ShafayetДокумент54 страницыNRBC-Internship Report - ShafayetShafayet JamilОценок пока нет

- Essay #01 (First Draft)Документ2 страницыEssay #01 (First Draft)thanhtam3819Оценок пока нет

- The 5th Edition of The World Health Organization Classification - of Haematolymphoid Tumours Myeloid and Histiocytic - Dendritic NeoplasmsДокумент17 страницThe 5th Edition of The World Health Organization Classification - of Haematolymphoid Tumours Myeloid and Histiocytic - Dendritic NeoplasmsADMINISTRACION LABORATORIO INTERMEDICAОценок пока нет

- The Message Development Tool - A Case For Effective Operationalization of Messaging in Social Marketing PracticeДокумент17 страницThe Message Development Tool - A Case For Effective Operationalization of Messaging in Social Marketing PracticesanjayamalakasenevirathneОценок пока нет

- 1 - Introducing Your SelfДокумент31 страница1 - Introducing Your SelfAbdurrahmanОценок пока нет

- Cable Drag ChainДокумент44 страницыCable Drag ChainsunhuynhОценок пока нет

- MAMALUMPONG JORDAN A. BSN-3 Literature ReviewДокумент3 страницыMAMALUMPONG JORDAN A. BSN-3 Literature ReviewJordan Abosama MamalumpongОценок пока нет