Академический Документы

Профессиональный Документы

Культура Документы

Data Sheet IRF530 (Power MOSFET) PDF

Загружено:

Juan Luis MerloИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Data Sheet IRF530 (Power MOSFET) PDF

Загружено:

Juan Luis MerloАвторское право:

Доступные форматы

1

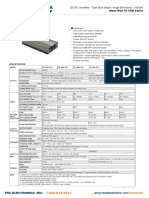

IRF530

14A, 100V, 0.160 Ohm, N-Channel Power

MOSFETs

These are N-Channel enhancement mode silicon gate

power eld effect transistors. They are advanced power

MOSFETs designed, tested, and guaranteed to withstand a

specied level of energy in the breakdown avalanche mode

of operation. All of these power MOSFETs are designed for

applications such as switching regulators, switching

convertors, motor drivers, relay drivers, and drivers for high

power bipolar switching transistors requiring high speed and

low gate drive power. These types can be operated directly

from integrated circuits.

Formerly developmental type TA17411.

Features

14A, 100V

r

DS(ON)

= 0.160

Single Pulse Avalanche Energy Rated

SOA is Power Dissipation Limited

Nanosecond Switching Speeds

Linear Transfer Characteristics

High Input Impedance

Related Literature

- TB334 Guidelines for Soldering Surface Mount

Components to PC Boards

Symbol

Packaging

JEDEC TO-220AB

Ordering Information

PART NUMBER PACKAGE BRAND

IRF530 TO-220AB IRF530

NOTE: When ordering, use the entire part number.

G

D

S

GATE

DRAIN (FLANGE)

SOURCE

DRAIN

Data Sheet February 2002

[ /Title

(IRF53

0,

RF1S5

30SM)

/Sub-

ject

(14A,

100V,

0.160

Ohm,

N-

Chan-

nel

Power

MOS-

FETs)

/Autho

r ()

/Key-

words

(14A,

100V,

0.160

Ohm,

N-

Chan-

nel

Power

MOS-

FETs,

Inter-

sil

Corpo-

ration,

TO-

220AB

, TO-

263AB

CAUTION: These devices are sensitive to electrostatic discharge; follow proper ESD Handling Procedures.

2002 Fairchild Semiconductor Corporation IRF530 Rev. B1

2

Absolute Maximum Ratings T

C

= 25

o

C, Unless Otherwise Specied

IRF530 UNITS

Drain to Source Breakdown Voltage (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

DS

100 V

Drain to Gate Voltage (R

GS

= 20k) (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

DGR

100 V

Continuous Drain Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

D

T

C

= 100

o

C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

D

14

10

A

A

Pulsed Drain Current (Note 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

DM

56 A

Gate to Source Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

GS

20 V

Maximum Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .P

D

79 W

Dissipation Derating Factor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.53 W/

o

C

Single Pulse Avalanche Energy Rating (Note 4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .E

AS

69 mJ

Operating and Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

J,

T

STG

-55 to 175

o

C

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10s. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

L

Package Body for 10s, See Techbrief 334 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

pkg

300

260

o

C

o

C

CAUTION: Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specication is not implied.

NOTE:

1. T

J

= 25

o

C to 150

o

C.

Electrical Specications T

C

= 25

o

C, Unless Otherwise Specied

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Drain to Source Breakdown Voltage BV

DSS

I

D

= 250A, V

GS

= 0V (Figure 10) 100 - - V

Gate to Threshold Voltage V

GS(TH)

V

GS

= V

DS

, I

D

= 250A 2 - 4.0 V

Zero Gate Voltage Drain Current I

DSS

V

DS

= 95V, V

GS

= 0V - - 25 A

V

DS

= 0.8 x Rated BV

DSS

, V

GS

= 0V, T

J

= 150

o

C - - 250 A

On-State Drain Current (Note 2) I

D(ON)

V

DS

> I

D(ON)

x r

DS(ON) MAX

, V

GS

= 10V 14 - - A

Gate to Source Leakage Current I

GSS

V

GS

= 20V - - 500 nA

Drain to Source On Resistance (Note 2) r

DS(ON)

I

D

= 8.3A, V

GS

= 10V (Figures 8, 9) - 0.14 0.16

Forward Transconductance (Note 2) g

fs

V

DS

50V, I

D

= 8.3A (Figure 12) 5.1 7.6 - S

Turn-On Delay Time t

d(ON)

V

DD

= 50V, I

D

14A, R

G

12, R

L

= 3.4

MOSFET Switching Times are Essentially

Independent of Operating Temperature

- 12 15 ns

Rise Time t

r

- 35 65 ns

Turn-Off Delay Time t

d(OFF)

- 25 70 ns

Fall Time t

f

- 25 59 ns

Total Gate Charge

(Gate to Source + Gate to Drain)

Q

g(TOT)

V

GS

= 10V, I

D

= 14A, V

DS

= 0.8 x Rated BV

DSS

I

g(REF)

= 1.5mA (Figure 14)

Gate Charge is Essentially Independent of

Operating Temperature

- 18 30 nC

Gate to Source Charge Q

gs

- 4 - nC

Gate to Drain Miller Charge Q

gd

- 7 - nC

Input Capacitance C

ISS

V

DS

= 25V, V

GS

= 0V, f = 1MHz (Figure 11) - 600 - pF

Output Capacitance C

OSS

- 250 - pF

Reverse Transfer Capacitance C

RSS

- 50 - pF

Internal Drain Inductance L

D

Measured from the

Contact Screw on Tab To

Center of Die

Modified MOSFET

Symbol Showing the

Internal Devices

Inductances

- 3.5 - nH

Measured from the Drain

Lead, 6mm (0.25in) from

Package to Center of Die

- 4.5 - nH

Internal Source Inductance L

S

Measured fromthe Source

Lead, 6mm (0.25in) From

Header to Source Bonding

Pad

- 7.5 - nH

Thermal Resistance Junction to Case R

JC

- - 1.9

o

C/W

Thermal Resistance Junction to

Ambient

R

JA

Free Air Operation - - 62.5

o

C/W

- - - -

L

S

L

D

G

D

S

IRF530

2002 Fairchild Semiconductor Corporation IRF530 Rev. B1

3

Source to Drain Diode Specications

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Continuous Source to Drain Current I

SD

Modified MOSFET Symbol

Showing the Integral

Reverse P-N Junction

Diode

- - 14 A

Pulse Source to Drain Current (Note 2) I

SDM

- - 56 A

Source to Drain Diode Voltage (Note 2) V

SD

T

J

= 25

o

C, I

SD

= 14A, V

GS

= 0V (Figure 13) - - 2.5 V

Reverse Recovery Time t

rr

T

J

= 25

o

C, I

SD

= 14A, dI

SD

/dt = 100A/s 5.5 120 250 ns

Reverse Recovery Charge Q

RR

T

J

= 25

o

C, I

SD

= 14A, dI

SD

/dt = 100A/s 0.17 0.6 1.3 C

NOTES:

2. Pulse test: pulse width 300s, duty cycle 2%.

3. Repetitive rating: pulse width limited by Max junction temperature. See Transient Thermal Impedance curve (Figure 3).

4. V

DD

= 25V, starting T

J

= 25

o

C, L = 530H, R

G

= 25, peak I

AS

= 14A (Figures 15, 16).

Typical Performance Curves Unless Otherwise Specied

FIGURE 1. NORMALIZED POWER DISSIPATION vs CASE

TEMPERATURE

FIGURE 2. MAXIMUMCONTINUOUS DRAIN CURRENT vs

CASE TEMPERATURE

FIGURE 3. MAXIMUM TRANSIENT THERMAL IMPEDANCE

G

D

S

T

C

, CASE TEMPERATURE (

o

C)

25 50 75 100 125 150 175 0

P

O

W

E

R

D

I

S

S

I

P

A

T

I

O

N

M

U

L

T

I

P

L

I

E

R

0

0

0.2

0.4

0.6

0.8

1.0

1.2

6

3

0

25 50 75 100 125 150

12

I

D

,

D

R

A

I

N

C

U

R

R

E

N

T

(

A

)

T

C

, CASE TEMPERATURE (

o

C)

15

175

9

t

P

, RECTANGULAR PULSE DURATION (s)

10

Z

J

C

,

T

R

A

N

S

I

E

N

T

T

H

E

R

M

A

L

I

M

P

E

D

A

N

C

E

10

-3

10

-2

0.1 1

1

10

-5

10

-4

10

0.01

0.1

NOTES:

DUTY FACTOR: D = t

1

/t

2

PEAK T

J

= P

DM

x Z

JC

+ T

C

P

DM

t

1

t

2

0.1

0.02

0.2

0.5

0.01

0.05

SINGLE PULSE

IRF530

2002 Fairchild Semiconductor Corporation IRF530 Rev. B1

4

FIGURE 4. FORWARD BIAS SAFE OPERATING AREA FIGURE 5. OUTPUT CHARACTERISTICS

FIGURE 6. SATURATION CHARACTERISTICS FIGURE 7. TRANSFER CHARACTERISTICS

FIGURE 8. DRAIN TO SOURCE ON RESISTANCE vs GATE

VOLTAGE AND DRAIN CURRENT

FIGURE 9. NORMALIZED DRAIN TOSOURCE ON

RESISTANCE vs JUNCTION TEMPERATURE

Typical Performance Curves Unless Otherwise Specied (Continued)

V

DS

, DRAIN TO SOURCE VOLTAGE (V)

10

0.1

10

1

I

D

,

D

R

A

I

N

C

U

R

R

E

N

T

(

A

)

10

2

10

2

LIMITED BY r

DS(ON)

AREA MAY BE

OPERATION IN THIS

T

J

= 175

o

C

SINGLE PULSE

100s

10s

1ms

10ms

10

3

1

10

3

T

C

= 25

o

C

V

DS

, DRAIN TO SOURCE VOLTAGE (V)

I

D

,

D

R

A

I

N

C

U

R

R

E

N

T

(

A

)

0

0 10 20 30 40

5

10

15

20

25

50

V

GS

= 7V

V

GS

= 6V

V

GS

= 5V

V

GS

= 4V

PULSE DURATION = 80s

V

GS

= 10V

V

GS

= 8V

DUTY CYCLE = 0.5% MAX

0

5

0 1 2 3 5

10

15

I

D

,

D

R

A

I

N

C

U

R

R

E

N

T

(

A

)

V

DS

, DRAIN TO SOURCE VOLTAGE (V)

V

GS

= 6V

V

GS

= 10V

20

4

V

GS

= 4V

V

GS

= 7V

V

GS

= 5V

25

V

GS

= 8V

PULSE DURATION = 80s

DUTY CYCLE = 0.5% MAX

0 4 6 8 10 2

0.1

1

10

I

D

S

(

O

N

)

,

D

R

A

I

N

T

O

S

O

U

R

C

E

C

U

R

R

E

N

T

(

A

)

V

GS

, GATE TO SOURCE VOLTAGE (V)

100

25

o

C 175

o

C

PULSE DURATION = 80s

DUTY CYCLE = 0.5% MAX

V

DS

50V

0

0.6

0.9

1.2

12 24 36 48

r

D

S

(

O

N

)

,

O

N

-

S

T

A

T

E

R

E

S

I

S

T

A

N

C

E

(

)

I

D

, DRAIN CURRENT (A)

60

1.5

0

0.3

V

GS

= 20V

V

GS

= 10V

PULSE DURATION = 80s

DUTY CYCLE = 0.5% MAX

N

O

R

M

A

L

I

Z

E

D

O

N

R

E

S

I

S

T

A

N

C

E

3.0

1.8

1.2

0.6

0

-60 -40 -20 0 20 40 60

T

J

, JUNCTION TEMPERATURE (

o

C)

100 120 140 160 180

2.4

80

PULSE DURATION = 80s

DUTY CYCLE = 0.5% MAX

V

GS

= 10V, I

D

= 14A

IRF530

2002 Fairchild Semiconductor Corporation IRF530 Rev. B1

5

FIGURE 10. NORMALIZED DRAIN TOSOURCE BREAKDOWN

VOLTAGE vs JUNCTION TEMPERATURE

FIGURE 11. CAPACITANCE vs DRAIN TO SOURCE VOLTAGE

FIGURE 12. TRANSCONDUCTANCE vs DRAIN CURRENT FIGURE 13. SOURCE TO DRAIN DIODE VOLTAGE

FIGURE 14. GATE TO SOURCE VOLTAGE vs GATE CHARGE

Typical Performance Curves Unless Otherwise Specied (Continued)

1.25

1.05

0.95

0.85

0.75

-60 -40 -20 0 20 40 60

T

J

, JUNCTION TEMPERATURE (

o

C)

N

O

R

M

A

L

I

Z

E

D

D

R

A

I

N

T

O

S

O

U

R

C

E

B

R

E

A

K

D

O

W

N

V

O

L

T

A

G

E

100 120 140 160 180

1.15

80

I

D

= 250A

1500

300

0

1

10 10

2

C

,

C

A

P

A

C

I

T

A

N

C

E

(

p

F

)

900

V

DS

, DRAIN TO SOURCE VOLTAGE (V)

1200

600

C

ISS

= C

GS

+ C

GD

C

RSS

= C

GD

C

OSS

C

DS

+ C

GD

C

ISS

C

OSS

C

RSS

V

GS

= 0V, f = 1MHz

I

D

, DRAIN CURRENT (A)

g

f

s

,

T

R

A

N

S

C

O

N

D

U

C

T

A

N

C

E

(

S

)

0

0 5 10 15 20

2

4

6

8

10

25

175

o

C

25

o

C

PULSE DURATION = 80s

DUTY CYCLE = 0.5% MAX

V

DS

50V

0 0.8 1.2 1.6 2.0 0.4

0.1

1

10

I

S

D

,

S

O

U

R

C

E

T

O

D

R

A

I

N

C

U

R

R

E

N

T

(

A

)

V

SD

, SOURCE TO DRAIN VOLTAGE (V)

100

175

o

C 25

o

C

PULSE DURATION = 80s

DUTY CYCLE = 0.5% MAX

Q

G

, GATE CHARGE (nC)

V

G

S

,

G

A

T

E

T

O

S

O

U

R

C

E

(

V

)

0

0 6 12 18 24

4

8

12

16

20

30

I

D

= 14A

V

DS

= 50V

V

DS

= 80V

V

DS

= 20V

IRF530

2002 Fairchild Semiconductor Corporation IRF530 Rev. B1

6

Test Circuits and Waveforms

FIGURE 15. UNCLAMPED ENERGY TEST CIRCUIT FIGURE 16. UNCLAMPED ENERGY WAVEFORMS

FIGURE 17. SWITCHING TIME TEST CIRCUIT FIGURE 18. RESISTIVE SWITCHING WAVEFORMS

FIGURE 19. GATE CHARGE TEST CIRCUIT FIGURE 20. GATE CHARGE WAVEFORMS

t

P

V

GS

0.01

L

I

AS

+

-

V

DS

V

DD

R

G

DUT

VARY t

P

TO OBTAIN

REQUIRED PEAK I

AS

0V

V

DD

V

DS

BV

DSS

t

P

I

AS

t

AV

0

V

GS

R

L

R

G

DUT

+

-

V

DD

t

ON

t

d(ON)

t

r

90%

10%

V

DS

90%

10%

t

f

t

d(OFF)

t

OFF

90%

50% 50%

10%

PULSE WIDTH

V

GS

0

0

0.3F

12V

BATTERY

50k

V

DS

S

DUT

D

G

I

g(REF)

0

(ISOLATED

V

DS

0.2F

CURRENT

REGULATOR

I

D

CURRENT

SAMPLING

I

G

CURRENT

SAMPLING

SUPPLY)

RESISTOR RESISTOR

SAME TYPE

AS DUT

Q

g(TOT)

Q

gd

Q

gs

V

DS

0

V

GS

V

DD

I

G(REF)

0

IRF530

2002 Fairchild Semiconductor Corporation IRF530 Rev. B1

Rev. H4

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is

not intended to be an exhaustive list of all such trademarks.

ACEx

Bottomless

CoolFET

CROSSVOLT

DenseTrench

DOME

EcoSPARK

E

2

CMOS

EnSigna

FACT

FACT Quiet Series

FAST

FASTr

FRFET

GlobalOptoisolator

GTO

HiSeC

ISOPLANAR

LittleFET

MicroFET

MicroPak

MICROWIRE

OPTOLOGIC

OPTOPLANAR

PACMAN

POP

Power247

PowerTrench

QFET

QS

QT Optoelectronics

Quiet Series

SILENT SWITCHER

SMART START

STAR*POWER

Stealth

SuperSOT-3

SuperSOT-6

SuperSOT-8

SyncFET

TinyLogic

TruTranslation

UHC

UltraFET

VCX

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;

NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR

CORPORATION.

As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body,

or (b) support or sustain life, or (c) whose failure to perform

when properly used in accordance with instructions for use

provided in the labeling, can be reasonably expected to

result in significant injury to the user.

2. A critical component is any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or In

Design

This datasheet contains the design specifications for

product development. Specifications may change in

any manner without notice.

Preliminary First Production This datasheet contains preliminary data, and

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

Obsolete Not In Production This datasheet contains specifications on a product

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

STAR*POWER is used under license

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

Вам также может понравиться

- D D D D: Description/ordering InformationДокумент13 страницD D D D: Description/ordering InformationpablituuОценок пока нет

- IRF9530Документ8 страницIRF9530Dani IngОценок пока нет

- Irf244, Irf245, Irf246, Irf247: 14A and 13A, 275V and 250V, 0.28 and 0.34 Ohm, N-Channel Power MosfetsДокумент8 страницIrf244, Irf245, Irf246, Irf247: 14A and 13A, 275V and 250V, 0.28 and 0.34 Ohm, N-Channel Power MosfetsKaren RodriguezОценок пока нет

- IRF610Документ8 страницIRF610gtranОценок пока нет

- 30A, 50V, 0.040 Ohm, N-Channel Power Mosfet Features: June 1999 File Number 2253.2 Data SheetДокумент7 страниц30A, 50V, 0.040 Ohm, N-Channel Power Mosfet Features: June 1999 File Number 2253.2 Data SheetArturo LaynaОценок пока нет

- Irf 540 NsДокумент11 страницIrf 540 NsLucas PascualОценок пока нет

- IRFP140: 31A, 100V, 0.077 Ohm, N-Channel Power Mosfet FeaturesДокумент7 страницIRFP140: 31A, 100V, 0.077 Ohm, N-Channel Power Mosfet Featuresdistribusi.pln.bulukumba ABKОценок пока нет

- Irf 630Документ7 страницIrf 630Uriel EutimioОценок пока нет

- IRF9540Документ8 страницIRF9540laplacexxxОценок пока нет

- Datasheet IRFP 9240Документ7 страницDatasheet IRFP 9240AguilaSolitariaОценок пока нет

- DS-MosfetДокумент9 страницDS-MosfetEmin KültürelОценок пока нет

- IRF9540, RF1S9540SM: 19A, 100V, 0.200 Ohm, P-Channel Power Mosfets FeaturesДокумент8 страницIRF9540, RF1S9540SM: 19A, 100V, 0.200 Ohm, P-Channel Power Mosfets FeaturesMartín ReynosoОценок пока нет

- HRF3205 100A, 55V, 0.008 Ohm, N-Channel, PowerДокумент9 страницHRF3205 100A, 55V, 0.008 Ohm, N-Channel, PowerZxdIaminxXzlovewithzxXzyouzxОценок пока нет

- FHL@?M: 'E Ljki@8 C LCK@D 8 Ib KДокумент13 страницFHL@?M: 'E Ljki@8 C LCK@D 8 Ib Kbongo77priestОценок пока нет

- 5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Документ7 страниц5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Rudi AnotheerОценок пока нет

- 5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Документ7 страниц5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Jaricsa BernaolaОценок пока нет

- Irf510 PDFДокумент7 страницIrf510 PDFandri SyahputraОценок пока нет

- Irl 3803Документ9 страницIrl 3803Prashath KugalaОценок пока нет

- 1000W True Sine Wave DC-AC Power Inverter: SeriesДокумент2 страницы1000W True Sine Wave DC-AC Power Inverter: SeriescezarsandufreeОценок пока нет

- Irfr120, Irfu120: 8.4A, 100V, 0.270 Ohm, N-Channel Power Mosfets FeaturesДокумент7 страницIrfr120, Irfu120: 8.4A, 100V, 0.270 Ohm, N-Channel Power Mosfets FeaturesWahyu DiyonoОценок пока нет

- RFP50N05LДокумент6 страницRFP50N05LNegru P. PlantatieОценок пока нет

- IRFR320, IRFU320: 3.1A, 400V, 1.800 Ohm, N-Channel Power Mosfets FeaturesДокумент7 страницIRFR320, IRFU320: 3.1A, 400V, 1.800 Ohm, N-Channel Power Mosfets Featuresmarcodlcruz94Оценок пока нет

- IRF9520Документ8 страницIRF9520David AllendesОценок пока нет

- IRF9640, RF1S9640SM: 11A, 200V, 0.500 Ohm, P-Channel Power Mosfets FeaturesДокумент7 страницIRF9640, RF1S9640SM: 11A, 200V, 0.500 Ohm, P-Channel Power Mosfets Featuresabduallah muhammadОценок пока нет

- Datasheet Mosfet 76132PДокумент10 страницDatasheet Mosfet 76132Padam woodОценок пока нет

- HT7540-1 HoltekSemiconductorДокумент18 страницHT7540-1 HoltekSemiconductorAndrey RossiОценок пока нет

- U9024NДокумент10 страницU9024Nitm12Оценок пока нет

- 10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: File Number 2311.3 Data Sheet July 1999Документ7 страниц10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: File Number 2311.3 Data Sheet July 1999FadiОценок пока нет

- Elp 7 ReportДокумент9 страницElp 7 ReportRishit JakhariaОценок пока нет

- IRF150 Power Mosfet For PWM RegulationДокумент8 страницIRF150 Power Mosfet For PWM RegulationOjo RojoОценок пока нет

- Datasheet For Irfp240Документ7 страницDatasheet For Irfp240Kandeke DaviesОценок пока нет

- HGTG12N60A4D, HGTP12N60A4D, HGT1S12N60A4DS: 600V, SMPS Series N-Channel IGBT With Anti-Parallel Hyperfast Diode FeaturesДокумент8 страницHGTG12N60A4D, HGTP12N60A4D, HGT1S12N60A4DS: 600V, SMPS Series N-Channel IGBT With Anti-Parallel Hyperfast Diode Featuresiulian_bОценок пока нет

- Datasheet IRF840 MOSFET LabДокумент7 страницDatasheet IRF840 MOSFET LabEdwin FlorezОценок пока нет

- Irf 630Документ7 страницIrf 630ban4444Оценок пока нет

- IRF630, RF1S630SM: 9A, 200V, 0.400 Ohm, N-Channel Power Mosfets FeaturesДокумент8 страницIRF630, RF1S630SM: 9A, 200V, 0.400 Ohm, N-Channel Power Mosfets FeaturesulisesОценок пока нет

- Mosfet: IPP50R380CEДокумент13 страницMosfet: IPP50R380CEFernando GuerreroОценок пока нет

- IRFP360: 23A, 400V, 0.200 Ohm, N-Channel Power Mosfet FeaturesДокумент7 страницIRFP360: 23A, 400V, 0.200 Ohm, N-Channel Power Mosfet FeaturesFran Javi Vila DiazОценок пока нет

- Irf840 MosfetДокумент8 страницIrf840 MosfetGokulnathKuppusamyОценок пока нет

- IRF540N: 33A, 100V, 0.040 Ohm, N-Channel, Power Mosfet Packaging FeaturesДокумент11 страницIRF540N: 33A, 100V, 0.040 Ohm, N-Channel, Power Mosfet Packaging Featureschristianc15Оценок пока нет

- FQP13N50C / FQPF13N50C: N-Channel QFET MosfetДокумент10 страницFQP13N50C / FQPF13N50C: N-Channel QFET MosfetFidel ArroyoОценок пока нет

- Ca3140, Ca3140aДокумент4 страницыCa3140, Ca3140amatias robertОценок пока нет

- 6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999Документ8 страниц6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999rex999Оценок пока нет

- IRF9520Документ7 страницIRF9520Emilio QuijanoОценок пока нет

- Irfz 34 NLДокумент10 страницIrfz 34 NLguerrero_27Оценок пока нет

- Datasheet IRF840 MOSFETДокумент10 страницDatasheet IRF840 MOSFETEdwin FlorezОценок пока нет

- Irfp 064 VДокумент9 страницIrfp 064 VPerrote PerroОценок пока нет

- 5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number 1573.3 Data Sheet June 1999Документ7 страниц5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number 1573.3 Data Sheet June 1999Rathy VadivelkumarОценок пока нет

- IRF510Документ8 страницIRF510aj_oaomvОценок пока нет

- F540NSДокумент10 страницF540NSedgarlibanioОценок пока нет

- Infineon IRFR5305 DataSheet v01 - 01 ENДокумент12 страницInfineon IRFR5305 DataSheet v01 - 01 ENDon BoscoОценок пока нет

- IRFR5305Документ12 страницIRFR5305Tspi RitzelОценок пока нет

- Irfi 3205 Power MosfetДокумент9 страницIrfi 3205 Power MosfetAndy WilsonОценок пока нет

- IRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesДокумент8 страницIRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesCesar AzcargortaОценок пока нет

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОт EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОценок пока нет

- 110 Waveform Generator Projects for the Home ConstructorОт Everand110 Waveform Generator Projects for the Home ConstructorРейтинг: 4 из 5 звезд4/5 (1)

- Human Machine InterfaceДокумент151 страницаHuman Machine InterfaceJuan Luis MerloОценок пока нет

- Lesson 1-7 ArduinoДокумент29 страницLesson 1-7 ArduinoMichelle Pullon100% (2)

- Tutorial PPT LabsДокумент61 страницаTutorial PPT LabsJuan Luis MerloОценок пока нет

- Old Analog Box GuideДокумент12 страницOld Analog Box GuideJuan Luis MerloОценок пока нет

- Carta Polar (10 Círculos)Документ1 страницаCarta Polar (10 Círculos)Juan Luis MerloОценок пока нет

- Identificacion de InstrumentosДокумент9 страницIdentificacion de InstrumentosJuan Luis MerloОценок пока нет

- Papel Grilla (Square Dots)Документ1 страницаPapel Grilla (Square Dots)Juan Luis MerloОценок пока нет

- Infoplc Net TermoparДокумент7 страницInfoplc Net TermoparJohn Jairo Castaño BetancurОценок пока нет

- Programming AT90S2313Документ4 страницыProgramming AT90S2313Juan Luis MerloОценок пока нет

- A 555 Timer IC TutorialДокумент21 страницаA 555 Timer IC TutorialanhtuandsОценок пока нет

- Using Schmitt Triggers PDFДокумент6 страницUsing Schmitt Triggers PDFJuan Luis MerloОценок пока нет

- Cadsoft Eagle PCB Technical Applications Note 3.0Документ8 страницCadsoft Eagle PCB Technical Applications Note 3.0lamushkОценок пока нет

- NE555 Data Sheet PDFДокумент15 страницNE555 Data Sheet PDFJuan Luis MerloОценок пока нет

- MB1010 - Datasheet EZ1Документ2 страницыMB1010 - Datasheet EZ1Paúl Martínez100% (1)

- TTL & CMOS Series (Complete) PDFДокумент22 страницыTTL & CMOS Series (Complete) PDFJuan Luis Merlo100% (1)

- Sensorless Control of 3-Phase Brushless DC Motors (AVR Uc)Документ14 страницSensorless Control of 3-Phase Brushless DC Motors (AVR Uc)Juan Luis MerloОценок пока нет

- AVR Programmer for Uploading CodeДокумент5 страницAVR Programmer for Uploading CodeJuan Luis MerloОценок пока нет

- Stepper Motor ControllerДокумент1 страницаStepper Motor ControllerJuan Luis MerloОценок пока нет

- 16F87x-16F87xA MIGRATIONДокумент4 страницы16F87x-16F87xA MIGRATIONEmilio J. Fernández GarcíaОценок пока нет

- Motor HHH FundamДокумент7 страницMotor HHH FundamKi SeyОценок пока нет

- Cadsoft Eagle PCB Technical Applications Note 3.0Документ8 страницCadsoft Eagle PCB Technical Applications Note 3.0lamushkОценок пока нет

- Eagle 5.4 - User LanguageДокумент132 страницыEagle 5.4 - User LanguageJuan Luis MerloОценок пока нет

- Basic Control TheoryДокумент8 страницBasic Control TheoryJuan Luis Merlo50% (2)

- Brushless DC MotorsДокумент14 страницBrushless DC MotorsNeroGetsu100% (1)

- Hanon Exercises PDFДокумент40 страницHanon Exercises PDFJuan Luis Merlo100% (3)

- IEC 61131-3 - Programming LanguagesДокумент74 страницыIEC 61131-3 - Programming LanguagesJuan Luis Merlo100% (2)

- Cadsoft Eagle PCB Technical Applications Note 3.0Документ8 страницCadsoft Eagle PCB Technical Applications Note 3.0lamushkОценок пока нет

- Exp5 PrelabДокумент3 страницыExp5 PrelabbkiremitciОценок пока нет

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationДокумент4 страницыSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationmigcasterОценок пока нет

- Irl 3705 NДокумент9 страницIrl 3705 NMeunome99Оценок пока нет

- VLSI Technology and Applications - 10B11EC612: Tutorial Sheet - 3Документ1 страницаVLSI Technology and Applications - 10B11EC612: Tutorial Sheet - 3harshit420Оценок пока нет

- MOSFET DC Circuit AnalysisДокумент13 страницMOSFET DC Circuit AnalysisDiana AnggreaniОценок пока нет

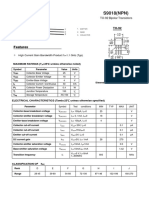

- S9018 (NPN) : FeaturesДокумент2 страницыS9018 (NPN) : Featuresran lanОценок пока нет

- Ferroelectric RAMДокумент7 страницFerroelectric RAMSwayams MishraОценок пока нет

- BJT FundamentalsДокумент33 страницыBJT FundamentalsSamreen ShabbirОценок пока нет

- 00989961Документ3 страницы00989961Satyabrata MahapatraОценок пока нет

- Quanta jm3Документ37 страницQuanta jm3CADASEDAОценок пока нет

- MOS capacitance and delayДокумент6 страницMOS capacitance and delayNaveen KuramОценок пока нет

- Operation of SCRДокумент3 страницыOperation of SCRRB PANGANОценок пока нет

- CT354 Optocoupler DatasheetДокумент10 страницCT354 Optocoupler DatasheetFrame JoshОценок пока нет

- Cmos Latch UpДокумент3 страницыCmos Latch UpSiddharth SabharwalОценок пока нет

- 9N90CДокумент8 страниц9N90CjostranОценок пока нет

- Unit-III Bipolar Junction Transistor PDFДокумент16 страницUnit-III Bipolar Junction Transistor PDFAnonymous 4F6VkOkWОценок пока нет

- Problems For BJT Section: Lecture Notes: Sec. 3Документ9 страницProblems For BJT Section: Lecture Notes: Sec. 3CattОценок пока нет

- SUD40N03-18P: Vishay SiliconixДокумент4 страницыSUD40N03-18P: Vishay SiliconixAlveant JuniorОценок пока нет

- 3 The TTL NAND Gate Full PDFДокумент7 страниц3 The TTL NAND Gate Full PDFMansi AnadiОценок пока нет

- BFG 31Документ7 страницBFG 31kili271828Оценок пока нет

- Eico 685 Operating ManualДокумент29 страницEico 685 Operating ManualkokoromialosОценок пока нет

- 3 Zener DiodeДокумент16 страниц3 Zener DiodeGurudevОценок пока нет

- SQ1440EH Product BundleДокумент19 страницSQ1440EH Product Bundleh_878236333Оценок пока нет

- The MOS Controlled Thyristor (MCT)Документ4 страницыThe MOS Controlled Thyristor (MCT)Debayan SarkarОценок пока нет

- MOSFET CharacteristicsДокумент39 страницMOSFET CharacteristicsvanithapremkumarОценок пока нет

- Bipolar Junction Transistor (BJT) - Construction, Types & Its ApplicationsДокумент1 страницаBipolar Junction Transistor (BJT) - Construction, Types & Its ApplicationszigijuОценок пока нет

- ALLAH The Most Merciful, The Most Beneficent"Документ89 страницALLAH The Most Merciful, The Most Beneficent"api-19788618Оценок пока нет

- bc546 547 548 PDFДокумент3 страницыbc546 547 548 PDFmaheseeeОценок пока нет

- Memory Interfacing With ExampleДокумент6 страницMemory Interfacing With ExampleSachin Jaysenan0% (3)

- Bill of Materials Preamp 2.1Документ2 страницыBill of Materials Preamp 2.1krishnaОценок пока нет