Академический Документы

Профессиональный Документы

Культура Документы

Tda7317 Ecualizador

Загружено:

Rafael Alcazar0 оценок0% нашли этот документ полезным (0 голосов)

70 просмотров13 страницThe TDA7317 is a monolithic, digitally controlled graphic equalizer realized in BiCMOS mixed technology. The stereosignal, beforefiltering, can be attenuated up to -17.625dB in 0.375dB step. All functions can be programmed via serial bus making easy to build a up controlled system.

Исходное описание:

Оригинальное название

TDA7317 ECUALIZADOR

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документThe TDA7317 is a monolithic, digitally controlled graphic equalizer realized in BiCMOS mixed technology. The stereosignal, beforefiltering, can be attenuated up to -17.625dB in 0.375dB step. All functions can be programmed via serial bus making easy to build a up controlled system.

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

70 просмотров13 страницTda7317 Ecualizador

Загружено:

Rafael AlcazarThe TDA7317 is a monolithic, digitally controlled graphic equalizer realized in BiCMOS mixed technology. The stereosignal, beforefiltering, can be attenuated up to -17.625dB in 0.375dB step. All functions can be programmed via serial bus making easy to build a up controlled system.

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 13

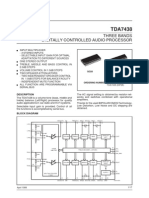

TDA7317

FIVEBANDS DIGITAL CONTROLLEDGRAPHICEQUALIZER

VOLUMECONTROL IN 0.375dBSTEP

FIVE BANDS STEREO GRAPHIC EQUAL-

IZER

CENTER FREQUENCY, BANDWIDTH, MAX

BOOST/CUT DEFINED BY EXTERNAL COM-

PONENTS

14dB CUT/BOOSTCONTROL IN 2dB/STEP

ALL FUNCTIONS PROGRAMMABLE VIA SE-

RIALBUS

VERYLOW DISTORTION

VERY LOW NOISE AND DC STEPPING BY

USE OF A MIXED BIPOLAR/CMOS TECH-

NOLOGY

DESCRIPTION

The TDA7317 is a monolithic, digitally controlled

graphicequalizer realized in BiCMOS mixed technol-

ogy. The stereosignal, beforeanyfiltering, canbe at-

tenuated up to -17.625dB in 0.375dB step.

All the functions can be programmed via serial

bus making easy to build a P controlled system.

Signal path is designedfor very lownoiseanddistor-

tion.

November 1999

SDIP30

ORDERING NUMBER: TDA7317

BLOCK DIAGRAM

1/12

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

S

Supply Voltage 10.2 V

Top Operating Temperature Range -40 to +85 C

T

stg

Storage Temperature Range -55 to +150 C

R

tjvins

Thermal Resistance Junction pins max 85 C/W

PIN CONNECTION

ELECTRICAL CHARACTERISTICS (Tamb = 25C, VS = 9V, RL = 10K, Rg = 600, f = 1KHz VIN =

1Vrms, all controls in flat position (AV = 0dB) unless otherwise specified).

Symbol Parameter Test Condition Min. Typ. Max. Unit

SUPPLY

V

S

Supply Voltage 6 9 10 V

I

S

Supply Current 8 14 20 mA

SVR Ripple Rejection f = 300Hz to 10KHz 60 80 dB

TDA7317

2/12

ELECTRICAL CHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

INPUT

R

I

Input Resistance 20 30 40 K

V

IN max

Max Input Signal THD = 0.3% 2 2.5 V

RMS

I

N S

Input Separation (1) 80 100 dB

VOLUMECONTROL

C

RANGE

Control Range 17.625 dB

A

VMIN

Min. Attenuation -0.5 0 0.5 dB

A

VMAX

Max. Attenuation 16.7 17.625 18.6 dB

A

STEP

Step Resolution 0.175 0.375 0.575 dB

E

A

Attenuation Set Error -1 1 dB

ET Tracking Error 0.5 dB

V

DC

DC Steps adjacent attenuation steps 0 3 mV

GRAPHIC EQUALIZER

THD Distortion 0.01 0.1 %

C

s

Channel Separation 80 100 dB

e

NO

Output Noise BW = 20Hz to 20KHz

flat, AV = 0dB

8 20 V

A curve 6 V

BW = 20Hz to 20KHz AV = 0dB

All bands = max. boost

All bands = max. cut

24

6

V

V

S/N Signal to Noise Ratio A

V

= 0dB; V

ref

= 1V

RMS

100 dB

B

step

Step Resolution 1 2 3 dB

C

RANGE

Control Range max boost/cut 12 14 16 dB

VDC DC Steps Adiacent Control Steps 0.5 3 mV

AUDIO OUTPUTS

V

O

Output Voltage THD = 0.3% 2 2.5 V

RMS

RL Output Load Resistance 2 K

C

L

Output Load Capacitance 10 nF

R

O

Output Resistance 5 10 20

V

OUT

DC Voltage Level 4.2 4.5 4.8 V

BUS INPUTS

V

IL

Input Low Voltage 1 V

V

IH

Input High Voltage 3 V

I

IN

Input Current -5 +5 A

V

O

Output Voltage SDA

Acknowledge

I

O

= 1.6mA 0.4 V

ADDRESS PIN (Internal 50K pull down resistor)

V

IL

Input Low Voltage 1 V

V

IH

Input High Voltage V

CC

-1V V

NOTE: The input is grounded thru the 2.2P capacitors

TDA7317

3/12

DEVICEDESCRIPTION

The TDA7317 is a five bands, digitally controlled

stereo Graphic Equalizer.

The device is intended for high quality audio ap-

plication in Hi-Fi, TV and car radio systems where

feature like low noise and THD are key factors. A

mixed Bipolar Cmos Technologyallows:

Cmos analog switches for pop free commuta-

tions, high frequency op.amp. (GWB = 10MHz)

and high linearity polisilicon resistor for THD =

0.01 (at Vin = 1Vrms) and a S/N ratio of 102dB.

The internal Block Diagramis shown on page 1.

The first stage is a volume control. The control

range is 0 to -17.625dBwith 0.375dBstep.

The very high resolution (0.375dB step) allows

the implementation of closed loop amplitude con-

trol system completely free from any acustical ef-

fect (stepping variation and pumping effect).

The volume control is followed by a serial five

bands equalizer. Each filtering cell is the biquad

cell shown in fig. 1

The internal resistor string is fixing the boost/cut

value while the buffer makes the Q (quality factor)

and central frequency, set by external compo-

nents, fully indipendent fromthe internal resistors.

Each filtering cell is realized using only 4 external

components (2 capacitors and 2 resistors) allow-

ing a flexible selection of centre frequency fo, Q

factor and gain. Here below the basic formulae

and the key features of each band pass filter are

reported:

fo = center frequency

Gv = gain/loss at the center frequency f

o

Gv = 20log(Av)

Q =

f

o

f

2

f

1

where f

2

, f

1

= 3dBBandwidth limits.

Av =

(R2 C2 ) + (R2 C1 ) + (R1 C1 )

(R2 C1 ) + (R2 C2 )

Q =

(R1 C1 R2 C2 )

(R2 C1 ) + (R2 C2 )

fo =

1

2 (R1 R2 C1 C2)

If C1 is fixed, then:

C2 =

Q

2

A

v

1 Q

2

C1

R2 =

1

2 C1 f

o

(A

v

1 ) Q

(A

v

1 Q

2

)

R1 =

(A

v

1)

2

A

v

1 Q

2

R2

Likewise, the componentsvalues can be deter-

mined by fixing one of the other three parameters.

Referring to fig. 1 the suggested R2 value should

be higher than 2K in order to have a good THD

(internal op. amp. current limit).

Viceversa the R1 value should be equal or lower

than 51K in order to keep the click(DC step)

very low.

A typical applicationis shown by fig. 2

Fig. 1

TDA7317

4/12

Figure 2: ApplicationCircuit

The five bands graphic equalizer is used in con-

junction with a TDA7318 (or another audioproces-

sor of the SGS-THOMSON731X family).

The audioprocessor bass and treble tone can fur-

nish twoextra filter bands.

Application requiring higher number of external

equalizer bands could be implemented by cas-

cading 2 or more TDA7317 devices. In fact the

dedicated ADDR pin allows 2 addresses selec-

tion. Anyway, the address of the graphic equalizer

is different fromthe audioprocessor one.

For example 11 bands are implemented by use of

2 TDA7317 plus an audioprocessor (TDA731X

family).

In case one filtering cell is not needed, a short cir-

cuit must be provided between the P1xy and

P2xy pins.

TDA7317

5/12

I

2

C BUS INTERFACE

Data transmission from microprocessor to the

TDA7317 and viceversa takes place thru the 2

wires I

2

C BUS interface, consisting of the two

lines SDA and SCL (pull-up resistors to positive

supply voltage must be externally connected).

Data Validity

As shown in fig. 3, the data on the SDA line must

be stable during the high period of the clock. The

HIGH and LOW state of the data line can only

change when the clock signal on the SCL line is

LOW.

Start and Stop Conditions

As shown in fig.4 a start condition is a HIGH to

LOW transition of the SDA line while SCL is

HIGH. The stop condition is a LOW to HIGH tran-

sition of the SDA line while SCL is HIGH.

Byte Format

Every byte transferred to the SDA line must con-

tain 8 bits. Each byte must be followed by an ac-

knowledge bit. The MSB is transferred first.

Acknowledge

The master (P) puts a resistive HIGH level on the

SDA line during the acknowledge clock pulse (see

fig. 5). The peripheral (audioprocessor) that ac-

knowledges has to pull-down (LOW) the SDA line

during the acknowledge clock pulse, so that the

SDAline is stable LOWduringthis clock pulse.

The audioprocessor which has been addressed

has to generate an acknowledge after the recep-

tion of each byte, otherwise the SDA line remains

at the HIGH level during the ninth clock pulse

time. In this case the master transmitter can gen-

erate the STOP information in order to abort the

transfer.

Transmissionwithout Acknowledge

Avoiding to detect the acknowledge of the audio-

processor, the P can use a simplier transmis-

sion: simply it generates the 9th clock pulse with-

out checking the slave acknowledging, and then

sends the new data.

This approach of course is less protected from

misworking and decreases the noise immunity.

Figure 3: Data Validity on the I

2

CBUS

Figure 4: Timing Diagramof I

2

CBUS

Figure 5: Acknowledge on the I

2

CBUS

TDA7317

6/12

SOFTWARE SPECIFICATION

Interface Protocol

The interface protocol comprises:

A start condition (s)

A chip address byte, containing the TDA7317

address (the 8th bit of the byte must be 0). The

TDA7317 must always acknowledge at the end

of each transmitted byte.

A sequenceof data (N-bytes + acknowledge)

A stop condition (P)

TDA7316 ADDRESS

MSB first byte LSB MSB LSB MSB LSB

S 1 0 0 0 0 1 A 0 ACK DATA ACK DATA ACK P

Data Transferred (N-bytes + Acknowledge)

ACK = Acknowledge

S = Start

P = Stop

MAX CLOCK SPEED100kbits/s

SOFTWARE SPECIFICATION

Chip address (84 or 86 Hex)

1

MSB

0 0 0 0 1 A 0

LSB

A = Logic level on pin ADDR

A = 1 if ADDRpin = open

A = 0 if ADDRpin = connected to ground

SOFTWARE SPECIFICATION (continued)

DATA BYTES(detailed description)

Volume

MSB LSB FUNCTION

0 X B2 B1 B0 A2 A1 A0 Volume 0.375dB steps

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

-0.375

-0.75

-1.125

-1.5

-1.875

-2.25

-2.625

0 X B2 B1 B0 A2 A1 A0 Volume -3dB steps

0

0

0

0

1

1

0

0

1

1

0

0

0

1

0

1

0

1

0

-3

-6

-9

-12

-15

TDA7317

7/12

APPLICATIONINFORMATION

A typical application is indicated in figure 4, while

the P.C. Board and components layout are re-

ported in figure 5. The external components, are

calculated for 2 different max boost/cut conditions

Graphic Equalizer

MSB LSB FUNCTION

1 D3 D2 D1 D0 S2 C1 C0

0

0

0

0

1

0

0

1

1

0

0

1

0

1

0

Band 1

Band 2

Band 3

Band 4

Band 5

D3

D3

D2

D2

D1

D1

1

0

C2

C2

C1

C1

C0

C0

cut

Boost

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0dB

2dB

4dB

6dB

8dB

10dB

12dB

14dB

AX = 0.375dBsteps, BX = 3dB steps, CX = 2dB steps, X = dontcare

STATUS AFTER POWER-ON RESET

Volume -17.25dB

Graphic equalizer bands -12dB

TABLE 1: Max Boost/cut = 20 dB (each cell = 14dB)

F (HZ) Q R1 (K) R2 (K) C1 (nF) C2 (nF) Av max (dB)

BAND 1 10363.38 1.49 47 5.1 0.820 1.2 13.52

BAND 2 261.03 1.49 47 5.1 33 47 13.63

BAND 3 1036.34 1.49 47 5.1 8.2 12 13.52

BAND 4 3168.08 1.49 47 5.1 2.7 3.9 13.57

BAND 5 59.75 1.11 43 7.5 220 100 13.88

For THDperformance the sequence Band 1, 2, 3, 4, 5, is recommended

TABLE2: Max Boost/cut = 17dB (each cell = 12dB)

F (HZ) Q R1 (K) R2 (K) C1 (nF) C2 (nF) Av max (dB)

BAND 1 10158.00 1.15 33 6.2 1.2 1 11.83

BAND 2 250.81 1.21 30 5.1 47 56 11.33

BAND 3 977.34 1.20 39 6.8 10 10 11.75

BAND 4 3429.00 1.25 39 6.2 2.7 3.3 11.67

BAND 5 61.82 1.15 33 6.2 180 180 11.27

TDA7317

8/12

Figure 4

Figure 5: PCP Board and componentslayout of the figure 4 (scale 1:1)

TDA7317

9/12

Measurements done on the test jig of fig. 5 using

the components indicated in table2, are reported

in figg. 6, 7,8.

Figure 6: Frequency Response Figure 7 THDvs Frequency Max Boost/cut =

:14dB

Figure 8: Cross Talk vs Frequency

Purchase of I

2

C Components of SGS-THOMSONMicrolectronics, conveys a license under the Philips

I

2

C Patent Rights to use these components in an I

2

C system, provided that the system conforms to

the I

2

C StandardSpecifications as defined by Philips.

TDA7317

10/12

SDIP30 (0.400)

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 5.08 0.20

A1 0.51 0.020

A2 3.05 3.81 4.57 0.12 0.15 0.18

B 0.36 0.46 0.56 0.014 0.018 0.022

B1 0.76 0.99 1.40 0.030 0.039 0.055

C 0.20 0.25 0.36 0.008 0.01 0.014

D 27.43 27.94 28.45 1.08 1.10 1.12

E 10.16 10.41 11.05 0.400 0.410 0.435

E1 8.38 8.64 9.40 0.330 0.340 0.370

e 1.778 0.070

e1 10.16 0.400

L 2.54 3.30 3.81 0.10 0.13 0.15

M 0(min.), 15(max.)

S 0.31 0.012

OUTLINE AND

MECHANICAL DATA

TDA7317

11/12

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parti es which may result from its use. No li cense is

granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are

subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

1999 STMicroelectronics Printed in Italy All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -

Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

TDA7317

12/12

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

Вам также может понравиться

- Tda 7339Документ12 страницTda 7339Giovanni Carrillo VillegasОценок пока нет

- Tda 7440Документ17 страницTda 7440Albert ThomasОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Tda 7313Документ14 страницTda 7313ClaudiuMaxmiucОценок пока нет

- Tda 7313Документ14 страницTda 7313Ariel NavarreteОценок пока нет

- TDA7440D: Tone Control Digitally Controlled Audio ProcessorДокумент17 страницTDA7440D: Tone Control Digitally Controlled Audio ProcessorJimmy R. Calderon GualeОценок пока нет

- Tda 7438Документ18 страницTda 7438sontuyet82Оценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- Tda 7439Документ17 страницTda 7439Arwana ChipmunksОценок пока нет

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsОт EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsОценок пока нет

- Tda 7449Документ18 страницTda 7449Ariel NavarreteОценок пока нет

- TDA7442Документ16 страницTDA7442gaston30-3@Оценок пока нет

- TDA7442 TDA7442D: Tone Control and Surround Digitally Controlled Audio ProcessorДокумент17 страницTDA7442 TDA7442D: Tone Control and Surround Digitally Controlled Audio ProcessormochuraОценок пока нет

- Tda 7313Документ15 страницTda 7313jordachadiОценок пока нет

- 4-Ch Output Stereo Audio Processor With 4 Stereo Inputs and Tone/Volume ControlДокумент13 страниц4-Ch Output Stereo Audio Processor With 4 Stereo Inputs and Tone/Volume ControlRaúl García LópezОценок пока нет

- Ads 7825Документ21 страницаAds 7825geo888007Оценок пока нет

- 3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LДокумент36 страниц3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858Ljnax101Оценок пока нет

- Hoja de Datos Del TDA 7439Документ20 страницHoja de Datos Del TDA 7439_el_patriarca_Оценок пока нет

- Dvb-S Tuner Max2120Документ21 страницаDvb-S Tuner Max2120Глеб АвдеенкоОценок пока нет

- Ak 5358Документ18 страницAk 5358Alver TuizaОценок пока нет

- Ads 7824Документ21 страницаAds 7824Andres Alberto Meza BrocheroОценок пока нет

- Max 2981Документ13 страницMax 2981Jamila RobinsonОценок пока нет

- +3 Volt, Serial Input Complete 12-Bit DAC AD8300Документ8 страниц+3 Volt, Serial Input Complete 12-Bit DAC AD8300jnax101Оценок пока нет

- mc1377 PDFДокумент18 страницmc1377 PDFAndres CamachoiОценок пока нет

- Tda 7442Документ17 страницTda 7442Ariel NavarreteОценок пока нет

- Tda 7468DДокумент22 страницыTda 7468DJohn Keneth Vasquez100% (1)

- 3 V/5 V, 1 MW 2-/3-Channel 16-Bit, Sigma-Delta Adcs: A MaxДокумент32 страницы3 V/5 V, 1 MW 2-/3-Channel 16-Bit, Sigma-Delta Adcs: A Maxmeroka2000Оценок пока нет

- 3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LДокумент32 страницы3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LJodelCamarinОценок пока нет

- MCP3901Документ62 страницыMCP3901oxobfeОценок пока нет

- 9-0-9 Step Down TransformerДокумент20 страниц9-0-9 Step Down TransformerSarthak JoshiОценок пока нет

- 16-Bit, 100 Ksps/200 Ksps Bicmos A/D Converter: W 10 V, 5 V and 3.3 VДокумент24 страницы16-Bit, 100 Ksps/200 Ksps Bicmos A/D Converter: W 10 V, 5 V and 3.3 Vlongtrandang5867Оценок пока нет

- Microstepping DMOS Driver With Translator: Description Features and BenefitsДокумент18 страницMicrostepping DMOS Driver With Translator: Description Features and BenefitsSaid BoubkerОценок пока нет

- Applications Features: 1988 Burr-Brown Corporation PDS-837E Printed in U.S.A. October, 1997Документ10 страницApplications Features: 1988 Burr-Brown Corporation PDS-837E Printed in U.S.A. October, 1997Arjuna Ajita Ananta VijayaОценок пока нет

- CLC5526 Digital Variable Gain Amplifier (DVGA) : General DescriptionДокумент10 страницCLC5526 Digital Variable Gain Amplifier (DVGA) : General DescriptionVănThịnhОценок пока нет

- Data Sheet: TDA1541AДокумент13 страницData Sheet: TDA1541Afarlocco23Оценок пока нет

- Adc11Dl066 Dual 11-Bit, 66 MSPS, 450 MHZ Input Bandwidth A/D Converter W/Internal ReferenceДокумент24 страницыAdc11Dl066 Dual 11-Bit, 66 MSPS, 450 MHZ Input Bandwidth A/D Converter W/Internal ReferenceVănThịnhОценок пока нет

- Ad 421Документ14 страницAd 421Vishal Devrao JadhavОценок пока нет

- LM1894 Dynamic Noise Reduction System DNR: General DescriptionДокумент10 страницLM1894 Dynamic Noise Reduction System DNR: General DescriptionKoszegi AttilaОценок пока нет

- Tda 7293Документ16 страницTda 7293Gerson FelipeОценок пока нет

- MCP 3201Документ28 страницMCP 3201Nacer MezghicheОценок пока нет

- That1510p PDFДокумент6 страницThat1510p PDFJefferson Gutama ValladaresОценок пока нет

- Ad7524 Ep PDFДокумент8 страницAd7524 Ep PDFjlfepeОценок пока нет

- Instruction Manual MODEL 2017-03A Up/DownconverterДокумент17 страницInstruction Manual MODEL 2017-03A Up/Downconverterch2231Оценок пока нет

- LC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778Документ12 страницLC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778tarpinoОценок пока нет

- Ta 0104 AДокумент18 страницTa 0104 AJump DownОценок пока нет

- AD831-MIXER 200-500MHzДокумент17 страницAD831-MIXER 200-500MHzChelaru CosminОценок пока нет

- PLL Frequency Synthesizer ADF4107: Features General DescriptionДокумент20 страницPLL Frequency Synthesizer ADF4107: Features General DescriptionThanh Son NguyenОценок пока нет

- Ad 7607Документ23 страницыAd 7607Mohanrajan RajendranОценок пока нет

- CB900K e 0203Документ73 страницыCB900K e 0203Vuong NguyenОценок пока нет

- WM9701A Low Power AC'97 Multimedia Audio Codec: Description FeaturesДокумент0 страницWM9701A Low Power AC'97 Multimedia Audio Codec: Description FeaturesJorBS57Оценок пока нет

- Exelente Amplificador de 100w TDA7294Документ17 страницExelente Amplificador de 100w TDA7294Everson CorreaОценок пока нет

- Atf36077 Appl2Документ4 страницыAtf36077 Appl2Johnny TienОценок пока нет

- Income Tax and VATДокумент498 страницIncome Tax and VATshankar k.c.100% (2)

- B. Pengenalan Kepada Pengawal Mikro 1. Mengenali Sistem Yang Berasaskan Pengawal MikroДокумент4 страницыB. Pengenalan Kepada Pengawal Mikro 1. Mengenali Sistem Yang Berasaskan Pengawal MikroSyamsul IsmailОценок пока нет

- Action ResearchДокумент2 страницыAction ResearchGeli BaringОценок пока нет

- William Hallett - BiographyДокумент2 страницыWilliam Hallett - Biographyapi-215611511Оценок пока нет

- SavannahHarbor5R Restoration Plan 11 10 2015Документ119 страницSavannahHarbor5R Restoration Plan 11 10 2015siamak dadashzadeОценок пока нет

- RPH Week 31Документ8 страницRPH Week 31bbwowoОценок пока нет

- Functional Programming in Swift by Eidhof Chris, Kugler Florian, Swierstra Wouter.Документ212 страницFunctional Programming in Swift by Eidhof Chris, Kugler Florian, Swierstra Wouter.angloesamОценок пока нет

- Rishika Reddy Art Integrated ActivityДокумент11 страницRishika Reddy Art Integrated ActivityRishika ReddyОценок пока нет

- Art of War Day TradingДокумент17 страницArt of War Day TradingChrispen MoyoОценок пока нет

- Sermon Manuscript Galatians 5:16-26Документ9 страницSermon Manuscript Galatians 5:16-26Nathaniel ParkerОценок пока нет

- Fire Prevention Plan Template - FINAL 5-30-08Документ5 страницFire Prevention Plan Template - FINAL 5-30-08Peter GeorgeОценок пока нет

- Enzymes IntroДокумент33 страницыEnzymes IntropragyasimsОценок пока нет

- DNA Vs RNA - Introduction and Differences Between DNA and RNAДокумент10 страницDNA Vs RNA - Introduction and Differences Between DNA and RNAKienlevyОценок пока нет

- LEMBAR JAWABAN CH.10 (Capital Budgeting Techniques)Документ4 страницыLEMBAR JAWABAN CH.10 (Capital Budgeting Techniques)Cindy PОценок пока нет

- IOT Architecture IIДокумент29 страницIOT Architecture IIfaisul faryОценок пока нет

- A Literary Nightmare, by Mark Twain (1876)Документ5 страницA Literary Nightmare, by Mark Twain (1876)skanzeniОценок пока нет

- Existentialism in LiteratureДокумент2 страницыExistentialism in LiteratureGirlhappy Romy100% (1)

- Digital Electronics Chapter 5Документ30 страницDigital Electronics Chapter 5Pious TraderОценок пока нет

- GLOBE2Документ7 страницGLOBE2mba departmentОценок пока нет

- Veritas™ High Availability Agent For WebSphere MQ Installation and Configuration Guide / WebSphere MQ InstallationДокумент64 страницыVeritas™ High Availability Agent For WebSphere MQ Installation and Configuration Guide / WebSphere MQ InstallationkarthickmsitОценок пока нет

- SICHEM Brochure 2023Документ8 страницSICHEM Brochure 2023krishnarao badisaОценок пока нет

- Philhis 1blm Group 6 ReportДокумент19 страницPhilhis 1blm Group 6 Reporttaehyung trashОценок пока нет

- The Comma Rules Conversion 15 SlidesДокумент15 страницThe Comma Rules Conversion 15 SlidesToh Choon HongОценок пока нет

- Lesser Known Homoeopathic Medicines of Alopecia Areata.20200718115446Документ9 страницLesser Known Homoeopathic Medicines of Alopecia Areata.20200718115446BruntОценок пока нет

- Xtype Power Train DTC SummariesДокумент53 страницыXtype Power Train DTC Summariescardude45750Оценок пока нет

- Tyler Nugent ResumeДокумент3 страницыTyler Nugent Resumeapi-315563616Оценок пока нет

- Rights of Parents in IslamДокумент11 страницRights of Parents in Islamstoneage989100% (2)

- Paper 1 AnalysisДокумент2 страницыPaper 1 AnalysisNamanОценок пока нет

- Week - 2 Lab - 1 - Part I Lab Aim: Basic Programming Concepts, Python InstallationДокумент13 страницWeek - 2 Lab - 1 - Part I Lab Aim: Basic Programming Concepts, Python InstallationSahil Shah100% (1)

- Preparing For CPHQ .. An Overview of Concepts: Ghada Al-BarakatiДокумент109 страницPreparing For CPHQ .. An Overview of Concepts: Ghada Al-BarakatiBilal SalamehОценок пока нет