Академический Документы

Профессиональный Документы

Культура Документы

Small Signal Discrete Time Modeling of Digitally Controlled PWM Converters (Cited 111)

Загружено:

delianchenИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Small Signal Discrete Time Modeling of Digitally Controlled PWM Converters (Cited 111)

Загружено:

delianchenАвторское право:

Доступные форматы

2552

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 22, NO. 6, NOVEMBER 2007

Small-Signal Discrete-Time Modeling of Digitally Controlled PWM Converters

Dragan Maksimovic, Senior Member, IEEE, and Regan Zane, Senior Member, IEEE

AbstractThe letter presents an exact small-signal discrete-time

model for digitally controlled pulsewidth modulated (PWM) dcdc

converters operating in constant frequency continuous conduction mode (CCM) with a single effective A/D sampling instant

per switching period. The model, which is based on well-known

approaches to discrete-time modeling and the standard -transform, takes into account sampling, modulator effects and delays

in the control loop, and is well suited for direct digital design of

digital compensators. The letter presents general results valid

for any CCM converter with leading or trailing edge PWM.

Specic examples, including approximate closed-form expressions

for control-to-output transfer functions are given for buck and

boost converters. The model is veried in simulation using an

independent system identication approach.

Index TermsDCDC converter, digital control, discrete-time

model, pulsewidth modulation (PWM) converter, small-signal

model.

I. INTRODUCTION

ISCRETE-TIME modeling of dcdc switching converters

has had a long history of contributions, starting from [1].

Effects of sampling due to the pulse-width modulator in the context of averaged small-signal models and standard analog controllers were discussed in [2]. Extensions of discrete-time modeling have included generalizations to various analog control

techniques including constraint modulations [3], [4], as well as

applications to computer-aided modeling and simulations [5],

[6]. Exact continuous-time small-signal converter models have

been developed based on a combination of discrete-time models

and the concept of equivalent hold [7]. Recently, the growing interest in practical digital control for high-frequency dcdc converters has prompted renewed interest in discrete-time analysis

and modeling [8][12] to facilitate direct digital compensator

design. In a digitally controlled constant-frequency pulsewidth

modulated (PWM) converter, an example of which is shown in

Fig. 1(a), the output voltage error is sampled by an A/D converter. A discrete-time compensator computes a duty-cycle control signal for a digital pulse-width modulator (DPWM). Discrete-time models suitable for sampling rates lower than the

switching frequency have been discussed in [8]. Sampling rates

equal to or even exceeding the switching frequency are now

practical, with dynamic performance dependent on control-loop

delays [10][12]. As noted in [10], the previously derived discrete-time models describe the behavior of the control variable

Manuscript received May 10, 2007; revised June 19, 2007. This work was

supported through the Colorado Power Electronics Center. Recommended for

publication by Associate Editor R. Teodorescu.

The authors are with the Colorado Power Electronics Center, Electrical

and Computer Engineering Department, University of Colorado, Boulder, CO

80309-0425 USA (e-mail: maksimov@colorado.edu; zane@colorado.edu).

Color versions of one or more of the gures in this letter are available online

at http://ieeexplore.ieee.org.

Digital Object Identier 10.1109/TPEL.2007.909776

and the converter states at a particular instant during a switching

period (e.g., at a beginning of the switch on-time [3], [4]). Therefore, these models are not directly applicable to digitally controlled converters where the A/D sampling instants can occur

at any time during a switching period. To address this problem,

a frequency-domain approach based on Laplace-domain modulator modeling [13] and the modied -transform has been described in [10]. This approach results in an exact discrete-time

model that correctly takes into account sampling, modulator effects and delays in the digital control loop. However, according

to [10], the approach is straightforwardly applicable only to

buck-type converters.

The purpose of this letter is to show how the well-known discrete-time modeling [1][4] can be extended to take into account the sampling, modulator effects and delays in a digitally

controlled converter. The result is an exact small-signal discrete-time model applicable to any constant-frequency PWM

converter. Section II describes the modeling approach. Model

examples and verication results are presented in Section III.

Conclusions are given in Section IV.

II. DISCRETE-TIME MODELING WITH DIGITAL

CONTROLLER SAMPLING AND DELAYS

Fig. 1(a) shows a dcdc converter (e.g., a buck converter) with

digital voltage-mode control. In the discussion, without loss of

1 is assumed together with

generality, a sensing gain of

a constant-frequency trailing-edge PWM having an equivalent

1. The converter operates in continsaw-tooth amplitude

uous-conduction mode. In each state of the switch (1 or 2), the

converter circuit is linear, time-invariant, with the corresponding

state-space description

(1)

where is the vector of converter states (e.g., inductor current

). We assume the input voltage

and capacitor voltage,

is constant, since the primary interest is in the control-tooutput responses.

The A/D converter samples the output voltage error at the

sampling rate equal to the switching frequency . The error

signal samples are processed by a discrete-time compensator

. The compensator output samples

control the switch

duty cycle via a digital pulse-width modulator (DPWM). This

modulator can be viewed as a D/A converter including a sampleand-hold followed by signal sampling at the modulated edge [2].

It is important to note that there are two samplers in the feedback loop: A/D sampling of the error voltage, and the modulator

sampling. As a result, the system small-signal model does not

include a sample-and-hold. Instead, the relationship between the

small-signal perturbations of the voltage error signal and the

includes a delay between the A/D sampling

duty-cycle

0885-8993/$25.00 2007 IEEE

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 22, NO. 6, NOVEMBER 2007

2553

, the derivation of

is not necessary. We simply proceed with the discrete-time model derivation according to the

waveforms shown in Fig. 1(c). These waveforms are shown for

the specic case of trailing edge modulation and the A/D sam. The small-signal displing in interval 2

crete-time model can be written as

(2)

where the matrix and vector coefcients can be solved by propagating the effect of each perturbation during the converter switch

states according to (1) and Fig. 1(c). Consider rst the effect of

1 of the states. Starting from the A/D

only a perturbation

1 , the perturbation

1 propagates

sampling at

, state 1 for

, and through switch state 2 for

nally state 2 for

. Therefore, the resulting perturbation

after one period

is given by

(3)

where is the steady-state duty ratio. Next, consider only the

in the duty cycle. The initial pereffect of perturbation

occurs at the modulation edge of the

turbation in the states

PWM output signal and can be found from (1) as linear extensions of the previous and next switch states

(4)

are the steady-state states at the PWM sampling

where

. The perturbation

then propagates

instant,

through the system over the remaining part of the switching

. The resulting

period, which is in switch state 2 for

matrix and vector coefcients for the model (2) are given in

and

Table I, where

Fig. 1. (a) Switching dcdc converter with digital voltage-mode control. (b)

Small-signal model of the digitally controlled dcdc converter. (c) Waveforms

illustrating discrete-time model derivation for the digitally controlled dcdc

converter with A/D sampling during interval 2.

(5)

The output state-space equation can be added according to (1)

as follows:

(6)

at

and the modulator sampling at , as shown in

Fig. 1(b), and illustrated by the waveforms in Fig. 1(c). The

total delay in the control loop includes the A/D conversion

time, the computation delay (i.e., the time it takes to compute the

), as well as the modulator delay

duty-cycle control signal

(i.e., the time between the update of

and the switch transition from state 1 to state 2). In the discussion that follows, we assume that the total delay is shorter than the switching period ,

. Inclusion of the delay in the discrete-time model

0

presented here is the key extension compared to the models in

[1][4].

afAs shown in the model of Fig. 1(b), the samples

through the equivalent

fect the converter state perturbations

hold

which models the converter responses between the

samples, leading to exact continuous-time models [7]. Since the

digital control system only operates on the values of the state

variables or the outputs sampled at the A/D sampling instants

is the state-to-output matrix in the subinterval

Note that

when the A/D sampling occurs [interval

in the case of the

timing diagram in Fig. 1(c)]. Finally, the standard -transform

of (2) and (6) gives the desired discrete-time control-to-output

transfer functions.

Although a buck converter is shown in Fig. 1(a), the results

in Table I are valid for any PWM converter that can be dened

by the state-space description in (1). In addition, although the

waveforms in Fig. 1(c) and the discussion above are based on

trailing-edge modulation and A/D sampling in interval 2, extensions to other modulation types or other sampling times are

simple. The results in Table I cover both leading- and trailingedge modulation with A/D sampling in either interval 1 or 2.

All that is required to derive an exact discrete-time model of

a digitally controlled PWM converter in CCM is to dene the

state-space description in the form of (1). Component losses,

2554

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 22, NO. 6, NOVEMBER 2007

TABLE I

DISCRETE-TIME SMALL-SIGNAL MODEL PARAMETERS FOR TRAILING AND LEADING EDGE PWM CONVERTERS IN CCM

input lters and other converter elements can all be accounted

for in the state-space description. The small-signal model is then

obtained from (2) and (6) according to the coefcients in Table I.

Such models can be easily dened in matrix-based tools such as

MATLAB and used for direct digital controller design. Extensions to modeling converters in discontinuous conduction mode

are not difcult.

Examples of direct digital design of proportional, integral,

derivative (PID) and higher-order compensators, as well as experimental verications of digitally controlled converters based

on the discrete-time model presented in this letter have been discussed in [14][16].

III. MODEL EXAMPLE AND VERIFICATION

As an example, consider the buck converter of Fig. 1(a) with

5 H,

25 m ,

5 F,

trailing edge PWM and:

16 m ,

1 ,

10 V,

1 V,

0.2,

1

1 MHz. In the buck converter,

,

,

0,

,

0. The coefcients in (1)

are given by

(7)

(8)

(9)

(10)

Note that only the output voltage

is used in (10) since

the primary interest is in solving the control-to-output voltage

transfer function. Additional outputs could be easily dened

based on the desired transfer function (e.g., inductor current).

The description of (7)(10) can then be used to dene the exact

small-signal model according to (2), (6), and Table I in a software tool such as MATLAB. In addition, approximate closedform expressions can be derived to gain insight into the effects

of system parameters, including the control loop delay .

As an example, in order to simplify the analysis, losses are

neglected except for the dominant effect of the capacitor ESR,

, in (9). Resulting simplied equations for

and

are

given by

(11)

(12)

for

simplify to

. The model (2), (6) and Table I then

(13)

(14)

(15)

(16)

Approximate expansions of the matrix exponentials in (14)

or the alternatives proposed in

and (15), such as

[17], can be employed to obtain an approximate closed-form analytical discrete-time model. Using the approximation

, the standard -transform of (13) and (16) yields the

control-to-output transfer function in closed form

(17)

where the numerator and denominator polynomials in (17) are

shown in Table II. Results are shown for the ideal (no losses)

buck converter and the ideal boost converter with A/D sampling

in interval 1 or in interval 2. Further discussions related to boost

or yback converters with capacitor ESR can be found in [16].

Note in all cases that the zeros of the discrete-time control-tooutput voltage transfer functions depend on the total delay in

the control loop, while the poles are not affected by the delay.

For the nonideal buck converter, it is also interesting to note that

the capacitor ESR does not add another zero. Rather, it just shifts

the zero in the direction opposite to the effect of . Fig. 2 shows

for the buck conthe magnitude and phase responses of

verter with the parameters dened earlier at the nominal

16 m for

0,

0.5 , and

. The delay effects,

which are clearly visible, especially in the phase responses, must

be taken into account in the design of high-performance digital

controllers.

0.5

The model results are also shown in Fig. 3 at

and compared to an independent method of frequency response

identication. The comparison was generated by performing

a switching level time-domain simulation in Simulink and injecting perturbation signals on the steady-state duty cycle for

cross-correlation based system identication, as described in

[18]. The simulation was performed using the buck converter

parameters dened above, a delay element to adjust according

to Fig. 1 (interval 2 sampling) and no quantization in the PWM

or output signal sampling. The samples (dots) obtained through

transient identication are exact matches to the small-signal

model (17), as shown in Fig. 3.

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 22, NO. 6, NOVEMBER 2007

2555

TABLE II

POLYNOMIALS FOR APPROXIMATE BUCK AND BOOST CLOSED-FORM CONTROL-TO-OUTPUT TRANSFER FUNCTIONS (TRAILING EDGE PWM)

G z

R

T t T

Fig. 2. Magnitude and phase responses of

( ) for the digitally-controlled

buck converter example operating at

= 1 MHz,

= 16 m

, for three

= 0, = 0.5 , = .

values of the total delay :

t t

f

t

IV. CONCLUSION

The letter presents an exact small-signal discrete-time model

for digitally controlled dcdc converters. The model, which is

based on well-known approaches to discrete-time modeling and

the standard -transform, takes into account sampling, modulator effects and delays in the control loop. Complete models are

derived that can be used for any leading or trailing edge PWM

converter operating in continuous conduction mode and with a

single A/D sampling instant per switching period. The models

can be used directly in software tools such as MATLAB for

system analysis and direct digital compensator design. Approximate closed-form control-to-output responses are derived for

buck and boost converters, with either trailing-edge or leadingedge PWM, and arbitrary A/D sampling instants. A model example is given for a buck converter to illustrate the effects of

controller delay and the capacitor ESR. The model is veried in

simulation using an independent system identication approach.

G z

Fig. 3. Comparison of model-based

( ) (line) to identication results

=

(dots) for the digitally-controlled buck converter example operating at

1 MHz,

= 0.5 ,

= 16 m

.

T R

REFERENCES

[1] D. J. Packard, Discrete modeling and analysis of switching regulators, Ph.D. dissertation, California Institute of Technology, Pasadena,

Nov. 1976.

[2] A. R. Brown and R. D. Middlebrook, Sampled-data modeling of

switching regulators, in Proc. IEEE Power Electron. Spec. Conf.,

1981, pp. 349369.

[3] G. C. Verghese, M. E. Elbuluk, and J. G. Kassakian, A general approach to sampled-data modeling of power electronic circuits, IEEE

Trans. Power Electron., vol. PE-1, no. 1, pp. 7689, Apr. 1986.

[4] J. G. Kassakian, M. F. Schlecht, and G. C. Verghese, Principles of

Power Electronics. Boston, MA: Addison-Wesley, 1991.

[5] F. C. Lee, R. P. Iwens, Y. Yu, and J. E. Triner, Generalized computer-aided discrete time-domain modeling and analysis of dcdc converters, IEEE Trans. Ind. Electron. Control Inst., vol. IECI-26, no. 2,

pp. 5869, May 1979.

[6] P. Maranesi, Small-signal circuit modeling in the frequency-domain

by computer-aided time-domain simulation, IEEE Trans. Power Electron., vol. PEL-7, no. 1, pp. 8388, Jan. 1992.

[7] B. Y. B. Lau and R. D. Middlebrook, Small-signal frequency response theory for piecewise-constant two-switched-network dc-to-dc

converters, in Proc. IEEE Power Electron. Spec. Conf., 1986, pp.

186200.

2556

[8] F. Huliehel and S. Ben-Yaakov, Low-frequency sampled-data models

of switched mode dcdc converters, IEEE Trans. Power Electron., vol.

6, no. 1, pp. 5561, Jan. 1991.

[9] C. C. Fang and E. H. Abed, Output regulation of dcdc switching

converters using discrete-time integral control, in Proc. Amer. Control

Conf., 1999, vol. 2, pp. 10521056.

[10] D. M. Van den Sype, K. De Gusseme, A. P. M. Van den Bossche, and J.

A. Melkebeek, Small-signal z-domain analysis of digitally controlled

converters, IEEE Trans. Power Electron., vol. 21, no. 2, pp. 470478,

Mar. 2006.

[11] D. Maksimovic and R. Zane, Small-signal discrete-time modeling of

digitally controlled dcdc converters, in Proc. IEEE COMPEL, Troy,

NY, Jul. 2006, pp. 231235.

[12] L. Corradini and P. Matavelli, Analysis of multiple sampling technique for digitally controlled dcdc converters, in Proc. IEEE Power

Electron. Spec. Conf., 2006, pp. 16.

[13] D. M. Van de Sype, K. De Gusseme, A. P. Van den Bossche, and J.

A. Melkebeek, Small-signal Laplace-domain analysis of uniformlysampled pulse-width modulators, in Proc. IEEE Power Electron. Spec.

Conf., 2004, vol. 6, pp. 42924298.

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 22, NO. 6, NOVEMBER 2007

[14] T. Takayama and D. Maksimovic, Digitally controlled 10 MHz monolithic buck converter, in Proc. IEEE COMPEL, Troy, NY, Jul. 2006,

pp. 154158.

[15] H. Hu, V. Yousefzadeh, and D. Maksimovic, Nonlinear control for

improved dynamic response of digitally controlled dcdc converters,

in Proc. IEEE Power Electron. Spec. Conf., 2006, pp. 25842590.

[16] V. Yousefzadeh, M. Shirazi, and D. Maksimovic, Minimum phase response in digitally controlled boost and yback converters, in Proc.

IEEE Appl. Power Electron. Conf., 2007, pp. 865870.

[17] V. Rajasekaran, J. Sun, and B. S. Heck, Biliner discrete-time modeling for enhanced stability prediction and digital control design, IEEE

Trans. Power Electron., vol. 18, no. 1, pp. 381389, Jan. 2003.

[18] B. Miao, R. Zane, and D. Maksimovic, System identication of power

converters with digital control through cross-correlation methods,

IEEE Trans. Power Electron., vol. 20, no. 5, pp. 10931099, Sep.

2005.

Вам также может понравиться

- Small-Signal Discrete-Time Modeling of Digitally Controlled PWM Converters PDFДокумент5 страницSmall-Signal Discrete-Time Modeling of Digitally Controlled PWM Converters PDFYaraОценок пока нет

- Sensorless Current Mode ControlДокумент6 страницSensorless Current Mode Controlsumiths32Оценок пока нет

- Power Systems-On-Chip: Practical Aspects of DesignОт EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardОценок пока нет

- Adv Power ElectronicsДокумент5 страницAdv Power ElectronicsSumon DharaОценок пока нет

- Regular Sampled PWMДокумент11 страницRegular Sampled PWMg.jayakrishnaОценок пока нет

- Small-Signal Modeling of Digitally Controlled Grid-Connected Inverters With FiltersДокумент14 страницSmall-Signal Modeling of Digitally Controlled Grid-Connected Inverters With FiltersTravis GrayОценок пока нет

- A Digital Current-Mode Control Technique For DC-DC ConvertersДокумент21 страницаA Digital Current-Mode Control Technique For DC-DC ConvertersShenbaga LakshmiОценок пока нет

- Buck Boost Converter Small Signal Model Dynamic Analysis Under System Uncertainties PDFДокумент13 страницBuck Boost Converter Small Signal Model Dynamic Analysis Under System Uncertainties PDFTariq KhanОценок пока нет

- Unified Model of PWM Switch Including Inductor in DCM (0074 1Документ2 страницыUnified Model of PWM Switch Including Inductor in DCM (0074 1Jesús MendozaОценок пока нет

- Universal Digital Controller For Boost CCM Power Factor Correction Stages Based On Current Rebuilding ConceptДокумент12 страницUniversal Digital Controller For Boost CCM Power Factor Correction Stages Based On Current Rebuilding ConceptsindhukamitkarОценок пока нет

- Variable Frequency Digital PWM Control For Low-Power Buck ConvertersДокумент5 страницVariable Frequency Digital PWM Control For Low-Power Buck Convertersantonytechno100% (1)

- Techniques UPS: DigitalДокумент6 страницTechniques UPS: DigitalFabian Rodriguez NietoОценок пока нет

- Full Control of A PWM DCAC Converter For AC Voltage RegulationДокумент9 страницFull Control of A PWM DCAC Converter For AC Voltage RegulationAndrés Felipe CelisОценок пока нет

- Continuous-Time Digital Controller For High-Frequency DC-DC ConvertersДокумент26 страницContinuous-Time Digital Controller For High-Frequency DC-DC ConvertersMegreenUnseen DocОценок пока нет

- DSP Based Real Time Implementation of AC-DC-AC Converter Using SPWM TechniqueДокумент18 страницDSP Based Real Time Implementation of AC-DC-AC Converter Using SPWM Techniquebalamurugan041992Оценок пока нет

- PWM-Switch Modeling DC-DC Converters: HermanДокумент7 страницPWM-Switch Modeling DC-DC Converters: HermanChristopher RosaОценок пока нет

- A Novel Scheme For Sliding-Mode Control of DC-DC Converters With A Constant Frequency Based On The Averaging ModelДокумент8 страницA Novel Scheme For Sliding-Mode Control of DC-DC Converters With A Constant Frequency Based On The Averaging ModelMouh SachaОценок пока нет

- A High-Performance Generalized Discontinuous PWM Algorithm: Ahmet M. Hava,, Russel J. Kerkman,, and Thomas A. LipoДокумент13 страницA High-Performance Generalized Discontinuous PWM Algorithm: Ahmet M. Hava,, Russel J. Kerkman,, and Thomas A. LipoSherif M. DabourОценок пока нет

- Family Controller PFCДокумент8 страницFamily Controller PFCWesley de PaulaОценок пока нет

- Simplified SVPWM-DTC of 3-Phase Induction Motor Using The Concept of Imaginary Switching TimesДокумент6 страницSimplified SVPWM-DTC of 3-Phase Induction Motor Using The Concept of Imaginary Switching Timesdjoo77Оценок пока нет

- AC Equivalent Circuit ModelingДокумент65 страницAC Equivalent Circuit Modelinghey_gluppyОценок пока нет

- PSPICE Simulation of Three-Phase Inverters by Means of Swiching Functions (Salazar Joós)Документ8 страницPSPICE Simulation of Three-Phase Inverters by Means of Swiching Functions (Salazar Joós)luism_falconiОценок пока нет

- Modeling of Quantization EffectsДокумент8 страницModeling of Quantization EffectsdelianchenОценок пока нет

- A Simple Digital Power-Factor CorrectionДокумент11 страницA Simple Digital Power-Factor CorrectionVinoth KumarОценок пока нет

- l24 PDFДокумент27 страницl24 PDFAshok KumarОценок пока нет

- SPWM V/HZ InverterДокумент51 страницаSPWM V/HZ InverterLabi BajracharyaОценок пока нет

- C. Buck-Boost Converter Modeling D. Cuk Converter Modeling: Di V DT L TDT Qon DV V DT C RДокумент6 страницC. Buck-Boost Converter Modeling D. Cuk Converter Modeling: Di V DT L TDT Qon DV V DT C RTeja VaitlaОценок пока нет

- Design and Implementation of An Observer Controller For A Buck ConverterДокумент11 страницDesign and Implementation of An Observer Controller For A Buck ConverterLee DonghyeeОценок пока нет

- Extension State Space Averaging Resonant Switches and BeyondДокумент8 страницExtension State Space Averaging Resonant Switches and BeyondMC TimbuОценок пока нет

- Computer Modeling and Simulation of PWM Converter CircuitsДокумент27 страницComputer Modeling and Simulation of PWM Converter CircuitsskrtamilОценок пока нет

- Ridley 1991Документ10 страницRidley 1991mounicapaluru_351524Оценок пока нет

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerДокумент12 страницDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaОценок пока нет

- Digital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveДокумент7 страницDigital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveijsretОценок пока нет

- A Modified Method For Tuning PID Controller For Buck-Boost ConverterДокумент7 страницA Modified Method For Tuning PID Controller For Buck-Boost ConverterIJAERS JOURNALОценок пока нет

- Fully Digital Hysteretic Modulator For DC-DC Switching ConvertersДокумент8 страницFully Digital Hysteretic Modulator For DC-DC Switching ConvertersAnand RamamurthyОценок пока нет

- Ntroduction: Fig.1. Principle Block DiagramДокумент4 страницыNtroduction: Fig.1. Principle Block Diagramanant0008Оценок пока нет

- Predictive CM Trans03Документ37 страницPredictive CM Trans03anonymus_mhОценок пока нет

- Time Domain Based Digital PWM Controller For DC-DC ConverterДокумент12 страницTime Domain Based Digital PWM Controller For DC-DC ConverterTetiHidayatiОценок пока нет

- Practical Feedback Loop Design Considerations For Switched Mode Power SuppliesДокумент14 страницPractical Feedback Loop Design Considerations For Switched Mode Power SuppliesDiego PhillipeОценок пока нет

- Direct Digital Control of Single-Phase AC/DC PWM Converter SystemДокумент10 страницDirect Digital Control of Single-Phase AC/DC PWM Converter SystemPham LongОценок пока нет

- Pulse-Width Modulation PDFДокумент8 страницPulse-Width Modulation PDFSindhuja ThogaruОценок пока нет

- Average and Small-Signal Modeling of Self-Oscillating Flyback Converter With Applied Switching DelayДокумент8 страницAverage and Small-Signal Modeling of Self-Oscillating Flyback Converter With Applied Switching DelayMohamed HaddadОценок пока нет

- A Simple and Ultra-Fast DSP-Based Space Vector PWM Algorithm andДокумент6 страницA Simple and Ultra-Fast DSP-Based Space Vector PWM Algorithm andShiviAroraОценок пока нет

- Lecture 24 Computer Modeling and Simulation of PWM Converter CircuitsДокумент6 страницLecture 24 Computer Modeling and Simulation of PWM Converter Circuitslenovo1986Оценок пока нет

- A New Model Predictive Control Approach To DC-DC Converter Based On Combinatory OptimizationДокумент8 страницA New Model Predictive Control Approach To DC-DC Converter Based On Combinatory OptimizationChaudhry Fahad Ali FastNUОценок пока нет

- An Analysis On Switching Loss Optimized PWM Strategies For Three Phase PWM Voltage Source ConvertersДокумент6 страницAn Analysis On Switching Loss Optimized PWM Strategies For Three Phase PWM Voltage Source ConvertersGanesh ChallaОценок пока нет

- A High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersДокумент4 страницыA High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersJessyОценок пока нет

- Uninterruptible Power Supply Multiloop Control Employing Digital Predictive Voltage and Current RegulatorsДокумент9 страницUninterruptible Power Supply Multiloop Control Employing Digital Predictive Voltage and Current RegulatorsPhạm Văn TưởngОценок пока нет

- DC Link Approach To Variable-Speed, Sensorless,: Induction Motor DriveДокумент5 страницDC Link Approach To Variable-Speed, Sensorless,: Induction Motor DrivesamirmansourОценок пока нет

- A New Switching Strategy For Pulse Width Modulation (PWM) Power ConvertersДокумент8 страницA New Switching Strategy For Pulse Width Modulation (PWM) Power Converterssathish2103Оценок пока нет

- Implementation and Performance Evaluation of DSP-Based Control For Constant-Frequency Discontinuous-Conduction-Mode Boost PFC Front EndДокумент10 страницImplementation and Performance Evaluation of DSP-Based Control For Constant-Frequency Discontinuous-Conduction-Mode Boost PFC Front EndEngr RashidОценок пока нет

- Fast-Predictive Optimal Control of NPC Multilevel ConvertersДокумент9 страницFast-Predictive Optimal Control of NPC Multilevel Converterskanda71Оценок пока нет

- Nonlinear Modeling of DC/DC Converters Using The Hammerstein's ApproachДокумент12 страницNonlinear Modeling of DC/DC Converters Using The Hammerstein's ApproachDipanjan DasОценок пока нет

- Digital Control Methods Sharing Synchronous Converter: For Current of Interleaved Buck AndreassenДокумент7 страницDigital Control Methods Sharing Synchronous Converter: For Current of Interleaved Buck Andreassenrmsharma1970Оценок пока нет

- Research Paper A Novel Method For Near State Pulse Width Modulation (NSPWM) Based Chopper DrivesДокумент4 страницыResearch Paper A Novel Method For Near State Pulse Width Modulation (NSPWM) Based Chopper Drivesdivyamanikandan007Оценок пока нет

- A High-Performance Generalized Discontinuous PWM Algorithm: Ahmet M. Hava,, Russel J. Kerkman,, and Thomas A. LipoДокумент13 страницA High-Performance Generalized Discontinuous PWM Algorithm: Ahmet M. Hava,, Russel J. Kerkman,, and Thomas A. LipoBrahmananda Reddy TeegalaОценок пока нет

- Two-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterДокумент9 страницTwo-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterRaveendhra IitrОценок пока нет

- A New Approach of Dead-Time Compensation For PWM Voltage InvertersДокумент8 страницA New Approach of Dead-Time Compensation For PWM Voltage Invertersshankul.saurabhОценок пока нет

- A New Mathematical Model and Control of A Three-Phase AC-DC Voltage Source ConverterДокумент8 страницA New Mathematical Model and Control of A Three-Phase AC-DC Voltage Source ConverterVenktesh MishraОценок пока нет

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsОт EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsОценок пока нет

- Reflections On Free MarketДокумент394 страницыReflections On Free MarketGRK MurtyОценок пока нет

- Tradingview ShortcutsДокумент2 страницыTradingview Shortcutsrprasannaa2002Оценок пока нет

- QA/QC Checklist - Installation of MDB Panel BoardsДокумент6 страницQA/QC Checklist - Installation of MDB Panel Boardsehtesham100% (1)

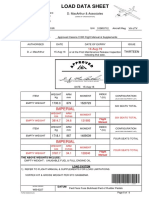

- Load Data Sheet: ImperialДокумент3 страницыLoad Data Sheet: ImperialLaurean Cub BlankОценок пока нет

- Intermediate Accounting (15th Edition) by Donald E. Kieso & Others - 2Документ11 страницIntermediate Accounting (15th Edition) by Donald E. Kieso & Others - 2Jericho PedragosaОценок пока нет

- Lab 6 PicoblazeДокумент6 страницLab 6 PicoblazeMadalin NeaguОценок пока нет

- Ludwig Van Beethoven: Für EliseДокумент4 страницыLudwig Van Beethoven: Für Eliseelio torrezОценок пока нет

- Catalog Celule Siemens 8DJHДокумент80 страницCatalog Celule Siemens 8DJHAlexandru HalauОценок пока нет

- As 60068.5.2-2003 Environmental Testing - Guide To Drafting of Test Methods - Terms and DefinitionsДокумент8 страницAs 60068.5.2-2003 Environmental Testing - Guide To Drafting of Test Methods - Terms and DefinitionsSAI Global - APACОценок пока нет

- Use of EnglishДокумент4 страницыUse of EnglishBelén SalituriОценок пока нет

- Ikea AnalysisДокумент33 страницыIkea AnalysisVinod BridglalsinghОценок пока нет

- PCДокумент4 страницыPCHrithik AryaОценок пока нет

- Epidemiologi DialipidemiaДокумент5 страницEpidemiologi DialipidemianurfitrizuhurhurОценок пока нет

- 06-Apache SparkДокумент75 страниц06-Apache SparkTarike ZewudeОценок пока нет

- Apm p5 Course NotesДокумент267 страницApm p5 Course NotesMusumbulwe Sue MambweОценок пока нет

- Selvan CVДокумент4 страницыSelvan CVsuman_civilОценок пока нет

- PeopleSoft Application Engine Program PDFДокумент17 страницPeopleSoft Application Engine Program PDFSaurabh MehtaОценок пока нет

- Applied-Entrepreneurship PPTДокумент65 страницApplied-Entrepreneurship PPTJanice EscañoОценок пока нет

- Convention On The Rights of Persons With Disabilities: United NationsДокумент13 страницConvention On The Rights of Persons With Disabilities: United NationssofiabloemОценок пока нет

- Engineering Notation 1. 2. 3. 4. 5.: T Solution:fДокумент2 страницыEngineering Notation 1. 2. 3. 4. 5.: T Solution:fJeannie ReguyaОценок пока нет

- Seminar On Despute Resolution & IPR Protection in PRCДокумент4 страницыSeminar On Despute Resolution & IPR Protection in PRCrishi000071985100% (2)

- A320 TakeoffДокумент17 страницA320 Takeoffpp100% (1)

- 18PGHR11 - MDI - Aditya JainДокумент4 страницы18PGHR11 - MDI - Aditya JainSamanway BhowmikОценок пока нет

- Interoperability Standards For Voip Atm Components: Volume 4: RecordingДокумент75 страницInteroperability Standards For Voip Atm Components: Volume 4: RecordingjuananpspОценок пока нет

- Instructions For Microsoft Teams Live Events: Plan and Schedule A Live Event in TeamsДокумент9 страницInstructions For Microsoft Teams Live Events: Plan and Schedule A Live Event in TeamsAnders LaursenОценок пока нет

- The Effectiveness of Risk Management: An Analysis of Project Risk Planning Across Industries and CountriesДокумент13 страницThe Effectiveness of Risk Management: An Analysis of Project Risk Planning Across Industries and Countriesluisbmwm6Оценок пока нет

- Electrical ConnectorsДокумент5 страницElectrical ConnectorsRodrigo SantibañezОценок пока нет

- Functions of Commercial Banks: Primary and Secondary FunctionsДокумент3 страницыFunctions of Commercial Banks: Primary and Secondary FunctionsPavan Kumar SuralaОценок пока нет

- Exp. 5 - Terminal Characteristis and Parallel Operation of Single Phase Transformers.Документ7 страницExp. 5 - Terminal Characteristis and Parallel Operation of Single Phase Transformers.AbhishEk SinghОценок пока нет

- Specialty Arc Fusion Splicer: FSM-100 SeriesДокумент193 страницыSpecialty Arc Fusion Splicer: FSM-100 SeriesSFTB SoundsFromTheBirdsОценок пока нет