Академический Документы

Профессиональный Документы

Культура Документы

CA3059

Загружено:

Luis Miguel BarrenoИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

CA3059

Загружено:

Luis Miguel BarrenoАвторское право:

Доступные форматы

3

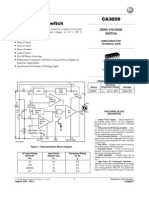

CA3059, CA3079

Zero-Voltage Switches for 50Hz-60Hz and

400Hz Thyristor Control Applications

Description

The CA3059 and CA3079 zero-voltage switches are mono-

lithic silicon integrated circuits designed to control a thyristor

in a variety of AC power switching applications for AC input

voltages of 24V, 120V, 208/230V, and 277V at 50Hz-60Hz

and 400Hz. Each of the zero-voltage switches incorporates

4 functional blocks (see the Functional Block Diagram) as

follows:

1. Limiter-Power Supply - Permits operation directly from an

AC line.

2. Differential On/Off Sensing Amplifier - Tests the condition

of external sensors or command signals. Hysteresis or

proportional-control capability may easily be implement-

ed in this section.

3. Zero-Crossing Detector - Synchronizes the output pulses

of the circuit at the time when the AC cycle is at zero volt-

age point; thereby eliminating radio-frequency interfer-

ence (RFI) when used with resistive loads.

4. Triac Gating Circuit - Provides high-current pulses to the

gate of the power controlling thyristor.

In addition, the CA3059 provides the following important

auxiliary functions (see the Functional Block Diagram).

1. A built-in protection circuit that may be actuated to remove

drive from the triac if the sensor opens or shorts.

2. Thyristor firing may be inhibited through the action of an

internal diode gate connected to Terminal 1.

3. High-power dc comparator operation is provided by over-

riding the action of the zero-crossing detector. This is ac-

complished by connecting Terminal 12 to Terminal 7.

Gate current to the thyristor is continuous when Terminal

13 is positive with respect to Terminal 9.

The CA3059 and CA3079 are supplied in 14 lead dual-in-

line plastic packages.

Features

Relay Control

Valve Control

Synchronous Switching of Flashing Lights

On-Off Motor Switching

Differential Comparator with Self-Contained Power

Supply for Industrial Applications

Photosensitive Control

Power One-Shot Control

Heater Control

Lamp Control

Type Features

CA3059 CA3079

24V, 120V, 208/230V, 277V at 50/60 . . .

or 400Hz Operation

X X

Differential Input . . . . . . . . . . . . . . . . . . X X

Low Balance Input Current (Max) - A. . . 1 2

Built-In Protection Circuit for . . . . . . . .

Opened or Shorted Sensor (Term 14)

X X

Sensor Range (Rx) - k. . . . . . . . . . . . . 2 - 100 2 - 50

DC Mode (Term 12) . . . . . . . . . . . . . . . . X

External Trigger (Term 6) . . . . . . . . . . . X

External Inhibit (Term 1) . . . . . . . . . . . . X

DC Supply Volts (Max) . . . . . . . . . . . . . 14 10

Operating Temperature Range (

o

C) . . . -55 to +125

Ordering Information

PART NUMBER TEMPERATURE PACKAGE

CA3059 -55

o

C to +125

o

C 14 Lead Plastic DIP

CA3079 -55

o

C to +125

o

C 14 Lead Plastic DIP

FN490.5

Oct 1999

Pinouts

CA3059 (PDIP)

TOP VIEW

CA3079 (PDIP)

TOP VIEW

1

2

3

4

5

6

7

14

13

12

11

10

9

8

FAIL-SAFE

SENSE AMP IN

ZCD OVERRIDE

R DRIVER (COM)

SENSE AMP REF

COMMON

R DRIVER V

+

INHIBIT

DC SUPPLY

TRIGGER OUT

AC IN

TRIGGER IN

COMMON

HIGH CURRENT

NEG. TRIGGER

1

2

3

4

5

6

7

14

13

12

11

10

9

8

SENSE AMP IN

R DRIVER (COM)

SENSE AMP REF

COMMON

DO NOT USE

DO NOT USE

R DRIVER V

+

DC SUPPLY

TRIGGER OUT

AC IN

COMMON

HIGH CURRENT

NEG. TRIGGER

DO NOT USE

DO NOT USE

O

B

S

O

L

E

T

E

P

R

O

D

U

C

T

N

O

R

E

C

O

M

M

E

N

D

E

D

R

E

P

L

A

C

E

M

E

N

T

o

u

r T

e

c

h

n

ic

a

l S

u

p

p

o

rt C

e

n

te

r

a

t

1

-8

8

8

-IN

T

E

R

S

IL

o

r

w

w

w

.in

te

rs

il.c

o

m

/ts

c

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2002. All Rights Reserved

4

CA3059, CA3079

Functional Block Diagram

FIGURE 1. SCHEMATIC DIAGRAM OF CA3059 AND CA3079

AC INPUT VOLTAGE (50/60 OR 400Hz)

V AC

INPUT SERIES RESISTOR (R

S

)

k

DISSIPATION RATING FOR R

S

W

24 2 0.5

120 10 2

208/230 20 4

277 25 5

NOTE: Circuitry within shaded areas, not included in CA3079

See chart

IC = Internal connection - DO NOT USE (Terminal restriction applies only to CA3079)

EXTERNAL

INHIBIT

* NTC SENSOR

IC

R

P

R

X

R

S

100F

15V

+

-

9 10 11 6

R

L

CURRENT

BOOST

MT

2

MT

1

IC

IC

INHIBIT

G

* NEGATIVE TEMPERATURE COEFFICIENT

0

CROSSING

DET.

TRIAC

GATING

CIRCUIT

4

3

ON/OFF

SENSING

AMPL.

7

8

13

14

PROTECTION

CIRCUIT

1

2

12

LIMITER 5

AC INPUT

VOLTAGE

POWER

SUPPLY

All resistance values are in

NOTE: Circuitry within shaded areas

not included in CA3079

IC = Internal connection - DO NOT USE (Terminal restriction applies only to

FAIL-SAFE INPUT

TO

COMMON

INHIBIT

INPUT

FOR

EXTERNAL

TRIGGER

COMMON

R

SENSOR

R

P

R

4

10K

R

3

12K

R

7

10K

R

2

27K

13

C

F

100F

15V

COMMON 2

12

1 7 14

10

9

11

8

R

5

9.6K

Q

3

Q

2

Q

4

Q

5

TO

COMMON

R

6

15K

R

9

25

R

8

15

3

4

Q

8

Q

9

Q

7

Q

6

Q

10

D

9

D

8

D

12

D

15

D

10

D

11

R

10

40K

D

7

D

13

D

2

D

1

R

1

5K

5

R

S

AC

LINE

INPUT

6

TO

THYRISTOR

GATE

FOR

INCREASED

GATE DRIVE

IC IC IC

IC

Q

1

D

3

D

6

D

5

D

4

FOR DC MODE

OR 400Hz

OPERATION

5

Specifications CA3059, CA3079

Absolute Maximum Ratings T

A

= +25

o

C Thermal Information

DC Supply Voltage (Between Terminals 2 & 7)

CA3059. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14V

CA3079. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10V

DC Supply Voltage (Between Terminals 2 & 8)

CA3059. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14V

CA3079. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10V

Peak Supply Current (Terminals 5 & 7) . . . . . . . . . . . . . . . . . . . 50mA

Output Pulse Current (Terminal 4) . . . . . . . . . . . . . . . . . . . . . 150mA

Thermal Resistance

JA

PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

o

C/W

Power Dissipation

Up to T

A

= +55

o

C CA3059, CA3079 . . . . . . . . . . . . . . . . . 950mW

Above T

A

= +55

o

C CA3059, CA3079 . . Derate Linearly 10mW/

o

C

Ambient Temperature

Operating. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55

o

C to +125

o

C

Storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -65

o

C to +150

o

C

Lead Temperature (During Soldering) . . . . . . . . . . . . . . . . . +265

o

C

At distance 1/16 1/32 (1.59 0.79) from case

for 10 seconds max

CAUTION: Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Electrical Specifications T

A

= +25

o

C, For all Types, Unless Otherwise Specified. All voltages are measured with respect to

Terminal 7. For Operating at 120V

RMS

, 50-60Hz (AC Line Voltage) (Note 1)

PARAMETERS SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

DC SUPPLY VOLTAGE (Figure 2A, 2B, 2C)

Inhibit Mode At 50/60Hz V

S

R

S

= 8k, I

L

= 0 6.1 6.5 7 V

At 400Hz R

S

= 10k, I

L

= 0 - 6.8 - V

At 50/60Hz R

S

= 5k, I

L

= 0 - 6.4 - V

Pulse Mode At 50/60Hz V

S

R

S

= 8k, I

L

= 0 6 6.4 7 V

At 400Hz R

S

= 10k, I

L

= 0 - 6.7 - V

At 50/60Hz R

S

= 5k, I

L

= 0 - 6.3 - V

Gate Trigger Current (Figures 3, 4A) I

GT

Terminal 4

Terminals 3 and 2 Connected,

V

GT

= 1V

- 105 - mA

PEAK OUTPUT CURRENT (PULSED) (Figures 4, 5)

With Internal Power Supply

Figure 4a, 4b

I

OM

Terminal 4

Terminal 3 open, Gate Trigger

Voltage (V

GT

) = 0

50 84 - mA

Terminals 3 and 2 Connected, Gate

Trigger Voltage (V

GT

) = 0

90 124 - mA

With External Power Supply

Figure 5a, 5b, 5c

I

OM

Terminal 4

Terminal 3 open, V+ = 12V, V

GT

= 0 - 170 - mA

Terminals 3 and 2 Connected,

V+ = 12V, V

GT

= 0

240 - mA

Inhibit Input Ratio (Figure 6) V

9

/V

2

Voltage Ratio of Terminals 9 to 2 0.465 0.485 0.520 -

TOTAL GATE PULSE DURATION (Note 2) (Figure 7A, 7B, 7C, 7D)

For Positive dv/dt 50-60Hz t

P

C

EXT

= 0 70 100 140 s

400Hz C

EXT

= 0, R

EXT

= - 12 - s

For Negative dv/dt 50-60Hz t

N

C

EXT

= 0 70 100 140 s

400Hz C

EXT

= 0, R

EXT

= - 10 - s

PULSE DURATION AFTER ZERO CROSSING (50-60Hz) (Figure 7A)

For Positive dv/dt t

P1

C

EXT

= 0, R

EXT

= - 50 - s

For Negative dv/dt t

N1

- 60 - s

OUTPUT LEAKAGE CURRENT (Figure 8)

Inhibit Mode I

4

- 0.001 10 A

INPUT BIAS CURRENT (Figure 9)

CA3059 I

I

- 220 1000 nA

CA3079 - 220 2000 nA

Common-mode Input Voltage Range V

CMR

Terminals 9 and 13 Connected - 1.5 to

5

- V

6

Specifications CA3059, CA3079

SENSITIVITY (Note 3) (Figures 4(a), 11)

Pulse Mode V

13

Terminal 12 open - 6 - mV

NOTES:

1. The values given in the Electrical Characteristics Chart at 120V also apply for operation at input voltages of 208/230V, and 277V, except

for Pulse Duration. However, the series resistor (R

S

) must have the indicated value, shown in the chart in the Functional Block Diagram,

for the specified input voltage.

2. Pulse Duration in 50Hz applications is approximately 15% longer than shown in Figure 7(b).

3. Required voltage change at Terminal 13 to either turn OFF the triac when ON or turn ON the triac when OFF.

Maximum Voltage Ratings T

A

= +25

o

C

MAXIMUM VOLTAGE RATINGS T

A

= +25

o

C

MAXIMUM

CURRENT

RATINGS

TERM.

NO.

NOTE 3

1 2 3 4

NOTE 1

5

NOTE 3

6 7 8 9 10 11

NOTE 3

12 13

NOTES

2, 3

14

I

IN

mA

I

OUT

mA

1

Note 3

Note 4 Note 4 Note 4 Note 4 15

0

10

-2

Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 10 0.1

2 0

-15

0

-15

2

-14

0

-14

0

Note 5

-14

0

Note 5

-14

0

-14

0

-14

0

-14

Note 4 0

-14

0

-14

150 10

3 0

-15

Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4

4 Note 4 2

-10

Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 0.1 150

5

Note 1

Note 4 7

-7

Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 50 10

6

Note 3

14

0

Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4

7 Note 4 14

0

Note 4 20

0

2.5

-2.5

14

0

6

-6

Note 4 Note 4

8 10

0

Note 4 Note 4 Note 4 Note 4 Note 4 0.1 2

9 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4 Note 4

10 Note 4 Note 4 Note 4 Note 4 Note 4 Note4

11 Note 4 Note 4 Note 4 Note 4 Note4

12

Note 3

Note 4 Note 4 50 50

13 Note 4 Note 4 Note4

14

Note 3

2 2

This chart gives the range of voltages which can be applied to the terminals listed horizontally with respect to the terminals listed vertically.

For example, the voltage range of horizontal Terminal 6 to vertical Terminal 4 is 2V to -10V.

NOTES:

1. Resistance should be inserted between Terminal 5 and external supply or line voltage for limiting current into Terminal 5 to less than

50mA.

2. Resistance should be inserted between Terminal 14 and external supply for limiting current into Terminal 14 to less than 2mA.

3. For the CA3079 indicated terminal is internally connected and, therefore, should not be used.

4. Voltages are not normally applied between these terminals; however, voltages appearing between these terminals are safe, if the spec-

ified voltage limits between all other terminals are not exceeded.

5. For CA3079 (0V to -10V).

Electrical Specifications T

A

= +25

o

C, For all Types, Unless Otherwise Specified. All voltages are measured with respect to

Terminal 7. For Operating at 120V

RMS

, 50-60Hz (AC Line Voltage) (Note 1) (Continued)

PARAMETERS SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

7

CA3059, CA3079

FIGURE 2A. DC SUPPLY VOLTAGE TEST CIRCUIT FOR CA3059

AND CA3079

FIGURE 2B. DC SUPPLY VOLTAGE vs AMBIENT TEMPERA-

TURE FOR CA3059 AND CA3079

FIGURE 2C. DC SUPPLY VOLTAGE vs EXTERNAL LOAD

CURRENT FOR CA3059 AND CA3079

FIGURE 3. GATE TRIGGER CURRENT vs GATE TRIGGER

VOLTAGE FOR CA3059 AND CA3079

FIGURE 4A. PEAK OUTPUT (PULSED) AND GATE TRIGGER

CURRENT WITH INTERNAL POWER SUPPLY

TEST CIRCUIT FOR CA3059 AND CA3079

FIGURE 4B. PEAK OUTPUT CURRENT (PULSED) vs AMBIENT

TEMPERATURE FOR CA3059 AND CA3079

2 13

5

7

PULSE 4.6K

CA3059

CA3079

AC LINE

R

S

8 4 9 10

11

INHIBIT

0.3K

4.6K

I

L

V

S

R

L

100F

EXTERNAL

LOAD

CURRENT

ALL RESISTANCE

VALUES ARE IN

7.00

6.75

6.50

6.25

6.00

5.75

I

N

T

E

R

N

A

L

D

C

S

U

P

P

L

Y

(

V

)

-75 -50 -25 0 25 50 75 100 125

AMBIENT TEMPERATURE (

o

C)

120VRMS, 50/60Hz OPERATION

INPUT RESISTANCE (R

S

) = 10k

NO EXTERNAL LOAD

INHIBIT MODE

PULSE MODE

I

N

T

E

R

N

A

L

D

C

S

U

P

P

L

Y

(

V

)

6.5

6.0

5.5

5.0

4.5

4.0

3.5

0 1 2 3 4 5 6 7 8

EXTERNAL LOAD CURRENT (mA)

120VRMS, 50/60Hz OPERATION

T

A

= +25

o

C

R

S

= 5k

(INHIBIT

MODE)

R

S

= 5k

(PULSE

MODE)

R

S

= 10k

(INHIBIT

MODE)

R

S

= 10k

(PULSE

MODE)

G

A

T

E

T

R

I

G

G

E

R

C

U

R

R

E

N

T

(

m

A

)

0 1 2 3

130

120

110

100

90

80

70

60

50

40

GATE TRIGGER (V)

TERMINAL 3 OPEN

TERMINALS 2 AND 3

CONNECTED

120VRMS, 50/60Hz OPERATION

T

A

= +25

o

C

CA3059

CA3079

9 10 11

5

7

4

2 3 13 8

R

S

10K

AC LINE

OSCILLOSCOPE

WITH

HIGH GAIN

INPUT

V

GT

100F

6K 5K

1

1%

I

OM

(4)

OR

I

GT

(4)

AMBIENT TEMPERATURE (

o

C)

-75 -50 -25 0 25 50 75 100 125

150

125

100

75

50 P

E

A

K

O

U

T

P

U

T

C

U

R

R

E

N

T

,

P

U

L

S

E

D

(

m

A

)

120VRMS, 50/60Hz OPERATION

GATE TRIGGER, V

GT

= 0 (V)

TERMINALS 2 AND 3

CONNECTED

TERMINAL 3 OPEN

175

8

CA3059, CA3079

FIGURE 5A. PEAK OUTPUT CURRENT (PULSED) WITH EXTER-

NAL POWER SUPPLY TEST CIRCUIT FOR CA3059

FIGURE 5B. PEAK OUTPUT CURRENT (PULSED) vs EXTER-

NAL POWER SUPPLY VOLTAGE FOR CA3059

FIGURE 5C. PEAK OUTPUT CURRENT (PULSED) vs AMBIENT

TEMPERATURE FOR CA3059

FIGURE 6(A). INPUT INHIBIT VOLTAGE RATIO TEST CIRCUIT

FOR CA3059 AND CA3079

FIGURE 6B. INPUT INHIBIT VOLTAGE RATIO vs AMBIENT TEM-

PERATURE FOR CA3059 AND CA3079

5

7

CA3059

120VRMS

10K

5

ALL RESISTANCE VALUES ARE IN

3 2

V+

OSCILLOSCOPE

WITH

HIGH GAIN

INPUT

13

4

100F

V

GT

1

1%

8

9

10

11

I

OM(4)

5K 6K

R

S

60Hz

0 5 10 15 20

300

250

200

150

100

50

0

EXTERNAL POWER SUPPLY, V+ (V)

P

E

A

K

O

U

T

P

U

T

,

P

U

L

S

E

D

(

m

A

)

TERMINALS 2 AND 3

CONNECTED

TERMINAL 3 OPEN

120VRMS, 50/60Hz OPERATION

GATE TRIGGER, VGT = 0 (V)

EXTERNAL

V+ = 13V

SUPPLY

3V

3V

5V

5V

8V

10V

8V

12V

13V

10V

12V

120VRMS, 50/60Hz OPERATION

GATE TRIGGER VOLTS (V

GT)

= 0

TERMINALS 2 AND 3 CONNECTED

TERMINAL 3 OPEN

250

200

150

100

50

0

P

E

A

K

O

U

T

P

U

T

,

P

U

L

S

E

D

(

m

A

)

AMBIENT TEMPERATURE (

o

C)

-50 -20 10 40 70 100 130

6

8 14

CA3059

CA3079

5

7

11 10 9

4

13 2

R

1

R

2

100F

120VRMS

60Hz

R

S

10K

ALL RESISTANCE

VALUES IN

0.60

0.55

0.50

0.45

0.40

0.35

0.30

-50 -25 0 25 50 75 100 125

AMBIENT TEMPERATURE (

o

C)

I

N

P

U

T

I

N

H

I

B

I

T

V

O

L

T

A

G

E

R

A

T

I

O

,

V

9

/

V

2

120VRMS, 50/60Hz OPERATION

9

CA3059, CA3079

FIGURE 7A. GATE PULSE DURATION TEST CIRCUIT WITH

ASSOCIATED WAVEFORM FOR CA3059 AND

CA3079

FIGURE 7B. TOTAL GATE PULSE DURATION vs EXTERNAL

CAPACITANCE FOR CA3059 AND CA3079

FIGURE 7C. PULSE DURATION AFTER ZERO CROSSING vs

EXTERNAL CAPACITANCE FOR CA3059 & CA3079

FIGURE 7D. TOTAL GATE PULSE DURATION vs EXTERNAL

RESISTANCE FOR CA3059

FIGURE 8. OUTPUT LEAKAGE CURRENT (INHIBIT MODE) vs

AMBIENT TEMPERATURE FOR CA3059 AND CA3079

FIGURE 9. INPUT BIAS CURRENT TEST CIRCUIT FOR CA3059

AND CA3079

13 12 8 2

6K 5K

100F

4 OSC.

WITH

HIGH

GAIN

INPUT

CA3059

CA3079

5

7

9

10

11

C

(EXT)

R

S

10K

120VRMS

60Hz

R

EXT

- dv/dt

AC LINE

+ dv/dt

GATE

PULSE

0V

t

P

t

P1

t

N1

t

N

NOTE: Circuitry within shaded area not included in CA3079.

All resistance values are in

1M

T

O

T

A

L

G

A

T

E

P

U

L

S

E

D

U

R

A

T

I

O

N

(

s

)

300

200

100

0

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09

EXTERNAL CAPACITANCE (F)

t

P

(POSITIVE dv/dt)

t

N

(NEGATIVE dv/dt)

120VRMS, 50/60Hz OPERATION

T

A

= +25

o

C

P

U

L

S

E

D

U

R

A

T

I

O

N

A

F

T

E

R

Z

E

R

O

C

R

O

S

S

I

N

G

(

s

)

700

600

500

400

300

200

100

0

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

EXTERNAL CAPACITANCE (F)

t

N1

(NEGATIVE dv/dt)

t

P1

(POSITIVE dv/dt)

120VRMS, 50/60Hz OPERATION

T

A

= +25

o

C

EXTERNAL RESISTANCE (k)

T

O

T

A

L

G

A

T

E

P

U

L

S

E

D

U

R

A

T

I

O

N

(

s

)

40

30

20

10

0

10 100

t

P

(POSITIVE dv/dt)

t

N

(NEGATIVE dv/dt)

120VRMS, 50/60Hz OPERATION

T

A

= +25

o

C

O

U

T

P

U

T

L

E

A

K

A

G

E

(

n

A

)

100

10

1

0.1

-80 -60 -40 -20 0 20 40 60 80 100 120 140

AMBIENT TEMPERATURE (

o

C)

120VRMS, 50/60Hz OPERATION

INPUT RESISTANCE (R

S

= 100k

NO EXTERNAL LOAD

CA3059

CA3079

2

7

9 +3V

13

8

I

I

V+ = 6V

10

CA3059, CA3079

FIGURE 10A. FIGURE 10B.

FIGURE 10C. FIGURE 10D.

FIGURE 10. RELATIVE PULSE WIDTH AND LOCATION OF ZERO CROSSING FOR 220V OPERATION FOR CA3059 AND CA3079

FIGURE 11. SENSITIVITY vs AMBIENT TEMPERATURE FOR

CA3059 AND CA3079

FIGURE 12. OPERATING REGIONS FOR BUILT-IN PROTEC-

TION CIRCUIT FOR CA3059

300

200

100

0

0 0.02 0.04 0.06 0.08 0.1

EXTERNAL CAPACITANCE (F)

220VRMS, 50/60Hz OPERATION

INPUT RESISTANCE (R

S

) = 10k

50Hz, t

P

(+ dv/dt)

60Hz, t

P

(+ dv/dt)

50Hz, t

N

(- dv/dt)

60Hz, t

N

(- dv/dt)

T

O

T

A

L

G

A

T

E

P

U

L

S

E

D

U

R

A

T

I

O

N

(

s

)

T

O

T

A

L

G

A

T

E

P

U

L

S

E

D

U

R

A

T

I

O

N

(

s

)

600

400

200

0

0 0.02 0.04 0.06 0.08 0.1

EXTERNAL CAPACITANCE (F)

60Hz, t

N

(- dv/dt) 50Hz, t

N

(- dv/dt)

60Hz, t

P

(+ dv/dt)

50Hz, t

P

(+ dv/dt)

220VRMS, 50/60Hz OPERATION

INPUT RESISTANCE (R

S

) = 20k

T

I

M

E

F

R

O

M

Z

E

R

O

C

R

O

S

S

I

N

G

T

O

E

N

D

O

F

P

U

L

S

E

(

s

)

0 0.02 0.04 0.06 0.08 0.1

600

400

200

0

220VRMS, 50/60Hz OPERATION

INPUT RESISTANCE (R

S

) = 10k

60Hz, t

N1

(- dv/dt)

50Hz, t

N1

(- dv/dt)

60Hz, t

P1

(+ dv/dt)

50Hz, t

P1

(+ dv/dt)

EXTERNAL CAPACITANCE (F)

T

I

M

E

F

R

O

M

Z

E

R

O

C

R

O

S

S

I

N

G

T

O

E

N

D

O

F

P

U

L

S

E

(

s

)

600

400

200

0

0 0.02 0.04 0.06 0.08 0.1

EXTERNAL CAPACITANCE (F)

220VRMS, 50/60Hz OPERATION

INPUT RESISTANCE (R

S

) = 20k

50Hz, t

N1

(- dv/dt)

60Hz, t

N1

(- dv/dt)

50Hz, t

P1

(+ dv/dt)

60Hz, t

P1

(+ dv/dt)

S

E

N

S

I

T

I

V

I

T

Y

,

V

1

3

(

m

V

)

S

E

N

S

O

R

R

E

S

I

S

T

A

N

C

E

,

R

O

N

-

R

O

F

F

(

)

30

20

10

0

-75 -50 -25 0 25 50 75 100 125

AMBIENT TEMPERATURE (

o

C)

18

12

6

0

SENSOR RESISTANCE = 5k

TERMINALS 7 AND 12 CONNECTED

DC GATE CURRENT MODE

(CA3058 & CA3059)

TERMINAL 12 OPEN

PULSED GATE CURRENT MODE

(ALL TYPES)

7

6

5

4

3

2

1

0

T

E

R

M

I

N

A

L

1

4

(

V

)

-50 -25 0 25 50 75

AMBIENT TEMPERATURE (

o

C)

THYRISTOR TURN-OFF

AREA OF NORMAL

OPERATION

AREA OF UNCERTAIN

OPERATION

AREA OF UNCERTAIN

OPERATION

THYRISTOR TURN-OFF

11

CA3059, CA3079

FIGURE 13. LINE-OPERATED ONE-SHOT TIMER FIGURE 14. LINE-OPERATED THYRISTOR CONTROL TIME

DELAY TURN-ON CIRCUIT

FIGURE 15. ON/OFF TEMPERATURE CONTROL CIRCUIT WITH DELAYED TURN-ON

FIGURE 16A. LINE-OPERATED IC TIMER FOR LONG TIME PERIODS

11

5

10

12

6 1

2

6

7

13

9

3

14 +

-

100F

15VDC

OFF ON

C1

R1

4

G

MT

1

MT

2

R

L

120VAC

60Hz

CA3059

t

ON

= 0.67 R

1

C

1

R

1

(max. value allowable) = 1m

10K

2W

11

5

10

12

6 1

2

8

7

14

+

-

100F

15VDC

C1

R1

4

G

MT

1

MT

2

R

L

120VAC

60Hz

CA3059

t

d

= 0.67 R

1

C

1

OFF

ON

9

13

3

10K

2W

CA3079

11

5

10

12

6 1

2

6

7

13

9

3

14 +

-

100F

15VDC

C1

R

P

4

G

MT

1

MT

2

R

L

120VAC

60Hz

CA3059

10K

2W

OFF

ON

R

1

R2

NTC

SENSOR

t

d

= R

T

C

1

R

T

=

R

1

R

2

R

1

+ R

2

10

11

1

2

9

6

11

11

10 16

1 5

2

4

8 3 7

8

1

9

6

10

12

13

8

16

12

14

15

CA3059

RECTIFIER

AND TRIAC

CONTROL

5

4

SWITCHED

LOAD

MT

2

MT

1

T2300B

MAX LOAD = 2.5A

G

1K

7

COS/MOS CD4040A

12-STAGE COUNTER

PULSE GENERATOR

CA3097E THYRISTOR/

TRANSISTOR ARRAY

R

4

10K

R

5

1K

13

SENSOR

100F

- +

C1

R2

68K

R1

R3

100K

R6

2M

R7

5K

IN

V

DD

+

10

K

OUTPUT

RESET

10K

120VAC 5K

2W

Terminal 1 goes High

(Logic 1) after 2048

pulses are applied to

Terminal 10.

NOTE:

For 8 hour delay:

R

1

= 12M

C

1

= 2F

12

CA3059, CA3079

FIGURE 16B. TIMING DIAGRAM FOR FIGURE 16A

FIGURE 17A. PROGRAMMABLE ULTRA-ACCURATE LINE-OPERATED TIMER.

e.g., 8 HRS

1 PULSE/SEC

NIGHT DAY

SENSOR ILLUMINATION

COUNTER RESET

(TERMINAL 11 OF CD4040)

CLOCK PULSES

(TERMINAL 9 OF CA3097E)

COUNTER OUTPUT

(TERMINAL 1 OF CD4040)

TERMINAL 6 OF CA3059 AND

TERMINAL 5 OF CA3097E

TERMINAL 4 OF CA3059

AND POWER IN LOAD

10

2

11

13

14

5

9

4

7

8

1

6

4

16 2 10

7 8 9

15

CA3059

RECTIFIER

PULSE

GENERATOR

TRIAC

CONTROL

11 16

10

8

TRIAC

G

200

C

1

100F

10K

1K

ASTABLE

SW

2

MONOSTABLE

R

L

10K

2W

1K

COS/MOS CD4020A

14-STAGE BINARY

COUNTER

120VAC

60Hz

RESET

SW1

RUN

C

2

0.001

120pps

2

7

H

G

F

E

D

C

B

A

1

+V

DD

( +6.5V)

V

DD

Kd Ka

2

8

2

9

2

10

2

11

2

12

2

13

2

14

a b c d e f g h

V

SS

Kb Kc

OUTPUT

CD4048A

EXPANDABLE

8 INPUT GATE

EXP

PROGRAMMING

INTERCONNECTIONS

T2302B

MAX LOAD = 2.5A

120pps

+V

DD

( +6.5V)

RESET

13

CA3059, CA3079

FIGURE 17B. PROGRAMMING TABLE FOR FIGURE 17(A).

TIME PERIODS (t = 0.5333 s)

1t 2t 4t 8t 16t 32t 64t 128t t

O

CD4020A TERMINALS

a b c d e f g h

CD4048A TERMINALS

A B C D E F G H

C NC NC NC NC NC NC NC 1t

NC C NC NC NC NC NC NC 2t

C C NC NC NC NC NC NC 3t

NC NC C NC NC NC NC NC 4t

C NC C NC NC NC NC NC 5t

NC C C NC NC NC NC NC 6t

C C C NC NC NC NC NC 7t

NC NC NC C NC NC NC NC 8t

C NC NC C NC NC NC NC 9t

NC C NC C NC NC NC NC 10t

C C NC C NC NC NC NC 11t

NC NC C C NC NC NC NC 12t

C NC C C NC NC NC NC 13t

NC C C C NC NC NC NC 14t

C C C C NC NC NC NC 15t

C C C C NC C C NC 111t

NC NC NC NC C C C NC 112t

C NC NC NC C C C NC 113t

C C C C C C C C 255t

NOTES:

1. t

O

= Total time delay = n

1

t + n

2

t + . . . n

n

t.

2. C = Connect. For example, interconnect terminal a of the CD4020A and terminal A of the CD4048A.

3. NC = No Connection. For example, terminal b of the CD4020A open and terminal B of the CD4048A connected to +V

DD

bus.

AC

CA3059

AC IN LOAD (R

L

)

CD4048A

SUPPLY

VOLTAGE

OUTPUT

(PIN 4 AND PIN 6)

OUTPUT

14

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporations quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

CA3059, CA3079

Power Supply Considerations for CA3059 and CA3079

The CA3059 and CA3079 are intended for operation as self-

powered circuits with the power supplied from and AC line

through a dropping resistor. The internal supply is designed

to allow for some current to be drawn by the auxiliary power

circuits. Typical power supply characteristics are given in

Figures 2(b) and 2(c).

Power Supply Considerations for CA3059

The output current available from the internal supply may not

be adequate for higher power applications. In such applica-

tions an external power supply with a higher voltage should

be used with a resulting increase in the output level. (See

Figure 4 for the peak output current characteristics.) When

an external power supply is used, Terminal 5 should be con-

nected to Terminal 7 and the synchronizing voltage applied

to Terminal 12 as illustrated in Figure 5(a).

Operation of Built-In Protection for the CA3059

A special feature of the CA3059 is the inclusion of a protec-

tion circuit which, when connected, removes power from the

load if the sensor either shorts or opens. The protection cir-

cuit is activated by connecting Terminal 14 to Terminal 13 as

shown in the Functional Block Diagram. To assure proper

operation of the protection circuit the following conditions

should be observed:

1. Use the internal supply and limit the external load current

to 2mA with a 5k dropping resistor.

2. Set the value of R

P

and sensor resistance (R

X

) between

2k and 100k.

3. The ratio of R

X

to R

P

, typically, should be greater than

0.33 and less than 3. If either of these ratios is not met

with an unmodified sensor over the entire anticipated

temperature range, then either a series or shunt resistor

must be added to avoid undesired activation of the circuit.

If operation of the protection circuit is desired under condi-

tions other than those specified above, then apply the data

given in Figure 12.

External Inhibit Function for the CA3059

A priority inhibit command may be applied to Terminal 1. The

presence of at least +1.2V at 10A will remove drive from

the thyristor. This required level is compatible with DTL or

T

2

L logic. A logical 1 activates the inhibit function.

DC Gate Current Mode for the CA3059

Connecting Terminals 7 and 12 disables the zero-crossing

detector and permits the flow of gate current on demand

from the differential sensing amplifier. This mode of opera-

tion is useful when comparator operation is desired or when

inductive loads are switched. Care must be exercised to

avoid overloading the internal power supply when operating

in this mode. A sensitive gate thyristor should be used with a

resistor placed between Terminal 4 and the gate in order to

limit the gate current.

Dimensions in parentheses are in millimeters and are derived from

the basic inch dimensions as indicated. Grid gradations are in mils

(10

-3

inch).

The photographs and dimensions represent a chip when it is par of

the wafer. When the wafer is cut into chips, the cleavage angles are

57

o

instead of 90

o

with respect to the face of the chip. Therefore, the

isolated chip is actually 7 mils (0.17mm) larger in both dimensions.

Operating Considerations

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

Вам также может понравиться

- CA3059, CA3079: Description FeaturesДокумент12 страницCA3059, CA3079: Description FeaturesMiltongrimi GrimilОценок пока нет

- CA3140Документ20 страницCA3140Brzata PticaОценок пока нет

- Ca3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesДокумент19 страницCa3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesRicardo Teixeira de AbreuОценок пока нет

- Chip Ca3098eДокумент12 страницChip Ca3098etopogigio240Оценок пока нет

- 000 1 Ca3109Документ20 страниц000 1 Ca3109moongaboongaОценок пока нет

- CA3160Документ19 страницCA3160Brzata PticaОценок пока нет

- Uc 1825Документ17 страницUc 1825RacielMCОценок пока нет

- Semiconductor Technical Data Zero Voltage SwitchДокумент6 страницSemiconductor Technical Data Zero Voltage SwitchMuresan SanduОценок пока нет

- TL 497 AДокумент20 страницTL 497 AJoaoОценок пока нет

- CA3059Документ9 страницCA3059chinametalОценок пока нет

- CA3080, CA3080A: Features DescriptionДокумент11 страницCA3080, CA3080A: Features DescriptionBatos1Оценок пока нет

- Ucc 3818Документ32 страницыUcc 3818jeyachadranaОценок пока нет

- D D D D D D D D D D D D D D D: SN65ALS180, SN75ALS180 Differential Driver and Receiver PairsДокумент21 страницаD D D D D D D D D D D D D D D: SN65ALS180, SN75ALS180 Differential Driver and Receiver PairsjohnysonycumОценок пока нет

- Ca3080, Ca3080A: 2Mhz, Operational Transconductance Amplifier (Ota) FeaturesДокумент11 страницCa3080, Ca3080A: 2Mhz, Operational Transconductance Amplifier (Ota) FeaturesBrzata PticaОценок пока нет

- Uc 3854Документ12 страницUc 3854Leandro CoradiОценок пока нет

- CA3080Документ12 страницCA3080yusufwpОценок пока нет

- LM 2904Документ7 страницLM 2904rmlarangОценок пока нет

- Precision Waveform Generator/Voltage Controlled Oscillator FeaturesДокумент12 страницPrecision Waveform Generator/Voltage Controlled Oscillator FeaturesCharles Tineo0% (1)

- Ca3080, Ca3080A: 2Mhz, Operational Transconductance Amplifier (Ota) FeaturesДокумент11 страницCa3080, Ca3080A: 2Mhz, Operational Transconductance Amplifier (Ota) FeaturesToshang SharmaОценок пока нет

- UC3845ANДокумент15 страницUC3845ANMiloud ChouguiОценок пока нет

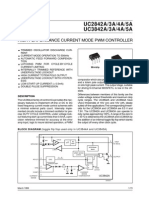

- UC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerДокумент16 страницUC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerCortés BernaОценок пока нет

- STR-A6151 STR-A6159: Universal-Input/13 or 16 W Flyback Switching RegulatorsДокумент7 страницSTR-A6151 STR-A6159: Universal-Input/13 or 16 W Flyback Switching RegulatorsVidal VelasquezОценок пока нет

- 1525AJДокумент7 страниц1525AJSalim BlognetОценок пока нет

- CMOS timing circuit NTE955MCДокумент7 страницCMOS timing circuit NTE955MCManuel ReynosoОценок пока нет

- PWM Module Drv101Документ20 страницPWM Module Drv101DTPHawkОценок пока нет

- STR-A6151 STR-A6159: Universal-Input/13 or 16 W Flyback Switching RegulatorsДокумент7 страницSTR-A6151 STR-A6159: Universal-Input/13 or 16 W Flyback Switching RegulatorsmilebaleОценок пока нет

- Ucc2800 PDFДокумент22 страницыUcc2800 PDFgarrycОценок пока нет

- 4 Ca741 (Harris)Документ5 страниц4 Ca741 (Harris)Ricardo Teixeira de AbreuОценок пока нет

- UC3825ADWДокумент15 страницUC3825ADWmichaelliu123456Оценок пока нет

- Single Ended Active Clamp/Reset PWM: Features DescriptionДокумент16 страницSingle Ended Active Clamp/Reset PWM: Features Descriptioncatsoithahuong84Оценок пока нет

- 8008fa - 72V Regulator PDFДокумент16 страниц8008fa - 72V Regulator PDFKaan GünayОценок пока нет

- Regulating Pulse Width Modulators with Improved PerformanceДокумент7 страницRegulating Pulse Width Modulators with Improved PerformancekkaytugОценок пока нет

- Ca3080 Ca3080a Intersil PDFДокумент11 страницCa3080 Ca3080a Intersil PDFsomtchekusОценок пока нет

- Uc 2526Документ9 страницUc 2526Nguyen HienОценок пока нет

- S Feature D Escriptio: LTC1255 Dual 24V High-Side MOSFET DriverДокумент16 страницS Feature D Escriptio: LTC1255 Dual 24V High-Side MOSFET DriverMuhammed AsimОценок пока нет

- D D D D D D D: MOC3009 THRU MOC3012 Optocouplers/OptoisolatorsДокумент7 страницD D D D D D D: MOC3009 THRU MOC3012 Optocouplers/OptoisolatorsFer TgОценок пока нет

- DatasheetДокумент19 страницDatasheetSwapnica GarreОценок пока нет

- Ca3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesДокумент22 страницыCa3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesfcabreraibanezОценок пока нет

- LT 1248 FDДокумент12 страницLT 1248 FDAtiqurrehman UmairОценок пока нет

- Ca3130, Ca3130aДокумент17 страницCa3130, Ca3130aproctepОценок пока нет

- A5800 and A5801: Discontinued ProductДокумент13 страницA5800 and A5801: Discontinued Productitamar_123Оценок пока нет

- D D D D D D: Description/ordering InformationДокумент13 страницD D D D D D: Description/ordering InformationdsadasdsakdjsakljОценок пока нет

- D D D D D D: Description/ordering InformationДокумент13 страницD D D D D D: Description/ordering Informationno nameejjОценок пока нет

- CA3240Документ16 страницCA3240Jorge NovoaОценок пока нет

- TL 496 DatasheetДокумент7 страницTL 496 DatasheetAnonymous vKD3FG6RkОценок пока нет

- Star Delta Wiring Diagram Motor Start yДокумент16 страницStar Delta Wiring Diagram Motor Start ydataroma100% (1)

- Low Power, 3.3 V, RS-232 Line Drivers/Receivers: F Charge Pump CapacitorsДокумент9 страницLow Power, 3.3 V, RS-232 Line Drivers/Receivers: F Charge Pump Capacitorsdarkinvader2099Оценок пока нет

- DatasheetДокумент7 страницDatasheetjamalludin jamal jamalОценок пока нет

- 12 Volt Smps Circuit DiagramДокумент7 страниц12 Volt Smps Circuit DiagramAnura MaddumageОценок пока нет

- Ca3096 DatasheetДокумент14 страницCa3096 Datasheetexia0012Оценок пока нет

- NCV2931Документ23 страницыNCV2931Vijai PrabhuОценок пока нет

- STR S5707 STR S5708 DatasheetДокумент9 страницSTR S5707 STR S5708 DatasheetJose Gregorio Sanchez Araujo0% (1)

- M/V™ Series Servo Drive: Description Power RangeДокумент11 страницM/V™ Series Servo Drive: Description Power RangeElectromateОценок пока нет

- Uc3842 Monitor Power Supply Regulator IcДокумент7 страницUc3842 Monitor Power Supply Regulator IcJoseph Sidhom SnadaОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorОт Everand110 Waveform Generator Projects for the Home ConstructorРейтинг: 4 из 5 звезд4/5 (1)

- Influence of System Parameters Using Fuse Protection of Regenerative DC DrivesОт EverandInfluence of System Parameters Using Fuse Protection of Regenerative DC DrivesОценок пока нет

- Program Peru 2016 - ENДокумент10 страницProgram Peru 2016 - ENLuis Miguel BarrenoОценок пока нет

- Graph Databases and Neo4J ReportДокумент81 страницаGraph Databases and Neo4J ReportLuis Miguel BarrenoОценок пока нет

- GitHub SuccinctlyДокумент80 страницGitHub Succinctlygandalf92Оценок пока нет

- Sampling and ReconstructionДокумент21 страницаSampling and ReconstructionLuis Miguel BarrenoОценок пока нет

- ATmega Set de InstruccionesДокумент160 страницATmega Set de Instruccionesdav.mova736Оценок пока нет

- PicoBlaze Amplifier and ADC Control Rev2Документ18 страницPicoBlaze Amplifier and ADC Control Rev2Billy Mauricio PinzonОценок пока нет

- Bare Advanced Demo of Ieeetran - Cls For Computer Society JournalsДокумент1 страницаBare Advanced Demo of Ieeetran - Cls For Computer Society JournalsLuis Miguel BarrenoОценок пока нет

- Sheet2 Solution PDFДокумент6 страницSheet2 Solution PDFVarun BishtОценок пока нет

- C 20 EC 3 4 Sem-MinДокумент77 страницC 20 EC 3 4 Sem-MinMallikarjuna KAОценок пока нет

- ICA Assignment ECAДокумент14 страницICA Assignment ECALAKSHMI NARAYANA ANEMIОценок пока нет

- 2 - Operational Amplifier ApplicationДокумент5 страниц2 - Operational Amplifier Applicationtareq omarОценок пока нет

- Operation La Amp EngДокумент20 страницOperation La Amp Engshaligram_2000Оценок пока нет

- OpampДокумент3 страницыOpampJayasree ManoharanОценок пока нет

- BEEIE - Unit 4 & 5 Question BankДокумент7 страницBEEIE - Unit 4 & 5 Question Banksachin barathОценок пока нет

- CHAP 17 - Linear-Digital ICsДокумент30 страницCHAP 17 - Linear-Digital ICsAli Duraz100% (1)

- Lic MCQДокумент148 страницLic MCQnithyasavi67% (9)

- Lec 102409005501 1Документ15 страницLec 102409005501 1Usman Arif100% (1)

- Lmx24-N, Lm2902-N Low-Power, Quad-Operational Amplifiers: 1 Features 3 DescriptionДокумент38 страницLmx24-N, Lm2902-N Low-Power, Quad-Operational Amplifiers: 1 Features 3 DescriptionRoni SocompiОценок пока нет

- Basic Electronics 2014Документ2 страницыBasic Electronics 2014Rajeswari PurushothamОценок пока нет

- KE30501 Lab 1 - Open and Close Loop SystemДокумент24 страницыKE30501 Lab 1 - Open and Close Loop SystemAlvin Tung Kwong ChoongОценок пока нет

- Precision AC-DC Converter LB-8Документ4 страницыPrecision AC-DC Converter LB-8ramad19806824Оценок пока нет

- 1 Problem 1. Sedra Smith Example 2.2Документ15 страниц1 Problem 1. Sedra Smith Example 2.2Entertainment 420Оценок пока нет

- EEEB113 Circuit Analysis I: Operational AmplifiersДокумент39 страницEEEB113 Circuit Analysis I: Operational AmplifiersMuhd RzwanОценок пока нет

- Hand Book of Electronics: January 2010Документ16 страницHand Book of Electronics: January 2010DanyBobОценок пока нет

- Phase Shift Keying: Exp - No:01Документ74 страницыPhase Shift Keying: Exp - No:01Sumit PatilОценок пока нет

- LM358Документ23 страницыLM358Anonymous sIAUueОценок пока нет

- 2 - EE - Intro - Electronics Pg. 28-41 Op Amp-Merged PDFДокумент402 страницы2 - EE - Intro - Electronics Pg. 28-41 Op Amp-Merged PDFAdelin IonutОценок пока нет

- BCT-Syllabus-1st-Year-1st-Part (1) - UnknownДокумент22 страницыBCT-Syllabus-1st-Year-1st-Part (1) - Unknownishanpokhrel16Оценок пока нет

- Lab Manual - Control SystemsДокумент106 страницLab Manual - Control SystemsMuhammad HamzaОценок пока нет

- Analog & Digital Electronics DOTE Text BookДокумент111 страницAnalog & Digital Electronics DOTE Text BookspvigneshОценок пока нет

- Opamp Lab Assign 1Документ9 страницOpamp Lab Assign 1NareshОценок пока нет

- LIC - List of PracticalsДокумент2 страницыLIC - List of PracticalsSamadhan ThokalОценок пока нет

- Graphic Era (Deemed To Be University), Dehradun: Semester I and IiДокумент3 страницыGraphic Era (Deemed To Be University), Dehradun: Semester I and IiTushar SharmaОценок пока нет

- Op Amp Guide Covers Ideal Behavior, CircuitsДокумент16 страницOp Amp Guide Covers Ideal Behavior, CircuitsscribsunilОценок пока нет

- PANJAB UNIVERSITY ELECTRONICS SYLLABUSДокумент59 страницPANJAB UNIVERSITY ELECTRONICS SYLLABUS62kapilОценок пока нет

- Isppac 10: Features Functional Block DiagramДокумент23 страницыIsppac 10: Features Functional Block DiagramFaiber CalderonОценок пока нет

- Presentation Op Amp Till 16.01.2024Документ32 страницыPresentation Op Amp Till 16.01.2024Harsh AgarwalОценок пока нет