Академический Документы

Профессиональный Документы

Культура Документы

Informe Practica N.5

Загружено:

Jose Miguel ChacónАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Informe Practica N.5

Загружено:

Jose Miguel ChacónАвторское право:

Доступные форматы

AMPLIFICADOR MULTIETAPA

Prctica de Laboratorio

Jose Miguel Chacon

Sergio Herrera

Daniel Morales

Ing. Martha Ospina

Universidad Distrital Francisco Jos de Caldas

Facultad de Ingeniera

Ingeniera Electrnica

Electrnica ll

Bogot DC

2014

OBJETIVOS

GENERAL

Disear y verificar el funcionamiento y condiciones de diseo de un

amplificador de dos etapas en cascada.

ESPECIFICOS

Comprobar los resultados analizados para determinar ganancias,

determinacin del punto Q, impedancias, y mximas seales de salida.

Determinar los porcentajes de error de cada amplificador.

Amplificar las seales de entrada por medio de cada configuracin.

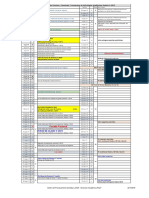

ANALISIS

Diseo de un amplificador de dos etapas emisor comn que permita el

manejo de una seal de salida de 10Vpp sobre una carga de 5K y que

produzca una ganancia total de 50, la mnima frecuencia a amplificar es

100Hz., utilice transistores de parmetros conocidos.

Trabajaremos con transistores BJT 2N2222A con hfe = 200.

Figura 1. Amplificador multietapa en emisor-emisor comn.

Si deseamos una ganancia total de 50, amplificaremos 10 veces la seal en la

primera etapa, y luego la amplificaremos 5 en la segunda, arbitrariamente, de ah

tenemos una seal de entrada:

Diseamos primero la segunda etapa:

Ahora,

[( ) ] ( )

[( )]

[]

Sin condensador en el emisor:

Para esta etapa la ganancia de voltaje es de 5;

Por tanto,

Hallamos resistencia dinmica y esttica:

()

Hallamos I

CQ

e I

BQ;

Hallamos V

BB

,

Hallamos R

B1

y R

B2

, despejando de:

()

Y

()

Y

,

De donde obtenemos:

Sabiendo que

Podemos, entonces suponer la RL del primer amplificador:

Impedancia de entrada del segundo amplificador y resistencia de carga del primero.

( ( )

( ())

Ac

[( ) ] ( )

[( )]

[]

Sin condensador en el emisor:

Para esta etapa la ganancia de voltaje es de 10;

Por tanto,

Hallamos resistencia dinmica y esttica:

()

Hallamos I

CQ

e I

BQ;

Hallamos V

BB

,

Hallamos R

B1

y R

B2

, despejando de:

()

Y

()

Y

,

De donde obtenemos:

Ahora hallamos los condensadores para que amplifique desde 100Hz:

( )

( )

En el primer amplificador:

Para Fl1 igual a la frecuencia baja de corte, tenemos un valor de

Y para Cc2,

Disee un amplificador de dos etapas emisor comn-colector comn que

permitan elevar una seal de 1Vpp a 10Vpp sobre una carga de 200, la

mnima frecuencia a amplificar es 100Hz, utilice transistores de parmetros

conocidos.

La ganancia del amplificador en sus dos etapas es:

Como sabemos que el emisor comn amplifica voltaje, pero el colector produce

una ganancia menos que 1, amplificamos en el emisor comn aproximadamente a

11, que ponemos en la segunda etapa:

Ahora,

[( ) ] ( )

[( )]

[]

Sin condensador en el emisor:

Para esta etapa la ganancia de voltaje es de 11;

Por tanto,

Hallamos resistencia dinmica y esttica:

()

Hallamos I

CQ

e I

BQ;

Hallamos V

BB

,

Hallamos R

B1

y R

B2

, despejando de:

()

Y

()

Y

,

De donde obtenemos:

Ahora hallamos los condensadores para que amplifique desde 100Hz:

( )

( )

En el primer amplificador:

Para Fl1 igual a la frecuencia baja de corte, tenemos un valor de

Y para Cc2,

DESARROLLO

Durante el desarrollo de la prctica de laboratorio se utilizaron los siguientes

instrumentos y/o dispositivos:

Cuatro transistores BJT NPN 2N2222A.

Resistencias de distintos valores.

Condensadores de distintos valores.

Protoboard

Osciloscopio

Multmetro

Generador de seales

Fuente DC

CONCLUSIONES

De esta prctica de laboratorio podemos concluir que podemos utilizar varias

etapas amplificadoras para amplificar seales muy pequeas hasta seales muy

grandes.

Вам также может понравиться

- AcopladoresДокумент83 страницыAcopladoresJose Miguel ChacónОценок пока нет

- Taller Unidades SolДокумент4 страницыTaller Unidades SolJose Miguel ChacónОценок пока нет

- Laboratorio Telecomunicaciones 2016-1 Universidad DistritalДокумент56 страницLaboratorio Telecomunicaciones 2016-1 Universidad DistritalJose Miguel ChacónОценок пока нет

- Proyecto Final Electrónica de PotenciaДокумент3 страницыProyecto Final Electrónica de PotenciaJose Miguel Chacón100% (1)

- PEI Del Colegio Eugenio Diaz CastroДокумент100 страницPEI Del Colegio Eugenio Diaz CastroJose Miguel Chacón0% (1)

- Syllabus Analisis de Fourier WaveletsДокумент10 страницSyllabus Analisis de Fourier WaveletsJose Miguel ChacónОценок пока нет

- Amplificadores RFДокумент55 страницAmplificadores RFJose Miguel ChacónОценок пока нет

- Ejercicios de Control AnalogicoДокумент3 страницыEjercicios de Control AnalogicoJose Miguel ChacónОценок пока нет

- Laboratorio 1 Circuitos TrifaasicosДокумент43 страницыLaboratorio 1 Circuitos TrifaasicosJose Miguel ChacónОценок пока нет

- Registro de StakeHoldersДокумент3 страницыRegistro de StakeHoldersJose Miguel ChacónОценок пока нет

- CIRCUITOSRESISTIVOSCorrecciònДокумент22 страницыCIRCUITOSRESISTIVOSCorrecciònJose Miguel ChacónОценок пока нет

- Chapter 02Документ82 страницыChapter 02jesus bastardoОценок пока нет

- Ecuaciones Diferenciales 2010-IIIДокумент1 страницаEcuaciones Diferenciales 2010-IIIJose Miguel ChacónОценок пока нет

- Python Introduccion A Buenas Practicas de Programacion-83Документ20 страницPython Introduccion A Buenas Practicas de Programacion-83Reuben Junoir Mza AdrianoОценок пока нет

- Caso Cabecitas Locas SLДокумент3 страницыCaso Cabecitas Locas SLJovanny Suazo0% (1)

- Minitab-Exp-Sesion 4-Ejemplo 2Документ6 страницMinitab-Exp-Sesion 4-Ejemplo 2John ArceОценок пока нет

- Cataro 2.4-5 GHZ Dual Band Wifi-OkДокумент3 страницыCataro 2.4-5 GHZ Dual Band Wifi-OkRodsonLarijoОценок пока нет

- Gestion Del Talento HumanoДокумент23 страницыGestion Del Talento HumanoJorgeBenitesPeredaОценок пока нет

- Tarea de Analisis IIДокумент19 страницTarea de Analisis IIAlex Pineda Tinoco100% (1)

- Ti-630i EsДокумент73 страницыTi-630i EsEmmanuel CarrilloОценок пока нет

- 070425medidor Elect. A1100Документ2 страницы070425medidor Elect. A1100Luis LizarragaОценок пока нет

- Practica Nº3 MatlabДокумент8 страницPractica Nº3 MatlabFelipe MadariagaОценок пока нет

- Manual MJX F45 Español PDFДокумент16 страницManual MJX F45 Español PDFRuizma22100% (1)

- 28 Guia No. 28 Interp - de Los Indi. de GestionДокумент13 страниц28 Guia No. 28 Interp - de Los Indi. de GestionKroixJohanОценок пока нет

- Hytera PT580H Plus TETRA Portable Terminal - Español - Manual de Mantenimiento AvanzadoДокумент11 страницHytera PT580H Plus TETRA Portable Terminal - Español - Manual de Mantenimiento AvanzadoAntonio Chavez MirandaОценок пока нет

- IS3 1 Metodologia-Proyectos 2023 PDFДокумент8 страницIS3 1 Metodologia-Proyectos 2023 PDFClaudia Carolina Arguello MorenoОценок пока нет

- Catálogo DigitalДокумент11 страницCatálogo DigitalSimon MartinezОценок пока нет

- Minfra-Mn-In-15-Fr-3 Resumen Mensual Estado Gral ProyДокумент2 страницыMinfra-Mn-In-15-Fr-3 Resumen Mensual Estado Gral ProyluisОценок пока нет

- Manual de Usuario CworkplusaДокумент248 страницManual de Usuario CworkplusaGiraldo RamirezОценок пока нет

- Guia Rapida Canon EOS 100DДокумент2 страницыGuia Rapida Canon EOS 100DAgapito79Оценок пока нет

- Especificaciones TecnicasДокумент7 страницEspecificaciones TecnicasVictor Valdebenito CartesОценок пока нет

- Central de Detección de Incendios D7024Документ16 страницCentral de Detección de Incendios D7024GerardoDemarcoОценок пока нет

- Tema 10. Numeros Internacionales NormalizadosДокумент21 страницаTema 10. Numeros Internacionales NormalizadosPAKI MARTINEZ PEÑARROCHAОценок пока нет

- En Contra de La Inteligencia ArtificialДокумент2 страницыEn Contra de La Inteligencia ArtificialNatalia GonzalezОценок пока нет

- Procuraduria Certificado PDFДокумент1 страницаProcuraduria Certificado PDFAmalfi EugeniaОценок пока нет

- Laboratorio MicroondasДокумент14 страницLaboratorio MicroondasDaniel CamiloОценок пока нет

- Recomendaciones para La Elaboración de Un Mapa ConceptualДокумент4 страницыRecomendaciones para La Elaboración de Un Mapa ConceptualSilEspnОценок пока нет

- Cronograma Gestion 2019-2 Ok PDFДокумент1 страницаCronograma Gestion 2019-2 Ok PDFSergio Choque lopezОценок пока нет

- Taller U3-SIG Erika J Cano AmayaДокумент5 страницTaller U3-SIG Erika J Cano AmayaErika J CanoОценок пока нет

- Examen U5 PDFДокумент3 страницыExamen U5 PDFJose Luis Perez SantillanОценок пока нет

- Estructura en C++Документ15 страницEstructura en C++William Marin AlvaradoОценок пока нет

- Informe Empresa Mundo MueblesДокумент36 страницInforme Empresa Mundo MueblesKatherine PinedaОценок пока нет

- Procedimientos GraficosДокумент27 страницProcedimientos GraficosCristian ErazoОценок пока нет