Академический Документы

Профессиональный Документы

Культура Документы

PIE Level

Загружено:

Vivek AnnepuИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

PIE Level

Загружено:

Vivek AnnepuАвторское право:

Доступные форматы

PIE Level

The PIE block multiplexes eight peripheral and external pin interrupts into one CPU interrupt. These

interrupts are divided into 12 groups: PIE group 1 - PIE group 12. The interrupts within a group are

multiplexed into one CPU interrupt. For example, PIE group 1 is multiplexed into CPU interrupt 1

(INT1) while PIE group 12 is multiplexed into CPU interrupt 12 (INT12). Interrupt sources connected to

the remaining CPU interrupts are not multiplexed. For the nonmultiplexed interrupts, the PIE passes

the request directly to the CPU.

For multiplexed interrupt sources, each interrupt group in the PIE block has an associated flag register

(PIEIFRx) and enable (PIEIERx) register (x = PIE group 1 - PIE group 12). Each bit, referred to as y,

corresponds to one of the 8 MUXed interrupts within the group. Thus PIEIFRx.y and PIEIERx.y

correspond to interrupt y (y = 1-8) in PIE group x (x = 1-12). In addition, there is one acknowledge bit

(PIEACK) for every PIE interrupt group referred to as PIEACKx (x = 1-12). Figure 79 illustrates the

behavior of the PIE hardware under various PIEIFR and PIEIER register conditions.

Once the request is made to the PIE controller, the corresponding PIE interrupt flag (PIEIFRx.y) bit is

set. If the PIE interrupt enable (PIEIERx.y) bit is also set for the given interrupt then the PIE checks the

corresponding PIEACKx bit to determine if the CPU is ready for an interrupt from that group. If the

PIEACKx bit is clear for that group, then the PIE sends the interrupt request to the CPU. If PIEACKx is

set, then the PIE waits until it is cleared to send the request for INTx. See Section 6.3 for details.

CPU Level

Once the request is sent to the CPU, the CPU level interrupt flag (IFR) bit corresponding to INTx is set.After a flag

has been latched in the IFR, the corresponding interrupt is not serviced until it isappropriately enabled in the CPU

interrupt enable (IER) register or the debug interrupt enable register (DBGIER) and the global interrupt mask

(INTM) bit.

Step 1. Any peripheral or external interrupt within the PIE group generates an interrupt. If interrupts

are enabled within the peripheral module then the interrupt request is sent to the PIE module.

Step 2. The PIE module recognizes that interrupt y within PIE group x (INTx.y) has asserted an

interrupt and the appropriate PIE interrupt flag bit is latched: PIEIFRx.y = 1.

Step 3. For the interrupt request to be sent from the PIE to the CPU, both of the following conditions

must be true:

(a) The proper enable bit must be set (PIEIERx.y = 1) and

(b) The PIEACKx bit for the group must be clear.

Step 4. If both conditions in 3a and 3b are true, then an interrupt request is sent to the CPU and the

acknowledge bit is again set (PIEACKx = 1). The PIEACKx bit will remain set until you clear it

to indicate that additional interrupts from the group can be sent from the PIE to the CPU.

Step 5. The CPU interrupt flag bit is set (CPU IFRx = 1) to indicate a pending interrupt x at the CPU

level.

Step 6. If the CPU interrupt is enabled (CPU IER bit x = 1, or DBGIER bit x = 1) AND the global

interrupt mask is clear (INTM = 0) then the CPU will service the INTx.

Step 7. The CPU recognizes the interrupt and performs the automatic context save, clears the IER

bit, sets INTM, and clears EALLOW. All of the steps that the CPU takes in order to prepare to

service the interrupt are documented in the TM S320C28x DSP CPU and Instruction Set

Reference Guide (literature number SPRU430).

Step 8. The CPU will then request the appropriate vector from the PIE.

Step 9. For multiplexed interrupts, the PIE module uses the current value in the PIEIERx and

PIEIFRx registers to decode which vector address should be used. There are two possible

cases:

(a) The vector for the highest priority interrupt within the group that is both enabled in the

PIEIERx register, and flagged as pending in the PIEIFRx is fetched and used as the

branch address. In this manner if an even higher priority enabled interrupt was flagged

after Step 7, it will be serviced first.

(b) If no flagged interrupts within the group are enabled, then the PIE will respond with the

vector for the highest priority interrupt within that group. That is the branch address used

for INTx.1. This behavior corresponds to the 28x TRAP or INT instructions

IQ MATH

EPWM

Time-base (TB):

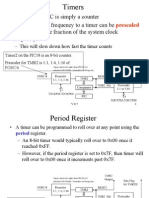

Scale the time-base clock (TBCLK) relative to the system clock (SYSCLKOUT).

Configure the PWM time-base counter (TBCTR) frequency or period.

Set the mode for the time-base counter:

count-up mode: used for asymmetric PWM

count-down mode: used for asymmetric PWM

count-up-and-down mode: used for symmetric PWM

Configure the time-base phase relative to another ePWM module.

Synchronize the time-base counter between modules through hardware or software.

Configure the direction (up or down) of the time-base counter after a synchronization event.

Configure how the time-base counter will behave when the device is halted by an emulator.

Specify the source for the synchronization output of the ePWM module:

Synchronization input signal

Time-base counter equal to zero

Time-base counter equal to counter-compare B (CMPB)

No output synchronization signal generated.

2. Counter-compare (CC):

Specify the PWM duty cycle for output EPWMxA and/or output EPWMxB

Specify the time at which switching events occur on the EPWMxA or EPWMxB output

Action-qualifier (AQ) Specify the type of action taken when a time-base or counter-compare submodule event

occurs:

No action taken

Output EPWMxA and/or EPWMxB switched high

Output EPWMxA and/or EPWMxB switched low

Output EPWMxA and/or EPWMxB toggled

Force the PWM output state through software control

Configure and control the PWM dead-band through software

Dead-band (DB) Control of traditional complementary dead-band relationship between upper and lower switches

Specify the output rising-edge-delay value

Specify the output falling-edge delay value

Bypass the dead-band module entirely. In this case the PWM waveform is passed through

without modification.

PWM-chopper (PC) Create a chopping (carrier) frequency.

Pulse width of the first pulse in the chopped pulse train.

Duty cycle of the second and subsequent pulses.

Bypass the PWM-chopper module entirely. In this case the PWM waveform is passed through

without modification.

Trip-zone (TZ)

Configure the ePWM module to react to one, all, or none of the trip-zone pins.

Specify the tripping action taken when a fault occurs:

Force EPWMxA and/or EPWMxB high

Force EPWMxA and/or EPWMxB low

Force EPWMxA and/or EPWMxB to a high-impedance state

Configure EPWMxA and/or EPWMxB to ignore any trip condition.

Configure how often the ePWM will react to each trip-zone pins:

One-shot

Cycle-by-cycle

Enable the trip-zone to initiate an interrupt.

Bypass the trip-zone module entirely.

Event-trigger (ET)

Enable the ePWM events that will trigger an interrupt.

Enable ePWM events that will trigger an ADC start-of-conversion event.

Specify the rate at which events cause triggers (every occurrence or every second or third

occurrence)

Poll, set, or clear event flags

2.2 Time-Base (TB) Submodule:

Another unique feature of the F2833x is its shadow functionality of operating registers, in the case of ePWM units available for compare

register A, B and period register. For some applications it is necessary to modify the values inside a compare or period register, every period.

The advantage of the background registers is that we can prepare the values for the next period in the current one. Without a background

function we would have to wait for the end of the current period, and then trigger a high prioritized interrupt. Sometimes this form of scheduling

will miss its deadline

ePWM Phase Synchronisation

Two hardware signals "SYNCI" (synch in) and "SYNCO" (synch out) can be used to synchronize ePWM

units to each other. For example, we could define one ePWM unit as a "master" to generate an output signal

"SYNCO" each time the counter equals period. Two more ePWM units could be initialized to recognize this

signal as "SYNCI" and start immediately counting, each time they receive this signal. In such way we have

established a synchronous set of 3 ePWM channels. But we can do even better. By using another register

called "TBPHS" we can introduce a phase shift between master, slave 1 and slave 2, an absolute necessity

for three-phase control systems.

Slide 7-4 shows such an example, where register TBCNT of ePWM2 and ePWM3 are preloaded with a start value that corresponds to 120 and 240

respectively. In this example ePWM1 has been initialized as master to generate SYNCO each time the counter register equals zero. With the enabled

phase input feature for ePWM2 and ePWM3 the two channels operate as slave 1 and slave 2 and will load their counter registers TBCNT with

numbers stored in the corresponding phase registers TBPHS.

Example:

ePWM1 counts from 0 to 6000. TBPRD = 6000

ePWM2 register TBPHS = 2000

ePWM3 register TBPHS = 4000

Here we can put any value clkdiv and hspclkdiv such that prd max value should not be exceeded..

EPwm1Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 2

EPwm1Regs.TBCTL.bit.CTRMODE = 2; // up - down mode

EPwm1Regs.AQCTLA.all = 0x0006; // ZRO = set, PRD = clear

EPwm1Regs.TBPRD = 37500; // 1KHz - PWM signal

EPwm1Regs.TBCTL.bit.SYNCOSEL = 1;

EPwm2Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1

EPwm2Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 2

EPwm2Regs.TBCTL.bit.CTRMODE = 2; // up - down mode

EPwm2Regs.AQCTLA.all = 0x0006; // ZRO = set, PRD = clear

EPwm2Regs.TBPRD = 37500; // 1KHz - PWM signal

EPwm2Regs.TBCTL.bit.PHSEN = 1;

EPwm2Regs.TBCTL.bit.SYNCOSEL = 0;

EPwm2Regs.TBPHS.half.TBPHS = 12500;

EPwm3Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1

EPwm3Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 2

EPwm3Regs.TBCTL.bit.CTRMODE = 2; // up - down mode

EPwm3Regs.AQCTLA.all = 0x0006; // ZRO = set, PRD = clear

EPwm3Regs.TBPRD = 37500; // 1KHz - PWM signal

EPwm3Regs.TBCTL.bit.PHSEN = 1;

EPwm2Regs.TBPHS.half.TBPHS = 25000;

2.3 Counter-Compare (CC) Submodule

The counter-compare submodule takes as input the time-base counter value. This value is continuously

compared to the counter-compare A (CMPA) and counter-compare B (CMPB) registers. When the

time-base counter is equal to one of the compare registers, the counter-compare unit generates an

appropriate event.

The counter-compare:

Generates events based on programmable time stamps using the CMPA and CMPB registers

CTR = CMPA: Time-base counter equals counter-compare A register (TBCTR = CMPA).

CTR = CMPB: Time-base counter equals counter-compare B register (TBCTR = CMPB)

Controls the PWM duty cycle if the action-qualifier submodule is configured appropriately

Shadows new compare values to prevent corruption or glitches during the active PWM cycle

Action-Qualifier (AQ) Submodule:

The action-qualifier submodule is responsible for the following:

Qualifying and generating actions (set, clear, toggle) based on the following events:

CTR = PRD: Time-base counter equal to the period (TBCTR = TBPRD).

CTR = Zero: Time-base counter equal to zero (TBCTR = 0x0000)

CTR = CMPA: Time-base counter equal to the counter-compare A register (TBCTR = CMPA)

CTR = CMPB: Time-base counter equal to the counter-compare B register (TBCTR = CMPB)

Managing priority when these events occur concurrently

Providing independent control of events when the time-base counter is increasing and when it is

decreasing. .

The action-qualifier submodule controls how the two outputs EPWMxA and EPWMxB behave when a

particular event occurs. The event inputs to the action-qualifier submodule are further qualified by the

counter direction (up or down). This allows for independent action on outputs on both the count-up

and

count-down phases.

The possible actions imposed on outputs EPWMxA and EPWMxB are:

Set High:

Set output EPWMxA or EPWMxB to a high level.

Clear Low:

Set output EPWMxA or EPWMxB to a low level.

Toggle:

If EPWMxA or EPWMxB is currently pulled high, then pull the output low. If EPWMxA or

EPWMxB is

currently pulled low, then pull the output high.

Do Nothing:

Keep outputs EPWMxA and EPWMxB at same level as currently set. Although the "Do Nothing"

option

prevents an event from causing an action on the EPWMxA and EPWMxB outputs, this event can still

trigger interrupts and ADC start of conversion.

Action-Qualifier Event Priority:

It is possible for the ePWM action qualifier to receive more than one event at the same time. In this

case

events are assigned a priority by the hardware. The general rule is events occurring later in time have a

higher priority and software forced events always have the highest priority.

In a running system, the active compare registers (CMPA and CMPB) are typically

updated from their respective shadow registers once every period. The user specifies when

the update will take place; either when the time-base counter reaches zero or when the

time-base counter reaches period.

//

#include "DSP2833x_Device.h"

// Prototype statements for functions found within this file.

void Gpio_select(void);

extern void InitSysCtrl(void);

interrupt void cpu_timer0_isr(void);

extern void InitPieCtrl(void);

extern void InitPieVectTable(void);

extern void InitCpuTimers(void);

extern void ConfigCpuTimer(struct CPUTIMER_VARS *, float, float);

void Setup_ePWM1A(void);

//###########################################################################

// main code

//###########################################################################

void main(void)

{

int counter=0; // binary counter for digital output

InitSysCtrl(); // Basic Core Initialization

EALLOW;

SysCtrlRegs.WDCR = 0x00AF; // Watchdog enabled, 4.3 milliseconds

EDIS;

DINT; // Disable all interrupts

Gpio_select(); // GPIO9,GPIO11,GPIO34 and GPIO49 as output (LEDs @ peripheral explorer)

Setup_ePWM1A();

InitPieCtrl();

InitPieVectTable();

EALLOW;

PieVectTable.TINT0 = &cpu_timer0_isr;

EDIS;

InitCpuTimers();

ConfigCpuTimer(&CpuTimer0,150,100);

PieCtrlRegs.PIEIER1.bit.INTx7 = 1;

IER |=1;

EINT;

ERTM; //enable real time interrupt

CpuTimer0Regs.TCR.bit.TSS = 0;

while(1)

{

while(CpuTimer0.InterruptCount == 0);

CpuTimer0.InterruptCount = 0;

EALLOW;

SysCtrlRegs.WDKEY = 0x55; // service WD #1

EDIS;

counter++;

if(counter&1) GpioDataRegs.GPASET.bit.GPIO9 = 1;

else GpioDataRegs.GPACLEAR.bit.GPIO9 = 1;

if(counter&2) GpioDataRegs.GPASET.bit.GPIO11 = 1;

else GpioDataRegs.GPACLEAR.bit.GPIO11 = 1;

if(counter&4) GpioDataRegs.GPBSET.bit.GPIO34 = 1;

else GpioDataRegs.GPBCLEAR.bit.GPIO34 = 1;

if(counter&8) GpioDataRegs.GPBSET.bit.GPIO49 = 1;

else GpioDataRegs.GPBCLEAR.bit.GPIO49 = 1;

}

}

void Gpio_select(void)

{

EALLOW;

GpioCtrlRegs.GPAMUX1.all = 0; // GPIO15 ... GPIO0 = General Puropse I/O

GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1; // ePWM1A active

GpioCtrlRegs.GPAMUX2.all = 0; // GPIO31 ... GPIO16 = General Purpose I/O

GpioCtrlRegs.GPBMUX1.all = 0; // GPIO47 ... GPIO32 = General Purpose I/O

GpioCtrlRegs.GPBMUX2.all = 0; // GPIO63 ... GPIO48 = General Purpose I/O

GpioCtrlRegs.GPCMUX1.all = 0; // GPIO79 ... GPIO64 = General Purpose I/O

GpioCtrlRegs.GPCMUX2.all = 0; // GPIO87 ... GPIO80 = General Purpose I/O

GpioCtrlRegs.GPADIR.all = 0;

GpioCtrlRegs.GPADIR.bit.GPIO9 = 1; // peripheral explorer: LED LD1 at GPIO9

GpioCtrlRegs.GPADIR.bit.GPIO11 = 1; // peripheral explorer: LED LD2 at GPIO11

GpioCtrlRegs.GPBDIR.all = 0; // GPIO63-32 as inputs

GpioCtrlRegs.GPBDIR.bit.GPIO34 = 1; // peripheral explorer: LED LD3 at GPIO34

GpioCtrlRegs.GPBDIR.bit.GPIO49 = 1; // peripheral explorer: LED LD4 at GPIO49

GpioCtrlRegs.GPCDIR.all = 0; // GPIO87-64 as inputs

EDIS;

}

interrupt void cpu_timer0_isr(void)

{

static int up_down = 1;

CpuTimer0.InterruptCount++;

EALLOW;

SysCtrlRegs.WDKEY = 0xAA; // service WD #2

EDIS;

if(up_down)

{

if(EPwm1Regs.CMPA.half.CMPA < EPwm1Regs.TBPRD) EPwm1Regs.CMPA.half.CMPA++;

else up_down = 0;

}

else

{

if(EPwm1Regs.CMPA.half.CMPA > 0) EPwm1Regs.CMPA.half.CMPA--;

else up_down = 1;

}

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

}

void Setup_ePWM1A(void)

{

EPwm1Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 2

EPwm1Regs.TBCTL.bit.CTRMODE = 2; // up - down mode

EPwm1Regs.CMPA.half.CMPA = 0;

EPwm1Regs.AQCTLA.all = 0x0060; // ZRO = set, PRD = clear

EPwm1Regs.TBPRD = 37500; // 1KHz - PWM signal

}

#include "DSP2833x_Device.h"

// Prototype statements for functions found within this file.

void Gpio_select(void);

extern void InitSysCtrl(void);

interrupt void cpu_timer0_isr(void);

extern void InitPieCtrl(void);

extern void InitPieVectTable(void);

extern void InitCpuTimers(void);

extern void ConfigCpuTimer(struct CPUTIMER_VARS *, float, float);

void Setup_ePWM1(void);

//###########################################################################

// main code

//###########################################################################

void main(void)

{

int counter=0; // binary counter for digital output

InitSysCtrl(); // Basic Core Initialization

EALLOW;

SysCtrlRegs.WDCR = 0x00AF; // Watchdog enabled, 4.3 milliseconds

EDIS;

DINT; // Disable all interrupts

Gpio_select(); // GPIO9,GPIO11,GPIO34 and GPIO49 as output (LEDs @ peripheral explorer)

Setup_ePWM1();

InitPieCtrl();

InitPieVectTable();

EALLOW;

PieVectTable.TINT0 = &cpu_timer0_isr;

EDIS;

InitCpuTimers();

ConfigCpuTimer(&CpuTimer0,150,100);

PieCtrlRegs.PIEIER1.bit.INTx7 = 1;

IER |=1;

EINT;

ERTM; //enable real time interrupt

CpuTimer0Regs.TCR.bit.TSS = 0;

while(1)

{

while(CpuTimer0.InterruptCount == 0);

CpuTimer0.InterruptCount = 0;

EALLOW;

SysCtrlRegs.WDKEY = 0x55; // service WD #1

EDIS;

counter++;

if(counter&1) GpioDataRegs.GPASET.bit.GPIO9 = 1;

else GpioDataRegs.GPACLEAR.bit.GPIO9 = 1;

if(counter&2) GpioDataRegs.GPASET.bit.GPIO11 = 1;

else GpioDataRegs.GPACLEAR.bit.GPIO11 = 1;

if(counter&4) GpioDataRegs.GPBSET.bit.GPIO34 = 1;

else GpioDataRegs.GPBCLEAR.bit.GPIO34 = 1;

if(counter&8) GpioDataRegs.GPBSET.bit.GPIO49 = 1;

else GpioDataRegs.GPBCLEAR.bit.GPIO49 = 1;

}

}

void Gpio_select(void)

{

EALLOW;

GpioCtrlRegs.GPAMUX1.all = 0; // GPIO15 ... GPIO0 = General Puropse I/O

GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1; // ePWM1A active

GpioCtrlRegs.GPAMUX1.bit.GPIO1 = 1;

GpioCtrlRegs.GPAMUX2.all = 0; // GPIO31 ... GPIO16 = General Purpose I/O

GpioCtrlRegs.GPBMUX1.all = 0; // GPIO47 ... GPIO32 = General Purpose I/O

GpioCtrlRegs.GPBMUX2.all = 0; // GPIO63 ... GPIO48 = General Purpose I/O

GpioCtrlRegs.GPCMUX1.all = 0; // GPIO79 ... GPIO64 = General Purpose I/O

GpioCtrlRegs.GPCMUX2.all = 0; // GPIO87 ... GPIO80 = General Purpose I/O

GpioCtrlRegs.GPADIR.all = 0;

GpioCtrlRegs.GPADIR.bit.GPIO9 = 1; // peripheral explorer: LED LD1 at GPIO9

GpioCtrlRegs.GPADIR.bit.GPIO11 = 1; // peripheral explorer: LED LD2 at GPIO11

GpioCtrlRegs.GPBDIR.all = 0; // GPIO63-32 as inputs

GpioCtrlRegs.GPBDIR.bit.GPIO34 = 1; // peripheral explorer: LED LD3 at GPIO34

GpioCtrlRegs.GPBDIR.bit.GPIO49 = 1; // peripheral explorer: LED LD4 at GPIO49

GpioCtrlRegs.GPCDIR.all = 0; // GPIO87-64 as inputs

EDIS;

}

interrupt void cpu_timer0_isr(void)

{

static int up_down = 1;

CpuTimer0.InterruptCount++;

EALLOW;

SysCtrlRegs.WDKEY = 0xAA; // service WD #2

EDIS;

if(up_down)

{

if(EPwm1Regs.CMPA.half.CMPA < EPwm1Regs.TBPRD) EPwm1Regs.CMPA.half.CMPA++;

else up_down = 0;

}

else

{

if(EPwm1Regs.CMPA.half.CMPA > 0) EPwm1Regs.CMPA.half.CMPA--;

else up_down = 1;

}

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

}

void Setup_ePWM1(void)

{

EPwm1Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 2

EPwm1Regs.TBCTL.bit.CTRMODE = 2; // up - down mode

EPwm1Regs.CMPA.half.CMPA = 0;

EPwm1Regs.AQCTLA.all = 0x0060; // ZRO = set, PRD = clear

EPwm1Regs.AQCTLB.all = 0x0090;

EPwm1Regs.TBPRD = 37500; // 1KHz - PWM signal

}

#include "DSP2833x_Device.h"

// Prototype statements for functions found within this file.

void Gpio_select(void);

extern void InitSysCtrl(void);

interrupt void cpu_timer0_isr(void);

extern void InitPieCtrl(void);

extern void InitPieVectTable(void);

extern void InitCpuTimers(void);

extern void ConfigCpuTimer(struct CPUTIMER_VARS *, float, float);

void Setup_ePWM1(void);

//###########################################################################

// main code

//###########################################################################

void main(void)

{

int counter=0; // binary counter for digital output

InitSysCtrl(); // Basic Core Initialization

EALLOW;

SysCtrlRegs.WDCR = 0x00AF; // Watchdog enabled, 4.3 milliseconds

EDIS;

DINT; // Disable all interrupts

Gpio_select(); // GPIO9,GPIO11,GPIO34 and GPIO49 as output (LEDs @ peripheral explorer)

Setup_ePWM1();

InitPieCtrl();

InitPieVectTable();

EALLOW;

PieVectTable.TINT0 = &cpu_timer0_isr;

EDIS;

InitCpuTimers();

ConfigCpuTimer(&CpuTimer0,150,100);

PieCtrlRegs.PIEIER1.bit.INTx7 = 1;

IER |=1;

EINT;

ERTM; //enable real time interrupt

CpuTimer0Regs.TCR.bit.TSS = 0;

while(1)

{

while(CpuTimer0.InterruptCount == 0);

CpuTimer0.InterruptCount = 0;

EALLOW;

SysCtrlRegs.WDKEY = 0x55; // service WD #1

EDIS;

counter++;

if(counter&1) GpioDataRegs.GPASET.bit.GPIO9 = 1;

else GpioDataRegs.GPACLEAR.bit.GPIO9 = 1;

if(counter&2) GpioDataRegs.GPASET.bit.GPIO11 = 1;

else GpioDataRegs.GPACLEAR.bit.GPIO11 = 1;

if(counter&4) GpioDataRegs.GPBSET.bit.GPIO34 = 1;

else GpioDataRegs.GPBCLEAR.bit.GPIO34 = 1;

if(counter&8) GpioDataRegs.GPBSET.bit.GPIO49 = 1;

else GpioDataRegs.GPBCLEAR.bit.GPIO49 = 1;

}

}

void Gpio_select(void)

{

EALLOW;

GpioCtrlRegs.GPAMUX1.all = 0; // GPIO15 ... GPIO0 = General Puropse I/O

GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1; // ePWM1A active

GpioCtrlRegs.GPAMUX1.bit.GPIO1 = 1;

GpioCtrlRegs.GPAMUX2.all = 0; // GPIO31 ... GPIO16 = General Purpose I/O

GpioCtrlRegs.GPBMUX1.all = 0; // GPIO47 ... GPIO32 = General Purpose I/O

GpioCtrlRegs.GPBMUX2.all = 0; // GPIO63 ... GPIO48 = General Purpose I/O

GpioCtrlRegs.GPCMUX1.all = 0; // GPIO79 ... GPIO64 = General Purpose I/O

GpioCtrlRegs.GPCMUX2.all = 0; // GPIO87 ... GPIO80 = General Purpose I/O

GpioCtrlRegs.GPADIR.all = 0;

GpioCtrlRegs.GPADIR.bit.GPIO9 = 1; // peripheral explorer: LED LD1 at GPIO9

GpioCtrlRegs.GPADIR.bit.GPIO11 = 1; // peripheral explorer: LED LD2 at GPIO11

GpioCtrlRegs.GPBDIR.all = 0; // GPIO63-32 as inputs

GpioCtrlRegs.GPBDIR.bit.GPIO34 = 1; // peripheral explorer: LED LD3 at GPIO34

GpioCtrlRegs.GPBDIR.bit.GPIO49 = 1; // peripheral explorer: LED LD4 at GPIO49

GpioCtrlRegs.GPCDIR.all = 0; // GPIO87-64 as inputs

EDIS;

}

interrupt void cpu_timer0_isr(void)

{

CpuTimer0.InterruptCount++;

EALLOW;

SysCtrlRegs.WDKEY = 0xAA; // service WD #2

EDIS;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

}

void Setup_ePWM1(void)

{

EPwm1Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 2

EPwm1Regs.TBCTL.bit.CTRMODE = 2; // up - down mode

EPwm1Regs.AQCTLA.all = 0x0060; // ZRO = set, PRD = clear

EPwm1Regs.AQCTLB.all = 0x0600;

EPwm1Regs.TBPRD = 37500; // 1KHz - PWM signal

EPwm1Regs.CMPA.half.CMPA = EPwm1Regs.TBPRD / 2;

EPwm1Regs.CMPB = EPwm1Regs.TBPRD / 2;

}

In this programme input to the dead band unit is epwm1a.but output is both epwm1a/1b

#include "DSP2833x_Device.h"

// Prototype statements for functions found within this file.

void Gpio_select(void);

extern void InitSysCtrl(void);

interrupt void cpu_timer0_isr(void);

extern void InitPieCtrl(void);

extern void InitPieVectTable(void);

extern void InitCpuTimers(void);

extern void ConfigCpuTimer(struct CPUTIMER_VARS *, float, float);

void Setup_ePWM1(void);

//###########################################################################

// main code

//###########################################################################

void main(void)

{

int counter=0; // binary counter for digital output

InitSysCtrl(); // Basic Core Initialization

EALLOW;

SysCtrlRegs.WDCR = 0x00AF; // Watchdog enabled, 4.3 milliseconds

EDIS;

DINT; // Disable all interrupts

Gpio_select(); // GPIO9,GPIO11,GPIO34 and GPIO49 as output (LEDs @ peripheral explorer)

Setup_ePWM1();

InitPieCtrl();

InitPieVectTable();

EALLOW;

PieVectTable.TINT0 = &cpu_timer0_isr;

EDIS;

InitCpuTimers();

ConfigCpuTimer(&CpuTimer0,150,100);

PieCtrlRegs.PIEIER1.bit.INTx7 = 1;

IER |=1;

EINT;

ERTM; //enable real time interrupt

CpuTimer0Regs.TCR.bit.TSS = 0;

while(1)

{

while(CpuTimer0.InterruptCount == 0);

CpuTimer0.InterruptCount = 0;

EALLOW;

SysCtrlRegs.WDKEY = 0x55; // service WD #1

EDIS;

counter++;

if(counter&1) GpioDataRegs.GPASET.bit.GPIO9 = 1;

else GpioDataRegs.GPACLEAR.bit.GPIO9 = 1;

if(counter&2) GpioDataRegs.GPASET.bit.GPIO11 = 1;

else GpioDataRegs.GPACLEAR.bit.GPIO11 = 1;

if(counter&4) GpioDataRegs.GPBSET.bit.GPIO34 = 1;

else GpioDataRegs.GPBCLEAR.bit.GPIO34 = 1;

if(counter&8) GpioDataRegs.GPBSET.bit.GPIO49 = 1;

else GpioDataRegs.GPBCLEAR.bit.GPIO49 = 1;

}

}

void Gpio_select(void)

{

EALLOW;

GpioCtrlRegs.GPAMUX1.all = 0; // GPIO15 ... GPIO0 = General Puropse I/O

GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1; // ePWM1A active

GpioCtrlRegs.GPAMUX1.bit.GPIO1 = 1;

GpioCtrlRegs.GPAMUX2.all = 0; // GPIO31 ... GPIO16 = General Purpose I/O

GpioCtrlRegs.GPBMUX1.all = 0; // GPIO47 ... GPIO32 = General Purpose I/O

GpioCtrlRegs.GPBMUX2.all = 0; // GPIO63 ... GPIO48 = General Purpose I/O

GpioCtrlRegs.GPCMUX1.all = 0; // GPIO79 ... GPIO64 = General Purpose I/O

GpioCtrlRegs.GPCMUX2.all = 0; // GPIO87 ... GPIO80 = General Purpose I/O

GpioCtrlRegs.GPADIR.all = 0;

GpioCtrlRegs.GPADIR.bit.GPIO9 = 1; // peripheral explorer: LED LD1 at GPIO9

GpioCtrlRegs.GPADIR.bit.GPIO11 = 1; // peripheral explorer: LED LD2 at GPIO11

GpioCtrlRegs.GPBDIR.all = 0; // GPIO63-32 as inputs

GpioCtrlRegs.GPBDIR.bit.GPIO34 = 1; // peripheral explorer: LED LD3 at GPIO34

GpioCtrlRegs.GPBDIR.bit.GPIO49 = 1; // peripheral explorer: LED LD4 at GPIO49

GpioCtrlRegs.GPCDIR.all = 0; // GPIO87-64 as inputs

EDIS;

}

interrupt void cpu_timer0_isr(void)

{

CpuTimer0.InterruptCount++;

EALLOW;

SysCtrlRegs.WDKEY = 0xAA; // service WD #2

EDIS;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

}

void Setup_ePWM1(void)

{

EPwm1Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 2

EPwm1Regs.TBCTL.bit.CTRMODE = 2; // up - down mode

EPwm1Regs.CMPA.half.CMPA = 0;

EPwm1Regs.AQCTLA.all = 0x0060; // ZRO = set, PRD = clear

EPwm1Regs.TBPRD = 37500; // 1KHz - PWM signal

EPwm1Regs.CMPA.half.CMPA = EPwm1Regs.TBPRD / 2;

EPwm1Regs.DBRED = 750;

EPwm1Regs.DBFED = 750;

EPwm1Regs.DBCTL.bit.OUT_MODE = 3; // ePWM1A = RED

EPwm1Regs.DBCTL.bit.POLSEL = 2; // S3=1 inverted signal at ePWM1B

EPwm1Regs.DBCTL.bit.IN_MODE = 0; // ePWM1A = source for RED & FED

}

The carrier clock of the ePWM Chopper Module is derived from SYSCLKOUT. The frequency and duty

cycle of the chopper unit are controlled via the CHPFREQ and CHPDUTY bits in the PCCTL register.

The one-shot block is a feature that provides a high-energy first pulse to ensure hard and fast power

switch turn on, while the subsequent pulses sustain pulses, ensuring the power switch remains on. The

one-shot width is programmed via the OSHTWTH bits.

The PWM-chopper sub module can be fully disabled (bypassed) via the CHPEN bit.

One of seven possible duty ratios can be selected ranging from 12.5% to 87.5%.

void Setup_ePWM1(void)

{

EPwm1Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 2

EPwm1Regs.TBCTL.bit.CTRMODE = 2; // up - down mode

EPwm1Regs.AQCTLA.all = 0x0060; // ZRO = set, PRD = clear

EPwm1Regs.AQCTLB.all = 0x0600;

EPwm1Regs.TBPRD = 37500; // 1KHz - PWM signal

EPwm1Regs.CMPA.half.CMPA = EPwm1Regs.TBPRD / 2;;

EPwm1Regs.CMPB = EPwm1Regs.TBPRD / 2;

EPwm1Regs.PCCTL.bit.CHPFREQ = 7; // SYSCLKOUT / 64 = 2.34375MHz

EPwm1Regs.PCCTL.bit.CHPDUTY = 3; // 50% duty cycle

EPwm1Regs.PCCTL.bit.CHPEN = 1; // 1= enable chopper mode

EPwm1Regs.PCCTL.bit.OSHTWTH = 14; // 120 *6.67 ns = 800 ns

}

Вам также может понравиться

- 3D Integration in VLSI Circuits Implementation Technologies and ApplicationsДокумент235 страниц3D Integration in VLSI Circuits Implementation Technologies and ApplicationslionkingОценок пока нет

- Datasheet Etx PMДокумент2 страницыDatasheet Etx PMMohamedAliOuhaddouОценок пока нет

- Universidad Nacional de IngenieríaДокумент19 страницUniversidad Nacional de IngenieríasaverfimОценок пока нет

- DC Motor Speed ControlДокумент5 страницDC Motor Speed ControlAnita WulansariОценок пока нет

- MPBES Lab 7Документ4 страницыMPBES Lab 7ahmedОценок пока нет

- Solution W17Документ25 страницSolution W17FirozОценок пока нет

- DSP GateДокумент5 страницDSP Gatebodige123Оценок пока нет

- 05 AVR Timer-Counter AVRДокумент95 страниц05 AVR Timer-Counter AVRPriscillaОценок пока нет

- 06 - Timer With PWM PDFДокумент14 страниц06 - Timer With PWM PDFSrikanth MahanthiОценок пока нет

- Avr ArchitectureДокумент29 страницAvr ArchitectureOdoch HerbertОценок пока нет

- Osmeoisis 2022-09-06 15-33-19PIC - Mid - C - 11Документ34 страницыOsmeoisis 2022-09-06 15-33-19PIC - Mid - C - 11Tomás BurónОценок пока нет

- Step Replace Module Flexi BSC NokiaДокумент19 страницStep Replace Module Flexi BSC Nokiarudibenget0% (1)

- Automatic College Bell REPORTДокумент34 страницыAutomatic College Bell REPORTNagraj Tondchore50% (2)

- End Sem ExamДокумент20 страницEnd Sem Examdorejis472Оценок пока нет

- STM32 Timer Features for Timing ApplicationsДокумент91 страницаSTM32 Timer Features for Timing ApplicationsnorbertscribdОценок пока нет

- Osmeoisis 2022-09-06 15-33-19PIC - Enh - A - 18Документ50 страницOsmeoisis 2022-09-06 15-33-19PIC - Enh - A - 18Tomás BurónОценок пока нет

- The University of Texas at Arlington Timers, Capture/Compare/PWMДокумент22 страницыThe University of Texas at Arlington Timers, Capture/Compare/PWMadamwaiz100% (1)

- Lab BookДокумент70 страницLab Bookअमरेश झाОценок пока нет

- Comphrahensiv Viva: Chandra Mohan ReddyДокумент41 страницаComphrahensiv Viva: Chandra Mohan ReddyRavee SankarОценок пока нет

- CCP PWMДокумент19 страницCCP PWMalaa_saq100% (1)

- 16-B PWM U O - C T Relevant Devices: IT Sing AN N HIP ImerДокумент12 страниц16-B PWM U O - C T Relevant Devices: IT Sing AN N HIP ImerLauderi MartinsОценок пока нет

- Pic Microcontroller 2.1 Pic It Is A Family of Modified Harvard Architecture Microcontrollers MadeДокумент16 страницPic Microcontroller 2.1 Pic It Is A Family of Modified Harvard Architecture Microcontrollers MadeSuresh KumarОценок пока нет

- Microcontroller Tutorial Ii Timers: What Is A Timer?Документ13 страницMicrocontroller Tutorial Ii Timers: What Is A Timer?Ting Chee SiongОценок пока нет

- PIC Peripherals GuideДокумент36 страницPIC Peripherals GuideMengesha KirosОценок пока нет

- TMS320F2812 - Event ManagerДокумент52 страницыTMS320F2812 - Event ManagerPantech ProLabs India Pvt LtdОценок пока нет

- MPMC Unit 4Документ35 страницMPMC Unit 4Dharani ChinnaОценок пока нет

- Space Vector PWM - 1Документ5 страницSpace Vector PWM - 1guanitouОценок пока нет

- EMISY Second Test Exemplary Questions Solved-9Документ14 страницEMISY Second Test Exemplary Questions Solved-9YANG LIUОценок пока нет

- STM32F3 TimersДокумент75 страницSTM32F3 TimersVport Port100% (1)

- AN594 - Using The CCP Module(s)Документ25 страницAN594 - Using The CCP Module(s)Guillermo Hernandez100% (3)

- Z-80 Counter/Timer Circuit SpecificationДокумент12 страницZ-80 Counter/Timer Circuit SpecificationTheAnonymousLugiaОценок пока нет

- Using The Xmega Timer:CounterДокумент17 страницUsing The Xmega Timer:CounterHongquan LiОценок пока нет

- ELEC 3040/3050 Lab #7: PWM Waveform GenerationДокумент22 страницыELEC 3040/3050 Lab #7: PWM Waveform GenerationBrandon2017Оценок пока нет

- Measuring EVM and In-Band Emissions: Figure 1. Waveform Generation Using AppДокумент7 страницMeasuring EVM and In-Band Emissions: Figure 1. Waveform Generation Using AppDUONG LEОценок пока нет

- Embedded MicrocontrollerДокумент30 страницEmbedded MicrocontrollervinoliabenitaОценок пока нет

- LPC1769 Interrupt ProgramДокумент9 страницLPC1769 Interrupt Programprathap100% (1)

- Chapter 4: One-Shots, Counters, and Clocks: I. The Monostable Multivibrator (One-Shot)Документ6 страницChapter 4: One-Shots, Counters, and Clocks: I. The Monostable Multivibrator (One-Shot)amitpatel1991Оценок пока нет

- Control UnitДокумент11 страницControl UnitDon KosalaОценок пока нет

- 50hz Sine PWM Using Tms320f2812 DSPДокумент19 страниц50hz Sine PWM Using Tms320f2812 DSPVisu Tamil100% (2)

- VLSI Stopwatch Chip Project ReportДокумент40 страницVLSI Stopwatch Chip Project ReportMani SinghОценок пока нет

- Lecture 15Документ9 страницLecture 15VINAYОценок пока нет

- SPRT 723 BДокумент5 страницSPRT 723 BAmarYalavarthiОценок пока нет

- 36Документ74 страницы36Sanoop MkОценок пока нет

- Infineon-Component - PSoC - 4 - Timer - Counter - and - PWM - V1.10-Software Module Datasheets-V02 - 01-ENДокумент42 страницыInfineon-Component - PSoC - 4 - Timer - Counter - and - PWM - V1.10-Software Module Datasheets-V02 - 01-ENFatenn BellakhdharОценок пока нет

- Defense MechanismДокумент27 страницDefense MechanismgkkishorekumarОценок пока нет

- ATmega Interrupts Explained/TITLEДокумент17 страницATmega Interrupts Explained/TITLEJarfoОценок пока нет

- Project Underdamped SystemДокумент6 страницProject Underdamped SystemPablo HenriqueОценок пока нет

- Modeling Definite Time Overcurrent Relay Auto Recloser in MATLABДокумент5 страницModeling Definite Time Overcurrent Relay Auto Recloser in MATLABHayat Ansari100% (1)

- 3G InterviewДокумент21 страница3G InterviewPrashant KumarОценок пока нет

- Osmeoisis 2022-09-06 15-33-19PIC - Mid - A - 17Документ40 страницOsmeoisis 2022-09-06 15-33-19PIC - Mid - A - 17Tomás BurónОценок пока нет

- Analog - Sine Wave Generation With Psoc 1 (Demonstration With CTCSS)Документ11 страницAnalog - Sine Wave Generation With Psoc 1 (Demonstration With CTCSS)Adonis LealОценок пока нет

- Timers and PWM on PIC MicrocontrollersДокумент38 страницTimers and PWM on PIC MicrocontrollersThanh LeОценок пока нет

- Interrupts and Traps in Oberon-ARMДокумент3 страницыInterrupts and Traps in Oberon-ARMmqt99311zwoho.comОценок пока нет

- Using External Interrupts For MegaAVR DevicesДокумент12 страницUsing External Interrupts For MegaAVR DevicesJhon ZumaetaОценок пока нет

- Control DC Motor Speed using STM32 PWMДокумент4 страницыControl DC Motor Speed using STM32 PWMJohn FarandisОценок пока нет

- E MIOSДокумент24 страницыE MIOSWily PonceОценок пока нет

- L 122a 6Документ13 страницL 122a 6Bogdan Alin100% (1)

- Interrupt Structure of 8051Документ16 страницInterrupt Structure of 8051Amar SinghОценок пока нет

- Simulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorОт EverandSimulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorОценок пока нет

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960От EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Оценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- BCC GTPДокумент2 страницыBCC GTPVivek AnnepuОценок пока нет

- BhaskarДокумент73 страницыBhaskarVivek AnnepuОценок пока нет

- Power ElectronicsДокумент27 страницPower ElectronicsVivek AnnepuОценок пока нет

- Cpu TimerДокумент11 страницCpu TimerVivek AnnepuОценок пока нет

- Jun 14 - OngoingДокумент2 страницыJun 14 - OngoingVivek AnnepuОценок пока нет

- Solar SheetДокумент4 страницыSolar SheetVivek AnnepuОценок пока нет

- Solar Sheet En630 AchithaДокумент4 страницыSolar Sheet En630 AchithaVivek AnnepuОценок пока нет

- Solar Sheet En630Документ4 страницыSolar Sheet En630Vivek AnnepuОценок пока нет

- Chapter 8 - Solar PondДокумент9 страницChapter 8 - Solar PondVivek AnnepuОценок пока нет

- Lecture0 Introduction 2013Документ2 страницыLecture0 Introduction 2013Vivek AnnepuОценок пока нет

- IRPS Spacer Q&AДокумент2 страницыIRPS Spacer Q&ASnehaОценок пока нет

- RVfpga GettingStartedGuideДокумент103 страницыRVfpga GettingStartedGuideSoumya Ranjan MishraОценок пока нет

- Gigabyte Technology Gigabyte Technology Gigabyte Technology: GA-G31M-S2C GA-G31M-S2C GA-G31M-S2CДокумент33 страницыGigabyte Technology Gigabyte Technology Gigabyte Technology: GA-G31M-S2C GA-G31M-S2C GA-G31M-S2CWilvert ChumaceroОценок пока нет

- 1989 Cmos Bicmos Data BookДокумент1 017 страниц1989 Cmos Bicmos Data BookFeysal ImranОценок пока нет

- Enhancing Performance With PipeliningДокумент71 страницаEnhancing Performance With Pipeliningapi-26072581Оценок пока нет

- IOE Syllabus for Digital Logic CourseДокумент5 страницIOE Syllabus for Digital Logic CoursePramod Kumar Chaudhary0% (1)

- MIPI CSI-2 Camera Interface Module OverviewДокумент11 страницMIPI CSI-2 Camera Interface Module OverviewVarun Shanker Trivedi0% (1)

- Chapter 3 Logic GatesДокумент16 страницChapter 3 Logic GatesbeebeeseyneeОценок пока нет

- Un32c5000 - 40C5000 - 46C5000 MainДокумент16 страницUn32c5000 - 40C5000 - 46C5000 Mainmj15015Оценок пока нет

- DL205 Series: Micromodule TypeДокумент68 страницDL205 Series: Micromodule TypeJoseph MedinaОценок пока нет

- Static CMOS Inverter DC CharacteristicsДокумент1 страницаStatic CMOS Inverter DC CharacteristicsCarlos SaavedraОценок пока нет

- Jan-Apr 2022 Enrollment Details (2021-22 EVEN)Документ85 страницJan-Apr 2022 Enrollment Details (2021-22 EVEN)yaligarumashankar89Оценок пока нет

- Introducing The PIC32MZ v4.6 (ENG)Документ158 страницIntroducing The PIC32MZ v4.6 (ENG)Andres Bruno SaraviaОценок пока нет

- P4m2proc PДокумент2 страницыP4m2proc PRichard ErasquinОценок пока нет

- Digital Logic Circuits Objective Questions PDFДокумент9 страницDigital Logic Circuits Objective Questions PDFNoor AhmedОценок пока нет

- Abit - M621 Schematics: Title Sheet ModifyДокумент33 страницыAbit - M621 Schematics: Title Sheet Modify775i945GZ100% (1)

- PIC18 Serial Port Programming in AssemblyДокумент37 страницPIC18 Serial Port Programming in Assemblyanses1000Оценок пока нет

- Csa - 1Документ15 страницCsa - 1Nathaniel BaldevinoОценок пока нет

- 4 PerformanceДокумент27 страниц4 Performance1352 : NEEBESH PADHYОценок пока нет

- Digital Electronics Jan 2018 IntroductionДокумент11 страницDigital Electronics Jan 2018 IntroductionWan AmnanОценок пока нет

- KS0649Документ15 страницKS0649Linzaw WinОценок пока нет

- Lecture 3Документ39 страницLecture 3akttripathi0% (1)

- Lecture9-Processor Organization & Instruction CycleДокумент15 страницLecture9-Processor Organization & Instruction CycletesfuОценок пока нет

- Modicon M580 - EPac Controller - BMEH582040Документ5 страницModicon M580 - EPac Controller - BMEH582040Ehsan RohaniОценок пока нет

- Process in Operating SystemДокумент5 страницProcess in Operating SystemSivaranjan GoswamiОценок пока нет

- Plot The DC Characteristics / 5 Regions of A CMOS InverterДокумент7 страницPlot The DC Characteristics / 5 Regions of A CMOS InverterSaurabh PriyadarshiОценок пока нет

- 197Документ113 страниц197Dhanya Geethanjali SasidharanОценок пока нет

- Altus Quark 2400 - ALNETДокумент3 страницыAltus Quark 2400 - ALNETzjjuniorОценок пока нет