Академический Документы

Профессиональный Документы

Культура Документы

Qfet Qfet Qfet Qfet: FQP90N08

Загружено:

Hãy Cố LênОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Qfet Qfet Qfet Qfet: FQP90N08

Загружено:

Hãy Cố LênАвторское право:

Доступные форматы

QFET QFET QFET QFET

TM

2000 Fairchild Semiconductor International

January 2001

Rev. A1, January 2001

F

Q

P

9

0

N

0

8

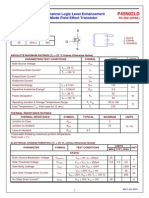

FQP90N08

80V N-Channel MOSFET

General Description

These N-Channel enhancement mode power field effect

transistors are produced using Fairchilds proprietary,

planar stripe, DMOS technology.

This advanced technology has been especially tailored to

minimize on-state resistance, provide superior switching

performance, and withstand a high energy pulse in the

avalanche and commutation modes. These devices are

well suited for low voltage applications such as automotive,

high efficiency switching for DC/DC converters, and DC

motor control.

Features

71A, 80V, R

DS(on)

= 0.016 @V

GS

= 10 V

Low gate charge ( typical 84 nC)

Low Crss ( typical 200 pF)

Fast switching

100% avalanche tested

Improved dv/dt capability

175C maximum junction temperature rating

Absolute Maximum Ratings T

C

= 25C unless otherwise noted

Thermal Characteristics

Symbol Parameter FQP90N08 Units

V

DSS

Drain-Source Voltage 80 V

I

D

Drain Current - Continuous (T

C

= 25C) 71 A

- Continuous (T

C

= 100C) 50.2 A

I

DM

Drain Current - Pulsed (Note 1) 284 A

V

GSS

Gate-Source Voltage 25 V

E

AS

Single Pulsed Avalanche Energy (Note 2) 1360 mJ

I

AR

Avalanche Current (Note 1) 71 A

E

AR

Repetitive Avalanche Energy (Note 1) 16 mJ

dv/dt Peak Diode Recovery dv/dt (Note 3) 6.5 V/ns

P

D

Power Dissipation (T

C

= 25C) 160 W

- Derate above 25C 1.06 W/C

T

J

, T

STG

Operating and Storage Temperature Range -55 to +175 C

T

L

Maximum lead temperature for soldering purposes,

1/8" from case for 5 seconds

300 C

Symbol Parameter Typ Max Units

R

JC

Thermal Resistance, Junction-to-Case -- 0.94 C/W

R

CS

Thermal Resistance, Case-to-Sink 0.5 -- C/W

R

JA

Thermal Resistance, Junction-to-Ambient -- 62.5 C/W

! "

!

!

!

"

"

"

! "

!

!

!

"

"

"

S

D

G

TO-220

FQP Series

G S D

2000 Fairchild Semiconductor International

F

Q

P

9

0

N

0

8

(Note 4)

(Note 4, 5)

(Note 4, 5)

(Note 4)

Rev. A1, January 2001

Electrical Characteristics T

C

= 25C unless otherwise noted

Notes:

1. Repetitive Rating : Pulse width limited by maximum junction temperature

2. L = 0.37mH, I

AS

= 71A, V

DD

= 25V, R

G

= 25 , Starting T

J

= 25C

3. I

SD

! 90A, di/dt ! 300A/s, V

DD

! BV

DSS,

Starting T

J

= 25C

4. Pulse Test : Pulse width !300s, Duty cycle !2%

5. Essentially independent of operating temperature

Symbol Parameter Test Conditions Min Typ Max Units

Off Characteristics

BV

DSS

Drain-Source Breakdown Voltage V

GS

= 0 V, I

D

= 250 A 80 -- -- V

BV

DSS

/ T

J

Breakdown Voltage Temperature

Coefficient

I

D

= 250 A, Referenced to 25C -- 0.1 -- V/C

I

DSS

Zero Gate Voltage Drain Current

V

DS

= 100 V, V

GS

= 0 V -- -- 1 A

V

DS

= 80 V, T

C

= 150C -- -- 10 A

I

GSSF

Gate-Body Leakage Current, Forward V

GS

= 25 V, V

DS

= 0 V -- -- 100 nA

I

GSSR

Gate-Body Leakage Current, Reverse V

GS

= -25 V, V

DS

= 0 V -- -- -100 nA

On Characteristics

V

GS(th)

Gate Threshold Voltage V

DS

= V

GS

, I

D

= 250 A 2.0 -- 4.0 V

R

DS(on)

Static Drain-Source

On-Resistance

V

GS

= 10 V, I

D

= 35.5 A -- 0.012 0.016

g

FS

Forward Transconductance V

DS

= 30 V, I

D

= 35.5 A -- 49 -- S

Dynamic Characteristics

C

iss

Input Capacitance

V

DS

= 25 V, V

GS

= 0 V,

f = 1.0 MHz

-- 2500 3250 pF

C

oss

Output Capacitance -- 900 1170 pF

C

rss

Reverse Transfer Capacitance -- 200 260 pF

Switching Characteristics

t

d(on)

Turn-On Delay Time

V

DD

= 40 V, I

D

= 90 A,

R

G

= 25

-- 30 70 ns

t

r

Turn-On Rise Time -- 360 730 ns

t

d(off)

Turn-Off Delay Time -- 100 210 ns

t

f

Turn-Off Fall Time -- 160 330 ns

Q

g

Total Gate Charge

V

DS

= 64 V, I

D

= 90 A,

V

GS

= 10 V

-- 84 110 nC

Q

gs

Gate-Source Charge -- 17 -- nC

Q

gd

Gate-Drain Charge -- 42 -- nC

Drain-Source Diode Characteristics and Maximum Ratings

I

S

Maximum Continuous Drain-Source Diode Forward Current -- -- 71 A

I

SM

Maximum Pulsed Drain-Source Diode Forward Current -- -- 284 A

V

SD

Drain-Source Diode Forward Voltage V

GS

= 0 V, I

S

= 71 A -- -- 1.5 V

t

rr

Reverse Recovery Time V

GS

= 0 V, I

S

= 90 A,

dI

F

/ dt = 100 A/s

-- 87 -- ns

Q

rr

Reverse Recovery Charge -- 265 -- nC

2000 Fairchild Semiconductor International Rev. A1, January 2001

F

Q

P

9

0

N

0

8

0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8

10

-1

10

0

10

1

10

2

175!

" Notes :

1. V

GS

=0V

2. 250#s PulseTest

25!

I

D

R

,

R

e

v

e

r

s

e

D

r

a

i

n

C

u

r

r

e

n

t

[

A

]

V

SD

, Source-Drain voltage [V]

2 4 6 8 10

10

-1

10

0

10

1

10

2

175!

25!

-55! " Notes :

1. V

DS

=30V

2. 250#s PulseTest

I

D

,

D

r

a

i

n

C

u

r

r

e

n

t

[

A

]

V

GS

, Gate-Source Voltage [V]

10

-1

10

0

10

1

10

0

10

1

10

2

V

GS

Top : 15.0 V

10.0V

8.0V

7.0V

6.0V

5.5V

5.0V

Bottom: 4.5 V

"Notes :

1. 250#s PulseTest

2. T

C

=25!

I

D

,

D

r

a

i

n

C

u

r

r

e

n

t

[

A

]

V

DS

, Drain-Source Voltage [V]

0 20 40 60 80 100

0

2

4

6

8

10

12

V

DS

= 40V

V

DS

= 64V

"Note: I

D

=90A

V

G

S

,

G

a

t

e

-

S

o

u

r

c

e

V

o

l

t

a

g

e

[

V

]

Q

G

, Total Gate Charge [nC]

10

-1

10

0

10

1

0

1000

2000

3000

4000

5000

6000

7000

C

iss

= C

gs

+ C

gd

(C

ds

= shorted)

C

oss

= C

ds

+ C

gd

C

rss

= C

gd

" Notes :

1. V

GS

= 0 V

2. f = 1 MHz

C

rss

C

oss

C

iss

C

a

p

a

c

i

t

a

n

c

e

[

p

F

]

V

DS

, Drain-Source Voltage [V]

0 100 200 300 400

0

10

20

30

40

50

" Note : T

J

= 25!

V

GS

= 20V

V

GS

= 10V

R

D

S

(

O

N

)

[

m

$

]

,

D

r

a

i

n

-

S

o

u

r

c

e

O

n

-

R

e

s

i

s

t

a

n

c

e

I

D

, Drain Current [A]

Typical Characteristics

Figure 5. Capacitance Characteristics Figure 6. Gate Charge Characteristics

Figure 3. On-Resistance Variation vs.

Drain Current and Gate Voltage

Figure 4. Body Diode Forward Voltage

Variation vs. Source Current

and Temperature

Figure 2. Transfer Characteristics Figure 1. On-Region Characteristics

2000 Fairchild Semiconductor International

F

Q

P

9

0

N

0

8

Rev. A1, January 2001

1 0

- 5

1 0

- 4

1 0

- 3

1 0

- 2

1 0

- 1

1 0

0

1 0

1

1 0

- 2

1 0

- 1

1 0

0

" N o t e s :

1 . Z

% J C

( t ) = 0 . 9 4 ! / W M a x .

2 . D u t y F a c t o r , D = t

1

/ t

2

3 . T

J M

- T

C

= P

D M

* Z

% J C

( t )

s i n g l e p u l s e

D = 0 . 5

0 . 0 2

0 . 2

0 . 0 5

0 . 1

0 . 0 1

Z

%

J

C (

t

)

,

T

h

e

r

m

a

l

R

e

s

p

o

n

s

e

t

1

, S q u a r e W a v e P u l s e D u r a t i o n [ s e c ]

25 50 75 100 125 150 175

0

20

40

60

80

I

D

,

D

r

a

i

n

C

u

r

r

e

n

t

[

A

]

T

C

, Case Temperature [!]

10

0

10

1

10

2

10

-1

10

0

10

1

10

2

10

3

10s

DC

10ms

1 ms

100 s

Operation in This Area

is Limited byR

DS(on)

" Notes :

1. T

C

= 25

o

C

2. T

J

= 175

o

C

3. Single Pulse

I

D

,

D

r

a

i

n

C

u

r

r

e

n

t

[

A

]

V

DS

, Drain-Source Voltage [V]

-100 -50 0 50 100 150 200

0.0

0.5

1.0

1.5

2.0

2.5

3.0

" Notes :

1. V

GS

=10V

2. I

D

=45A

R

D

S

(

O

N

)

,

(

N

o

r

m

a

l

i

z

e

d

)

D

r

a

i

n

-

S

o

u

r

c

e

O

n

-

R

e

s

i

s

t

a

n

c

e

T

J

, Junction Temperature [

o

C]

-100 -50 0 50 100 150 200

0.8

0.9

1.0

1.1

1.2

"Notes:

1. V

GS

=0V

2. I

D

=250#A

B

V

D

S

S

,

(

N

o

r

m

a

l

i

z

e

d

)

D

r

a

i

n

-

S

o

u

r

c

e

B

r

e

a

k

d

o

w

n

V

o

l

t

a

g

e

T

J

, Junction Temperature [

o

C]

Typical Characteristics (Continued)

Figure 9. Maximum Safe Operating Area Figure 10. Maximum Drain Current

vs. Case Temperature

Figure 7. Breakdown Voltage Variation

vs. Temperature

Figure 8. On-Resistance Variation

vs. Temperature

Figure 11. Transient Thermal Response Curve

t

1

P

DM

t

2

2000 Fairchild Semiconductor International Rev. A1, January 2001

F

Q

P

9

0

N

0

8

Charge

V

GS

10V

Q

g

Q

gs

Q

gd

3mA

V

GS

DUT

V

DS

300nF

50K$

200nF 12V

Same Type

as DUT

Charge

V

GS

10V

Q

g

Q

gs

Q

gd

3mA

V

GS

DUT

V

DS

300nF

50K$

200nF 12V

Same Type

as DUT

V

GS

V

DS

10%

90%

t

d(on)

t

r

t

on

t

off

t

d(off)

t

f

V

DD

10V

V

DS

R

L

DUT

R

G

V

GS

V

GS

V

DS

10%

90%

t

d(on)

t

r

t

on

t

off

t

d(off)

t

f

V

DD

10V

V

DS

R

L

DUT

R

G

V

GS

E

AS

= L I

AS

2

----

2

1

--------------------

BV

DSS

- V

DD

BV

DSS

V

DD

V

DS

BV

DSS

t

p

V

DD

I

AS

V

DS

(t)

I

D

(t)

Time

10V DUT

R

G

L

I

D

t

p

E

AS

= L I

AS

2

----

2

1

E

AS

= L I

AS

2

----

2

1

----

2

1

--------------------

BV

DSS

- V

DD

BV

DSS

V

DD

V

DS

BV

DSS

t

p

V

DD

I

AS

V

DS

(t)

I

D

(t)

Time

10V DUT

R

G

LL

I

D

I

D

t

p

Gate Charge Test Circuit & Waveform

Resistive Switching Test Circuit & Waveforms

Unclamped Inductive Switching Test Circuit & Waveforms

2000 Fairchild Semiconductor International

F

Q

P

9

0

N

0

8

Rev. A1, January 2001

Peak Diode Recovery dv/dt Test Circuit & Waveforms

DUT

V

DS

+

_

Driver

R

G

Same Type

as DUT

V

GS

dv/dt controlled by R

G

I

SD

controlled by pulse period

V

DD

L

I

SD

10V

V

GS

( Driver )

I

SD

( DUT )

V

DS

( DUT )

V

DD

Body Diode

Forward Voltage Drop

V

SD

I

FM

, Body Diode Forward Current

Body Diode Reverse Current

I

RM

Body Diode Recovery dv/dt

di/dt

D =

Gate Pulse Width

Gate Pulse Period

--------------------------

DUT

V

DS

+

_

Driver

R

G

Same Type

as DUT

V

GS

dv/dt controlled by R

G

I

SD

controlled by pulse period

V

DD

LL

I

SD

10V

V

GS

( Driver )

I

SD

( DUT )

V

DS

( DUT )

V

DD

Body Diode

Forward Voltage Drop

V

SD

I

FM

, Body Diode Forward Current

Body Diode Reverse Current

I

RM

Body Diode Recovery dv/dt

di/dt

D =

Gate Pulse Width

Gate Pulse Period

-------------------------- D =

Gate Pulse Width

Gate Pulse Period

--------------------------

2000 Fairchild Semiconductor International Rev. A1, January 2001

F

Q

P

9

0

N

0

8

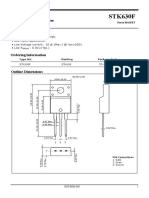

Package Dimensions

4.50 0.20 9.90 0.20

1.52 0.10

0.80 0.10

2.40 0.20

10.00 0.20

1.27 0.10

3.60 0.10

(8.70)

2

.

8

0

0

.

1

0

1

5

.

9

0

0

.

2

0

1

0

.

0

8

0

.

3

0

1

8

.

9

5

M

A

X

.

(

1

.

7

0

)

(

3

.

7

0

)

(

3

.

0

0

)

(

1

.

4

6

)

(

1

.

0

0

)

(

4

5

)

9

.

2

0

0

.

2

0

1

3

.

0

8

0

.

2

0

1

.

3

0

0

.

1

0

1.30

+0.10

0.05

0.50

+0.10

0.05

2.54TYP

[2.54 0.20]

2.54TYP

[2.54 0.20]

TO-220

2000 Fairchild Semiconductor International Rev. F1

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not

intended to be an exhaustive list of all such trademarks.

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;

NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR

INTERNATIONAL.

As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body,

or (b) support or sustain life, or (c) whose failure to perform

when properly used in accordance with instructions for use

provided in the labeling, can be reasonably expected to

result in significant injury to the user.

2. A critical component is any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or In

Design

This datasheet contains the design specifications for

product development. Specifications may change in

any manner without notice.

Preliminary First Production This datasheet contains preliminary data, and

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

Obsolete Not In Production This datasheet contains specifications on a product

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

ACEx

Bottomless

CoolFET

CROSSVOLT

DOME

E

2

CMOS

EnSigna

FACT

FACT Quiet Series

FAST

FASTr

GlobalOptoisolator

GTO

HiSeC

ISOPLANAR

MICROWIRE

OPTOLOGIC

OPTOPLANAR

POP

PowerTrench

QFET

QS

QT Optoelectronics

Quiet Series

SuperSOT-3

SuperSOT-6

SuperSOT-8

SyncFET

TinyLogic

UHC

VCX

Вам также может понравиться

- Elektronika DatasheetДокумент7 страницElektronika DatasheetproxyeaaahОценок пока нет

- Irfp 064 VДокумент9 страницIrfp 064 VPerrote PerroОценок пока нет

- F1010EДокумент8 страницF1010EKamran KhanОценок пока нет

- FQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETДокумент10 страницFQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETJavier Ayerdis NarváezОценок пока нет

- FQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETДокумент9 страницFQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETsoweloОценок пока нет

- Irfi 3205 Power MosfetДокумент9 страницIrfi 3205 Power MosfetAndy WilsonОценок пока нет

- Irfr 5305Документ11 страницIrfr 5305LucaDirafОценок пока нет

- SSP 45 N 20 AДокумент6 страницSSP 45 N 20 AJosué Daniel SotoОценок пока нет

- Fdms7670: N-Channel Powertrench MosfetДокумент7 страницFdms7670: N-Channel Powertrench MosfetDwi TjitosonОценок пока нет

- Sss7n60a TransistorДокумент6 страницSss7n60a Transistordeath914Оценок пока нет

- Generation V Technology Ultra Low On-Resistance Complimentary Half Bridge Surface Mount Fully Avalanche RatedДокумент10 страницGeneration V Technology Ultra Low On-Resistance Complimentary Half Bridge Surface Mount Fully Avalanche RatedFidel ArroyoОценок пока нет

- V R Max I: IRF1312 IRF1312S IRF1312LДокумент11 страницV R Max I: IRF1312 IRF1312S IRF1312LPanos DiamantoulakisОценок пока нет

- FQB8N60C / FQI8N60C: 600V N-Channel MOSFETДокумент9 страницFQB8N60C / FQI8N60C: 600V N-Channel MOSFETemelchor57Оценок пока нет

- FQPF8N80CДокумент11 страницFQPF8N80CWsad WsadОценок пока нет

- Irf7509 MosfetДокумент8 страницIrf7509 Mosfetnithinmundackal3623Оценок пока нет

- IRF650B / IRFS650B: 200V N-Channel MOSFETДокумент11 страницIRF650B / IRFS650B: 200V N-Channel MOSFETMiloud ChouguiОценок пока нет

- Irl 530 NДокумент9 страницIrl 530 NEric Lenin Marin MoncadaОценок пока нет

- FQP13N50C / FQPF13N50C: N-Channel QFET MosfetДокумент10 страницFQP13N50C / FQPF13N50C: N-Channel QFET MosfetFidel ArroyoОценок пока нет

- Mosfet Irf2708Документ9 страницMosfet Irf2708ferdialvascribdОценок пока нет

- IRF9540NДокумент8 страницIRF9540Nhardik_patel182000Оценок пока нет

- Fdp51N25 / Fdpf51N25 Unifet: 250V N-Channel MosfetДокумент10 страницFdp51N25 / Fdpf51N25 Unifet: 250V N-Channel MosfetJosué Daniel SotoОценок пока нет

- Irfp 460 AДокумент8 страницIrfp 460 AKasun Darshana PeirisОценок пока нет

- Irf 4905Документ9 страницIrf 4905Andre Vitor DobrychtopОценок пока нет

- Irfz 24 NДокумент9 страницIrfz 24 Njmbernal7487886Оценок пока нет

- Smps Mosfet: Irfb23N20Dpbf Irfs23N20Dpbf Irfsl23N20DpbfДокумент11 страницSmps Mosfet: Irfb23N20Dpbf Irfs23N20Dpbf Irfsl23N20DpbfΠΕΤΡΟΣ ΛΟΥΚΑΣОценок пока нет

- 5305SДокумент10 страниц5305SHugo Camacho RamirezОценок пока нет

- SFR/U9120: Advanced Power MOSFETДокумент7 страницSFR/U9120: Advanced Power MOSFETJavier BendekОценок пока нет

- Advanced Power Electronics Corp.: AP15N03H/JДокумент6 страницAdvanced Power Electronics Corp.: AP15N03H/JShezan ShaniОценок пока нет

- IRFZ34N Datasheet - KДокумент8 страницIRFZ34N Datasheet - KNairo FilhoОценок пока нет

- Ta36n30p PDFДокумент5 страницTa36n30p PDFperro sОценок пока нет

- FQD2N60C / FQU2N60C: N-Channel Qfet MosfetДокумент9 страницFQD2N60C / FQU2N60C: N-Channel Qfet MosfetTomescu MarianОценок пока нет

- IRF650B / IRFS650B: 200V N-Channel MOSFETДокумент10 страницIRF650B / IRFS650B: 200V N-Channel MOSFETbinoelОценок пока нет

- Irfp 140 NДокумент9 страницIrfp 140 NCodinasound CaОценок пока нет

- FQP6N60C/FQPF6N60C: 600V N-Channel MOSFETДокумент10 страницFQP6N60C/FQPF6N60C: 600V N-Channel MOSFETBiswajit SarkarОценок пока нет

- Irfp 90 N 20 DДокумент9 страницIrfp 90 N 20 DAndré Frota PaivaОценок пока нет

- 9N50CДокумент10 страниц9N50CtecjotaОценок пока нет

- IRF740B/IRFS740B: 400V N-Channel MOSFETДокумент11 страницIRF740B/IRFS740B: 400V N-Channel MOSFETMistery of the souldОценок пока нет

- IRF8788Документ9 страницIRF8788Robert KovacsОценок пока нет

- Datasheet IRFB11N50AДокумент8 страницDatasheet IRFB11N50AMartín SayagoОценок пока нет

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedДокумент9 страницAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedPedro Cu AguirreОценок пока нет

- FQP12N60C / FQPF12N60C: 600V N-Channel MOSFETДокумент10 страницFQP12N60C / FQPF12N60C: 600V N-Channel MOSFETJose GuerreroОценок пока нет

- FQP5N60C / FQPF5N60C: N-Channel QFET MosfetДокумент10 страницFQP5N60C / FQPF5N60C: N-Channel QFET Mosfethfog2000181Оценок пока нет

- Coolmos Power Transistor: Features Product SummaryДокумент12 страницCoolmos Power Transistor: Features Product SummarychiknaОценок пока нет

- 30V N-Channel Trench MOSFET: 30V, 50A, 8.5m : DS D GS DS (ON) GS GSДокумент7 страниц30V N-Channel Trench MOSFET: 30V, 50A, 8.5m : DS D GS DS (ON) GS GSLance WalkerОценок пока нет

- TK12A50DДокумент6 страницTK12A50DRaskipusОценок пока нет

- Irfp 260 NДокумент9 страницIrfp 260 NJolaine MojicaОценок пока нет

- 13N60 Series: N-Channel Power MOSFET 13A, 600volts DescriptionДокумент8 страниц13N60 Series: N-Channel Power MOSFET 13A, 600volts DescriptionAndres AlegriaОценок пока нет

- DatasheetДокумент7 страницDatasheetrene gonzОценок пока нет

- Irfb4020Pbf: Digital Audio MosfetДокумент8 страницIrfb4020Pbf: Digital Audio Mosfetto_netiksОценок пока нет

- Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MДокумент11 страницFdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MKevin TateОценок пока нет

- P45N02LD Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorДокумент3 страницыP45N02LD Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorAnonymous qrSsYuxyoYОценок пока нет

- Semiconductor KHB2D0N60P/F: Technical DataДокумент7 страницSemiconductor KHB2D0N60P/F: Technical DataTol SirtОценок пока нет

- Sss7n60b (7n60b) MosfetДокумент11 страницSss7n60b (7n60b) MosfetCamilo AldanaОценок пока нет

- Irfz 34 NLДокумент10 страницIrfz 34 NLguerrero_27Оценок пока нет

- 2N7000Документ7 страниц2N7000Ricardo GutierrezОценок пока нет

- Irf 540 NsДокумент11 страницIrf 540 NsLucas PascualОценок пока нет

- FDP 2614Документ8 страницFDP 2614HadeedAhmedSherОценок пока нет

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОт EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОценок пока нет

- 110 Waveform Generator Projects for the Home ConstructorОт Everand110 Waveform Generator Projects for the Home ConstructorРейтинг: 4 из 5 звезд4/5 (1)

- Activation Response For IARДокумент1 страницаActivation Response For IARHãy Cố LênОценок пока нет

- MFRC522Документ95 страницMFRC522durimukОценок пока нет

- TIP41CДокумент2 страницыTIP41CBruno NascimentoОценок пока нет

- CodeДокумент2 страницыCodeHãy Cố LênОценок пока нет

- 12Документ2 страницы12Hãy Cố LênОценок пока нет

- Chan Led 7 Doan 2 So 18 CHANДокумент2 страницыChan Led 7 Doan 2 So 18 CHANHãy Cố LênОценок пока нет

- PhatДокумент1 страницаPhatHãy Cố LênОценок пока нет

- Acr2 Cambien Dongdien - TMPДокумент2 страницыAcr2 Cambien Dongdien - TMPHãy Cố LênОценок пока нет

- Nrf24l01 2.4ghz Wireless Transceiver Module ManualДокумент43 страницыNrf24l01 2.4ghz Wireless Transceiver Module ManualmuassegafОценок пока нет

- Chan Led 7 Doan 4 SoДокумент1 страницаChan Led 7 Doan 4 SoHãy Cố LênОценок пока нет

- Sand To Silicon 22nm VersionДокумент18 страницSand To Silicon 22nm VersionDavid Rubio SaezОценок пока нет

- 9N50CДокумент10 страниц9N50CtecjotaОценок пока нет

- G. Pulla Reddy Engineering College (Autonomous) : Kurnool Department of Electrical & Electronics Engineering Power Electronics (PEP) Laboratory (Scheme-2013)Документ87 страницG. Pulla Reddy Engineering College (Autonomous) : Kurnool Department of Electrical & Electronics Engineering Power Electronics (PEP) Laboratory (Scheme-2013)Sreenath SreenathОценок пока нет

- Digital'IC Design ETIN20': Outline&Документ13 страницDigital'IC Design ETIN20': Outline&Ricardo Gómez GómezОценок пока нет

- Ec8351 Electron Devices and CircuitsДокумент1 страницаEc8351 Electron Devices and CircuitsAnonymous yO7rcec6vuОценок пока нет

- Description: 2 GBIT (256M × 8 Bit) Cmos Nand E PromДокумент65 страницDescription: 2 GBIT (256M × 8 Bit) Cmos Nand E Promsuan kwang Tan100% (1)

- MOC70P1 / MOC70P2 / MOC70P3: Phototransistor Optical Interrupter SwitchДокумент5 страницMOC70P1 / MOC70P2 / MOC70P3: Phototransistor Optical Interrupter SwitchalangoesleiteОценок пока нет

- Soluciones 9Документ4 страницыSoluciones 9manuОценок пока нет

- EE 4350 MOSFET Design Simulation IДокумент4 страницыEE 4350 MOSFET Design Simulation IalОценок пока нет

- Transistors 12700Документ4 страницыTransistors 12700randyОценок пока нет

- Assignment - 3 Hardware Design Methodology: Submitted By: Shaily Garg MEC2019010 M.Tech (MI)Документ31 страницаAssignment - 3 Hardware Design Methodology: Submitted By: Shaily Garg MEC2019010 M.Tech (MI)Shaily GargОценок пока нет

- MosfetДокумент4 страницыMosfetKunal SinghОценок пока нет

- 2SK2663 Datasheet (PDF) - Shindengen Electric MFG - Co.ltd - HVX-2 Series Power MOSFET (900V 1A)Документ12 страниц2SK2663 Datasheet (PDF) - Shindengen Electric MFG - Co.ltd - HVX-2 Series Power MOSFET (900V 1A)Pablo Acapulco GuerreroОценок пока нет

- Transistor Operation 1 PDFДокумент24 страницыTransistor Operation 1 PDFKavooОценок пока нет

- Poly To B.tech ElectronicsДокумент5 страницPoly To B.tech ElectronicsReshmi R NairОценок пока нет

- VP Operations Semiconductor Engineering in Silicon Valley CA Resume Jay KumarДокумент3 страницыVP Operations Semiconductor Engineering in Silicon Valley CA Resume Jay KumarJayKumar1Оценок пока нет

- TD 62305Документ9 страницTD 62305hassanОценок пока нет

- Transistor MOSFET - STK630Документ3 страницыTransistor MOSFET - STK630David Jonatan Alayo LlajarunaОценок пока нет

- Datasheet IRF840 MOSFET LabДокумент7 страницDatasheet IRF840 MOSFET LabEdwin FlorezОценок пока нет

- Microelectronics Reliability: Yong LiuДокумент8 страницMicroelectronics Reliability: Yong Liu李云龙Оценок пока нет

- NPN Epitaxial Silicon TransistorДокумент5 страницNPN Epitaxial Silicon TransistorMugurel LupuОценок пока нет

- Making The Move From 28Nm To 16Nm Finfet - Easy As Pop: JC Yu Technical Marketing Manager Physical Design GroupДокумент21 страницаMaking The Move From 28Nm To 16Nm Finfet - Easy As Pop: JC Yu Technical Marketing Manager Physical Design GroupPhạm Đức ThuậnОценок пока нет

- Datasheet Sustituto en Placa Orig de ChinaДокумент3 страницыDatasheet Sustituto en Placa Orig de ChinaVictor PerezОценок пока нет

- Technical Answers For Real World Problems (TARP) Assignment-7Документ3 страницыTechnical Answers For Real World Problems (TARP) Assignment-7Anup PatelОценок пока нет

- Difference Between Power and Small Signal DiodeДокумент4 страницыDifference Between Power and Small Signal DiodeMohamed IbrahemОценок пока нет

- SYLLABUSДокумент2 страницыSYLLABUSDr-Asit Kumar ParidaОценок пока нет

- Power Transistor ( 40V, 2A) : 2SB1183 / 2SB1239Документ1 страницаPower Transistor ( 40V, 2A) : 2SB1183 / 2SB1239Angel Simo MoralesОценок пока нет

- ME442 Chapter3Документ72 страницыME442 Chapter3AlanОценок пока нет

- ELTR - 353 - Power Electronics PDFДокумент156 страницELTR - 353 - Power Electronics PDFEngr Shehzad HaneefОценок пока нет

- Changes in Non Volatile Memory Qualification MethodsДокумент20 страницChanges in Non Volatile Memory Qualification MethodsbilllanadeОценок пока нет