Академический Документы

Профессиональный Документы

Культура Документы

Path Sensitization

Загружено:

vinovictory8571Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Path Sensitization

Загружено:

vinovictory8571Авторское право:

Доступные форматы

Lecture 5 Test Pattern Generation

Functional vs. Structural

Definition and Types

Path sensitization method

ATPG for Sequential

Circuits

Functional vs. Structural ATPG

Functional ATPG

generate complete set of tests for

circuit input-output combinations

129 inputs, 65 outputs:

2

129

=

680,564,733,841,876,926,926,749,

214,863,536,422,912

patterns

Using 1 GHz ATE, would take

2.15 x 10

22

years

Sum and Carry Circuits

Structural test:

No redundant adder hardware, 64 bit slices

Each with 27 faults (using fault equivalence)

At most 64 x 27 = 1728 faults (tests)

Takes 0.000001728 s on 1 GHz ATE

Designer gives small set of functional tests

augment with structural tests to boost coverage to

98

+

%

Functional vs. Structural (Contd)

Definition of Automatic Test-Pattern

Generator

Operations on digital hardware:

Inject fault into circuit modeled in computer

Use various ways to activate and propagate fault effect through

hardware to circuit output

Output flips from expected to faulty signal

Test generation cost

fault-dependent or not

Quality of generated test

fault coverage (fault simulation)

Test application cost

test time, memory requirements

TG Types

Exhaustive

cheap generation, high FC, expensive application

Fault-Oriented (deterministic)

expensive generation, possibly high FC, cheaper

application

Random (pseudo-random)

cheap generation, low FC, + - expensive application

Exhaustive Algorithm

For n-input circuit, generate all 2

n

input

patterns

Unfeasible, unless circuit is partitioned into

cones of logic, with 15 inputs

Perform exhaustive ATPG for each cone

Misses faults that require specific activation

patterns for multiple cones to be tested

Pseudo-Exhaustive Method

Partition large circuit into fanin cones

Backtrace from each PO to PIs influencing it

Test fanin cones in parallel

Reduced #of tests from 2

8

= 256 to 2

5

x 2 = 64

Incomplete fault coverage

Pseudo-Exhaustive Pattern Generation

Random-Pattern Generation

Random-Pattern Generation

Flow chart for

method

Use to get

tests for 60-

80% of faults,

then switch to

deterministic

ATPG for rest

Random Pattern Testing

Bottom:

Random-

Pattern

Resistant

circuit

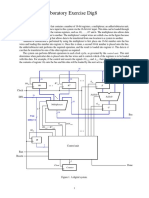

Path Sensitization Method

Path Sensitization Method

1 Fault Sensitization (activation)

2 Fault Propagation

3 Line J ustification

Path Sensitization Method

Fault l s-a-v

Activation

set l to v

Propagation

find a path from l to a primary output that keeps

faulty value

J ustification

set the primary inputs to activate the fault

Composite Logic Values

consider line value for original AND faulty

circuit

v/v

f

= original/faulty

Symbols D and D (Roth, 1966)

D = 1/0

D = 0/1

0 = 0/0

1 = 1/1

Operations on Composite Values

D + 0 = 0/1 + 0/0 = 0/1 = D

V/V

f

0/0 0

1/1 1

1/0 D

0/1 D

AND 0 1 D D X

0 0 0 0 0 0

1 0 1 D D X

D 0 D D 0 X

D 0 D 0 D X

X 0 X X X x

Path Sensitization Method

Path Sensitization Method

1

Propagation

D

Path Sensitization Method

Path Sensitization Method

Propagation: try path f h k L

1

D

D

D

D

0

1

1

Path Sensitization Method

Path Sensitization Method

Propagation: try path f h k L

1

D

D

D

D

0

1

1

Path Sensitization Method

Path Sensitization Method

J ustification: Try path f h k L blocked

at j, since there is no way to justify the 1 on i

1

0

D

D

1

1

1

D

D

D

Path Sensitization Method

Path Sensitization Method

J ustification: Try path f h k L blocked

at j, since there is no way to justify the 1 on i

1

D

D

D

1

1

D

D

1

1

1

Path Sensitization Method

Path Sensitization Method

Backtracking!

1

D

D

D

1

1

D

D

1

1

1

X

X

X

X

X

X

X

X

Try other propagation: path g i j k L

0

D

D

D

1

D

D

1

1

Path Sensitization Method

D

Try other propagation: path g i j k L

0

D

D

D

1

D

D

1

1

Path Sensitization Method

D

Try other propagation: path g i j k L

0

D

D

D

1

D

D

1

0

1

Path Sensitization Method

D

Major Combinational Automatic

Test-Pattern Generation Algorithms

D-Algorithm (Roth) -- 1966

PODEM (Goel) -- 1981

FAN (Fujiwara and Shimono) --1983

Sequential Circuit ATPG

Time-Frame Expansion

Problem of sequential circuit ATPG

Time-frame expansion

Example of Sequential Circuit

CB

MB

Sequential Circuits

A sequential circuit has memory in addition to

combinational logic.

Test for a fault in a sequential circuit is a

sequence of vectors, which

Initializes the circuit to a known state

Activates the fault, and

Propagates the fault effect to a primary output

Methods of sequential circuit ATPG

Time-frame expansion methods

Simulation-based methods

Extended D-Algorithm

1. Pick up a target fault f.

2. Create a copy of a combinational logic, set it

time-frame 0.

3. Generate a test for f using D-algorithm for time-

frame 0.

4. When the fault effect is propagate to the DFFs,

continue fault propagation in the next time-frame.

5. When there are values required in the DFFs,

continue the justification in the previous time-frame.

Example for Extended D- Algorithm

st_1

Example: Step 1

Example: Step 2

Example: Step 3

Summary

Summary

Hierarchical ATPG -- 9 Times speedup (Min)

Handles adders, comparators, MUXes

Advances over D-algorithm

Results of 40 years research mature methods:

Path sensitization

Simulation-based

Boolean satisfiability and neural networks

Genetic algorithms

Вам также может понравиться

- Scan Path DesignДокумент54 страницыScan Path DesignGowtham HariОценок пока нет

- Static Timing Analysis - SureshДокумент33 страницыStatic Timing Analysis - SureshSuresh BharathОценок пока нет

- Lecture 2 Verilog PDFДокумент35 страницLecture 2 Verilog PDFkayleОценок пока нет

- Programming With Awk and PerlДокумент4 страницыProgramming With Awk and PerlUjjwal PradhanОценок пока нет

- Io MultiplexingДокумент19 страницIo Multiplexingsubramanyam62Оценок пока нет

- Verilog Operators Part-IДокумент5 страницVerilog Operators Part-IsenthilОценок пока нет

- Digital VLSI Design Lecture 3: Logic Synthesis: Semester A, 2018-19 Lecturer: Dr. Adam TemanДокумент47 страницDigital VLSI Design Lecture 3: Logic Synthesis: Semester A, 2018-19 Lecturer: Dr. Adam TemansrajeceОценок пока нет

- Timing Paths Static Timing Analysis STA Basic Part 1 VLSI Concepts PDFДокумент10 страницTiming Paths Static Timing Analysis STA Basic Part 1 VLSI Concepts PDFravishopingОценок пока нет

- D2A1-1-3-DV VCD Based Power SignoffДокумент17 страницD2A1-1-3-DV VCD Based Power SignoffRaj Shekhar ReddyОценок пока нет

- FifoДокумент5 страницFifoVenky KoolchipОценок пока нет

- Unix Basics and TCL ScriptingДокумент49 страницUnix Basics and TCL ScriptingTaha PerwaizОценок пока нет

- Dynamic Vs Static Timing AnalysisДокумент4 страницыDynamic Vs Static Timing AnalysismturadagiОценок пока нет

- JTAG TutorialДокумент6 страницJTAG Tutorialmrunal1729Оценок пока нет

- Stuck at FaultДокумент6 страницStuck at Faultamy2chang_1Оценок пока нет

- OpenSTA TutorialДокумент57 страницOpenSTA TutorialAbhinav VarakanthamОценок пока нет

- Question / Answer: 1. What Is Synthesis Process ?Документ6 страницQuestion / Answer: 1. What Is Synthesis Process ?Meet ZankatОценок пока нет

- Apb Protocal: Presented By, Sulthana ShaikДокумент26 страницApb Protocal: Presented By, Sulthana ShaikJerin VargheseОценок пока нет

- Recovery and Removal TimeДокумент3 страницыRecovery and Removal TimeSwapnil RawatОценок пока нет

- System Verilog TrainingДокумент2 страницыSystem Verilog TrainingVlsi GuruОценок пока нет

- Es Zg532 - Testability of Vlsi DesignДокумент7 страницEs Zg532 - Testability of Vlsi DesignvithyaОценок пока нет

- CompressionДокумент45 страницCompressionRajesh DurisalaОценок пока нет

- VLSI Basics - VLSI Design FlowДокумент5 страницVLSI Basics - VLSI Design Flowsrinivas525Оценок пока нет

- Real-Time System AssignmentДокумент4 страницыReal-Time System AssignmentTommy Kyen'de BilОценок пока нет

- Introduction To VHDLДокумент88 страницIntroduction To VHDLpusd_90Оценок пока нет

- Tap ControllerДокумент16 страницTap ControllerMoin PashaОценок пока нет

- Tetramax DF DsДокумент4 страницыTetramax DF DsBrijesh S DОценок пока нет

- Implementation of PODEM Algorithm: OutlineДокумент2 страницыImplementation of PODEM Algorithm: OutlineNivin PaulОценок пока нет

- System Verilog: Program Block & InterfaceДокумент38 страницSystem Verilog: Program Block & InterfaceMeghana VeggalamОценок пока нет

- Timing Paths: Timing Analysis Is Performed by Splitting The Design Into Different Paths Based OnДокумент3 страницыTiming Paths: Timing Analysis Is Performed by Splitting The Design Into Different Paths Based OnNandaОценок пока нет

- Jtag - AN IEEE 1149.1 STDДокумент42 страницыJtag - AN IEEE 1149.1 STDkanchanstiwariОценок пока нет

- Clock Domain Crossing Issues &Документ35 страницClock Domain Crossing Issues &Nishanth Gowda100% (1)

- C C C C CC C: C C C CДокумент4 страницыC C C C CC C: C C C CRishav HarshОценок пока нет

- Chapter2 Clocks Resets-04Документ8 страницChapter2 Clocks Resets-04hardeepОценок пока нет

- Notes3 PDFДокумент97 страницNotes3 PDFrahulsportyОценок пока нет

- Guidelines For Design Synthesis Using Synopsys Design Compiler Design SynthesisДокумент13 страницGuidelines For Design Synthesis Using Synopsys Design Compiler Design Synthesisnishad_86Оценок пока нет

- Ring Oscillator IssueДокумент2 страницыRing Oscillator IssueAnonymous Mw7ZFF3A3Оценок пока нет

- Digital Interview QuestionsДокумент9 страницDigital Interview Questionsselvi0412Оценок пока нет

- 03-Verilog Modules and Ports-MergedДокумент170 страниц03-Verilog Modules and Ports-MergedqwertyОценок пока нет

- Logic Circuits Midterm ReviewerДокумент38 страницLogic Circuits Midterm ReviewerHector Ledesma IIIОценок пока нет

- Design of Power Efficient Posit Multiplier Using Compressor Based AdderДокумент8 страницDesign of Power Efficient Posit Multiplier Using Compressor Based AdderIJRASETPublicationsОценок пока нет

- VLSI Physical Design - Physical Design Interview Question Part 2Документ2 страницыVLSI Physical Design - Physical Design Interview Question Part 2srinathОценок пока нет

- Introduction To SynthesisДокумент39 страницIntroduction To SynthesisJayanth bemesettyОценок пока нет

- Digital Design FlowДокумент71 страницаDigital Design FlowSanjuОценок пока нет

- TP Ansys Redhawk PDFДокумент4 страницыTP Ansys Redhawk PDFEkansh DadheechОценок пока нет

- TCL Awk Xgraph BasicsДокумент73 страницыTCL Awk Xgraph BasicsVinay ChalluruОценок пока нет

- Lab2 Logic Synthesis With Design Compiler - New PDFДокумент26 страницLab2 Logic Synthesis With Design Compiler - New PDF陳美如Оценок пока нет

- Lab1 DC Tmax 2012 1217 v1Документ43 страницыLab1 DC Tmax 2012 1217 v1jasonturfОценок пока нет

- Delays in Asic DesignДокумент17 страницDelays in Asic DesignJayanth bemesettyОценок пока нет

- Transition Delay Fault Brad Hill ELEC 7250 April 13, 2006Документ6 страницTransition Delay Fault Brad Hill ELEC 7250 April 13, 2006pravallika vysyarajuОценок пока нет

- Testability in EOCHL (And Beyond ) : Vladimir ZivkovicДокумент24 страницыTestability in EOCHL (And Beyond ) : Vladimir ZivkovicsenthilkumarОценок пока нет

- Lesson8 CMOS GatesДокумент33 страницыLesson8 CMOS GatestienchuanОценок пока нет

- Class 12 TopicsДокумент43 страницыClass 12 Topicsgideontargrave7Оценок пока нет

- Formality Basic Lab InstructionДокумент9 страницFormality Basic Lab InstructionhardeepОценок пока нет

- Lec4 VerilogДокумент58 страницLec4 VerilogRohit BhelkarОценок пока нет

- Texas Instruments Placement Paper May 2011Документ5 страницTexas Instruments Placement Paper May 2011Shayendra RajuОценок пока нет

- Table of Contents: The IDDQ MysteryДокумент9 страницTable of Contents: The IDDQ MysteryShweta SinhaОценок пока нет

- Basic Timing Constraints TutorialДокумент34 страницыBasic Timing Constraints Tutorialapi-3737190100% (3)

- Simulation in SimvisionДокумент2 страницыSimulation in SimvisionIliyasMohammedОценок пока нет

- Sram Part1Документ36 страницSram Part1api-285860375Оценок пока нет

- Electronics and Microprocessor May2014 QP PDFДокумент2 страницыElectronics and Microprocessor May2014 QP PDFvinovictory8571Оценок пока нет

- Choose To BelieveДокумент62 страницыChoose To Believevinovictory857175% (4)

- Micro Processor and Microcontroller ND 2014Документ2 страницыMicro Processor and Microcontroller ND 2014vinovictory8571Оценок пока нет

- Question Paper Code: 31364Документ3 страницыQuestion Paper Code: 31364vinovictory8571Оценок пока нет

- Nptel: NOC:Electromagnetic Theory - Video CourseДокумент1 страницаNptel: NOC:Electromagnetic Theory - Video Coursevinovictory8571Оценок пока нет

- Mpandmc ND 2012Документ2 страницыMpandmc ND 2012vinovictory8571Оценок пока нет

- ME2401 Mechatronics NotesДокумент99 страницME2401 Mechatronics NotesVijayasuthaJero0% (1)

- Mechtronics NeedДокумент21 страницаMechtronics Needvinovictory8571Оценок пока нет

- Privacy-Preserving Location-Based On-Demand Routing in MANETsДокумент16 страницPrivacy-Preserving Location-Based On-Demand Routing in MANETsvinovictory8571Оценок пока нет

- Ec6304 Ec1 April May 2015Документ8 страницEc6304 Ec1 April May 2015vinovictory8571Оценок пока нет

- ADSP7Документ3 страницыADSP7Raj KumarОценок пока нет

- MSM ApproachДокумент10 страницMSM Approachvinovictory8571Оценок пока нет

- AASR Authenticated Anonymous Secure Routing For MANETs in Adversarial EnvironmentsДокумент9 страницAASR Authenticated Anonymous Secure Routing For MANETs in Adversarial Environmentsvinovictory8571Оценок пока нет

- AASR Authenticated Anonymous Secure Routing For MANETs in Adversarial EnvironmentsДокумент9 страницAASR Authenticated Anonymous Secure Routing For MANETs in Adversarial Environmentsvinovictory8571Оценок пока нет

- Design and Implementation of Reconfigurable Alu On FpgaДокумент4 страницыDesign and Implementation of Reconfigurable Alu On FpgajeetendrasidhiОценок пока нет

- VerilogPresent-v1 3Документ77 страницVerilogPresent-v1 3Gowthami NagarajОценок пока нет

- Security Enhancements For Mobile Adhoc Networks With Trust Management Using Uncertain ReasoningДокумент12 страницSecurity Enhancements For Mobile Adhoc Networks With Trust Management Using Uncertain Reasoninglogu_thalirОценок пока нет

- Risk-Aware Mitigation For MANET Routing AttacksДокумент12 страницRisk-Aware Mitigation For MANET Routing Attacksvinovictory8571Оценок пока нет

- M.E Time Table-2014Документ74 страницыM.E Time Table-20146karthikrec_79324597Оценок пока нет

- Microcontroller Based Speed Cntrol SystemДокумент3 страницыMicrocontroller Based Speed Cntrol Systemvinovictory8571Оценок пока нет

- Manets - Applications and ChallengesДокумент14 страницManets - Applications and Challengesvinovictory8571Оценок пока нет

- AASR Authenticated Anonymous Secure Routing For MANETs in Adversarial EnvironmentsДокумент5 страницAASR Authenticated Anonymous Secure Routing For MANETs in Adversarial Environmentsvinovictory8571Оценок пока нет

- M.E Time Table-2014Документ74 страницыM.E Time Table-20146karthikrec_79324597Оценок пока нет

- AlarmДокумент14 страницAlarmShanmugasundaram MuthuswamyОценок пока нет

- Delay Reliability and Trust in MANETsДокумент153 страницыDelay Reliability and Trust in MANETsvinovictory8571Оценок пока нет

- Advisor KiyosakiДокумент5 страницAdvisor KiyosakiPrince A-oneОценок пока нет

- Trading For A Living - A. ElderДокумент312 страницTrading For A Living - A. Eldercatta_00Оценок пока нет

- 07 Boolean Testing Using Fault ModelsДокумент16 страниц07 Boolean Testing Using Fault Modelsdayas1979Оценок пока нет

- Department of Ece, Adhiparasakthi College of Engineering, KalavaiДокумент31 страницаDepartment of Ece, Adhiparasakthi College of Engineering, KalavaiGiri PrasadОценок пока нет

- Combinational Circuits: Multiplexers Question Solving-IДокумент8 страницCombinational Circuits: Multiplexers Question Solving-IAnulekha SahaОценок пока нет

- Set 1 AnswersДокумент22 страницыSet 1 AnswersgokulchandruОценок пока нет

- Assignment 1Документ2 страницыAssignment 1Game Lone DocОценок пока нет

- Micro Holtek 48R50A-1Документ39 страницMicro Holtek 48R50A-1GlennОценок пока нет

- GFK-1504N - VersaMax User Manual PDFДокумент521 страницаGFK-1504N - VersaMax User Manual PDFgauravtrivedi77Оценок пока нет

- Last Lecture: Introduction To Sequential Logic and SystemsДокумент9 страницLast Lecture: Introduction To Sequential Logic and SystemsSatya RajОценок пока нет

- Modify A USB KKL 409.1 Vagcom Cable For BMW Bike K-LineДокумент4 страницыModify A USB KKL 409.1 Vagcom Cable For BMW Bike K-LinePatrick Stivén50% (2)

- FPGAДокумент47 страницFPGAtulasiОценок пока нет

- GPGPU Sim TutorialДокумент28 страницGPGPU Sim TutorialMohan Kumar NОценок пока нет

- Datapath Design: Fixed-Point ArithmeticДокумент4 страницыDatapath Design: Fixed-Point ArithmeticAnneОценок пока нет

- Unit 4 Part 1 MicroprocessorДокумент14 страницUnit 4 Part 1 MicroprocessorMuthu KumaranОценок пока нет

- Ti 28335 DSKДокумент1 страницаTi 28335 DSKankit1979Оценок пока нет

- 512K (64K X 8) Otp Eprom AT27C512R: FeaturesДокумент12 страниц512K (64K X 8) Otp Eprom AT27C512R: FeaturesAndrea MartinezОценок пока нет

- BSC (Hons) Electronics Computer Science - E33Документ7 страницBSC (Hons) Electronics Computer Science - E33kriskl03Оценок пока нет

- CA 2mark and 16 Mark With AnswerДокумент109 страницCA 2mark and 16 Mark With AnswerJagadeesh Mohan100% (1)

- Smart Lock 400Документ16 страницSmart Lock 400Kelvin LoОценок пока нет

- Laboratory Exercise D: R0, - . - , R7 and A. The Multiplexer Also Allows DataДокумент6 страницLaboratory Exercise D: R0, - . - , R7 and A. The Multiplexer Also Allows DataMunya RushambwaОценок пока нет

- OpenWrt USB Print StorageДокумент2 страницыOpenWrt USB Print StoragefatadefacebookОценок пока нет

- CPU945 6ES5998-3UF21 06 e OCR PDFДокумент673 страницыCPU945 6ES5998-3UF21 06 e OCR PDFfabyanoОценок пока нет

- LAB 11 8051 Interrupt ProgrammingДокумент14 страницLAB 11 8051 Interrupt ProgrammingHamza NasirОценок пока нет

- EC6711-Embedded Laboratory Uploaded by PRABHU.SДокумент66 страницEC6711-Embedded Laboratory Uploaded by PRABHU.Sprabhu s100% (2)

- Scheme Asus z99d PDFДокумент94 страницыScheme Asus z99d PDFЮра ИвановОценок пока нет

- What Are The Different Motherboard Components and Their Functions PDFДокумент4 страницыWhat Are The Different Motherboard Components and Their Functions PDFMaria Norberta MandacОценок пока нет

- Downloaded From Manuals Search EngineДокумент99 страницDownloaded From Manuals Search EngineBill DikОценок пока нет

- Eoc ProjectДокумент27 страницEoc ProjectJainithisshОценок пока нет

- PC Standards: Bigelow / Troubleshooting, Maintaining & Repairing Pcs / Bigelow / 3272-8 / Chapter CДокумент2 страницыPC Standards: Bigelow / Troubleshooting, Maintaining & Repairing Pcs / Bigelow / 3272-8 / Chapter CkumararguruОценок пока нет

- Parul University: Pin Diagram of 8086Документ14 страницParul University: Pin Diagram of 8086Lakshmi KumariОценок пока нет

- Peripherals of A ComputerДокумент16 страницPeripherals of A ComputerAkmal HishamОценок пока нет

- 03N - Top Level View of Computer Function and InterconnectionДокумент38 страниц03N - Top Level View of Computer Function and InterconnectionDoc TelОценок пока нет

- SIT111 2.2C TaskSheetДокумент2 страницыSIT111 2.2C TaskSheetkunal20002005Оценок пока нет