Академический Документы

Профессиональный Документы

Культура Документы

Design Guide For Atmel's C51 Standard Devices

Загружено:

Neelakanta Kalla0 оценок0% нашли этот документ полезным (0 голосов)

23 просмотров21 страницаDesign Guide

for Atmel 8xC51 Standard Devices

Оригинальное название

Doc 7764

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документDesign Guide

for Atmel 8xC51 Standard Devices

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

23 просмотров21 страницаDesign Guide For Atmel's C51 Standard Devices

Загружено:

Neelakanta KallaDesign Guide

for Atmel 8xC51 Standard Devices

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 21

Design Guide

for Atmels C51 Standard Devices

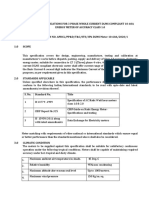

Introduction

The aim of this document is to help customers to avoid errors that are frequently done

in order save efforts and time during hardware debugging sessions.

This document relates only to Atmels C51 standard devices. It is the responsability of

the user to read the datasheet of his own device and check if the features and proce-

dures described here are applicable.

Abbreviations

ISP: In-System Programming

FLIP: FLexible In-system Programmer

GUI: Graphical User Interface

BLJB: Boot Loader Jump Bit

HPC: High Pin Count

LPC: Low Pin Count

HSB: Hardware Security Byte

Application Notes used as references

How to calculate the capacitor of the reset input of a

C51 microcontroller

(doc 4284.pdf)

External Brown-out Protection for C51

microcontrollers with Active High Reset Input

(doc 4183.pdf)

How to use a third Overtone crystal with a 80C51

family microcontroller

(doc397c496b2072e.pdf)

C51 MCUs

7764A805111/07

2

7764A805111/07

1. Basics of ATMELs C51 Standard devices

1.1 Program memory configurations

1.1.1 Scope

Figure 1-1. Code fetched from external program memory

Figure 1-2. Code fetched from internal program memory

External program memory

Standard C51

P2

P0

AD7:0

A15:8

A7:0

A15:8

D7:0

A7:0

ALE

Latch

OE /PSEN

GND

EA

P2

P0

ALE

EA

VCC Standard C51

/PSEN

VCC

VCC

10K

Table 1-1. Pin description

PIN I/O External Code Internal Code

EA Input Must be connected to GND

Must be connected to VCC, directly or through a

10K resistor.

ALE

Output

signal

This signal is used to clock the Least Significant Byte into the

address latch.

Not used.

Must be left unconnected in normal operation

PSEN

Output

signal

This signal is used to strobe the external program memory

when the MCU fetches the code byte.

Not used.

Must be left unconnected in normal operation

P0

I/O

port

Port 0 serves as a multiplexed address/data bus. It emits the

low byte of the Program Counter (PCL) as an address, and

then goes into a float state awaiting the arrival of the code

byte from the Program Memory.

Can be used as a general purpose I/O port. In

this case external 10K pull-ups must be

provided.

P2

I/O

port

Port 2 emits the high byte of the Program Counter (PCH)

Can be used as a general purpose I/O port.

No external pull-ups are needed as this port

owns internal pull-ups

3

7764A805111/07

1.1.2 Type of package

In most of the products, two kind of packages are proposed: the HPC (High Pin Count) and the

LPC (Low Pin Count).

The HPC packages support the external code and therefore provide the appropriate pins (EA,

ALE, PSEN, P0, P2), while the LPC packages do not support the external code and do not pro-

vide any of the dedicated pins.

1.1.3 Hardware Security Byte (HSB)

1.1.4 Reduced EMI Mode

The ALE signal is used to demultiplex address and data buses on port 0 when used with exter-

nal program or data memory. Nevertheless, during internal code execution, ALE signal is still

generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer

output but remains active during MOVX and MOVC instructions and external fetches. During

ALE disabling, ALE pin is weakly pulled high.

1.2 Hardware reset

1.2.1 Internal features

Some C51 devices may implement the following features:

Power On Reset (POR)

Power Fail Detector (PFD)

Hardware Watch-Dog Timer (WDT)

Internal Pull-up on reset pin

There are different ways to drive the reset pin depending on which features are implemented in

the device. The user is invited to carefully read the product datasheet to know which features are

or are not implemented.

WARNING

Parts are delivered by default with HSB set to maximum security (see product datasheet for

further information). This configuration prevents the MCU from fetching external code.

On ROM products the user will need to take care about the HSB configuration at the time he

orders the mask ROM if the external code mode is needed on his application.

On FLASH products the user will need to perform a full chip erase by means of an external

programmer before using the parts if the external code mode is needed on his application.

4

7764A805111/07

Figure 1-3. Reset bock diagram

Watch Dog

RST

Internal Reset

Timer

Microcontroller

Vcc

C51

Core

POR

PFD

Table 1-2. Features descriptions

Feature Description Impact on RST pin

PFD

The role of the PFD is to monitor the power supply drops during a steady state

condition in order to suspend the microcontrollers activity. When the PFD is

active, it holds the MCU under a reset state to prevent the MCU from having

unpredictable behaviour.

Optional feature

While the PFD is active, the reset pin

is driven by the PFD.

POR

The role of the POR is to monitor the rising of internal power supply of the

microcontroller core. It releases the internal reset only when the internal

voltage is enough for the core to operate.

Optional feature

- No external components or

superviser devices are needed to

drive the reset pin

- While the POR is active, the reset pin

is driven by the POR

- RST pin may be left unconnected

WDT

The WDT automatically resets the chip if the software fails to reset the WDT

before the selected time interval has elapsed.

Basic feature of C51 devices

While the WDT is active, the reset pin

is driven by the WDT.

Internal

Pull-up

Saves an external component No external pull-up needed

5

7764A805111/07

Figure 1-4. Behaviour of POR and PFD

VCore

t

Internal

VPFDP

VPFDM

1

0

P

O

R

P

O

R

P

F

D

Reset

Active

Not active

6

7764A805111/07

1.2.2 How to drive the RST pin according to the features implemented on the device

This procedure is only applicable to Active High reset pins. However, this procedure can be eas-

ily adapted for microcontrollers with Active Low Reset pins.

1.2.2.1 POR not implemented

When the POR is not implemented, it is necessary to implement external components to assure

a correct reset of the MCU.

a) Using an external capacitor

Read application note How to calculate the capacitor of the reset input of a C51 microcontrol-

ler (doc 4284).

Internal pull-up

External Pull-up

RST

Internal Reset

Microcontroller

C

R

VCC

RST

Internal Reset

Microcontroller

C

R

VCC

7

7764A805111/07

b) Using an external Brown-out device

Read application note External Brown-out Protection for C51 microcontrollers with Active High

Reset Input (doc 4183).

Sometimes the RST pin may be internally forced by the WDT so that the external peripherals if

any are reset at the same time as the MCU. While the WDT is active the RST pin operates as an

output. Therefore the RST pin cannot be externally forced to a permanent level. If the external

Brown-out device operates in this way, an intermediate resistor Rint or a diode must be imple-

mented between the Brown-out device and the RST pin.

Brown-out device with an intermediate resistor

Brown-out device with a diode

RST

Internal Reset

Microcontroller

R

Brown-out

device

To other on-board

circuitry

Watchdog

Timer

Rint

VCC

RST

Internal Reset

Microcontroller

R

Brown-out

device

To other on-board

circuitry

Watchdog

Timer

1N4148

VCC

8

7764A805111/07

1.2.2.2 POR implemented

When the POR is implemented, the use of external components is optional.

The RST pin may be left unconnected.

a) No external components used

b) Using an external capacitor

RST

Internal Reset

Microcontroller

R

VCC

Power Fail

Detector

Watchdog

Timer

Power On

Reset

RST

Internal Reset

Microcontroller

R

Power Fail

Detector

Watchdog

Timer

Power On

Reset

C

VCC

9

7764A805111/07

c) Using an external Brown-out device

Read application note External Brown-out Protection for C51 microcontrollers with Active High

Reset Input (doc 4183).

Sometimes the RST pin may be internally forced by the POR or the PFD or the WDTso that the

external peripherals if any are reset at the same time as the MCU. While the POR or the PFD or

the WDT are active the RST pin operates as an output. Therefore the RST pin cannot be exter-

nally forced to a permanent level. If the external Brown-out device operates in this way, an

intermediate resistor Rint or a diode must be implemented between the Brown-out device and

the RST pin.

Brown-out device with an intermediate resistor

Brown-out device with a diode

RST

Internal Reset

Microcontroller

R

Brown-out

device

To other on-board

circuitry

Rint

Power Fail

Detector

Watchdog

Timer

Power On

Reset

VCC

RST

Internal Reset

Microcontroller

R

Brown-out

device

To other on-board

circuitry

1N4148

Power Fail

Detector

Watchdog

Timer

Power On

Reset

VCC

10

7764A805111/07

1.3 Oscillator circuit

The on-chip oscillator is composed of a single-stage inverter and a parallel feedback resistor.

The XTAL1 and XTAL2 pins are respectively the input and the output of the inverter, which can

be configured with off-chip components as a Pierce oscillator.

Figure 1-5. Oscillator Schematic

CL: load capacitance given by crystals manufacturer

CI: internal capacitance of the MCU (given by the product datasheet)

CS: Stray capacitance of the circuit board

C1, C2: external capacitors

We have the following equation: CL = (C1xC2)/(C1+C2)+CI+CS

If C1=C2=CF and CS is negligible then CL = CF/2+CI and CF=2x(CL-CI)

Feedback

Resistor

XTAL1 XTAL2

GND GND

Microcontroller

C1 C2

To internal

clock circuitry

Crystal

11

7764A805111/07

1.3.1 Test conditions

It is recommended to monitor the clock on XTAL2 pin.

Special care must be taken when measuring XTAL1 signal. A high impedance probe must be

used to avoid any distorsion of the signal.

Test condition: probes impedance > 1 MOhm

This means that oscilloscopes active probes are prohibited due to their weak impedance (usu-

ally around 100KOhm)

1.3.2 Relationship between oscillator and ALE frequencies

Output pulse for latching the low byte of the address during an access to external memory. In

normal operation, ALE is emitted at a constant rate of the oscillator frequency and can be used

for external timing or clocking.

Note that one ALE pulse is skipped during each access to external data memory.

ALE can be disabled by setting SFRs AUXR.0 bit. When this bit is set, ALE will be inactive dur-

ing internal fetches.

XTAL1 XTAL2

Microcontroller

High impedance probe

MCUs Clock mode ALE frequency

X1 mode Freq(ale) = Freq(osc )/6

X2 mode Freq(ale) = Freq(osc )/3

12

7764A805111/07

1.3.3 Overtone crystals

Problem: Sometimes overtone crystals are used with a standard oscillator circuit where a spe-

cific one is required to make the crystal to oscillate on its third overtone.

Consequence: an overtone crystal used with a standard oscillator circuit, oscillates on its funda-

mental frequency instead of oscillating on its third overtone frequency. The clock frequency seen

by the MCU is 1/3 of the expected frequency.

Action: check the type of the crystal you are using. If you really want to use an overtone crystal,

apply one of the following solutions.

1. A resistor of 3.9K between Xtal1 et Xtal2, a cap of 4.7 pF between Xtal1 and Vss, and a

cap of 15pF between Xtal2 and Vss

2. Read application note How to use a third Overtone crystal with a 80C51 family micro-

controller (doc397c496b2072e.pdf). Apply the following component values :

L1= 1.5 H

C3=4.7nF

CP1=12pF

CP2=27pF

C2 : not needed

3. Same solution as number 2 except the LC network is, in this case, connected to Xtal1 :

L1= 1.5 H

C3=4.7nF

CP1=10pF

CP2=10pF

Feedback

Resistor

XTAL1 XTAL2

GND GND

Microcontroller

4.7pF 15pF

To internal

clock circuitry

3.9K

Crystal

Overtone

13

7764A805111/07

1.4 Microcontroller status

During hardware or firmware debugging, it is sometimes interesting to know what the state of the

microcontroller is. See table below for details.

Note: Port 0 can force a 0 level. A "one" will leave port floating.

Hardware

conditions Microcontroller status

RST EA ALE PSEN XTAL2 Mode P0 P1 P2 P3

Active 1 1 1 Flat Reset FF FF FF

Not active 1 Toggling 1 Toggling

Operating mode

Fetches internal code

Not active 1 1 1 Toggling

Idle mode

Does not fetch code

Port Data

(1)

Port Data Port Data Port Data

Not active 1 0 0 Flat

Power down mode

Does not fetch code

Port Data

(1)

Port Data Port Data Port Data

Active 0 1 1 Flat Reset FF FF FF FF

Not active 0 Toggling 1 Toggling

Operating mode

Fetches external code

Not active 0 1 1 Toggling

Idle mode

Does not fetch code

Floating Port Data Address Port Data

Not active 0 0 0 Flat

Power down mode

Does not fetch code

Floating Port Data Port Data Port Data

14

7764A805111/07

2. In-System Programming (ISP)

The In-System Programming feature will be referenced as ISP in the rest of the document.

Most of Atmels C51 devices support the ISP mode. This feature enables the user to program

the device directly on his application without having to unsolder the device or using an external

programmer. This feature is made by means of a bootloader firmware embedded in the device

itself. A PC based application like FLIP (FLexible In-system Programmer) or any equivalent cus-

tom software enables to communicate with the bootloader to perform the part programming.

FLIP can be downloaded free of charge from the Atmels web site. It supports different interfaces

like RS232, USB, and CAN following the used device. Ensure you are always using the latest

version of FLIP.

The ISP mode is invoked by applying an hardware condition. The hardware condition differs

between a HPC and a LPC package (See Type of package on page 3.)

2.1 HPC package

2.1.1 Hardware settings

The following hardware settings must be applied in normal mode (execution) before starting the

ISP mode (programming).

EA pin must be tied to Vcc. The bootloader is only active when internal program memory is

used.

ALE pin cannot be forced by an external signal. This pin is driven by the MCU. Leave this pin

unconnected if not used.

PSEN pin cannot be forced by an external signal. This pin is driven by the MCU. Leave this

pin unconnected if not used.

2.1.2 Starting the ISP mode

Software condition: there are some configuration bits available in the part which enables to con-

figure the bootloader behaviour. Refer to the products bootloader datasheet for further

information. These bits are accessible from the GUI of FLIP. The BLJB bit is part of these. Most

of the time, it is activated at manufacturing level on new chips to have the device run in ISP

mode at first power on. When the BLJB is active, the user does not need to apply the hardware

condition described here after. It may be usefull at production level for instance. The BLJB bit is

deactivated by the bootloader after the first programming. It is then the responsability of the user

to re-activate it.

Hardware condition: when the BLJB bit is inactive, the only way to have the device run in ISP

mode, is to apply the hardware condition.

The hardware condition consists to apply an hardware reset while pulling the PSEN pin to

ground then to release the PSEN pin once the hardware reset has been applied.

It is recommended to pull the PSEN pin to ground through a 1K resistor to prevent the PSEN pin

from being damaged.

WARNING

Do not apply the hardware condition at power up otherwise the ISP mode may fail to start.

The hardware condition must be applied only when the device has started and when the

power supplies are stables.

15

7764A805111/07

Figure 2-1. HPC hardware condition

2.2 LPC package

2.2.1 Hardware settings

There are no specific hardware settings to apply.

2.2.2 Starting the ISP mode

Software condition:

Normally the BSB (Boot Status Byte) is activated (0xFF) at manufacturing level on new chips to

have the device run in ISP mode at first power on. When the BSB is active, the user does not

need to apply the hardware condition described here after. It may be useful at customers pro-

duction level for instance. The BSB is deactivated (0x00) by the bootloader after the first

programming. It is then the responsability of the user to re-activate it.

ALE EA

VCC

Standard C51

/PSEN

RST

VCC

GND

1K

Unconnected

VCC

VSS

VCC

GND

GND

C1

C2

Crystal

GND

XTAL2

XTAL1

UART / USB / CAN interfaces

PC running FLIP

Bootloader

WARNING

For LPC packages the BLJB bit is activated at manufacturing level and MUST NEVER be

changed by the user. If this ever occurs, the only way to restore the ISP mode is to re-pro-

gram the device by an external programmer.

16

7764A805111/07

Figure 1. Low Pin Count regular boot process

Hardware condition: when the BSB is inactive, the only way to have the device run in ISP mode,

is to apply the hardware condition.

As the PSEN pin is not available in LPC packages, a port pin is used instead to apply the hard-

ware condition which consists by default to apply a hardware reset while pulling P1.0 pin to

ground then to release P1.0 pin once the hardware reset has been applied.

P1.0 is an Atmel default setting which can be easily changed by FLIP. The user can select a

another port if P1.0 is inappropriate for his application. Refer to the products bootloader

datasheet for further information.

RESET

BLJB = 1

P1_CF = FFh

P3_CF = FFh

P4_CF = FFh

P1_CF = P1

P3_CF = P3

P4_CF = P4

Start Bootloader

BSB = 0

SBV < 7Fh

Start User Bootloader Start Application

Yes

No

No

No

No

Yes

Yes

Yes

Yes

Yes

Yes

No

No

No

Yes

Yes

No

No

H

a

r

d

w

a

r

e

B

o

o

t

P

r

o

c

e

s

s

S

o

f

t

w

a

r

e

B

o

o

t

P

r

o

c

e

s

s

i

n

L

o

w

P

i

n

C

o

u

n

t

Bit ENBOOT in AUXR1 Register is

Initialized with BLJB Inverted

ENBOOT = 1

PC = F400h

ENBOOT = 0

PC = 0000h

Hardware condition

CAUTION

Do not change the BLJB bit

17

7764A805111/07

Figure 2-2. LPC hardware condition

2.3 Using the ISP mode over RS232 interface

2.3.1 Baudrate

The maximum baudrate supported by the device depends on the crystal value or signal fre-

quency injected on XTAL1 pin. Refer to product datasheet for further information.

2.3.2 Hardware

The schematics of the interface are given here after.

Auto ISP feature: the implementation of this feature is optional.

When this feature is supported by the hardware, the same option can be activated in the prefer-

ences menu of FLIP. This option enables FLIP to manage and set automatically the hardware

condition to have the device run in ISP and to proceed with the part programming.

Standard C51

P1.0

RST

VCC

GND

VCC

VSS

VCC

GND

GND

C1

C2

Crystal

GND

XTAL2

XTAL1

UART / USB / CAN interfaces

PC running FLIP

Bootloader

18

7764A805111/07

D

T

R

R

x

_

P

C

C

T

S

D

S

R

T

x

_

M

C

U

R

x

_

M

C

U

T

x

_

P

C

R

T

S

V

c

c

V

c

c

V

c

c

V

c

c

V

c

c

V

c

c

V

c

c

V

c

c

V

c

c

/

P

S

E

N

P

3

_

0

/

R

x

D

P

3

_

1

/

T

x

D

R

S

T

A

U

T

O

I

S

P

F

E

A

T

U

R

E

R

S

2

3

2

I

N

T

E

R

F

A

C

E

C

2

5

1

0

0

n

C

2

5

1

0

0

n

C

1

7

1

0

0

n

C

1

7

1

0

0

n

C

2

2

1

0

0

n

C

2

2

1

0

0

n

C

2

6

1

0

0

n

C

2

6

1

0

0

n

S

W

1

R

E

S

E

T

S

W

1

R

E

S

E

T

2

3

1 4

1

7

U

9

A

7

4

H

C

1

2

5

/

S

O

_

5

U

9

A

7

4

H

C

1

2

5

/

S

O

_

5

C

D

2

1

0

0

n

C

D

2

1

0

0

n

D

1

2

G

r

e

e

n

L

e

d

T

x

L

E

D

D

1

2

G

r

e

e

n

L

e

d

T

x

L

E

D

5

6

1 4

4

7

U

1

0

B

7

4

H

C

1

2

5

/

S

O

_

5

U

1

0

B

7

4

H

C

1

2

5

/

S

O

_

5

C

1

8

1

0

0

n

C

1

8

1

0

0

n

D

1

1

G

r

e

e

n

L

e

d

R

x

L

E

D

D

1

1

G

r

e

e

n

L

e

d

R

x

L

E

D

C

1

9

1

0

0

n

C

1

9

1

0

0

n

1

2

J

1

1R

T

S

J

1

1R

T

S

C

2

3

1

0

0

n

C

2

3

1

0

0

n

R

6

1

0

K

R

6

1

0

K

1

2

J

1

3

J

1

3

C

2

1

1

0

0

n

C

2

1

1

0

0

n

5 9 4 8 3 7 2 6 1

P

1

S

U

B

-

D

9

F

E

M

A

L

E

R

S

2

3

2

P

1

S

U

B

-

D

9

F

E

M

A

L

E

R

S

2

3

2

R

2

3

1

K

R

2

3

1

KR

2

4

1

K

R

2

4

1

K S

W

8

I

S

P

S

W

8

I

S

P

C

1

+

1

C

1

-

3

C

2

+

4

C

2

-

5

V C C

1 6

G N D

1 5

V

+

2

V

-

6

R

1

O

U

T

1

2

R

2

O

U

T

9

T

1

I

N

1

1

T

2

I

N

1

0

R

1

I

N

1

3

R

2

I

N

8

T

1

O

U

T

1

4

T

2

O

U

T

7

U

7

S

I

P

E

X

-

S

P

3

2

3

2

E

C

A

U

7

S

I

P

E

X

-

S

P

3

2

3

2

E

C

A

R

2

2

1

K

R

2

2

1

K

C

2

0

1

0

0

n

C

2

0

1

0

0

n

C

1

6

1

0

0

n

C

1

6

1

0

0

n

C

1

+

1

C

1

-

3

C

2

+

4

C

2

-

5

V C C

1 6

G N D

1 5

V

+

2

V

-

6

R

1

O

U

T

1

2

R

2

O

U

T

9

T

1

I

N

1

1

T

2

I

N

1

0

R

1

I

N

1

3

R

2

I

N

8

T

1

O

U

T

1

4

T

2

O

U

T

7

U

8

S

I

P

E

X

-

S

P

3

2

3

2

E

C

A

U

8

S

I

P

E

X

-

S

P

3

2

3

2

E

C

A

C

2

4

1

0

0

n

C

2

4

1

0

0

n

1

2

J

1

2D

T

R

J

1

2D

T

R

19

7764A805111/07

3. Troubleshooting

3.1 MCU not starting or operating in a reliable way

Possible root

cause I/O External Code Internal Code

POWERS and

GND delivered

to the device

Input

- Must be stables

- Monitor power supplies

- Check if GND is properly supplied to device

XTA2 pin Output - Monitor XTAL2 to see if the oscillator has started and is working properly. Check if your crystal is not an overtone part.

RST pin I/O

- If RST pin is not correctly driven, MCU is not properly reset.

- If the device does not have an internal POR, read application note: how to calculate the capacitor of the reset input of

a C51 microcontroller (doc 4284)

- If an external Brown-out device is used, an intermediate resistor or diode must be implemented between RST pin and

the Brown-out device

EA pin Input - Must be connected to GND

- Must be connected to VCC, directly or through a 10K

resistor.

- MCU may not work properly, if this pin is left floatting

ALE pin

Output

signal

- This signal is used to clock the Least

Significant Byte into the address latch

- the frequency of this signal enables to guess the

frequency that the core runs at.

(See Relationship between oscillator and ALE

frequencies on page 11.)

- Not used.

- Must be left unconnected in normal operation

- If ALE is not disabled by firmware, the frequency of this

signal enables to guess the frequency that the core runs at.

See Relationship between oscillator and ALE frequencies

on page 11.)

PSEN pin

Output

signal

- This signal is used to strobe the external program

memory when the MCU fetches the code byte.

- Monitor ALE and PSEN pins to get the status of the

MCU. ( See Microcontroller status on page 13.)

- Not used.

- Must be left unconnected in normal operation

- If ALE is not disabled by firmware, monitor ALE and PSEN

pins to get the status of the MCU. ( See Microcontroller

status on page 13.)

P0

I/O

port

Port 0 serves as a multiplexed address/data bus. It

emits the low byte of the Program Counter (PCL) as an

address, and then goes into a float state awaiting the

arrival of the code byte from the Program Memory

Can be used as a general purpose I/O port.

In this case external pull-ups must be provided.

P2

I/O

port

Port 2 emits the high byte of the Program Counter

(PCH)

Can be used as a general purpose I/O port.

No external pull-ups are needed as this port owns internal

pull-ups

HSB set to maximum

security

Does not work No impact

Device is damaged Try another device

20

7764A805111/07

3.2 In-System Programming does not work

Possible root cause External Code Internal Code

MCU is not working in ISP mode

NOT

APPLICABLE

Apply the hardware condition. See In-System Programming (ISP) on page

14. and read the devices bootloader datasheet.

MCU does not work properly

Monitor power supplies, XTAL2, RST, EA, ALE, PSEN ( See MCU not

starting or operating in a reliable way on page 19.)

Device is damaged Try a new or another device

Printed on recycled paper.

7764A805111/07

2007 Atmel Corporation. All rights reserved. Atmel

, logo and combinations thereof, and Everywhere You Are

are the trademarks or regis-

tered trademarks, of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any

intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMELS TERMS AND CONDI-

TIONS OF SALE LOCATED ON ATMELS WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY

WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR

PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-

TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT

OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no

representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications

and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically providedot-

herwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmels products are not intended, authorized, or warranted for use as compo-

nents in applications intended to support or sustain life.

Atmel Corporation Atmel Operations

2325 Orchard Parkway

San Jose, CA 95131, USA

Tel: 1(408) 441-0311

Fax: 1(408) 487-2600

Regional Headquarters

Europe

Atmel Sarl

Route des Arsenaux 41

Case Postale 80

CH-1705 Fribourg

Switzerland

Tel: (41) 26-426-5555

Fax: (41) 26-426-5500

Asia

Room 1219

Chinachem Golden Plaza

77 Mody Road Tsimshatsui

East Kowloon

Hong Kong

Tel: (852) 2721-9778

Fax: (852) 2722-1369

Japan

9F, Tonetsu Shinkawa Bldg.

1-24-8 Shinkawa

Chuo-ku, Tokyo 104-0033

Japan

Tel: (81) 3-3523-3551

Fax: (81) 3-3523-7581

Memory

2325 Orchard Parkway

San Jose, CA 95131, USA

Tel: 1(408) 441-0311

Fax: 1(408) 436-4314

Microcontrollers

2325 Orchard Parkway

San Jose, CA 95131, USA

Tel: 1(408) 441-0311

Fax: 1(408) 436-4314

La Chantrerie

BP 70602

44306 Nantes Cedex 3, France

Tel: (33) 2-40-18-18-18

Fax: (33) 2-40-18-19-60

ASIC/ASSP/Smart Cards

Zone Industrielle

13106 Rousset Cedex, France

Tel: (33) 4-42-53-60-00

Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd.

Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300

Fax: 1(719) 540-1759

Scottish Enterprise Technology Park

Maxwell Building

East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000

Fax: (44) 1355-242-743

RF/Automotive

Theresienstrasse 2

Postfach 3535

74025 Heilbronn, Germany

Tel: (49) 71-31-67-0

Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd.

Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300

Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom

Avenue de Rochepleine

BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00

Fax: (33) 4-76-58-34-80

Literature Requests

www.atmel.com/literature

Вам также может понравиться

- ATmega4208 09 DS80000867CДокумент17 страницATmega4208 09 DS80000867CNeelakanta KallaОценок пока нет

- Communication and Networking Technologies For UAVs ASurvey ResponseДокумент24 страницыCommunication and Networking Technologies For UAVs ASurvey ResponseAyoub AtlanticОценок пока нет

- Working Model Amr of XYZ Company: 2G Quad BandДокумент1 страницаWorking Model Amr of XYZ Company: 2G Quad BandNeelakanta KallaОценок пока нет

- IV. V. VI. Vii. Viii. IX.: AnnexureДокумент1 страницаIV. V. VI. Vii. Viii. IX.: AnnexureNeelakanta KallaОценок пока нет

- Communication and Networking Technologies For UAVs ASurvey ResponseДокумент24 страницыCommunication and Networking Technologies For UAVs ASurvey ResponseAyoub AtlanticОценок пока нет

- 10.12 User Manual of HXE310CT CTPT Meter V2 PDFДокумент76 страниц10.12 User Manual of HXE310CT CTPT Meter V2 PDFMalitha Peiris100% (1)

- Electroactive Polymer Artificial MuscleДокумент5 страницElectroactive Polymer Artificial MuscleNeelakanta KallaОценок пока нет

- Safety Data Sheet: Section 1. IdentificationДокумент12 страницSafety Data Sheet: Section 1. IdentificationNeelakanta KallaОценок пока нет

- Road Transport and Safety Bill 2015Документ350 страницRoad Transport and Safety Bill 2015Mohamed Nazeem.Оценок пока нет

- Communicating With An Energy Meter Using Iec 62056 Through TCP - IpДокумент7 страницCommunicating With An Energy Meter Using Iec 62056 Through TCP - IpVОценок пока нет

- 12Документ15 страниц12Neelakanta KallaОценок пока нет

- Quotation For Home Automation FormatДокумент2 страницыQuotation For Home Automation FormatNeelakanta KallaОценок пока нет

- Opencpu: GCC Installation GuideДокумент17 страницOpencpu: GCC Installation GuideNeelakanta KallaОценок пока нет

- Safety Data Sheet: Safety Commission Regulations Which Take Precedence Over OSHA Hazard Communication LabelingДокумент4 страницыSafety Data Sheet: Safety Commission Regulations Which Take Precedence Over OSHA Hazard Communication LabelingNeelakanta KallaОценок пока нет

- Dream The Convergence Future With Drone and Iot Technology: Ground Control SystemДокумент2 страницыDream The Convergence Future With Drone and Iot Technology: Ground Control SystemNeelakanta Kalla100% (1)

- Elsie ManualДокумент132 страницыElsie ManualNeelakanta KallaОценок пока нет

- Mastering Arduinojson 6: Efficient Json Serialization For Embedded C++Документ39 страницMastering Arduinojson 6: Efficient Json Serialization For Embedded C++Neelakanta KallaОценок пока нет

- Export InfoДокумент1 страницаExport InfoNeelakanta KallaОценок пока нет

- A Pilot Study On The Human by Low Frequency Noise: Body Vibration InducedДокумент8 страницA Pilot Study On The Human by Low Frequency Noise: Body Vibration InducedNeelakanta KallaОценок пока нет

- Modelsim TUTORIAL PDFДокумент82 страницыModelsim TUTORIAL PDFhasbiiieОценок пока нет

- Openmv 3Документ1 страницаOpenmv 3Neelakanta KallaОценок пока нет

- Disclosure To Promote The Right To InformationДокумент19 страницDisclosure To Promote The Right To InformationNeelakanta KallaОценок пока нет

- 13 2laserradars3d PDFДокумент20 страниц13 2laserradars3d PDFNeelakanta KallaОценок пока нет

- Print ElectoralДокумент1 страницаPrint ElectoralNeelakanta KallaОценок пока нет

- 5 Wire Curtain MotorДокумент1 страница5 Wire Curtain MotorNeelakanta KallaОценок пока нет

- DNN Machine LearningДокумент6 страницDNN Machine LearningNeelakanta KallaОценок пока нет

- Design and Simulation of Two Phase Interleaved Buck ConverterДокумент8 страницDesign and Simulation of Two Phase Interleaved Buck ConverterNeelakanta KallaОценок пока нет

- Disclosure To Promote The Right To InformationДокумент18 страницDisclosure To Promote The Right To InformationNeelakanta KallaОценок пока нет

- Tak Tsy Stech BriefДокумент2 страницыTak Tsy Stech BriefNeelakanta KallaОценок пока нет

- Si-RS485 MODBUSДокумент4 страницыSi-RS485 MODBUSNeelakanta KallaОценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- Global Pulse Survey 9th Edition ReportДокумент65 страницGlobal Pulse Survey 9th Edition ReportZaid Al-Mohammed SalihОценок пока нет

- Differential: Systems OperationДокумент3 страницыDifferential: Systems OperationAhmed RezkОценок пока нет

- Brand Architecture Assignment Week 2 - LGДокумент3 страницыBrand Architecture Assignment Week 2 - LGDivyanshu JhaОценок пока нет

- Rizal's Life, Works and Contributions to Nation BuildingДокумент9 страницRizal's Life, Works and Contributions to Nation BuildingAngel OmlasОценок пока нет

- EBOOK - Cold Chain QualificationДокумент20 страницEBOOK - Cold Chain QualificationYoussef AliОценок пока нет

- Advantages and Disadvantages of A SERIES and PARALLEL CircuitДокумент5 страницAdvantages and Disadvantages of A SERIES and PARALLEL CircuitAna Ats YviОценок пока нет

- Gayle Kovacevic - Math Teacher Resume 2023 No AddressДокумент2 страницыGayle Kovacevic - Math Teacher Resume 2023 No Addressapi-596111130Оценок пока нет

- Micro LaterologДокумент25 страницMicro Laterologali_hamza223Оценок пока нет

- Entrepreneurship Q1 MOD-4Документ17 страницEntrepreneurship Q1 MOD-4LOUIE MARK FANGONОценок пока нет

- DSM Somos: Stereolithography Materials Selector Guide: Property SummaryДокумент2 страницыDSM Somos: Stereolithography Materials Selector Guide: Property SummaryHImanshu BhattОценок пока нет

- Thermodynamic processes and energy transfers in open and closed systemsДокумент12 страницThermodynamic processes and energy transfers in open and closed systemsravitejabvОценок пока нет

- The Breath of LifeДокумент6 страницThe Breath of Lifekabshiel100% (1)

- Process Safety Capability StudiesДокумент51 страницаProcess Safety Capability Studiestloganat100% (2)

- Hazardous Area TerminologyДокумент7 страницHazardous Area TerminologyDayo IdowuОценок пока нет

- Krish Mar23Документ4 страницыKrish Mar23Gengaraj PothirajОценок пока нет

- Lecture 6 - TorsionДокумент25 страницLecture 6 - TorsionCJ Valete JacobОценок пока нет

- InductionДокумент26 страницInductionDileep NaraharasettyОценок пока нет

- Create data entry forms in ExcelДокумент4 страницыCreate data entry forms in ExcelTrixie CabotageОценок пока нет

- D 100394 X 012Документ52 страницыD 100394 X 012Preyas SuvarnaОценок пока нет

- Life Is A Journey: Student's GuideДокумент154 страницыLife Is A Journey: Student's GuidejuancmuОценок пока нет

- 41Cr4 Chemical PDFДокумент2 страницы41Cr4 Chemical PDFGayathriRajasekaranОценок пока нет

- Overview of Electronic Commerce: © 2008 Pearson Prentice Hall, Electronic Commerce 2008, Efraim Turban, Et AlДокумент44 страницыOverview of Electronic Commerce: © 2008 Pearson Prentice Hall, Electronic Commerce 2008, Efraim Turban, Et AlOntiq DeyОценок пока нет

- Focused Ion BeamДокумент90 страницFocused Ion BeamLotus DarkОценок пока нет

- Minesight - Designing Cuts For STP and Calculating Reserves With ReserveДокумент38 страницMinesight - Designing Cuts For STP and Calculating Reserves With ReserveDody100% (1)

- Servicing Manual: Wall-Mounted Condensing BoilerДокумент44 страницыServicing Manual: Wall-Mounted Condensing BoilerNicu Pirvu100% (3)

- Biblio SyriacДокумент12 страницBiblio Syriacjean-marie_mouescaОценок пока нет

- NigeriaДокумент17 страницNigeriaMohammed IssakaОценок пока нет

- Origin of NatyasastraДокумент9 страницOrigin of NatyasastraArya V NairОценок пока нет

- A Study On Financial Performance of State Bank of India: April 2018Документ6 страницA Study On Financial Performance of State Bank of India: April 2018priyankaОценок пока нет

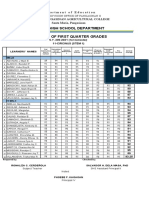

- Department of Education Senior High School 1st Quarter GradesДокумент4 страницыDepartment of Education Senior High School 1st Quarter GradesRonaliza CerdenolaОценок пока нет