Академический Документы

Профессиональный Документы

Культура Документы

Training Chasis NA7D - A

Загружено:

julio gamboaИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Training Chasis NA7D - A

Загружено:

julio gamboaАвторское право:

Доступные форматы

ORDER NO.

MTNC010309G1

B1 & B5

Copyright 2001 by Matsushita Electric Corporation of America.

All rights reserved. Unauthorized copying and distribution is a

violation of law.

Technical Guide

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

Please file and use this TECHNICAL GUIDE for

the NA7D/A CHASSIS together with the Main

Service Manuals and other publications related

to models based on the NA7D/A chassis.

2

Notes

3

Description of Boards ....................................... 4

New Technology

MPU ..................................................................... 6

Analog Front-end Block................................... 9

Y/C Separation................................................ 9

ACC............................................................... 10

Luminance Processor.................................... 11

Blackstretch Circuits...................................... 11

Sharpness Control......................................... 12

Chroma Processor Block............................... 12

Killer .............................................................. 12

Color.............................................................. 12

Cb/Cr to R-Y/B-Y Conversion........................ 12

RGB Matrix Block .......................................... 13

ACL ............................................................... 13

Gamma () Correction ................................... 13

Mute .............................................................. 13

OSD Function................................................ 13

Analog Back-end Block ................................. 14

Deflection Block............................................. 14

Sync Separation............................................ 14

H SYNC SEPA (auto slicer) .......................... 14

V SYNC SEPA .............................................. 14

AFC1 ............................................................. 14

AFC2 ............................................................. 15

V Counter ...................................................... 15

Functional Block Diagrams

Audio Signal Path............................................. 18

Video & Sync Signal Path................................ 19

I2C Bus Line System........................................ 20

MPU Control ...................................................... 21

Audio

MTS Sound Detection and Separation .......... 24

Composite Signal .......................................... 24

Mono or L+R Signal ...................................... 24

LR Signal .................................................... 24

Secondary Audio Program (SAP) mode ....... 24

dbx

Effect .................................................... 24

Matrix Circuit ................................................. 24

AGC Audio Control Surround......................... 26

IC2501 Audio Controller................................ 26

AGC.............................................................. 26

AI Sound ....................................................... 26

Audio Multiplex System................................... 27

Abstract......................................................... 27

The North American System......................... 27

Audio Amplifiers............................................ 28

Deflection

Deflection Circuit ............................................ 30

Vertical Output Circuit .................................. 30

Sawtooth Wave Generating Circuit .............. 30

Drive Circuit ................................................. 30

Vertical Output Pulse Amplifying Circuit ...... 31

Vertical Output Circuit Operation ................. 31

Pulse Amplifier Circuit

(Pump Up) Operation ............................... 31

Horizontal Output Circuit............................... 32

Horizontal Output .......................................... 32

Horizontal Drive Circuit ................................. 33

Power Supply

Power Supply Overview

(US Models) ...................................................... 36

Power Supply Overview

(CT-G3349L)...................................................... 37

Protection Circuits........................................... 38

Over Current Protection................................ 38

Spot Killer...................................................... 38

Neck Protector .............................................. 38

The purpose of this Technical Guide is to present an overall view of the circuits used in the NA7D/A

Chassis. The guide can assist the service technician in troubleshooting a receiver. By using general

block diagrams, the guide provides the technician with an overall view of the entire system.

The block diagrams include a general description of circuits. The purpose of the descriptions is to help

the technician understand how particular circuits operate.

By using block diagrams and circuit descriptions, the Technical Guide will help the technician develop

knowledge about this Chassis.

Table of Contents

4

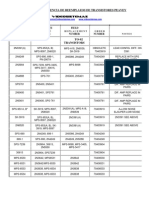

Description of Boards Used on the NA7 Chassis

Table 1 lists the various boards and their functions

which may be used on any of the receivers based on

the NA7 Chassis.

TABLE 1: PANEL DESCRIPTIONS

B-PANEL (TNP2AA079)

SURROUND SOUND CONTROL

BASS/TREBLE/BALANCE CONTROL

C-PANEL (TNP2AA075 & TNP2AA086)

RGB DRIVES

J-PANEL (TNP2AA093)

HALF TONE SWITCHING

A-PANEL (TNP2AH031 & TNP2AH024)

AUDIO/VIDEO AND S-VHS INPUT TERMINALS

VIDEO SWITCHING

MTS PROCESSING

HALFTONE SWITCHING

POWER SUPPLIES

MICRO PROCESSOR CONTROLS

AUDIO AMPLIFICATION

VERTICAL AND HORIZONTAL DEFLECTION

CONTROLS

PROTECTION CIRCUITRY

Z-PANEL (TNP2AA010)

PINCUSHION CORRECTION

P-PANEL (TNP2AA014)

DC - DC CONVERTOR POWER SUPPLY

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

NEW TECHNOLOGY

6

M65580MAP100 (MPU/VCJ)

The MPU/VCJ employed in the NA7D/A chassis

incorporates processes that on other chassis are

performed by other ICs. These functions include

synchronization, TV, EXT, Y/C switching, Video

Chroma Jungle (VCJ) and filtering. Fig. 2 & Fig. 3

display the block diagram for the IC as a whole and

in detail respectively.

Figure 1: MPU/VCJ Pinout

7

Figure 2: MPU/VCJ Block Diagram

8

Figure 3: MPU/VCJ Block Diagram (for Signal Processing)

9

Analog Front End Block (Fig. 4)

The MPU, via the I

2

C Bus data, selects the

appropriate input from the TV_In, EXT_In or Y/C_In.

CVBS or Y signal is amplified to twice the input

signal and output from pin 18 to pin 17 for Sync

Separation block and to pin 77 for CC DEC. When

Standard Analog Composite (CVBS) signal is

selected for input, it is input to the first 8bit ADC.

When Y/C signal is selected for input, the Y portion

is input to the first 8bit ADC and the Chroma is input

to the second 8bit ADC. The signals are then

converted to digital signals.

The reference voltage can be either 1.7V (1.2Vp-p),

1.8V (1.3Vp-p) or 1.9V (1.4Vp-p), selected by the

MPU, via the I

2

C BUS data. The timing of the ADC

and Logic CLK can be changed by the MPU, via the

I

2

C Bus data.

Figure 4: Analog Front End Block

Y/C Separation (Fig. 5)

A two-dimensional YC separation is performed using

1 line memory and an algorithm. Input CVBS signal

is fed in to a filter (H-BPF) in the horizontal direction

and the filter (HV-BPF) in the horizontal-vertical

direction for detecting in which direction (H or V) the

input signal correlates. When there is no correlation

in the vertical direction the filter is changed from HV-

BPF to H-BPF. The sensitivity of the correlation

detection can be adjusted by the MPU, via the I

2

C

BUS. Regardless of correlation detection H-BPF or

HV-BPF can be selected by the MPU, via the I

2

C

BUS. This circuit is effective only when input CVBS

is larger than a determined level. If the level is small,

the Luminance signal is filtered by Trap around FSC

frequency and the Chrominance is filtered by Y/C

separator. In case of Y/C input, the circuit will bypass

the process by the MPU, via the I

2

C BUS. Y&C

signals are passed to the Y processing block and the

C processing block respectively.

Figure 5: Y/C Separation

10

ACC (Fig. 6a & Fig. 6b)

This IC contains digital ACC to boost input. If burst

level is smaller than the level of MPU, via the I

2

C

BUS, three analog ACC amps, each of 10dB operate

in order. The on/off status is also controlled by the

MPU, via the I

2

C BUS, as follows:

0 = amp off: 0dB

1 = ampx1 on: 10.5dB

2 = ampx2 on: 21dB

3 = ampx3 on: 31.5dB

When the third analog ACC amp is on, digital ACC

circuit can be set to off by the MPU, via the I

2

C BUS.

It can also be forced to be in the off state by the

MPU, via the I

2

C BUS.

Figure 6a: ACC Processing

Figure 6b: ACC Processing

11

Luminance Processor (Fig. 7)

In this process, the Y/C delay timing, blackstretch,

YNR, sharpness of input luminance signal is

controlled by the MPU, via the I

2

C data, the following

way:

Y/C delay adjustment: luminance signal can be

delayed to adjust to chroma signal delay time by

MPU, via the I

2

C BUS data. The YNR function

subtract noise at around fsc frequency from

luminance signal.

Figure 7: Y/C Separation

Blackstretch Circuits

The IC has detection for input Y signal in dot, field

and time dimension. Fig. 8 details the process.

Figure 8: Blackstretch Circuits

One of the status can be selected for white area of Y

input signal. Each status is determined by the upper

system, and it can also be checked by the MPU, via

the I

2

C Bus, or IM (Intelligent Monitor) terminals

(pin 11). Fig. 9 displays the process of the black

stretch.

YC Separation

Normal 2 Line Comb Filter

Weak Signal Y: Trap Filter (Digital)

C: Band Pass Filter

(BPF, Digital)

Input Block Amp is ON

Small Burst Signal (Chroma)

12

Figure 9: Blackstretch Process

Sharpness Control

Preshoot and overshoot signals are added to the

input luminance signal to emphasis on the outline of

the picture. The width and gain of the preshoot and

overshoot can be controlled by the MPU, via the I

2

C

BUS, as well as the upper limit of the sharpness

level.

Chroma Processor Block (Fig. 10)

Input chroma is converted to R-Y & B-Y signals by

offset canceller, demodulator ACC, Color, Tint and

Killer circuits.

When color signal is present, input chroma is

demodulated by 4fsc CLK to input burst signal and

calculation of its components. Tint is controlled by

the MPU, via the I

2

C BUS data.

Figure 10: Chroma processing

Killer

When the burst level is smaller than Killer level set

by the MPU, via the I

2

C BUS, in succession of two

fields, it is switched to Killer-on (Chroma output

OFF). It can also be forced to switch by the MPU, via

the I

2

C BUS. The switching between on and off is

done on a condition of hysteresis and interval. Killer

detection is also done by noise detection and V

coincidence.

Color

Color level is controlled by the MPU via the I

2

C BUS.

Cb/Cr to R-Y/B-Y Conversion

Following is the conversion formula in which the

normalized Cb/Cr signals are converted to R-Y/B-Y:

R-Y=1.14 x Cr

B-Y=2.03 x Cb

13

RGB Matrix Block (Fig. 11)

The Y, R-Y & B-Y signals that are input to the IC are

processed by the RGB matrix to generate the R, G &

B signals by the following formula:

R = 1 x Y + 0 x (B-Y) + r x (R-Y)

G = 1 x Y - (13/16) x (B-Y) - (7/16) x (R-Y)

B = 1 x Y + 1 x (B-Y) + 0 x (R-Y)

where r = 12/8, 13/8, 14/8

If the result is negative, the output is clipped to

000h. Level can be fixed to 0 (LSB) by Mute of

MPU, via the I

2

C BUS.

Figure 11: RGB Matrix

ACL

The R/G/B signals are multiplied with ACL data and

Contrast data (6 & 7 bit respectively). The signals

are clipped when they exceed a maximum level,

then data is divided by a constant. Contrast and ACL

data are set to fixed levels in standard case. Data

below a certain level is fixed to a predetermined

level for only OSD signal when F.B. signal = 1.

Gamma () Correction

Gamma points (16 kinds) and on/off/inverse/no-

inverse mode of R/G/B signals are controlled by the

MPU, via the I

2

C BUS. See Fig. 12.

Figure 12: Gamma () Correction

Mute

On/off of R/G/B is controlled by the MPU, via the I

2

C

BUS data.

OSD Function

Input picture data R/G/B are overlaid by RGB OSD

(through Q050 ~ Q052) F.B. and half tone signals

from the MCU block through IC050.

OSD overlay and halftone (transparent) are two

kinds of display modes in OSD function.

Note: Gamma on/off can be controlled by

MPU via the I

2

C.

Gamma Point (circle) can be adjusted

by 64LSB steps from 64LSB to

960LSB by MPU via the I

2

C

It has inverse mode (Line-B) and non

inverse mode (Line-A).

14

Analog Back-end Block

9 bit Cut-off DACs and 7 bit Drive DACs control the 3

channels 10 bit high speed video DACs for main

R/G/B signals. R/G/B output are also controlled for

Spot killer. See Fig. 13.

Figure 13: Analog Back-end Block

Deflection Block

The signal for synchronization of the input video is

generated in this area as well as the horizontal and

vertical synchronization. It contains two phase

locked loops, AFC1 & AFC2. AFC1 generates the

horizontal and vertical timing pulse. Phase and

frequency are synchronized by the input sync. The H

SYNC generated at AFC1 is the reference timing for

all data related to display. AFC2 is used to adjust the

phase of the horizontal drive pulse and

compensation for the delay of the horizontal output

stage such as FBT.

Sync Separation:

The Sync Separation is composed of H SYNC SEPA

which extracts COMPOSITE SYNC from input

CVBS signal and V SYNC SEPA which extracts V

SYNC from COMPOSITE SYNC.

H SYNC SEPA (auto slicer)

The input CVBS signal is clamped to pedestal level

by BGP (burst gate pulse) generated at DEF LOGIC

block. The center voltage of the pedestal voltage

and the sync tip voltage is generated. COMPOSITE

SYNC can be separated by comparing the center

voltage with the input CVBS.

V SYNC SEPA

During the period H of COMPOSITE SYNC

(negative polarity), the capacitor is charged, and in

the period L, it is discharged with the determined

current in the IC. The wave like triangle is generated

in the horizontal period. V SYNC can be separated

by comparing the triangle waveform with the

determined voltage. Only the pulse over the

determined time is identified as V PULSE.

AFC1

AFC1 is composed of freerun frequency adjustment

and fH pulse. Free running frequency of HVCO is

adjusted to around 15.73KHz by VCO control circuit

of which standard frequency is 4fsc (=14.32MHz).

The free running frequency can be changed by

MPU, via the I

2

C BUS. fH pulse generated by

division of the HVCO, is compared in phase with the

input H SYNC to synchronize. BGP for SYNC SEPA,

HD pulse for signal processing, timing pulses for

AFC2 are generated in this stage. The gain of AFC1

can be changed by the MPU, via the I

2

C BUS data,

and the state of COINCIDENCE. See Fig. 14.

Figure 14: AUTO ADJ & AFC1

15

AFC2

Two timing pulses for H-RAMP (corresponding to the

rising and falling edges of HOUT) generated in

AFC1 stage are applied to the delay circuit

controlled by the voltage. H-pulse (HOUT) is

generated by this circuit. HOUT is fed back to this

stage as a reference pulse (FBP) through the

horizontal drive circuits (H drive Tr, FBT, etc.). The

phase of HOUT can be adjusted by comparing FBP

with the output of divider in AFC1 and control the

threshold voltage of delay circuit. The phase of FBP

is adjusted to be in the blanking period of the input

CVBS signal.

Coincidence

In the period of SYNC SEPA and for FBP is H, a

capacitor is charged by the current. During L the

capacitor is discharged. The voltage at the capacitor

is check. During LOCK, the output of the detector

is H. During UNLOCK the output of the detector is

L. The detector has a fast and slow modes. The

slow mode is output by the MPU, via the I

2

C BUS,

and the killer circuit is set to on. Fast mode is used

for skew distortion of VTR at the upper side of the

TV screen. Loop gain is controlled by AFC1 by the

skew and unlock detection. If AFC is in LOCK and

phase is not within acceptable range then the skew

at the upper side of the screen is compensated by

selecting a higher AFC1 gain.

V COUNTER

In the vertical period, the counter by 2fH CLK rate is

used. The circuit extracts only pure vertical timing

pulse from V SYNC SEPA signal is generated in V

SYNC SEPA stage. When abnormal vertical pulses

are encountered they are ignored.

The counter is reset by the input vertical signal and

output the reference pulse to Vramp circuit. In that

process the counter is operated by 2fH clock and

when the number of counter is over a predetermined

limit, the next V pulse is not ignored. When V SYNC

SEPA output is missing, V pulse is regenerated by

the determined timing (window function). V counter

is reset by itself when no V SYNC SEPA signal is

received and stop receiving the signal for a

determined period. This circuit also has a function of

V shift to adjust vertical position of screen and V

COINCIDENCE to detect if V counter is locked or

unlocked.

X-ray and Neck Protector

The X-ray protector can be set to non-active state by

the MPU, via the I

2

C BUS. When the voltage at

pin 36 is higher than the first threshold voltage

(VthHD), the frequency of Hout is fixed to about

16.5KHz. When it is higher than the second

threshold voltage (VthSD), Hout is stopped (no

signal). The threshold voltages can be selected by

the MPU, via the I

2

C BUS.

If the horizontal high voltage circuit is malfunctioning

and the X-ray protector does not work properly, the

electron beam may overheat and melt the CRT

neck. Therefore this circuit detects these abnormal

states and shuts down the RGB output. When pin 40

is low (0V) the output of the R/G/B is set to zero (no

signal).

Intelligent Monitor

One analog or digital signal can be monitored (Vdd,

input of ADCs, Hsync output, etc.) through pin 11.

The signal is selected by the MPU, via the I

2

C BUS.

16

Notes

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

FUNCTIONAL

BLOCK DIAGRAMS

18

This section describes the flow diagrams for main

functions. Fig. 15 provides the audio signal flow.

Fig. 16 provides the video/sync signal flows. Fig. 17

details the I

2

C operation and Fig. 15 ~ Fig. 18

include various MPU functions and control.

Other sections provide details and other aspects of

the operation, such as audio, deflection, power

supplies and protection.

.

F

i

g

u

r

e

1

5

:

A

u

d

i

o

S

i

g

n

a

l

P

a

t

h

1

9

Figure 16: Video & Sync signal path

*

*

See Fig. 30 for

20

I

2

C Bus Line System

The NA7D/A incorporates an Inter-Integrated Circuit

(I

2

C) double polarity bus (see Fig. 17). The I

2

C bus

carries information between devices connected to

the bus using two lines, the Serial Data (SDA) and

Serial Clock (SCL). Each device has an unique

address for data transfer called the Slave Address.

When data is transmitted or received, the devices on

the bus are either a Master or a Slave. For NA7D/

A chassis, the Master device is the IC001

Microprocessor Unit (MPU). The MPU initiates a

data transfer on the bus line and generates the clock

signal that permits data to be sent. The MPU then

addresses the Slave devices, which receive the

transmitted data and return an acknowledgment to

the MPU.

The I

2

C bus system performs control functions that

replaces many of the mechanical controls needed in

a television receiver. Instead of adjusting individual

mechanical controls, electronic control functions can

be performed using the On Screen Display Menu in

Serviceman Mode.

Figure 17: I

2

C Bus

MCU

MCU

SIGNAL

PROCESSOR

SIGNAL

PROCESSOR

SCL

SDA

21

Figure 18: MPU/VCJ Control

See Fig. 30 for details

22

Notes

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

AUDIO

24

MTS Sound Detection And Separation

Composite Signal

The composite audio signal from the tuner inputs to

MTS Decoder IC2201 pin 14 (MPX in) (see Fig. 19).

The signal is processed by a low pass Stereo Filter

which passes signals below 15.75kHz. The output

from the Stereo Filter contains the L+R signal

(mono) and may also contain the L-R signal (stereo)

plus the Stereo Pilot signal (stereo broadcast

indicator). The signal is then applied to four circuits:

Pilot detector

Stereo PLL

L+R Demod (FM)

L-R Demod (AM)

Mono or L+R Signal

The L+R signal is FM demodulated and then sent to

the L+R Filter. The high frequency components of

the signal are de-emphasized and sent to the Matrix

circuit for left and right channel simulation.

LR Signal

When the 15.75kHz stereo pilot signal is detected at

pin 6, indicating AM stereo broadcast, the stereo

PLL switches on the L-R Demod to demodulate the

AM signal.

The signal is then passed to the L-R Filter which

removes the high frequency noise components.

The signal is then passed to the L-R/SAP switch,

which is controlled by I

2

C bus user input (Stereo or

SAP), and output to pin 15.

The signal from pin 15 is coupled via an external

capacitor to pin 16 and applied to the dbx circuit.

Secondary Audio Program (SAP) mode

The input signal applied at MTS IC2201 pin 14 (MPX

in) is fed to the SAP Filter and the Noise band pass

filter (BPF). The Noise BPF removes components

around 240 kHz.

If Stereo is selected, the signal is passed through the

SAP Noise Detector to the SAP Demod to mute the

SAP demodulator.

If SAP is selected, the SAP signal is demodulated,

filtered for noise components, output via pin 13, and

applied to the dbx circuit via pin 12.

dbx

Effect

dbx is a compression, expansion, pre-emphasis, de-

emphasis system that reduces the overall audio

noise level. As the overall level in the audio chain

increases, the noise level increases also. With dbx,

the audio level increases, but by only half as much.

Using a 2 to 1 compression ratio, the input signal is

compressed and a shelving filter is referenced to

the input level to set the pre-emphasis. A shelving

filter is a circuit with a flat frequency response that

has two bands of frequencies that are separated by

a third band. This third band has either a downward

or upward sloping frequency response.

The output signal is decompressed and the high

frequencies are rolled off by the de-emphasis filter.

The output audio signal now has a greater S/N then

the input signal. It has a flat frequency response and

up to 30 dB less noise.

Note: MTS IC2201 pin 10 is the timing current

setting of the dbx rms value detection, and

is set at about 1.3V. Pin 6 is the reference

power supply stabilization voltage, and is

set at about 4.5V.

dbx is a registered trademark of Carillon Electronics

Corp.

Matrix Circuit

The matrix circuit switches the output audio signal

according to the selection received from MPU IC001

through the I

2

C bus at pins 19 (SDA) and 18 (SCL).

The signals are output through pins 21 (L-out) and

22 (R-out) to the sound switching circuit.

Selection Matrix Effect

Mono L+R or mono to output to pins 21 & 22

Stereo

to pin 22

to pin 21

SAP SAP to output to pins 21 & 22

L R + ( ) L R ( ) +

2

--------------------------------------------

L R + ( ) L R ( )

2

-------------------------------------------

2

5

Figure 19: Multiplex Television Sound (MTS)

26

Figure 20: AGC Audio Path

AGC Audio Control Surround

IC2501 Audio Controller

IC2501 Audio Controller/Sound Processor controls

all aspects of the sound via the MPU: bass, treble,

balance, AGC, AI Sound, and Mute (see Fig. 20).

AGC

At times the received audio signal level is too high or

too low, so special circuits are needed to equalize

audio levels across various programming.

AGC is designed to detect and compensate for the

large variations in audio input levels across TV

channels and other sound sources connected to the

AV jacks. When AGC is on, the input/output gain is

boosted for low signal levels and reduced for high

signal levels (see Fig. 21).

Figure 21: AGC Effect on Sound

The circuit detects level changes via AGC Det 1,

which outputs to AGC Det 2 (Control circuit) to

provide a gain factor for both left and right channel

AGC circuits. At a level predetermined by the RC

network on IC2501 pin 5, the internal switch toggles

the contacts and adjusts the gain to the output

terminals.

Bass, Treble, Balance

When a user makes an adjustment to the audio

output via the front keyboard or the remote control,

data from the MPU is clocked (at 12 MHz) via the

I

2

C bus to the IC2501 I

2

C interface at pins 16 and

17. Pulse width modulation switching controls which

DAC will be applied to the audio signal.

AI Sound

The IC2501 AI Sound circuit uses an algorithm

based on the difference in frequency characteristics

between music and speech (see Fig. 22 and

Fig. 23). The circuit is incorporated by simple

hardware and microprocessor control to equalize the

sound level across inputs and automatically controls

bass and treble to the optimum degree.

Continuous speech consists of repetitions of a

consonant, a vowel and silence. Power levels

change rapidly. Consonants have large changes in

power level and spectrum; vowels are steadier, with

smaller changes.

Musical sounds have relatively small changes in

power and spectrum, with longer steady parts.

27

Figure 22: AI Audio Algorithm

The original waveform (speech or music) is sent to a

level rectifying circuit, a waveshaping circuit, and

then is fed to the microprocessor. The

microprocessor samples the waveform and sets

threshold values, then makes judgements whether

to boost bass and treble for music or reduce them for

speech.

Figure 23: AI Audio Frequency Response

Audio Multiplex System

Abstract

In audio multiplex broadcasting, a separate sound

signal, unrelated to the broadcast content, is sent in

addition to the monaural sound. This is done in order

to accomplish transmission of stereo signals and is

achieved via frequency multiplex technology. In

todays broadcast, the traditional L + R and L - R

signals are sent. The signals are monitored,

cleaned, decompressed and finally separated in the

matrix circuit to the L and R components.

Matrix: (L+R) + (L-R) = 2L

(L+R) - (L-R) = 2R

The North American System

The North American Television sound system is

composed of three types of modulation: FM, FM

Multiplex (stereo and SAP) and AM (see Fig. 24).

Monaural Broadcasting: Monaural sound (L + R) is

sent as 25kHz FM signal in the 4.5MHz audio

carrier wave.

Multiplex Broadcasting: The L (left) and R (right)

signals are sent in two different packets in addition

to other required signals. The multiplex signal has

four components:

L + R - identical to the monaural signal.

L - R - amplitude modulated with a center

frequency of 35.1kHz (twice the horizontal

frequency of 15.75kHz.)

Secondary Audio Programming (SAP) - FM

modulated (+/- 15kHz) with a center

frequency of 78.75kHz (5f

h

).

Stereo pilot - FM signal at 15.75kHz (

5kHz).

28

Figure 24: North American Multiplex

Audio Amplifiers

Fig. 25 depicts the process in which the audio

amplifiers operate. The MPU controls the volume

and mute operation. The amplified signals output at

pin 10 and is sent to the speakers. Note that on a

mono receivers only the left audio amplifier is

operational, sending the signal to the single speaker.

Figure 25: Audio Amplifiers

fH 2fH 3fH 4fH 5fH

AM

FM

f (Hz)

2 (L - R)

L + R

SAP

25kHz

50kHz

15kHz

f

H

= 15.75kHz

FM

S

T

P

i

l

o

t

S

i

g

n

a

l

5

k

H

z

C

a

r

r

i

e

r

D

e

v

i

a

t

i

o

n

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

DEFLECTION

30

Deflection Circuit

Vertical Output Circuit

Sawtooth Wave Generating Circuit

The vertical sync pulse at pin 2 creates a timing

sawtooth wave in C452 (see Fig. 26). This

determines the amplitude of the voltage at pin 4,

which is controlled by pin 68 of the MPU. This

adjustment is available in service mode. The voltage

at pin 4 sets the 50-60 Hz amplitude for the voltage

at pin 5. The vertical drive corrects the rectilinear

straightness, vertical amplitude and pulse amplitude

in the same IC.

Drive Circuit

1. The sawtooth wave is sent to the vertical drive

circuit. The wave current in the vertical

deflection coil is fed back to pin 7 to improve

the vertical straightness of the signal.

2. The vertical drive section of IC451 amplifies

the sawtooth wave to correct for straightness

of the wave so the vertical output circuit will

operate. The corrected wave is sent to the

vertical output circuit.

Figure 26: IC451 - Vertical Deflection Circuit

31

Vertical Output Pulse Amplifying Circuit

Vertical Output Circuit Operation

1. The sawtooth wave voltage from the vertical

drive circuit is inverted in Q1 and input to Q2

and Q3 (see Fig. 27).

2. The Q2 and Q3 threshold voltage is set to the

center of the sawtooth wave. The first half of

the wave turns on Q2, resulting in the charging

current (a) being sent to C1 (see Fig. 28).

3. The second half of the wave turns on Q3,

resulting in the discharge current (b) being

output from C1.

4. A sawtooth wave current is sent to the

deflection coil. However, to reverse the current

within the vertical flyback period, the pulse

from the pulse amplifier circuit is added to the

collector of Q2. This results in a large voltage

input to the deflection coil during the instant

after Q2 is turned on.

Pulse Amplifier Circuit (Pump Up) Operation

1. When currents (a) and (b) are sent (during the

vertical scanning period), Q4 is off because no

voltage is input to its base. A negative pulse

from the vertical deflection coil is fed back to

the base of Q5, which turns Q5 on. 26V are

sent through D1, which inputs a 26V charge to

C2.

2. The differentiated pulse during the flyback

period is added to the base of Q4 and Q5,

turning Q4 on and Q5 off. 26V is input to C2

negative (-) pin through Q4 and added to the

26V C2 charge, resulting in a 52V pulse at

pin 13 (see Fig. 29).

3. The 52V pulse is input to the deflection coil,

raising the electron beam in one instant.

Figure 27: IC451 - Vertical Output Pulse Amplifying Circuit

Figure 28: IC451 pin 12 Voltage Figure 29: Pump Up Wave

Voltage input to the Deflection Coil Q1 Collector Differential

Q2 ON Q3 ON

Waveform of

Q4-Q5 base Pin 9 voltage

Pin13 voltage

32

Horizontal Output Circuit

Horizontal Output

The square wave of the horizontal signal sent by the

MPU is applied to Q501, the horizontal drive.

That turns Q501 on (see Fig. 30). 130 volts flows

through the primary of T501 and the horizontal drive,

Q501. A horizontal pulse is induced into the

secondary windings of T501. This pulse drives the

horizontal output Q551 to make the sawtooth wave

current in H-DY (horizontal deflection coil) and EHT

(extra high tension voltage).

Figure 30: Horizontal Drive and Output Circuit

33

Horizontal Drive Circuit

Figure 31: Horizontal Drive Circuit

34

Notes

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

POWER SUPPLY

3

6

Figure 32: Power Supply Overview (NA7D)

3

7

Figure 33: Power Supply Overview (NA7A)

38

Protection Circuits

Over Current Protection

The over current protection circuit is designed to prevent

damage to the Receiver due to shorts in the 130V line.

During normal operation, current flowing through R821 &

R822 produces low voltage across the resistors that is

not sufficient to turn Q820 ON.

When a short occurs, the current through R821 & R822

increases, causing a rise in the voltage across the

resistors. When the voltage drop reaches the point

where V

be

is high enough to turn Q820 ON, a signal is

sent by Q820 to the MPU pin 9 (KEY2). The MPU then

shuts the Receiver OFF.

Spot Killer

The spot killer circuit is designed to prevent the high

intensity beam that could form at the center of the screen

in an event of abnormal power loss.

The circuit is made up of Q605, Q606 and related

components.

During normal operation, the high voltage at the base of

the PNP transistor, Q605, keeping it OFF. When Q605 is

off, it keeps Q606 OFF. Under these conditions, C606 is

charged when Q606 is OFF. That prevents D607 ~ D609

from conducting. That also allows the only path for the

RGB current to flow (from Q006 ~ Q008) to the C board,

the CRT driver.

When the 12V line goes low due to an abrupt loss of

power, Q605 & Q606 turn ON and C606 discharges

allowing the output from Q006 ~ Q008 to flow through

D607 ~ D609. Therefore the RGB output signal is

prevented from flowing to the C board. See Fig. 34.

Figure 34: Spotkiller Protector Circuit

Neck Protector (Fig. 35)

The neck protector protects the CRT in an event of

shorting in the V-out or DY circuits. The circuit consists

of Q451 & Q452 and related components.

During normal operation, the vertical out from IC451

conducts through the Zener diode, D452. That keeps

Q451 ON and Q452 OFF. A high signal is sent to the

MPU pin 40 indicating normal conditions.

When the Vert out of IC451 is low (damage to the IC), it

turns Q451 OFF. The base of Q452 is at ~9V, turning it

ON. Q452 starts conducting, lowering the voltage at

MPU pin 40. The MPU senses the change that occurred

and it shuts down the RGB output, resulting in a black

screen

39

Figure 35: Neck Protector Circuit

Figure 36: Standby Voltage

Figure 37: DC Operation (AC/DC Models Only)

130V

DC Voltage Supply

Power

40

Figure 38: Degaussing Coil (AC/DC Models Only)

Printed in USA

K01032593ZR0330

Вам также может понравиться

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Noblex 21TC667U STR-W6754 LA76933 LA78141-E R2S15908SPP LA72703 LA42205-E Chassis LA8-AДокумент29 страницNoblex 21TC667U STR-W6754 LA76933 LA78141-E R2S15908SPP LA72703 LA42205-E Chassis LA8-Amarquitos550b100% (1)

- Radar 1622 Service ManualДокумент42 страницыRadar 1622 Service Manualaepsaepudin7033Оценок пока нет

- TCL Chasis M28 PDFДокумент78 страницTCL Chasis M28 PDFjosenicolas12000Оценок пока нет

- Rca 21t18 Chassis-M28Документ81 страницаRca 21t18 Chassis-M28Estalyn GomezОценок пока нет

- 29TC679FДокумент29 страниц29TC679FGustavo ChavezОценок пока нет

- Chassis M28!01!2135MH-MA1 Manual de ServicioДокумент81 страницаChassis M28!01!2135MH-MA1 Manual de ServicioGiovanny Gregorio Gonzalez SanchezОценок пока нет

- Audiologic 2901TVGX - Sanyo C21LB29S Chasis LA5-AДокумент30 страницAudiologic 2901TVGX - Sanyo C21LB29S Chasis LA5-AWalter AlvarengaОценок пока нет

- Sanyo Camara Circuitos Vpc-Az1 - sm5310328Документ52 страницыSanyo Camara Circuitos Vpc-Az1 - sm5310328jorge_chaparro_1Оценок пока нет

- GP3 - Complete GuideДокумент31 страницаGP3 - Complete GuideAndres AlegriaОценок пока нет

- TCL TV M35 36 Service ManualДокумент96 страницTCL TV M35 36 Service ManualRituparna Dutta Chowdhury100% (1)

- Sanyo c20lb87b, 20tc645 CH Lc1b (ET)Документ24 страницыSanyo c20lb87b, 20tc645 CH Lc1b (ET)Luis DominguezОценок пока нет

- TWRKV46F150 PMSM SensorlessДокумент22 страницыTWRKV46F150 PMSM Sensorlessb_dupОценок пока нет

- TV Philco Pfs2980Документ30 страницTV Philco Pfs2980Mario Cesar RuizОценок пока нет

- SERVICE MANUAL Colour Television: Model No. C29FS51Документ30 страницSERVICE MANUAL Colour Television: Model No. C29FS51dmst622Оценок пока нет

- SERVICE MANUAL Colour Television: Model No. PS2114Документ30 страницSERVICE MANUAL Colour Television: Model No. PS2114Roger Martínez BermúdezОценок пока нет

- Sanyo CM29FS2 FB1B PDFДокумент41 страницаSanyo CM29FS2 FB1B PDFJerald D'costaОценок пока нет

- Pourquoi Utilser Signal Conditioner LS7084Документ4 страницыPourquoi Utilser Signal Conditioner LS7084bientinhxanhthamОценок пока нет

- Manual Service 32LC821F PDFДокумент50 страницManual Service 32LC821F PDFies837Оценок пока нет

- Service Manual: Mb97 IdtvДокумент64 страницыService Manual: Mb97 IdtvAli Rawefi100% (1)

- 70 1495Документ100 страниц70 1495ka2zev100% (1)

- Sanyo Mod.c21lf37 Chassis La5-A PDFДокумент30 страницSanyo Mod.c21lf37 Chassis La5-A PDFroto44Оценок пока нет

- Specifications: 1. Picture Tube 4. Power SupplyДокумент49 страницSpecifications: 1. Picture Tube 4. Power Supplyfvb_spamОценок пока нет

- Sanyo c29lk40sДокумент30 страницSanyo c29lk40sAdrian HernandezОценок пока нет

- Voltage To Frequency ConverterДокумент7 страницVoltage To Frequency ConverterRodfer SorianoОценок пока нет

- Sanyo C29FS51 Chassis LB6-A Service ManualДокумент30 страницSanyo C29FS51 Chassis LB6-A Service Manualnaupas007100% (1)

- Color Monitor: Service ManualДокумент24 страницыColor Monitor: Service Manuala4623Оценок пока нет

- Teac MC-D95Документ32 страницыTeac MC-D95Djalma MilanОценок пока нет

- PHILIPS LC04 LCD TV Technical Training ManualДокумент44 страницыPHILIPS LC04 LCD TV Technical Training Manualcentauro2013Оценок пока нет

- TK 3107Документ28 страницTK 3107Abe LimiОценок пока нет

- Channel Unit E&M VF-P Op HandbookДокумент97 страницChannel Unit E&M VF-P Op HandbookzehantnОценок пока нет

- Raytheon R1206XXДокумент70 страницRaytheon R1206XXtyutyuОценок пока нет

- TK-2107 SMДокумент30 страницTK-2107 SMgpasztori2262Оценок пока нет

- Chassis LA6-A LA6A Mono Manual de ServicioДокумент26 страницChassis LA6-A LA6A Mono Manual de Serviciojavier258Оценок пока нет

- Sanyo LCD-24XH7 - Manual de ServicioДокумент38 страницSanyo LCD-24XH7 - Manual de ServicioCarlos D MauroОценок пока нет

- Panoramic: SERVICE MANUAL Colour TelevisionДокумент26 страницPanoramic: SERVICE MANUAL Colour TelevisionYanina MimosaОценок пока нет

- Basic Electronics Circuits: Experiment 1Документ9 страницBasic Electronics Circuits: Experiment 1SavithaGnОценок пока нет

- CVMK Power Analyzer Manual Part1Документ29 страницCVMK Power Analyzer Manual Part1dsffgdsgsgasfgasfgОценок пока нет

- Service Manual: 17-Inch LCD Monitor U170ATAДокумент40 страницService Manual: 17-Inch LCD Monitor U170ATAStefanОценок пока нет

- UPS SystemДокумент4 страницыUPS Systemमृत्युंजय झाОценок пока нет

- China Ve01 With Tda93xx An17821 Stv9302a La78040 Ka5q0765-SmДокумент40 страницChina Ve01 With Tda93xx An17821 Stv9302a La78040 Ka5q0765-SmAmadou Fall100% (1)

- SAF7113H: 1. General DescriptionДокумент75 страницSAF7113H: 1. General DescriptionEbbanoFristsОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorОт Everand110 Waveform Generator Projects for the Home ConstructorРейтинг: 4 из 5 звезд4/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1От EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Рейтинг: 4.5 из 5 звезд4.5/5 (3)

- Power Systems-On-Chip: Practical Aspects of DesignОт EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardОценок пока нет

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsОт EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsОценок пока нет

- Modern Control of DC-Based Power Systems: A Problem-Based ApproachОт EverandModern Control of DC-Based Power Systems: A Problem-Based ApproachОценок пока нет

- Digital Signal Processing Using the ARM Cortex M4От EverandDigital Signal Processing Using the ARM Cortex M4Рейтинг: 1 из 5 звезд1/5 (1)

- Advanced Control of AC / DC Power Networks: System of Systems Approach Based on Spatio-temporal ScalesОт EverandAdvanced Control of AC / DC Power Networks: System of Systems Approach Based on Spatio-temporal ScalesОценок пока нет

- Circuito y PCB Balastro Electronico - 37BДокумент3 страницыCircuito y PCB Balastro Electronico - 37Bjulio gamboaОценок пока нет

- Air Con Service ManualДокумент39 страницAir Con Service Manualjulio gamboa100% (1)

- Alto PBM8.250 500 PDFДокумент51 страницаAlto PBM8.250 500 PDFjulio gamboaОценок пока нет

- Manual WaveletДокумент626 страницManual Waveletjulio gamboaОценок пока нет

- Aplicaciones Del MC10116Документ4 страницыAplicaciones Del MC10116julio gamboaОценок пока нет

- Blues Piano (Metodo para PartiturasДокумент37 страницBlues Piano (Metodo para PartiturasLuiza Rodrigues100% (10)

- Eon Silicon SolutionsДокумент6 страницEon Silicon Solutionsjulio gamboaОценок пока нет

- Guia de Refer en CIA para El Reemplazo de Transistores Peavey - VideosistemasДокумент24 страницыGuia de Refer en CIA para El Reemplazo de Transistores Peavey - VideosistemasGloria Vela0% (1)

- 95-03097 Ballvlv300350 WCB PDFДокумент26 страниц95-03097 Ballvlv300350 WCB PDFasitdeyОценок пока нет

- Art Appreciation Chapter 3 SummaryДокумент6 страницArt Appreciation Chapter 3 SummaryDiego A. Odchimar IIIОценок пока нет

- Auditing Principles and Practices-IДокумент8 страницAuditing Principles and Practices-IMoti BekeleОценок пока нет

- Data Science ProjectsДокумент3 страницыData Science ProjectsHanane GríssetteОценок пока нет

- Driver Drowsiness Detection System Using Raspberry PiДокумент7 страницDriver Drowsiness Detection System Using Raspberry PiIJRASETPublicationsОценок пока нет

- Financial Institutions Markets and ServicesДокумент2 страницыFinancial Institutions Markets and ServicesPavneet Kaur Bhatia100% (1)

- Reaction PaperДокумент3 страницыReaction PaperLois DolorОценок пока нет

- LU 5.1 ElectrochemistryДокумент32 страницыLU 5.1 ElectrochemistryNurAkila Mohd YasirОценок пока нет

- UG ENGLISH Honours PDFДокумент59 страницUG ENGLISH Honours PDFMR.Shantanu SharmaОценок пока нет

- 02 CT311 Site WorksДокумент26 страниц02 CT311 Site Worksshaweeeng 101Оценок пока нет

- SPFL Monitoring ToolДокумент3 страницыSPFL Monitoring ToolAnalyn EnriquezОценок пока нет

- Ultimate Trading Guide - Flash FUT 2023Документ33 страницыUltimate Trading Guide - Flash FUT 2023marciwnw IОценок пока нет

- Outlook of PonДокумент12 страницOutlook of Ponty nguyenОценок пока нет

- API RP 7C-11F Installation, Maintenance and Operation of Internal Combustion Engines.Документ3 страницыAPI RP 7C-11F Installation, Maintenance and Operation of Internal Combustion Engines.Rashid Ghani100% (1)

- Canon I-SENSYS MF411dw Parts CatalogДокумент79 страницCanon I-SENSYS MF411dw Parts Catalogmarian100% (1)

- Dist - Propor.danfoss PVG32Документ136 страницDist - Propor.danfoss PVG32Michal BujaraОценок пока нет

- Lab Science of Materis ReportДокумент22 страницыLab Science of Materis ReportKarl ToddОценок пока нет

- Study and Interpretation of The ScoreДокумент10 страницStudy and Interpretation of The ScoreDwightPile-GrayОценок пока нет

- Population Second TermДокумент2 страницыPopulation Second Termlubna imranОценок пока нет

- The Intel 8086 / 8088/ 80186 / 80286 / 80386 / 80486 Jump InstructionsДокумент3 страницыThe Intel 8086 / 8088/ 80186 / 80286 / 80386 / 80486 Jump InstructionsalexiouconОценок пока нет

- Legrand Price List-01 ST April-2014Документ144 страницыLegrand Price List-01 ST April-2014Umesh SutharОценок пока нет

- Level of Organisation of Protein StructureДокумент18 страницLevel of Organisation of Protein Structureyinghui94Оценок пока нет

- Polyether Polyol Production AssignmentДокумент9 страницPolyether Polyol Production AssignmentanurdiaОценок пока нет

- Our Story Needs No Filter by Nagarkar SudeepДокумент153 страницыOur Story Needs No Filter by Nagarkar SudeepKavya SunderОценок пока нет

- Bichelle HarrisonДокумент2 страницыBichelle HarrisonShahbaz KhanОценок пока нет

- Wordbank 15 Coffee1Документ2 страницыWordbank 15 Coffee1akbal13Оценок пока нет

- SCIENCE 11 WEEK 6c - Endogenic ProcessДокумент57 страницSCIENCE 11 WEEK 6c - Endogenic ProcessChristine CayosaОценок пока нет

- Module 7 NSTP 1Документ55 страницModule 7 NSTP 1PanJan BalОценок пока нет

- Vendor Registration FormДокумент4 страницыVendor Registration FormhiringОценок пока нет

- Equilibrium of A Rigid BodyДокумент30 страницEquilibrium of A Rigid BodyChristine Torrepenida RasimoОценок пока нет