Академический Документы

Профессиональный Документы

Культура Документы

Acpm 5001

Загружено:

pavlodeОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Acpm 5001

Загружено:

pavlodeАвторское право:

Доступные форматы

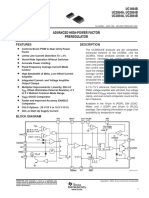

ACPM-5001-TR1

Multimode PA - UMTS Band1 and CDMA IMT (1920-1980MHz)

3x3mm Power Amplifer Module with Coupler

Data Sheet

Description

The ACPM-5001-TR1 is a fully matched 10-pin surface

mount module developed to support multimode applica-

tions including UMTS Band1 and CDMA IMT band(Band6).

The ACPM-5001-TR1 meets stringent linearity require-

ments up to 28.25dBm output power for UMTS Rel.99

and 27.75 dBm for CDMA. The 3mmx3mm form factor

package is self contained, incorporating 50ohm input and

output matching networks. The PA also contains internal

DC blocking capacitors for RF input and output ports.

The ACPM-5001-TR1 features 5

th

generation of CoolPAM

(CoolPAM5) circuit technology which supports 3 power

modes active bypass, mid power and high power modes.

The CoolPAM is stage bypass technology enhancing

PAE (power added efciency) at low and medium power

range. The active bypass feature is added to CoolPAM5 to

enhance the PAE further at low output range and it enables

the PA to have exceptionally low quiescent current. It

dramatically saves the average power consumption and

accordingly extends the talk time of mobiles and prolongs

a battery life.

A directional coupler is integrated into the module and

both coupling and isolation ports are available exter-

nally, supporting daisy chain. The integrated coupler

has excellent coupler directivity, which minimizes the

coupled output power variation or delivered power

variation caused by the load mismatch from the antenna.

The coupler directivity, or the output power variation into

the mismatched load, is critical to the TRP and SAR per-

formance of the mobile phones in real feld operations as

well as compliance tests for the system specifcations.

The ACPM-5001 has integrated on-chip Vref and on-module

bias switch as the one of the key features of the CoolPAM-5,

so an external constant voltage source is not required,

eliminating the external LDO regulators and switches

from circuit boards of mobile devices. It also makes the PA

fully digital-controllable by the Ven pin that simply turns

the PA on and of from the digital control logic input from

Description (Cont.)

baseband chipsets. All of the digital control input pins

such as the Ven, Vmode and Vbp are fully CMOS compat-

ible and can operate down to the 1.35V logic. The current

consumption by digital control pins is negligible.

The power amplifer is manufactured on an advanced

InGaP HBT (hetero-junction Bipolar Transistor) MMIC

(microwave monolithic integrated circuit) technology

ofering state-of-the-art reliability, temperature stability

and ruggedness.

Features

x Thin Package (0.9mm typ)

x Excellent Linearity

x 3-mode power control with Vbp and Vmode

Bypass / Mid Power Mode / High Power Mode

x High Efciency at max output power

x 10-pin surface mounting package

x Internal 50ohm matching networks for both RF input

and output

x Integrated coupler

Coupler and Isolation ports for daisy chain

x Lead-free, RoHS compliant, Green

Applications

x UMTS (WCDMA, HSDPA, HSUPA, HSPA+)

x CDMA

Ordering Information

Part Number Number of Devices Container

ACPM-5001-TR1 1000 178mm (7)

Tape/Reel

ACPM-5001-BLK 100 Bulk

2

Absolute Maximum Ratings

No damage assuming only one parameter is set at limit at a time with all other parameters set at or below nominal value.

Operation of any single parameter outside these conditions with the remaining parameters set at or below nominal

values may result in permanent damage.

Description Min. Typ. Max. Unit

RF Input Power (Pin) 0 10 dBm

DC Supply Voltage (Vcc1, Vcc2) 0 3.4 5.0 V

Enable Voltage (Ven) 0 2.6 3.3 V

Mode Control Voltage (Vmode) 0 2.6 3.3 V

Bypass Control (Vbp) 0 2.6 3.3 V

Storage Temperature (Tstg) -55 25 +125 C

Recommended Operating Condition

Description Min. Typ. Max. Unit

DC Supply Voltage (Vcc1, Vcc2) 3.2 3.4 4.2 V

Enable Voltage (Ven)

Low

High

0

1.35

0

2.6

0.5

3.1

V

V

Mode Control Voltage (Vmode)

Low

High

0

1.35

0

2.6

0.5

3.1

V

V

Bypass Control Voltage (Vbp)

Low

High

0

1.35

0

2.6

0.5

3.1

V

V

Operating Frequency (fo) 1920 1980 MHz

Ambient Temperature (Ta)

UMTS

CDMA

-20

-30

25

25

85

85

C

C

Operating Logic Table

Power Mode Ven Vmode Vbp Pout (Rel99)

Pout (HSDPA,

HSUPA MPR=0dB)

High Power Mode High Low X ~ 28.25 dBm ~ 27.25 dBm

Mid Power Mode High High Low ~ 17 dBm ~ 16 dBm

Bypass Mode High High High ~ 7 dBm ~ 6 dBm

Shut Down Mode Low Low Low

3

Electrical Characteristics for WCDMA Mode

Conditions: Vcc = 3.4V, Ven = 2.6V, Ta = 25C, Zin/Zout = 50ohm

Signal Confguration: 3GPP (DPCCH + 1DPDCH) Up-Link unless specifed otherwise.

Characteristics Condition Min. Typ. Max. Unit

Operating Frequency Range 1920 1980 MHz

Maximum Output Power

(High Power Mode)

Rel99 28.25 dBm

HSDPA, HSUPA MPR=0dB 27.25 dBm

CDMA2000 RC1 27.75 dBm

Gain High Power Mode, Pout=28.25dBm 23 27 dB

Mid Power Mode, Pout=17dBm 14 18 dB

Bypass Mode, Pout=7dBm 7 11 dB

Power Added Efciency High Power Mode, Pout=28.25dBm 36.3 40 %

Mid Power Mode, Pout=17dBm 15.3 20.1 %

Bypass Mode, Pout=7dBm 6.8 12.3 %

Total Supply Current High Power Mode, Pout=28.25dBm 490 540 mA

Mid Power Mode, Pout=17dBm 72 95 mA

Mid Power Mode, Pout=13.5dBm 50 mA

Bypass Mode, Pout=7dBm 11 20 mA

Bypass Mode, Pout=3.5dBm 8.5 mA

Quiescent Current High Power Mode 85 117 150 mA

Mid Power Mode 10 20 30 mA

Bypass Mode 1 3.1 5 mA

Enable Current High Power Mode 5 PA

Mid Power Mode 5 PA

Bypass Mode 5 PA

Mode Control Current Mid Power Mode 5 PA

Bypass Mode 5 PA

Bypass Control Current Bypass 5 PA

Total Current in Power-down mode Ven=0V, Vmode=0V, Vbp=0V 5 PA

UMTS Adjacent

Channel

Leakage Ratio

(ACLR)

5 MHz ofset

10 MHz ofset

Pout (max power MPR)

-41

-54

-36

-46

dBc

dBc

Adjacent Channel

Power Ratio (ACPR)

1.25 MHz ofset

1.98 MHz ofset

Pout max power -50

-58

-44

-53

dBc

dBc

Harmonic

Suppression

Second

Third

High Power Mode, Pout=28.25dBm -42

-56

-35

-45

dBc

dBc

Input VSWR 2.5:1

Stability (Spurious Output) VSWR 5:1, All phase -60 dBc

Rx Band Noise Power (Vcc=4.2V) High Power Mode, Pout=28.25dBm -137 dBm/Hz

GPS Band Noise Power (Vcc=4.2V) High Power Mode, Pout=28.25dBm -141 dBm/Hz

ISM Band Noise Power (Vcc=4.2V) High Power Mode, Pout=28.25dBm -145 dBm/Hz

Rx Band Gain (21102170MHz) Where G is gain in Tx band G-3 dB

DCS Band Gain (1805-1880MHz) Where G is gain in Tx band G dB

GPS Band Gain (1574-1577MHz) Where G is gain in Tx band G-2.5 dB

GLONASS Band Gain (1597-1607MHz) Where G is gain in Tx band G-2 dB

ISM Band Gain (2400-2483.5MHz) Where G is gain in Tx band G-10 dB

Media Band Gain (716-728MHz) Where G is gain in Tx band G-19 dB

Phase Discontinuity bypass modelmid power mode,

at Pout=7dBm

mid power modelhigh power mode,

at Pout=17dBm

20

30

deg

deg

Ruggedness Pout<28.25dBm, Pin<10dBm,

All phase High Power Mode

10:1 VSWR

Coupling factor RF Out to CPL port 20 dB

Daisy Chain Insertion Loss ISO port to CPL port, Ven=Low 0.25 dB

4

HSDPA Signal confguration used:

3GPP TS 34.121-1

Annex C (normative e): Measurement channels

C.10.1 UL reference measurement channel for HSDPA tests

Table C.10.1.4: E values for transmitter characteristics tests with HS-DPCCH

Sub-test 2 (CM=1.0, MPR=0.0)

HSUPA signal confguration used:

3GPP TS 34.121-1

Annex C (normative): Measurement channels

C.11.1 UL reference measurement channel for E-DCH tests

Table C.11.1.3: E values for transmitter characteristics tests with HS-DPCCH and E-DCH Sub-test 1 (CM=1.0, MPR=0.0)

At 3.2V operation, 0.5dB backof is allowed for maximum power output.

Footprint

All dimensions are in millimeter

X-Ray Top View

0.125

0.10

0.35

0.35

0.60

0.10

1.50

0.25

0.3

Pin 1

PIN Description

Pin # Name Description

1 Vcc1 DC Supply Voltage

2 RFin RF Input

3 Vbp Bypass Control

4 Vmode Mode Control

5 Ven PA Enable

6 CPL Coupling port of Coupler

7 GND Ground

8 ISO Isolation port of Coupler

9 RFOut RF Out

10 Vcc2 DC Supply Voltage

5

Package Dimensions

All dimensions ae in millimeter

Marking Specifcation

Manufacturing Part Number

Lot Number

P Manufacturing Info

YY Manufacturing Year

WW Work Week

QAAAAA Assembly Lot Number

Pin 1 Mark

A5001

PYYWW

QAAAAA

3 0.1

2

3

4

3 0.1

Pin 1 Mark

1

0.5

0.9 0.1

5

9

8

7

10

6

6

Metallization

Solder Mask Opening

Solder Paste Stencil Aperture

PCB Design Guidelines

The recommended PCB land pattern is shown in fgures

on the left side. The substrate is coated with solder mask

between the I/O and conductive paddle to protect the

gold pads from short circuit that is caused by solder

bleeding/bridging.

Stencil Design Guidelines

A properly designed solder screen or stencil is required

to ensure optimum amount of solder paste is deposited

onto the PCB pads.

The recommended stencil layout is shown here. Reducing

the stencil opening can potentially generate more voids.

On the other hand, stencil openings larger than 100% will

lead to excessive solder paste smear or bridging across

the I/O pads or conductive paddle to adjacent I/O pads.

Considering the fact that solder paste thickness will

directly afect the quality of the solder joint, a good choice

is to use laser cut stencil composed of 0.100mm(4mils) or

0.127mm(5mils) thick stainless steel which is capable of

producing the required fne stencil outline.

0.65

0.45

0.50

0.60

1.50

1.30

0.525

0.55 0.45

1.10

1.10

0.60

0.35

0.475

0.30

0.60

0.35

0.55

0.45

on 0.5mm pitch

0.3mm

0.475

connected to a inner layer

through a via hole for a

better isolation between

CPL_IN(ISO) and RFout

7

Evaluation Board Schematic

Evaluation Board Description

1 Vcc1

2 RF In

3 Vbp

4 Vmode

5 Ven

Vcc2 10

RF Out 9

GND 7

CPL 6

Ven

Vmode

RF In

Vcc1 Vcc2

Isolation

C1

100pF

C2

100pF

2.2uF

C6 C7

330pF

C4

330pF

C5

2.2uF

Vbp

C3

100pF

ISO 8

RF Out

Coupler

50ohm

C1

C2

C3

C4 C6

C5 C7

A5001

PYYWW

QAAAAA

8

Tape and Reel Information

Dimension List

Annote Millimeter

A0 3.400.10

B0 3.400.10

K0 1.350.10

D0 1.550.05

D1 1.600.10

P0 4.000.10

P1 8.000.10

Annote Millimeter

P2 2.000.05

P10 40.000.20

E 1.750.10

F 5.500.05

W 12.000.30

T 0.300.05

Tape and Reel Format 3 mm x 3 mm

A

5

0

0

1

P

Y

Y

W

W

Q

A

A

A

A

A

9

Plastic Reel Format (all dimensions are in millimeters)

Reel Drawing

NOTES:

1. Reel shall be labeled with the following

information (as a minimum).

a. manufacturers name or symbol

b. Avago Technologies part number

c. purchase order number

d. date code

e. quantity of units

2. A certicate of compliance (c of c) shall

be issued and accompany each shipment

of product.

3. Reel must not be made with or contain

ozone depleting materials.

4. All dimensions in millimeters (mm)

50 min.

12.4

+2.0

-0.0

18.4 max.

25

min wide (ref)

Slot for carrier tape

insertion for attachment

to reel hub (2 places 180 apart)

BACK VIEW

FRONT VIEW

178

Shading indicates

thru slots

+0.4

-0.2

21.0 0.8

13.0 0.2

1.5 min.

10

Handling and Storage

ESD (Electrostatic Discharge)

Electrostatic discharge occurs naturally in the environ- naturally in the environ- naturally in the environ-

ment. With the increase in voltage potential, the outlet of

neutralization or discharge will be sought. If the acquired

discharge route is through a semiconductor device, de- through a semiconductor device, de- through a semiconductor device, de- de- de-

structive damage will result.

ESD countermeasure methods should be developed and

used to control potential ESD damage during handling in

a factory environment at each manufacturing site.

MSL (Moisture Sensitivity Level)

Plastic encapsulated surface mount package is sensitive to

damage induced by absorbed moisture and temperature.

Avago Technologies follows JEDEC Standard J-STD 020B.

Each component and package type is classifed for

moisture sensitivity by soaking a known dry package at

Moisture Classifcation Level and Floor Life

MSL Level Floor Life (out of bag) at factory ambient =< 30C/60% RH or as stated

1 Unlimited at =< 30C/85% RH

2 1 year

2a 4 weeks

3 168 hours

4 72 hours

5 48 hours

5a 24 hours

6 Mandatory bake before use. After bake, must be refowed within the time limit specifed on the label

Note :

1. The MSL Level is marked on the MSL Label on each shipping bag.

various temperatures and relative humidity, and times.

After soak, the components are subjected to three con-

secutive simulated refows.

The out of bag exposure time maximum limits are deter-

mined by the classifcation test describe below which cor-

responds to a MSL classifcation level 6 to 1 according to

the JEDEC standard IPC/JEDEC J-STD-020B and J-STD-033.

ACPM-5001-TR1 is MSL3. Thus, according to the J-STD-033

p.11 the maximum Manufacturers Exposure Time (MET)

for this part is 168 hours. After this time period, the part

would need to be removed from the reel, de-taped and

then re-baked. MSL classifcation refow temperature for

the ACPM-5001-TR1 is targeted at 260C+0/-5C. Figure

and table on next page show typical SMT profle for

maximum temperature of 260 +0/-5C.

11

Refow Profle Recommendations

Typical SMT Refow Profle for Maximum Temperature = 260 +0/-5C

25

Time

T

e

m

p

e

r

a

t

u

r

e

Tp

TL

tp

tL

t 25C to Peak

Ramp-up

ts

Tsmin

Ramp-down

Preheat

Critical Zone

T

L to Tp

Tsmax

Typical SMT Refow Profle for Maximum Temperature = 260 +0/-5C

Profle Feature Sn-Pb Solder Pb-Free Solder

Average ramp-up rate (TL to TP) 3C/sec max 3C/sec max

Preheat

Temperature Min (Tsmin)

Temperature Max (Tsmax)

Time (min to max) (ts)

100C

150C

60-120 sec

150C

200C

60-120 sec

Tsmax to TL

Ramp-up Rate 3C/sec max

Time maintained above:

Temperature (TL)

Time (TL)

183C

60-150 sec

217C

60-150 sec

Peak temperature (Tp) 240 +0/-5C 260 +0/-5C

Time within 5C of actual Peak Temperature (tp) 10-30 sec 20-40 sec

Ramp-down Rate 6C/sec max 6C/sec max

Time 25C to Peak Temperature 6 min max. 8 min max.

12

Storage Condition

Packages described in this document must be stored

in sealed moisture barrier, antistatic bags. Shelf life in a

sealed moisture barrier bag is 12 months at <40C and

90% relative humidity (RH) J-STD-033 p.7.

Out-of-Bag Time Duration

After unpacking the device must be soldered to the PCB

within 168 hours as listed in the J-STD-020B p.11 with

factory conditions <30C and 60% RH.

Baking

It is not necessary to re-bake the part if both conditions

(storage conditions and out-of bag conditions) have been

satisfed. Baking must be done if at least one of the con-

ditions above have not been satisfed. The baking condi-

tions are 125C for 12 hours J-STD-033 p.8.

CAUTION

Tape and reel materials typically cannot be baked at the

temperature described above. If out-of-bag exposure

time is exceeded, parts must be baked for a longer time

at low temperatures, or the parts must be de-reeled,

de-taped, re-baked and then put back on tape and reel.

(See moisture sensitive warning label on each shipping

bag for information of baking).

Board Rework

Component Removal, Rework and Remount

If a component is to be removed from the board, it is

recommended that localized heating be used and the

maximum body temperatures of any surface mount

component on the board not exceed 200C. This method

will minimize moisture related component damage. If any

component temperature exceeds 200C, the board must

be baked dry per 4-2 prior to rework and/or component

removal. Component temperatures shall be measured at

the top center of the package body. Any SMD packages

that have not exceeded their foor life can be exposed to

a maximum body temperature as high as their specifed

maximum refow temperature.

Removal for Failure Analysis

Not following the above requirements may cause

moisture/refow damage that could hinder or com- damage that could hinder or com- damage that could hinder or com- com- com-

pletely prevent the determination of the original failure

mechanism.

Baking of Populated Boards

Some SMD packages and board materials are not able to

withstand long duration bakes at 125C. Examples of this

are some FR-4 materials, which cannot withstand a 24 hr

bake at 125C. Batteries and electrolytic capacitors are

also temperature sensitive. With component and board

temperature restrictions in mind, choose a bake tem-

perature from Table 4-1 in J-STD 033; then determine the

appropriate bake duration based on the component to be

removed. For additional considerations see IPC-7711 and

IPC-7721.

Derating due to Factory Environmental Conditions

Factory foor life exposures for SMD packages removed

from the dry bags will be a function of the ambient envi-

ronmental conditions. A safe, yet conservative, handling

approach is to expose the SMD packages only up to the

maximum time limits for each moisture sensitivity level

as shown in next table. This approach, however, does not

work if the factory humidity or temperature is greater

than the testing conditions of 30C/60% RH. A solution

for addressing this problem is to derate the exposure

times based on the knowledge of moisture difusion in

the component package materials ref. JESD22-A120).

Recommended equivalent total foor life exposures can

be estimated for a range of humidities and temperatures

based on the nominal plastic thickness for each device.

Table on next page lists equivalent derated foor lives for

humidities ranging from 20-90% RH for three tempera-

ture, 20C, 25C, and 30C.

Table on next page is applicable to SMDs molded

with novolac, biphenyl or multifunctional epoxy mold

compounds. The following assumptions were used in cal-

culating this table:

1. Activation Energy for difusion = 0.35eV (smallest

known value).

2. For 60% RH, use Difusivity = 0.121exp ( -0.35eV/kT)

mm2/s (this used smallest known Difusivity @ 30C).

3. For >60% RH, use Difusivity = 1.320exp ( -0.35eV/kT)

mm2/s (this used largest known Difusivity @ 30C).

For product information and a complete list of distributors, please go to our web site: www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries.

Data subject to change. Copyright 2005-2010 Avago Technologies. All rights reserved.

AV02-2476EN - December 17, 2010

Recommended Equivalent Total Floor Life (days) @ 20C, 25C & 30C, 35C

For ICs with Novolac, Biphenyl and Multifunctional Epoxies (Refow at same temperature at which the component was

classifed) Maximum Percent Relative Humidity

Maximum Percent Relative Humidity

Package Type and

Body Thickness

Moisture

Sensitivity Level 5% 10% 20% 30% 40% 50% 60% 70% 80% 90%

Body Thickness 3.1 mm

Including

PQFPs >84 pin,

PLCCs (square)

All MQFPs

or

All BGAs 1 mm

Level 2a

94

124

167

231

44

60

78

103

32

41

53

69

26

33

42

57

16

28

36

47

7

10

14

19

5

7

10

13

4

6

8

10

35C

30C

25C

20C

Level 3

8

10

13

17

7

9

11

14

6

8

10

13

6

7

9

12

6

7

9

12

4

5

7

10

3

4

6

8

3

4

5

7

35C

30C

25C

20C

Level 4

3

5

6

8

3

4

5

7

3

4

5

7

2

4

5

7

2

3

5

7

2

3

4

6

2

3

3

5

1

2

3

4

1

2

3

4

35C

30C

25C

20C

Level 5

2

4

5

7

2

3

5

7

2

3

4

6

2

2

4

5

1

2

3

5

1

2

3

4

1

2

2

3

1

1

2

3

1

1

2

3

35C

30C

25C

20C

Level 5a

1

2

3

5

1

1

2

4

1

1

2

3

1

1

2

3

1

1

2

3

1

1

2

2

1

1

1

2

1

1

1

2

1

1

1

2

35C

30C

25C

20C

Body 2.1 mm

Thickness

<3.1 mm including

PLCCs (rectangular)

18-32 pin

SOICs (wide body)

SOICs 20 pins,

PQFPs 80 pins

Level 2a

58

86

148

30

39

51

69

22

28

37

49

3

4

6

8

2

3

4

5

1

2

3

4

35C

30C

25C

20C

Level 3

12

19

25

32

9

12

15

19

7

9

12

15

6

8

10

13

5

7

9

12

2

3

5

7

2

2

3

5

1

2

3

4

35C

30C

25C

20C

Level 4

5

7

9

11

4

5

7

9

3

4

5

7

3

4

5

6

2

3

4

6

2

3

4

5

1

2

3

4

1

2

2

3

1

1

2

3

35C

30C

25C

20C

Level 5

3

4

5

6

2

3

4

5

2

3

3

5

2

2

3

4

2

2

3

4

1

2

3

4

1

1

2

3

1

1

1

3

1

1

1

2

35C

30C

25C

20C

Level 5a

1

2

2

3

1

1

2

2

1

1

2

2

1

1

2

2

1

1

2

2

1

1

2

2

1

1

1

2

0.5

0.5

1

2

0.5

0.5

1

1

35C

30C

25C

20C

Body Thickness <2.1 mm

including

SOICs <18 pin

All TQFPs, TSOPs

or

All BGAs <1 mm body

thickness

Level 2a

17

28

1

1

2

2

0.5

1

1

2

0.5

1

1

1

35C

30C

25C

20C

Level 3

8

11

14

20

5

7

10

13

1

1

2

2

0.5

1

1

2

0.5

1

1

1

35C

30C

25C

20C

Level 4

7

9

12

17

4

5

7

9

3

4

5

7

2

3

4

6

1

1

2

2

0.5

1

1

2

0.5

1

1

1

35C

30C

25C

20C

Level 5

7

13

18

26

3

5

6

8

2

3

4

6

2

2

3

5

1

2

3

4

1

1

2

2

0.5

1

1

2

0.5

1

1

1

35C

30C

25C

20C

Level 5a

7

10

13

18

2

3

5

6

1

2

3

4

1

1

2

3

1

1

2

2

1

1

2

2

1

1

1

2

0.5

1

1

2

0.5

0.5

1

1

35C

30C

25C

20C

Вам также может понравиться

- FX/MX128: Audio Band ScramblerДокумент11 страницFX/MX128: Audio Band Scrambleryc1teОценок пока нет

- Paradise Datacom Mini-Redundant SSPA 209495 RevAДокумент8 страницParadise Datacom Mini-Redundant SSPA 209495 RevAarzeszutОценок пока нет

- DatasheetДокумент8 страницDatasheetgijiskariaОценок пока нет

- ML50 Spec TechДокумент29 страницML50 Spec TechmfresiaОценок пока нет

- 5051 AppДокумент37 страниц5051 AppawemetalОценок пока нет

- Tja1040t PDFДокумент18 страницTja1040t PDF81968Оценок пока нет

- Advantech Wireless AMT 30 Modem Data SheetДокумент2 страницыAdvantech Wireless AMT 30 Modem Data SheetarzeszutОценок пока нет

- Description Power Range: Analog Servo DriveДокумент7 страницDescription Power Range: Analog Servo DriveElectromateОценок пока нет

- Tda 7294Документ17 страницTda 7294Abubakar SidikОценок пока нет

- Description Power Range: Analog Servo DriveДокумент7 страницDescription Power Range: Analog Servo DriveElectromateОценок пока нет

- Lmh6882 DC To 2.4Ghz, High Linearity, Dual, Programmable Differential AmplifierДокумент32 страницыLmh6882 DC To 2.4Ghz, High Linearity, Dual, Programmable Differential AmplifierJoseph BernardОценок пока нет

- AFBR 776BxxxZ and AFBR 786BxxxZ Twelve Channel Transmitter and Receiver Pluggable Parallel Fiber Optics ModulesДокумент48 страницAFBR 776BxxxZ and AFBR 786BxxxZ Twelve Channel Transmitter and Receiver Pluggable Parallel Fiber Optics ModulesTene Emil GabrielОценок пока нет

- MR-J2S-S099 - Specifications and Instruction Manual BCN-B11127-478 (01.02) PDFДокумент84 страницыMR-J2S-S099 - Specifications and Instruction Manual BCN-B11127-478 (01.02) PDFDoDuyBacОценок пока нет

- Low-If 2.4-Ghz Ism Transceiver Atr2406: FeaturesДокумент25 страницLow-If 2.4-Ghz Ism Transceiver Atr2406: FeaturesDeepa DevarajОценок пока нет

- ATV71HC20N4 DocumentДокумент8 страницATV71HC20N4 DocumentToth VasileОценок пока нет

- 40G QSFP+ PSM IR4 SOQP-3140-01 From SinovoДокумент16 страниц40G QSFP+ PSM IR4 SOQP-3140-01 From SinovomelissaОценок пока нет

- Pulse Autonom 3052 PDFДокумент8 страницPulse Autonom 3052 PDFRobert RodriguezОценок пока нет

- Features Description: D D D D D D D D D D D DДокумент16 страницFeatures Description: D D D D D D D D D D D D1eugen1Оценок пока нет

- RFR D H - Am-H RK: Eceiver Ecoder Ybrid IДокумент4 страницыRFR D H - Am-H RK: Eceiver Ecoder Ybrid IΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣОценок пока нет

- A4988 DatasheetДокумент20 страницA4988 DatasheetJose OnoОценок пока нет

- Description Power Range: Analog Servo DriveДокумент7 страницDescription Power Range: Analog Servo DriveElectromateОценок пока нет

- HT7A6003 EMI-Improved Green Mode PWM Controller With Integrated ProtectionsДокумент10 страницHT7A6003 EMI-Improved Green Mode PWM Controller With Integrated ProtectionsEnéas BaroneОценок пока нет

- Integrated Circuits Data Sheet for SAA1057 Radio Tuning PLL Frequency Synthesizer ICДокумент13 страницIntegrated Circuits Data Sheet for SAA1057 Radio Tuning PLL Frequency Synthesizer ICulil amriОценок пока нет

- Datasheet ATV61EXS5C63N4Документ8 страницDatasheet ATV61EXS5C63N4flake03Оценок пока нет

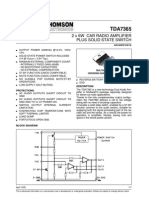

- 2 X 6W Car Radio Amplifier Plus Solid State Switch: Protections DescriptionДокумент8 страниц2 X 6W Car Radio Amplifier Plus Solid State Switch: Protections DescriptionMiloud ChouguiОценок пока нет

- An 11.1Gbps Analog PRML Receiver For EDC of Up To 400km-Reach WDM Fiber-Optic LinksДокумент4 страницыAn 11.1Gbps Analog PRML Receiver For EDC of Up To 400km-Reach WDM Fiber-Optic LinksGbarbarОценок пока нет

- Max 2981Документ13 страницMax 2981Jamila RobinsonОценок пока нет

- LMH6550 Differential, High Speed Op Amp: R R V V AДокумент25 страницLMH6550 Differential, High Speed Op Amp: R R V V AJavier Felipe AlvaradoОценок пока нет

- PTP 58400 Lite Integrated - Link Complete: Specifications Sheet Motorola CanopyДокумент1 страницаPTP 58400 Lite Integrated - Link Complete: Specifications Sheet Motorola Canopysgonzalez_betinОценок пока нет

- Ads 7870Документ43 страницыAds 7870Moorthy VenkatachalamОценок пока нет

- MIC-2 Multi-Instrument Data Sheet: Measurements DisplayДокумент6 страницMIC-2 Multi-Instrument Data Sheet: Measurements DisplayvladraqulОценок пока нет

- Elber Datasheets Mobile Systems - SPM - (Mt-Mr-Line) (En)Документ2 страницыElber Datasheets Mobile Systems - SPM - (Mt-Mr-Line) (En)Techne PhobosОценок пока нет

- 11.3Gb/s Full-Band Tunable Super-X2 Transceiver: TL8000 SeriesДокумент10 страниц11.3Gb/s Full-Band Tunable Super-X2 Transceiver: TL8000 SeriesmofiwОценок пока нет

- HPMX 3002Документ9 страницHPMX 3002sri kalyanОценок пока нет

- Datasheet Flatpack2 48 2000Документ2 страницыDatasheet Flatpack2 48 2000Novocain82Оценок пока нет

- Data - Sheet - c78-727133 Nodo Con Retorno Digital Tecn GanДокумент8 страницData - Sheet - c78-727133 Nodo Con Retorno Digital Tecn GanMary V. LopezОценок пока нет

- Data Sheet - Preliminary: Afbr-79Eiz, Afbr-79EidzДокумент19 страницData Sheet - Preliminary: Afbr-79Eiz, Afbr-79EidzlksmrОценок пока нет

- A4989 DatasheetДокумент17 страницA4989 DatasheetGopalkrishnan Nadar100% (1)

- Variable speed drive data sheetДокумент13 страницVariable speed drive data sheetMutu DanielОценок пока нет

- SR510 MДокумент73 страницыSR510 McampuspointОценок пока нет

- DK PC3000 ModulesДокумент11 страницDK PC3000 ModulessickosatОценок пока нет

- Description Power Range: Analog Servo DriveДокумент7 страницDescription Power Range: Analog Servo DriveElectromateОценок пока нет

- 412 Arduino Shield Uno Gsm-Gprs-Sms-ManualДокумент28 страниц412 Arduino Shield Uno Gsm-Gprs-Sms-ManualnazekОценок пока нет

- Optimux-1553: Fiber Multiplexers For 3 E3/T3 Over STM-1/OC-3Документ8 страницOptimux-1553: Fiber Multiplexers For 3 E3/T3 Over STM-1/OC-3Quan HoangОценок пока нет

- Satellite ModemДокумент2 страницыSatellite ModemalifshahОценок пока нет

- Description Power Range: Analog Servo DriveДокумент7 страницDescription Power Range: Analog Servo DriveElectromateОценок пока нет

- AC 800M Controller Data SheetДокумент4 страницыAC 800M Controller Data Sheetrmsr_7576100% (1)

- 250T Frequency TransmitterДокумент13 страниц250T Frequency Transmitterreality88Оценок пока нет

- Sunair RT-9000B DatasheetДокумент2 страницыSunair RT-9000B Datasheetfalcom2Оценок пока нет

- Programmable Digital QPSK/16-QAM Modulator: Internal Reference Clock MultiplierДокумент32 страницыProgrammable Digital QPSK/16-QAM Modulator: Internal Reference Clock MultiplierCristian Villalobos CampañaОценок пока нет

- RF2125 High Power Linear Amplifier IC DatasheetДокумент6 страницRF2125 High Power Linear Amplifier IC Datasheetmichaelliu123456Оценок пока нет

- Tps 61183Документ25 страницTps 61183GilvaneSilvaОценок пока нет

- CLC5526 Digital Variable Gain Amplifier (DVGA) : General DescriptionДокумент10 страницCLC5526 Digital Variable Gain Amplifier (DVGA) : General DescriptionVănThịnhОценок пока нет

- Ultra Small Linear TransponderДокумент8 страницUltra Small Linear Transponderpe1rahОценок пока нет

- Spf5189z Data SheetДокумент11 страницSpf5189z Data SheetAparna BhardwajОценок пока нет

- RTXM192-xxx DDMДокумент16 страницRTXM192-xxx DDMmatsmats1Оценок пока нет

- CDP 1802 Data Sheet 2Документ7 страницCDP 1802 Data Sheet 2DaveОценок пока нет

- Central Control Unit With Layer-One Converter For Remote Electrical Tilt (RET) and Tower Mounted Amplifi Er (TMA) ControlДокумент2 страницыCentral Control Unit With Layer-One Converter For Remote Electrical Tilt (RET) and Tower Mounted Amplifi Er (TMA) Controldoug_nguyen7864Оценок пока нет

- ACS714Документ15 страницACS714connect2nsОценок пока нет

- Ericsson AMOS CommandДокумент10 страницEricsson AMOS CommandNayan Abdullah50% (2)

- Load, configure, monitor and troubleshoot an eNodeBДокумент3 страницыLoad, configure, monitor and troubleshoot an eNodeBkhushAbcdОценок пока нет

- Etsi Supplement - Services - CodesДокумент21 страницаEtsi Supplement - Services - CodespavlodeОценок пока нет

- Zyxel LTE3311-Q222Документ4 страницыZyxel LTE3311-Q222pavlodeОценок пока нет

- Ericsson AMOS CommandДокумент10 страницEricsson AMOS CommandNayan Abdullah50% (2)

- Basic Mo CommandsДокумент4 страницыBasic Mo CommandspavlodeОценок пока нет

- 3G Moshell CMDДокумент24 страницы3G Moshell CMDDikal Pebrianda100% (11)

- Ralink 3070 USB WiFi AP ModeДокумент3 страницыRalink 3070 USB WiFi AP ModepavlodeОценок пока нет

- Poynting PANL A0038 AntennaДокумент1 страницаPoynting PANL A0038 AntennapavlodeОценок пока нет

- Lte Broadcast Infographic PDFДокумент1 страницаLte Broadcast Infographic PDFpavlodeОценок пока нет

- Cellular Radio Network ManagementДокумент91 страницаCellular Radio Network Managementle_linh_53Оценок пока нет

- Huawei B593u 12 Lte Cpe DatasheetДокумент26 страницHuawei B593u 12 Lte Cpe DatasheetpavlodeОценок пока нет

- Apxv9r13b C A20 PDFДокумент2 страницыApxv9r13b C A20 PDFpavlodeОценок пока нет

- Supplementary DownlinkДокумент14 страницSupplementary DownlinkanasОценок пока нет

- POYNTING-ADPT-026 Modem To AntennaДокумент2 страницыPOYNTING-ADPT-026 Modem To AntennapavlodeОценок пока нет

- Danish Norvegian Study 2012-ReportДокумент3 страницыDanish Norvegian Study 2012-ReportpavlodeОценок пока нет

- GSM Timer DocumentationДокумент76 страницGSM Timer DocumentationHassan Awan100% (1)

- Ericsson RNC RAB CombinationsДокумент2 страницыEricsson RNC RAB Combinationspavlode100% (1)

- Bssmap 29010-480Документ126 страницBssmap 29010-480pavlodeОценок пока нет

- RANAP SignallingДокумент59 страницRANAP SignallingpavlodeОценок пока нет

- Snapdragon 820 Processor Product BriefДокумент2 страницыSnapdragon 820 Processor Product BriefSaran SaetangОценок пока нет

- GSM Paging Issue AnalyseДокумент25 страницGSM Paging Issue AnalysesrilasithaОценок пока нет

- GSM - UMTS Cell Reselection & HandoverДокумент11 страницGSM - UMTS Cell Reselection & Handovercool_virginboyОценок пока нет

- Nokia 5G Masterplan White PaperДокумент18 страницNokia 5G Masterplan White PaperFausy A. Frías100% (2)

- Generated ReasonvcДокумент4 страницыGenerated ReasonvcRicky SuradiradjaОценок пока нет

- 56243013-3GUMTS Transport Guide PDFДокумент8 страниц56243013-3GUMTS Transport Guide PDFpavlodeОценок пока нет

- Admission Control and Load Control in Umts NetworkДокумент4 страницыAdmission Control and Load Control in Umts Networkantony_claret100% (2)

- Sierrawireless AceManagerДокумент81 страницаSierrawireless AceManagerpavlodeОценок пока нет

- GARP Description PDFДокумент25 страницGARP Description PDFpavlodeОценок пока нет

- GSM Quick RefДокумент2 страницыGSM Quick Reframesh1munnarОценок пока нет