Академический Документы

Профессиональный Документы

Культура Документы

Power Amplifiers Part 1 Class A: We Have Studied The Design of Small-Signal Amplifiers

Загружено:

malamigsajpanОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Power Amplifiers Part 1 Class A: We Have Studied The Design of Small-Signal Amplifiers

Загружено:

malamigsajpanАвторское право:

Доступные форматы

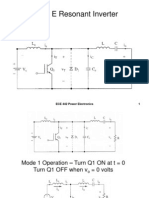

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 1 of 18 Prof. S. Long

Power Amplifiers; Part 1 Class A

Device Limitations

Large signal output match

Define efficiency, power-added efficiency

Class A operating conditions

Thermal resistance

We have studied the design of small-signal amplifiers

The designs were based on small-signal S-parameters.

The output was often conjugately matched to increase gain.

conjugate match: SS AC Load Line

Re Z

L

{ }= Re Z

OUT

{ }

I

DQ

V

DQ

I

DQ

V

DQ

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 2 of 18 Prof. S. Long

The small signal conjugate match leads to limitations on

voltage and current swing. Not important for SS amps, but

crucial for power amps.

V <<V

DQ

I << I

DQ

Power amps require a large-signal design methodology:

Vand I are significant compared with V

DQ

and I

DQ

.

Power Amp Objective: Get the largest Vand I without:

1. Clipping large saturation of gain;

- distortion generated

2. Destroying the device.

avoid breakdown

I

MAX

must be within device specs

P

DISS

must not overheat the device

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 3 of 18 Prof. S. Long

Device limitations and clipping.

Every device has maximum voltage and current limits.

Breakdown voltage:

Electric field large enough to generate

electron-hole pair qV>E

gap

of

semiconductor.

Electrons injected into channel from

source or into collector from emitter

are accelerated in high field.

Collisions transfer energy to Si atoms. Electron is

released, accelerates

creates hole.

Electron-hole pairs are then accelerated further

generating more electrons, holes.

This leads to rapid increase in current for voltages

beyond breakdown

AVALANCHE BREAKDOWN!!!

S G D

Electric field

electrons

holes

S G D

Electric field

electrons

holes

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 4 of 18 Prof. S. Long

Maximum Current

GaAs FET:

I

DSS

for FET = I

D

@V

GS

= 0

I

D

qnv

sat

n V

GS

V

T

( )

m

also must avoid forward gate conduction on MESFET

or PHEMT

Si MOSFET:

Imax specified by foundry or manufacturer

Also must avoid gate oxide breakdown

BJ T: I

MAX

is limited by collector electric field profile

when mobile charge fixed charge,

=

q N

D

n ( )x

electric field 0

transit delay

f

T

We will discuss thermal limitations later. Heat generation

will limit the operation of all device types

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 5 of 18 Prof. S. Long

Conjugate Match Revisited.

We have learned that max. power transfer occurs when

R

L

= R

dS

.

true for small signal condition

-no device limitations.

But what happens when we have limitations on voltage and

current?

Suppose V

max

=10V, I

max

=1A, R

dS

=100

1. Conjugate Match. R

L

||R

dS

= 50 = R

L

V

OUT

= I

max

R

L

= 50V !

clearly, I

max

cant be reached since V

max

=10V

P

OUT

=

V

max

/ 2 ( )

2

2R

L

=

25

100

=

1

4

W

jB

- jB R

ds

R

L

I

L

V

OUT

+

-

I

d

jB

- jB R

ds

R

L

I

L

V

OUT

+

-

I

d

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 6 of 18 Prof. S. Long

2. Load Line Match. R

L

=

V

max

I

max

=10

P

OUT

=

25

20

=1.25W

This uses the maximum capability of the device

more realistically, improvement of 2-3 dB is typical

Here you can see the large signal load line with slope 1/R

L

I

DQ

V

DQ V

BR

I

MAX

V

Dsat

I

DQ

V

DQ V

BR

I

MAX

V

Dsat

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 7 of 18 Prof. S. Long

We have now shown that different criteria are used for

output matching a power amp than a small signal amp.

You may have noticed that the large signal load line

doesnt extend to V

DS

=0. To avoid excessive distortion,

we must also take into account the knee voltage (V

Dsat

or

V

CEsat

). Clipping will occur if the drain voltage swing

extends into the ohmic region of the device characteristic.

Thus, our definition of the large signal load line resistance

must take this into account:

BR knee

L

max

V V

R

I

= for maximum voltage swing

Some additional PA concepts

Efficiency

OUT

DC

P

x 100%

P

=

Power Dissipation

D DC OUT

P P P =

Must be removed as heat.

P

D

can also limit the maximum P

OUT

T

max

=150

o

C

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 8 of 18 Prof. S. Long

Power-Added-Efficiency

OUT IN

DC

P P

PAE

P

=

Gain should be at least 10dB to avoid significant

reduction in PAE.

Efficiency is important because

1) PAs are used for power

2) Wasted power must be removed as heat

3) Wasted power consumes batteries faster

Suppose Pout =10 kW

(FM broadcast transmitter)

(%)

P

D

(kW) P

DC

(kW)

90 1.1 11.1

50 10 20

25 30 40

10 90 100

P

IN

P

DC

P

OUT

P

IN

P

DC

P

OUT

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 9 of 18 Prof. S. Long

First PA: Class A.

Most similar to small-signal amp.

V

DQ

and I

DQ

set so that amp is always on.

conduction angle =

"on" time

T

2 = 2

Case 1 : resistive load. bad idea for PA, but familiar.

(we will refer later to this V

DC

as V

DC1

)

Neglecting V

knee

, we find

DC BR

L

max CQ

V V

R

I 2I

= =

V

DC

R

L

I

CQ

V

CQ

=V

DC

/2

V

DC

= V

BR

I

MAX

= 2 I

CQ

I

CQ

V

CQ

=V

DC

/2

V

DC

= V

BR

I

MAX

= 2 I

CQ

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 10 of 18 Prof. S. Long

I

C

( ) = I

CQ

+ I

m

sin ( =t)

Maximum value of

m CQ

I I = (just begins to clip)

We can see that the average DC component is ICQ and the fundamental

component of current is Im, OR:

We can use Fourier integrals to determine P

DC

and P

OUT

. The DC term (a

0

)

can be used to calculate power dissipation:

( )

DC

DC c

2

V

P i d

2

0

=

DC

CQ m DC CQ

2

V

I I sin d V I

2

0

= + =

constant DC power, constant input current. You can use Fourier integrals to

also find coefficients for fundamental and harmonics. T =2

( )

T

2

T / 2

0

1

a f x dx

T

=

( ) ( )

T

2

n

T

2

2

a f x sin nx dx

T

=

( ) ( )

T

2

T

2

n

2

b f x cos nx dx

T

=

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 11 of 18 Prof. S. Long

Power at fundamental frequency : n=1

( )

2

1 m OUT m m

1

a I i I sin d I

= = =

2

sin d

P

OUT

=

1

2

Re V

m

I

m

*

{ }

=

1

2

V

m

I

m

V

m

=

V

DC

2

; I

m

=

V

m

R

L

Thus:

1 max 1 max

I 1

2 2 2 8

DC DC

V I V

Pout = =

and, P

OUT

=

I

m

2

R

L

2

=

I

CQ

2

R

L

2

=

V

DC

2

8R

L

since

max CQ

I 2I = ,

BR DC

V V = ,

BR

L

max

V

R

I

=

In terms of device limitations, the maximum output power is

P

OUT

=

1

2

I

max

2

4

V

BR

I

max

=

V

BR

I

max

8

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 12 of 18 Prof. S. Long

what about harmonics? n >1?

n d =0

-

m n m

1

I a I sin sin

=

with no nonlinearity in ( ) I

c

, no harmonic currents.

Efficiency:

P

DC

= V

DC

I

CQ

=

V

DC

2

2R

L

DC

CQ

L

V

I

2R

=

so =

P

OUT

P

DC

=

1

4

25% ( ) max!

If we AC couple the load resistor:

We have current divider.

Efficiency can be much worse.

so, bad idea for any power application

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 13 of 18 Prof. S. Long

For RF applications we can do much better.

Case 2: inductive load.

V

DC

=V

DC2

=V

DC1

/2

now,

DC BR

L

max CQ

V V

R

I I

= = (no change -assume same

device limitations)

2

2 2 max max

2 4 8

DC DC BR

OUT

L

V V I V I

P

R

= = = same as case 1

but:

2

2

2 2 1

1

2

DC

DC DC CQ DC

L

V

P V I P

R

= = =

=

1

2

50% ( )

I

CQ

V

CQ

=V

DC

2V

DC

= V

BR

I

CQ

V

CQ

=V

DC

2V

DC

= V

BR

R

L

V

DC

R

L

V

DC

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 14 of 18 Prof. S. Long

we have P

OUT

case 2 ( ) = P

OUT

case 1 ( )

but P

DC

case 2 ( ) =

1

2

P

DC

case 1 ( )

because: ( ) 2

DC

V case

( )

1

DC

1

V case

2

=

Thus, the inductive feed allows the amplifier to produce the

same output power with half the supply voltage. This also

applies to tuned amplifiers.

So: 50% of

DC

P can be converted into

useful output power if we swing rail

to rail.

Alternatively, we can get 2 times more P

OUT

for the

same V

DC

if the device has sufficient breakdown

voltage. (twice the voltage; twice the R

L

)

2

2

max

2 2 max 1 max

2

2 4 2

DC

m DC L

DC DC DC

L

V

V V R

I

V V I V I

Pout

R

= =

= = =

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 15 of 18 Prof. S. Long

But, what about a more typical situation

where we have a large range of signal powers

to be amplified?

How much power gets dissipated in the device?

D DC OUT

P P P = (heat in transistor)

We have doubled the efficiency (now 50%), but still have

maximum power dissipated in device at zero input.

undesirable for power amp where high

powers may be required.

ok for driver stage low power; highly linear.

Pout

P

D

P

DC

= V

DC

I

CQ

I

m

I

CQ

= V

DC

/R

L

Power

Pout = V

DC

2

/2R

L

(constant)

Pout

P

D

P

DC

= V

DC

I

CQ

I

m

I

CQ

= V

DC

/R

L

Power

Pout = V

DC

2

/2R

L

(constant)

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 16 of 18 Prof. S. Long

Thermal Limitations

T

J

150C why?

reliability

failure mechanisms are

strongly temperature

dependent

MTTF e

Ea/KT

Ea =activation energy

Thermal model.

T

J

<150C

T

C

T

HS

T

Ambient

R

TH

J C

R

TH

C HS

R

TH

HS A

heat sink

package

air T = 25C

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 17 of 18 Prof. S. Long

Thermal Resistance relates T to power dissipation

(like ohms law for heat)

,

, , ,

( )

J TH J C D C

TH J C TH C HS TH HS A D A

T R P T

R R R P T

= +

= + + +

TH

R has units of C /watt

R

TH

JC

R

TH

CHS

R

TH

HSA

T

J

T

C

T

HS

T

A

ECE 145A/218A Power Amplifier Design Lectures

Power Amplifier Design 1

5/24/07 18 of 18 Prof. S. Long

Class A Power Amplifier Summary

1. Device limitations (V

BR

and I

MAX

and T

MAX

) constrain the

design for a PA.

not

*

OUT

!

Large signal load line match

2. T

MAX

=150C for reliable operation

3. Waste power, P

D

= P

DC

P

OUT

is converted to heat. Must

be removed

4. Efficiency,

P

OUT

P

DC

, or PAE,

P

OUT

P

IN

P

DC

are critical for PAs.

For Class A with same output power, same R

L

:

Resistive DC feed (1) Inductive feed (2)

V

DC

V

DC1

V

DC2

=V

DC1

/2

25% max 50% max

P

OUT

2

1

8

DC

L

V

R

2 2

2 1

2 8

DC DC

L L

V V

R R

=

V

DC

max

up to V

BR

up to V

BR

2

R

L

=

1

2

DC BR

MAX CQ

V V

I I

=

2 1

2

DC DC BR

MAX CQ CQ

V V V

I I I

= =

BR knee

opt

MAX

V V

R

I

Вам также может понравиться

- Multistage AmplifierДокумент22 страницыMultistage AmplifierVijay AnandhОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Basic Op-Amp Circuits: EE 126 - Industrial Electronics Handout: Operational Amplifiers Operational Amplifiers (Op-Amps)Документ6 страницBasic Op-Amp Circuits: EE 126 - Industrial Electronics Handout: Operational Amplifiers Operational Amplifiers (Op-Amps)kyope17Оценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- Energy ConversionДокумент45 страницEnergy ConversionJohn Pura50% (2)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsОт EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsОценок пока нет

- Electronics Circuit Design LabДокумент34 страницыElectronics Circuit Design Labsrvdhar100% (1)

- Push Pull Ampilfier - c9Документ4 страницыPush Pull Ampilfier - c9quynh04cdt1Оценок пока нет

- STEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10От EverandSTEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10Оценок пока нет

- AEC LabManualДокумент30 страницAEC LabManualPrateek PaliwalОценок пока нет

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1От EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Рейтинг: 4.5 из 5 звезд4.5/5 (3)

- Project Report of Public Address SystemДокумент14 страницProject Report of Public Address SystemZohaib Jahan50% (2)

- Two StageДокумент6 страницTwo StageSiphosethuSidloyiОценок пока нет

- Lecture21 Multistage AmplifiersДокумент10 страницLecture21 Multistage AmplifierscitraumariОценок пока нет

- Project 2 EE087732Документ13 страницProject 2 EE087732Mei QiiОценок пока нет

- DC-DC BoostДокумент21 страницаDC-DC BoostvinaykumaarОценок пока нет

- ET1006 1112S2Exam Formulae SheetsДокумент4 страницыET1006 1112S2Exam Formulae SheetstestniaОценок пока нет

- Lab Report: ANA Log Ic Design LabДокумент14 страницLab Report: ANA Log Ic Design LabNitishОценок пока нет

- Step-ByStep Flyback SMPS DesignДокумент6 страницStep-ByStep Flyback SMPS DesignPhạm Văn TưởngОценок пока нет

- Analog & Digital Electronics: Course No: PH-218 Lec-19: Power Amplifiers and Output StagesДокумент18 страницAnalog & Digital Electronics: Course No: PH-218 Lec-19: Power Amplifiers and Output StagesSagarThapaОценок пока нет

- Aec U 4Документ26 страницAec U 4kelamkiranmai265Оценок пока нет

- LIC Lab ManualДокумент78 страницLIC Lab ManualPrinthya GudiyaОценок пока нет

- Common Emitter Amplifier: S.No Name of The Component/ Equipment Specifications QtyДокумент0 страницCommon Emitter Amplifier: S.No Name of The Component/ Equipment Specifications Qtyagama1188Оценок пока нет

- Slua653b 5W USB Flyback Design ReviewДокумент21 страницаSlua653b 5W USB Flyback Design ReviewPhạm Văn TưởngОценок пока нет

- RectifierДокумент37 страницRectifierMahendra Mandalapu MОценок пока нет

- Objectives:: Electronics I Laboratory - EXPERIMENT 10 Common Emitter AmplifierДокумент6 страницObjectives:: Electronics I Laboratory - EXPERIMENT 10 Common Emitter AmplifierRabindraMaharanaОценок пока нет

- Einstein: College of EngineeringДокумент80 страницEinstein: College of EngineeringPoonkothaiMyilОценок пока нет

- D Single Phase Fully: Esign of Controlled Converter Using Cosine Wave Crossing Control With Various ProtectionsДокумент6 страницD Single Phase Fully: Esign of Controlled Converter Using Cosine Wave Crossing Control With Various Protectionsঅর্ণব কোলেОценок пока нет

- ADIC ExperimentsДокумент41 страницаADIC ExperimentsTushar PatilОценок пока нет

- 1448249900UG - EE 2209 - Power Amplifier - 20140201 (Compatibility Mode)Документ31 страница1448249900UG - EE 2209 - Power Amplifier - 20140201 (Compatibility Mode)Tanvir Ahmed MunnaОценок пока нет

- 13 - FET and Power AmpДокумент35 страниц13 - FET and Power AmpTuanHungОценок пока нет

- Basic Electronics by BakshiДокумент226 страницBasic Electronics by Bakshiniju86% (7)

- Lab Report Solayman Ewu - CompressДокумент12 страницLab Report Solayman Ewu - CompressVic100% (1)

- Dar Es Salaam Institute of Technology: Electronics and Telecommunication EngineeringДокумент13 страницDar Es Salaam Institute of Technology: Electronics and Telecommunication EngineeringSokoine Hamad DenisОценок пока нет

- Class E Resonant InverterДокумент28 страницClass E Resonant InverterSenthil Kumar0% (1)

- DC DC BoostДокумент21 страницаDC DC BoosttrshaaaОценок пока нет

- Integrator DiffentiatorДокумент7 страницIntegrator Diffentiatorআব্দুল্লাহ আল ইমরানОценок пока нет

- Lecture 3 - Transistor AmplifiersДокумент34 страницыLecture 3 - Transistor AmplifiersMeesixОценок пока нет

- 665 PA - NotesДокумент31 страница665 PA - Notesthap_dinhОценок пока нет

- AEC Manual 2018-2019Документ99 страницAEC Manual 2018-2019Raza SikandarОценок пока нет

- LIC Lab ManualДокумент79 страницLIC Lab ManualSakthikumar Balasundaram67% (3)

- Cascode AmplifierДокумент6 страницCascode AmplifierRajesh NatarajanОценок пока нет

- Ecgr3156 Experiment 1 BJT Differential Pair With BJT Current MirrorДокумент8 страницEcgr3156 Experiment 1 BJT Differential Pair With BJT Current MirrorSargamОценок пока нет

- Unit 1 AmplifiersДокумент46 страницUnit 1 Amplifiersvimalaspl7831Оценок пока нет

- EEE 4308L Electronics I Laboratory Laboratory #1 Operational Amplifier-Based IntegratorsДокумент19 страницEEE 4308L Electronics I Laboratory Laboratory #1 Operational Amplifier-Based IntegratorsnoneОценок пока нет

- RC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentДокумент8 страницRC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentMani BharathiОценок пока нет

- Ec8351 Electronic Circuits 1 Unit 2 Solved WMRДокумент11 страницEc8351 Electronic Circuits 1 Unit 2 Solved WMRSaravanan MurugaiyanОценок пока нет

- S T K 4 2 3 1 I I 2-Channel Loowmin Af Power Amp (Dual Supplies)Документ8 страницS T K 4 2 3 1 I I 2-Channel Loowmin Af Power Amp (Dual Supplies)Arthur JonesОценок пока нет

- EEE 54 DP1 Documentation - Mendoza - SorianoДокумент2 страницыEEE 54 DP1 Documentation - Mendoza - SorianoDarl John MendozaОценок пока нет

- Exercise 3 - Summer Semester 2019Документ8 страницExercise 3 - Summer Semester 2019Mario PajaОценок пока нет

- Electronic Circuits LatestДокумент69 страницElectronic Circuits LatestSai SadiqОценок пока нет

- Universal Block DiagramДокумент6 страницUniversal Block Diagramapneetsandhu1234Оценок пока нет

- Audio Amplifier (English)Документ11 страницAudio Amplifier (English)Zhamir ZhakwanОценок пока нет

- Analog Communications Lab ManualДокумент61 страницаAnalog Communications Lab ManualSriLakshmi RaheemОценок пока нет

- L08 Power Amplifier (Class A)Документ24 страницыL08 Power Amplifier (Class A)mkrasanОценок пока нет

- aeclAB 1Документ41 страницаaeclAB 1ayjagadishОценок пока нет

- Switch Mode Power Supplies: SPICE Simulations and Practical DesignsДокумент9 страницSwitch Mode Power Supplies: SPICE Simulations and Practical Designscms124dОценок пока нет

- Applied Electronics Lab 1Документ9 страницApplied Electronics Lab 1Rickel RoweОценок пока нет

- VoIP Testing With TEMS InvestigationДокумент20 страницVoIP Testing With TEMS Investigationquantum3510Оценок пока нет

- U2 - Week1 PDFДокумент7 страницU2 - Week1 PDFJUANITO MARINOОценок пока нет

- Auto Report LogДокумент3 страницыAuto Report LogDaniel LermaОценок пока нет

- Pradhan Mantri Gramin Digital Saksharta Abhiyan (PMGDISHA) Digital Literacy Programme For Rural CitizensДокумент2 страницыPradhan Mantri Gramin Digital Saksharta Abhiyan (PMGDISHA) Digital Literacy Programme For Rural Citizenssairam namakkalОценок пока нет

- Certification DSWD Educational AssistanceДокумент3 страницыCertification DSWD Educational AssistancePatoc Stand Alone Senior High School (Region VIII - Leyte)Оценок пока нет

- Ucbackup Faq - Commvault: GeneralДокумент8 страницUcbackup Faq - Commvault: GeneralhherОценок пока нет

- TokyoДокумент6 страницTokyoMarcio BonziniОценок пока нет

- Rideable Segway Clone - Low Cost and Easy Build: Digital MPU6050 Accelerometer/gyro IMU BoardДокумент45 страницRideable Segway Clone - Low Cost and Easy Build: Digital MPU6050 Accelerometer/gyro IMU BoardpaolaОценок пока нет

- CE5215-Theory and Applications of Cement CompositesДокумент10 страницCE5215-Theory and Applications of Cement CompositesSivaramakrishnaNalluriОценок пока нет

- COVID Immunization Record Correction RequestДокумент2 страницыCOVID Immunization Record Correction RequestNBC 10 WJARОценок пока нет

- 1 075 Syn4e PDFДокумент2 страницы1 075 Syn4e PDFSalvador FayssalОценок пока нет

- MPPWD 2014 SOR CH 1 To 5 in ExcelДокумент66 страницMPPWD 2014 SOR CH 1 To 5 in ExcelElvis GrayОценок пока нет

- WPGPipingIndex Form 167 PDFДокумент201 страницаWPGPipingIndex Form 167 PDFRaj AryanОценок пока нет

- SyllabusДокумент9 страницSyllabusrr_rroyal550Оценок пока нет

- Consultancy Services For The Feasibility Study of A Second Runway at SSR International AirportДокумент6 страницConsultancy Services For The Feasibility Study of A Second Runway at SSR International AirportNitish RamdaworОценок пока нет

- Shares and Share CapitalДокумент50 страницShares and Share CapitalSteve Nteful100% (1)

- Fammthya 000001Документ87 страницFammthya 000001Mohammad NorouzzadehОценок пока нет

- HW4 Fa17Документ4 страницыHW4 Fa17mikeiscool133Оценок пока нет

- Tank Emission Calculation FormДокумент12 страницTank Emission Calculation FormOmarTraficanteDelacasitosОценок пока нет

- Completed NGC3 ReportДокумент4 страницыCompleted NGC3 ReportTiCu Constantin100% (1)

- Basic Electronic Troubleshooting For Biomedical Technicians 2edДокумент239 страницBasic Electronic Troubleshooting For Biomedical Technicians 2edClovis Justiniano100% (22)

- Ap06 - Ev04 Taller en Idioma Inglés Sobre Sistema de DistribuciónДокумент9 страницAp06 - Ev04 Taller en Idioma Inglés Sobre Sistema de DistribuciónJenny Lozano Charry50% (2)

- Enumerator ResumeДокумент1 страницаEnumerator Resumesaid mohamudОценок пока нет

- CW February 2013Документ60 страницCW February 2013Clint FosterОценок пока нет

- Spa ClaimsДокумент1 страницаSpa ClaimsJosephine Berces100% (1)

- Project 1. RockCrawlingДокумент2 страницыProject 1. RockCrawlingHằng MinhОценок пока нет

- Sun Hung Kai 2007Документ176 страницSun Hung Kai 2007Setianingsih SEОценок пока нет

- Pharmaceutical Microbiology NewsletterДокумент12 страницPharmaceutical Microbiology NewsletterTim SandleОценок пока нет

- WhatsNew 2019 enДокумент48 страницWhatsNew 2019 enAdrian Martin BarrionuevoОценок пока нет

- Part A Plan: Simple Calculater Using Switch CaseДокумент7 страницPart A Plan: Simple Calculater Using Switch CaseRahul B. FereОценок пока нет