Академический Документы

Профессиональный Документы

Культура Документы

Compiler Notes KCG Unit IV

Загружено:

Dr. MNV KiranbabuОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Compiler Notes KCG Unit IV

Загружено:

Dr. MNV KiranbabuАвторское право:

Доступные форматы

KCG COLLEGE OF TECHNOLOGY-CHENNAI-97

COMPUTER SCIENCE AND ENGINEERING

VI SEM CSE

CS1352 Principles of Compiler Design Unit-IV Question and answers

UNIT IV CODE GENERATION 9

Issues in the design of code generator The target machine Runtime Storage management

Basic Blocks and Flow Graphs Next-use Information A simple Code generator DAG

representation of Basic Blocks Peephole Optimization.

1) What is the role of code generator in a compiler?

CODE GENERATION

Thefinalphaseinourcompilermodelisthecode generator.Ittakesasinputan

intermediaterepresentationofthesourceprogramandproducesasoutputanequivalenttarget

program.

Therequirementstraditionallyimposedonacodegeneratoraresevere.The

outputcodemustbecorrectandofhighquality,meaningthatitshouldmakeeffectiveuseof

theresourcesofthetargetmachine.Moreover,thecodegeneratoritselfshouldrunefficiently.

fig. 1

2) Write in detail the issues in the design of code generator.

ISSUES IN THE DESIGN OF A CODE GENERATOR

Whilethedetailsaredependentonthetargetlanguageandtheoperatingsystem,issues

suchasmemorymanagement,instructionselection,registerallocation,andevaluationorderare

inherentinalmostallcodegenerationproblems.

INPUT TO THE CODE GENERATOR

Theinputtothecodegeneratorconsistsoftheintermediaterepresentationofthe

sourceprogramproducedbythefrontend,togetherwithinformationinthesymboltablethatisused

todeterminetheruntimeaddressesofthedataobjectsdenotedbythenamesintheintermediate

representation.

Thereareseveralchoicesfortheintermediatelanguage,including:linearrepresentations

suchaspostfixnotation,threeaddressrepresentationssuchasquadruples,virtualmachine

representationssuchassyntaxtreesanddags.

Weassumethatpriortocodegenerationthefrontendhasscanned,parsed,andtranslatedthe

sourceprogramintoareasonablydetailedintermediaterepresentation,sothevaluesofnames

appearingintheintermediatelanguagecanberepresentedbyquantitiesthatthetargetmachine

candirectlymanipulate(bits,integers,reals,pointers,etc.).Wealsoassumethatthenecessary

typecheckinghastakeplace,sotypeconversionoperatorshavebeeninsertedwherevernecessary

andobvioussemanticerrors(e.g.,attemptingtoindexanarraybyafloatingpointnumber)have

alreadybeendetected.Thecodegenerationphasecanthereforeproceedontheassumptionthatits

inputisfreeoferrors.Insomecompilers,thiskindofsemanticcheckingisdonetogetherwithcode

generation.

TARGET PROGRAMS

Theoutputofthecodegeneratoristhetargetprogram.Theoutputmaytakeonavariety

offorms:absolutemachinelanguage,relocatablemachinelanguage,orassemblylanguage.

Producinganabsolutemachinelanguageprogramasoutputhastheadvantagethatit

canbeplacedinalocationinmemoryandimmediatelyexecuted.Asmallprogramcanbecompiled

andexecutedquickly.Anumberofstudent-jobcompilers,suchasWATFIVandPL/C,produce

absolutecode.

Producingarelocatablemachinelanguageprogramasoutputallowssubprogramsto

becompiledseparately.Asetofrelocatableobjectmodulescanbelinkedtogetherandloadedfor

executionbyalinkingloader.Althoughwemustpaytheaddedexpenseoflinkingandloadingif

weproducerelocatableobjectmodules,wegainagreatdealofflexibilityinbeingabletocompile

subroutinesseparatelyandtocallotherpreviouslycompiledprogramsfromanobjectmodule.If

thetargetmachinedoesnothandlerelocationautomatically,thecompilermustprovideexplicit

relocationinformationtotheloadertolinktheseparatelycompiledprogramsegments.

Producinganassemblylanguageprogramasoutputmakestheprocessofcode

generationsomewhateasier.Wecangeneratesymbolicinstructionsandusethemacrofacilitiesof

theassemblertohelpgeneratecode.Thepricepaidistheassemblystepaftercodegeneration.

Becauseproducingassemblycodedoesnotduplicatetheentiretaskoftheassembler,thischoiceis

anotherreasonablealternative,especiallyforamachinewithasmallmemory,whereacompilermust

usesseveralpasses.

MEMORY MANAGEMENT

Mappingnamesinthesourceprogramtoaddressesofdataobjectsinruntimememory

isdonecooperativelybythefrontendandthecodegenerator.Weassumethatanameinathree-

addressstatementreferstoasymboltableentryforthename.

Ifmachinecodeisbeinggenerated,labelsinthreeaddressstatementshavetobe

convertedtoaddressesofinstructions.Thisprocessisanalogoustothebackpatching.Suppose

thatlabelsrefertoquadruplenumbersinaquadruplearray.Aswescaneachquadrupleinturnwe

candeducethelocationofthefirstmachineinstructiongeneratedforthatquadruple,simplyby

maintainingacountofthenumberofwordsusedfortheinstructionsgeneratedsofar.Thiscountcan

bekeptinthequadruplearray(inanextrafield),soifareferencesuchasj:goto iisencountered,

andiislessthanj,thecurrentquadruplenumber,wemaysimplygenerateajumpinstructionwith

thetargetaddressequaltothemachinelocationofthefirstinstructioninthecodeforquadruplei.If,

however,thejumpisforward,soiexceedsj,wemuststoreonalistforquadrupleithelocationof

thefirstmachineinstructiongeneratedforquadruplej.Thenweprocessquadruplei,wefillinthe

propermachinelocationforallinstructionsthatareforwardjumpstoi.

INSTRUCTION SELECTION

Thenatureoftheinstructionsetofthetargetmachinedeterminesthedifficultyof

instructionselection.Theuniformityandcompletenessoftheinstructionsetareimportantfactors.If

thetargetmachinedoesnotsupporteachdatatypeinauniformmanner,theneachexceptiontothe

generalrulerequiresspecialhandling.

Instructionspeedsandmachineidiomsareotherimportantfactors.Ifwedonotcare

abouttheefficiencyofthetargetprogram,instructionselectionisstraightforward.Foreachtypeof

three-addressstatementwecandesignacodeskeletonthatoutlinesthetargetcodetobegenerated

forthatconstruct.

Forexample,everythreeaddressstatementoftheformx:=y+z,wherex,y,andzarestatically

allocated,canbetranslatedintothecodesequence

MOVy,R0/*loadyintoregisterR0*/

ADDz,R0/*addztoR0*/

MOVR0,x/*storeR0intox*/

Unfortunately,thiskindofstatementby-statementcodegenerationoftenproducespoorcode.For

example,thesequenceofstatements

a:=b+c

d:=a+e

wouldbetranslatedinto

MOVb,R0

ADDc,R0

MOVR0,a

MOVa,R0

ADDe,R0

MOVR0,d

Herethefourthstatementisredundant,andsoisthethirdifaisnotsubsequentlyused.

Thequalityofthegeneratedcodeisdeterminedbyitsspeedandsize.

Atargetmachinewitharichinstructionsetmayprovideseveralwaysofimplementingagiven

operation.Sincethecostdifferencesbetweendifferentimplementationsmaybesignificant,anaive

translationoftheintermediatecodemayleadtocorrect,butunacceptablyinefficienttargetcode.For

exampleifthetargetmachinehasanincrementinstruction(INC),thenthethreeaddressstatement

a:=a+1maybeimplementedmoreefficientlybythesingleinstructionINCa,ratherthanbyamore

obvioussequencethatloadsaintoaregister,addonetotheregister,andthenstorestheresultback

intoa.

MOVa,R0

ADD#1,R0

MOVR0,a

Instructionspeedsareneededtodesigngoodcodesequencebutunfortunately,accurate

timinginformationisoftendifficulttoobtain.Decidingwhichmachinecodesequenceisbestfora

giventhreeaddressconstructmayalsorequireknowledgeaboutthecontextinwhichthatconstruct

appears.

REGISTER ALLOCATION

Instructionsinvolvingregisteroperandsareusuallyshorterandfasterthanthose

involvingoperandsinmemory.Therefore,efficientutilizationofregisterisparticularlyimportantin

generatinggoodcode.Theuseofregistersisoftensubdividedintotwosubproblems:

1.Duringregister allocation,weselectthesetofvariablesthatwillresideinregistersatapoint

intheprogram.

2.Duringasubsequentregister assignmentphase,wepickthespecificregisterthatavariable

willresidein.

Findinganoptimalassignmentofregisterstovariablesisdifficult,evenwithsingle

registervalues.Mathematically,theproblemisNP-complete.Theproblemisfurthercomplicated

becausethehardwareand/ortheoperatingsystemofthetargetmachinemayrequirethatcertain

registerusageconventionsbeobserved.

Certainmachinesrequireregister pairs(anevenandnextoddnumberedregister)for

someoperandsandresults.Forexample,intheIBMSystem/370machinesintegermultiplication

andintegerdivisioninvolveregisterpairs.Themultiplicationinstructionisoftheform

Mx,y

wherex,isthemultiplicand,istheevenregisterofaneven/oddregisterpair.

Themultiplicandvalueistakenfromtheoddregisterpair.Themultiplieryisasingleregister.The

productoccupiestheentireeven/oddregisterpair.

Thedivisioninstructionisoftheform

Dx,y

wherethe64-bitdividendoccupiesaneven/oddregisterpairwhoseevenregisterisx;yrepresents

thedivisor.Afterdivision,theevenregisterholdstheremainderandtheoddregisterthequotient.

Nowconsiderthetwothreeaddresscodesequences(a)and(b)inwhichtheonlydifferenceisthe

operatorinthesecondstatement.Theshortestassemblysequencefor(a)and(b)aregivenin(c).

Ristandsforregisteri.L,STandAstandforload,storeandaddrespectively.Theoptimalchoice

fortheregisterintowhichaistobeloadeddependsonwhatwillultimatelyhappentoe.

t:=a+bt:=a+b

t:=t*ct:=t+c

t:=t/dt:=t/d

(a)(b)

fig.2Twothreeaddresscodesequences

LR1,aLR0,a

AR1,bAR0,b

MR0,cAR0,c

DR0,dSRDAR0,32

STR1,tDR0,d

STR1,t

(a) (b)

fig.3Optimalmachinecodesequence

CHOICE OF EVALUATION ORDER

Theorderinwhichcomputationsareperformedcanaffecttheefficiencyofthetarget

code.Somecomputationordersrequirefewerregisterstoholdintermediateresultsthanothers.

Pickingabestorderisanotherdifficult,NP-completeproblem.Initially,weshallavoidtheproblem

bygeneratingcodeforthethree-addressstatementsintheorderinwhichtheyhavebeenproduced

bytheintermediatecodegenerator.

APPROCHES TO CODE GENERATION

Themostimportantcriterionforacodegeneratoristhatitproducecorrectcode.

Correctnesstakesonspecialsignificancebecauseofthenumberofspecialcasesthatcodegenerator

mustface.Giventhepremiumoncorrectness,designingacodegeneratorsoitcanbeeasily

implemented,tested,andmaintainedisanimportantdesigngoal.

3) What are basic blocks and flowgraphs?

BASIC BLOCKS AND FLOW GRAPHS

Agraphrepresentationofthree-addressstatements,calledaflow graph,isusefulfor

understandingcode-generationalgorithms,evenifthegraphisnotexplicitlyconstructedbyacode-

generationalgorithm.Nodesintheflowgraphrepresentcomputations,andtheedgesrepresentthe

flowofcontrol.Flowgraphofaprogramcanbeusedasavehicletocollectinformationaboutthe

intermediateprogram.Someregister-assignmentalgorithmsuseflowgraphstofindtheinnerloops

whereaprogramisexpectedtospendmostofitstime.

BASIC BLOCKS

Abasic blockisasequenceofconsecutivestatementsinwhichflowofcontrolenters

atthebeginningandleavesattheendwithouthaltorpossibilityofbranchingexceptattheend.The

followingsequenceofthree-addressstatementsformsabasicblock:

t1:=a*a

t2:=a*b

t3:=2*t2

t4:=t1+t3

t5:=b*b

t6:=t4+t5

Athree-addressstatementx:=y+zissaidtodefinexandtouseyorz.Anameinabasicblockis

saidtolive atagivenpointifitsvalueisusedafterthatpointintheprogram,perhapsinanotherbasic

block.

Thefollowingalgorithmcanbeusedtopartitionasequenceofthree-addressstatementsintobasic

blocks.

Algorithm1:Partitionintobasicblocks.

Input:Asequenceofthree-addressstatements.

Output:Alistofbasicblockswitheachthree-addressstatementinexactlyoneblock.

Method:

1. Wefirstdeterminethesetofleaders,thefirststatementsofbasicblocks.

Therulesweusearethefollowing:

I)Thefirststatementisaleader.

II)Anystatementthatisthetargetofaconditionalorunconditionalgotoisaleader.

III)Anystatementthatimmediatelyfollowsagotoorconditionalgotostatementisaleader.

2.Foreachleader,itsbasicblockconsistsoftheleaderandallstatementsuptobutnot

includingthenextleaderortheendoftheprogram.

Example3:Considerthefragmentofsourcecodeshowninfig.7;itcomputesthedotproductoftwo

vectorsaandboflength20.Alistofthree-addressstatementsperformingthiscomputationonour

targetmachineisshowninfig.8.

begin

prod:=0;

i:=1;

dobegin

prod:=prod+a[i]*b[i];

i:=i+1;

end

whilei<=20

end

fig 7:programtocomputedotproduct

LetusapplyAlgorithm1tothethree-addresscodeinfig8todetermineitsbasic

blocks.statement(1)isaleaderbyrule(I)andstatement(3)isaleaderbyrule(II),sincethelast

statementcanjumptoit.Byrule(III)thestatementfollowing(12)isaleader.Therefore,statements

(1)and(2)formabasicblock.Theremainderoftheprogrambeginningwithstatement(3)formsa

secondbasicblock.

(1)prod:=0

(2)i:=1

(3)t1:=4*i

(4)t2:=a[t1]

(5)t3:=4*i

(6)t4:=b[t3]

(7)t5:=t2*t4

(8)t6:=prod+t5

(9)prod:=t6

(10)t7:=i+1

(11)i:=t7

(12)ifi<=20goto(3)

fig 8.Three-addresscodecomputingdotproduct

prod := 0

i := 1

4) What are the structure preserving transformations on basic blocks?

TRANSFORMATIONSONBASICBLOCKS

Abasicblockcomputesasetofexpressions.Theseexpressionsarethevaluesofthe

namesliveonexitfromblock.Twobasicblocksaresaidtobeequivalentiftheycomputethesame

setofexpressions.

Anumberoftransformationscanbeappliedtoabasicblockwithoutchangingthe

setofexpressionscomputedbytheblock.Manyofthesetransformationsareusefulforimproving

thequalityofcodethatwillbeultimatelygeneratedfromabasicblock.Therearetwoimportant

classesoflocaltransformationsthatcanbeappliedtobasicblocks;thesearethestructure-preserving

transformationsandthealgebraictransformations.

STRUCTURE-PRESERVINGTRANSFORMATIONS

Theprimarystructure-preservingtransformationsonbasicblocksare:

1.commonsub-expressionelimination

2.dead-codeelimination

3.renamingoftemporaryvariables

4.interchangeoftwoindependentadjacentstatements

Weassumebasicblockshavenoarrays,pointers,orprocedurecalls.

1. Common sub-expression elimination

Considerthebasicblock

a:=b+c

b:=a-d

c:=b+c

d:=a-d

Thesecondandfourthstatementscomputethesameexpression,

namelyb+c-d,andhencethisbasicblockmaybetransformedintotheequivalentblock

a:=b+c

b:=a-d

c:=b+c

d:=b

Althoughthe1

st

and3

rd

statementsinbothcasesappeartohavethesameexpressionon

theright,thesecondstatementredefinesb.Therefore,thevalueofbinthe3

rd

statement

isdifferentfromthevalueofbinthe1

st

,andthe1

st

and3

rd

statementsdonotcomputethe

sameexpression.

2.Dead-code elimination

Supposexisdead,thatis,neversubsequentlyused,atthepointwherethestatement

x:=y+zappearsinabasicblock.Thenthisstatementmaybesafelyremovedwithout

changingthevalueofthebasicblock.

3. Renaming temporary variables

Supposewehaveastatementt:=b+c,wheretisatemporary.Ifwechangethisstatement

tou:=b+c,whereuisanewtemporaryvariable,andchangeallusesofthisinstanceof

ttou,thenthevalueofthebasicblockisnotchanged.Infact,wecanalwaystransform

abasicblockintoanequivalentblockinwhicheachstatementthatdefinesatemporary

definesanewtemporary.Wecallsuchabasicblockanormal-formblock.

4.Interchange of statements

Supposewehaveablockwiththetwoadjacentstatements

t1:=b+c

t2:=x+y

Thenwecaninterchangethetwostatementswithoutaffectingthevalueoftheblockifand

onlyifneitherxnoryist1andneitherbnorcist2.Anormal-formbasicblockpermitsall

statementinterchangesthatarepossible.

5) What are the instructions and address modes of the target machine?

Thetargetmachinecharacteristicsare

l Byte-addressable, 4 bytes/word, n registers

l Two operand instructions of the form

l op source, destination

l Example opcodes: MOV, ADD, SUB, MULT

l Several addressing modes

l An instruction has an associated cost

l Cost corresponds to length of instruction

Addressing Modes & Extra Costs

6) Generate target code for the source language statement

(a-b) + (a-c) + (a-c);

The 3AC for this can be written as

t := a b

u := a c

v := t + u

d := v + u //d live at the end

Show the code sequence generated by the simple code generation algorithm

What is its cost? Can it be improved?

Total cost=12

7) What is an activation record?

Informationneededbyasingleexecutionofprocedureismanagedusingacontiguous

blockofstoragecalledanactivationrecordorframe.Itiscustomarytopushthe

activationrecordofaprocedureontheruntimestackwhentheprocedureiscalledand

topoptheactivationrecordoffthestackwhencontrolreturnstothecaller.

8) What are the contents of activation record?

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Java8 Tutorial PDFДокумент59 страницJava8 Tutorial PDFGeorgescu TudorОценок пока нет

- RPG Interview Questions IBMДокумент6 страницRPG Interview Questions IBMJosiah RaymundoОценок пока нет

- 01Документ5 страниц01Ram AnandОценок пока нет

- Jaimini Chara Dasha: (Method of Raghavabhatta & Nrisimhasuri)Документ1 страницаJaimini Chara Dasha: (Method of Raghavabhatta & Nrisimhasuri)Dr. MNV KiranbabuОценок пока нет

- Examples: Analyzing AlgorithmsДокумент3 страницыExamples: Analyzing AlgorithmsDr. MNV KiranbabuОценок пока нет

- Results of Some Important YogasДокумент1 страницаResults of Some Important YogasDr. MNV KiranbabuОценок пока нет

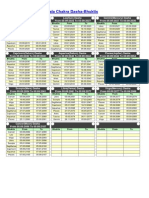

- Kala Chakra Dasha Set-UpДокумент1 страницаKala Chakra Dasha Set-UpDr. MNV KiranbabuОценок пока нет

- Kala Chakra Dasha-Bhuktis: Bhuktis From To Bhuktis From To Bhuktis From ToДокумент1 страницаKala Chakra Dasha-Bhuktis: Bhuktis From To Bhuktis From To Bhuktis From ToDr. MNV KiranbabuОценок пока нет

- X Pdfqqweee334443Документ1 страницаX Pdfqqweee334443Dr. MNV KiranbabuОценок пока нет

- Observations From SarvashtakavargaДокумент1 страницаObservations From SarvashtakavargaDr. MNV KiranbabuОценок пока нет

- Jaimini Mandooka Dasha: (Alternate Method of Division)Документ1 страницаJaimini Mandooka Dasha: (Alternate Method of Division)Dr. MNV KiranbabuОценок пока нет

- Q 9 DDDДокумент1 страницаQ 9 DDDDr. MNV KiranbabuОценок пока нет

- Observations From K.C.D Jeeva-Rashi and Amsha-RashiДокумент1 страницаObservations From K.C.D Jeeva-Rashi and Amsha-RashiDr. MNV KiranbabuОценок пока нет

- Q 7 AasswwqqДокумент1 страницаQ 7 AasswwqqDr. MNV KiranbabuОценок пока нет

- Observations From K.C.D Jeeva-Rashi and Amsha-RashiДокумент1 страницаObservations From K.C.D Jeeva-Rashi and Amsha-RashiDr. MNV KiranbabuОценок пока нет

- Planet Details: Astrologer: Dr. Kumara SanjayaДокумент1 страницаPlanet Details: Astrologer: Dr. Kumara SanjayaDr. MNV KiranbabuОценок пока нет

- Maitri ChakraДокумент1 страницаMaitri ChakraDr. MNV KiranbabuОценок пока нет

- Vimshottari Dasha: From........ To Dasha Lord Name Duration S.NДокумент1 страницаVimshottari Dasha: From........ To Dasha Lord Name Duration S.NDr. MNV KiranbabuОценок пока нет

- Planet Details: Astrologer: Dr. Kumara SanjayaДокумент1 страницаPlanet Details: Astrologer: Dr. Kumara SanjayaDr. MNV KiranbabuОценок пока нет

- Planet Details: Astrologer: Dr. Kumara SanjayaДокумент1 страницаPlanet Details: Astrologer: Dr. Kumara SanjayaDr. MNV KiranbabuОценок пока нет

- Planet Details: Astrologer: Dr. Kumara SanjayaДокумент1 страницаPlanet Details: Astrologer: Dr. Kumara SanjayaDr. MNV KiranbabuОценок пока нет

- Planet Details: Astrologer: Dr. Kumara SanjayaДокумент1 страницаPlanet Details: Astrologer: Dr. Kumara SanjayaDr. MNV KiranbabuОценок пока нет

- Enta Sep RaДокумент1 страницаEnta Sep RaDr. MNV KiranbabuОценок пока нет

- DDDДокумент1 страницаDDDDr. MNV KiranbabuОценок пока нет

- JampakaДокумент1 страницаJampakaDr. MNV KiranbabuОценок пока нет

- Go RaeДокумент1 страницаGo RaeDr. MNV KiranbabuОценок пока нет

- Kala Chakra Dasha-Bhuktis: Bhuktis From To Bhuktis From To Bhuktis From ToДокумент1 страницаKala Chakra Dasha-Bhuktis: Bhuktis From To Bhuktis From To Bhuktis From ToDr. MNV KiranbabuОценок пока нет

- Planetary Positions: Lagna Kundali Chandra KundaliДокумент1 страницаPlanetary Positions: Lagna Kundali Chandra KundaliDr. MNV KiranbabuОценок пока нет

- Full Integration of Matlab Simulink With Control Application Developement Using OPC UAДокумент6 страницFull Integration of Matlab Simulink With Control Application Developement Using OPC UABraian Konzgen100% (1)

- JavaДокумент24 страницыJavaProximoОценок пока нет

- Fanuc Pmc-Model Sa1/Sb7 Supplemental Programming Manual (LADDER Language)Документ12 страницFanuc Pmc-Model Sa1/Sb7 Supplemental Programming Manual (LADDER Language)mikeОценок пока нет

- Solutions Manual For Java 2E, Ralph MorelliДокумент544 страницыSolutions Manual For Java 2E, Ralph Morellisharklops100% (2)

- C Programming QuestionsДокумент28 страницC Programming QuestionsJayОценок пока нет

- COPYRIGHДокумент2 страницыCOPYRIGHJohan WahyudiОценок пока нет

- States, State Graphs, and Transition Testing: 1. SynopsisДокумент28 страницStates, State Graphs, and Transition Testing: 1. Synopsisanil kumar100% (1)

- Changeman HandbookДокумент14 страницChangeman HandbookBharat SahniОценок пока нет

- Cygwin Package ListДокумент40 страницCygwin Package ListotgwaterОценок пока нет

- Computer Fundamentals and Programming: Montaigne Garcia MolejonДокумент68 страницComputer Fundamentals and Programming: Montaigne Garcia MolejonUnknownОценок пока нет

- LearnCProgrammingLanguagebyTutorialsPoint 1 PDFДокумент322 страницыLearnCProgrammingLanguagebyTutorialsPoint 1 PDFRocky AndikaОценок пока нет

- Mbed Course Notes - Digital Input and OutputДокумент16 страницMbed Course Notes - Digital Input and OutputeasaahmedОценок пока нет

- Software Debugging Techniques: P. AdragnaДокумент16 страницSoftware Debugging Techniques: P. AdragnapavanaОценок пока нет

- Javaunit1 130907015927Документ29 страницJavaunit1 130907015927UjjWal MahAjanОценок пока нет

- Cobas 6000 SOPДокумент1 311 страницCobas 6000 SOPJohn Rumbaugh83% (6)

- MCQДокумент28 страницMCQKiranОценок пока нет

- Java File ProcessingДокумент16 страницJava File ProcessingJava OOPОценок пока нет

- ARM® Cortex® M4 Cookbook - Sample ChapterДокумент29 страницARM® Cortex® M4 Cookbook - Sample ChapterPackt Publishing100% (1)

- +2 CS 1,2,5 Marks Q&A - Gunaa 2Документ159 страниц+2 CS 1,2,5 Marks Q&A - Gunaa 2Jothiranjini KarthikeyanОценок пока нет

- FlexLine GeoCOM Manual en PDFДокумент131 страницаFlexLine GeoCOM Manual en PDFdamindaОценок пока нет

- Language Processing ActivitiesДокумент14 страницLanguage Processing ActivitiesarchtfОценок пока нет

- Syllabus PGDCAДокумент37 страницSyllabus PGDCAmd sahidulla ayonОценок пока нет

- Copy of ICPC Assiut Newcomers TrainingДокумент28 страницCopy of ICPC Assiut Newcomers Trainingsasasocial3Оценок пока нет

- COM Interop Part 1Документ22 страницыCOM Interop Part 1bagsajalОценок пока нет

- CS 101 Lecture 1 PDFДокумент31 страницаCS 101 Lecture 1 PDFMohammad ArafatОценок пока нет

- Chemistry - General Knowledge Questions and Answers Page 5Документ3 страницыChemistry - General Knowledge Questions and Answers Page 5surya123sОценок пока нет

- Intermediate Code GenerationДокумент62 страницыIntermediate Code GenerationSalithaОценок пока нет