Академический Документы

Профессиональный Документы

Культура Документы

Práctica Nº5 Pedro Asmal

Загружено:

Diego CriolloАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Práctica Nº5 Pedro Asmal

Загружено:

Diego CriolloАвторское право:

Доступные форматы

Abstract_

pedro aqui

pon tu introduccion.

I. INTRODUCCIN

Yo le se poner el abstract que esta en ingles en

espaol de introduccin pro wueno ah pon

como sabes poner tu..!!!....

..

..

II. OBJETIVOS

- Comprobar el funcionamiento bsico de

un Multiplexor.

- Conocer y diferenciar cada parte del

multiplexor.

- Armar y disear un esquema que

obtenga los sonidos de un piano.

III. MARCO TERICO

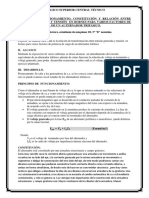

A. Multiplexores.

Un multiplexor es un circuito digital que

selecciona una de entre varias entradas de datos

I y lleva su valor lgico a la nica salida Z del

circuito. La seleccin de los datos se realiza

mediante una o varias entradas de control S.

Fig 1. Esquema Bsico Multiplexor 2 entradas.

La codificacin binaria resultante de las

entradas S indica el ndice de la entrada I que

pasa a la salida. Existiendo una entrada de

habilitacin (enable), la cual pone en

funcionamiento el circuito, y trabajo en bajo

activo. La seleccin de una lnea de salida

especfica se controla por los valores de los bits

de las n lneas de seleccin. [1]

Fig 2. Multiplexor 2 entradas Compuerta Logicas.

La seleccin de una lnea de salida especfica

se controla por los valores de los bits de las n

lneas de seleccin. [1]

Fig 3. Multiplexor 4 entradas Compuerta Logicas.

Prctica N 6

MANEJO DE LOS MULTIPLEXORES

Asmal Arias Pedro Andrs

pasmal@est.ups.edu.ec

Universidad Politcnica Salesiana

B. Decodificador 74147

La entrada es un nmero BCD de 4 BITS, el

nmero BCD se transforma en un cdigo de 7

segmentos que ilumina los segmentos del

visualizador LED.

Fig. 4. Codificador BCD 74147

Tambin se muestran 3 entradas extras en el

smbolo lgico. La entrada de test de lmparas

har lucir todos los segmentos adecuados para

ver si son operativos.

Pedro adjuntale un chance mas de teora no

sabia que mas darte poniendo..!!!

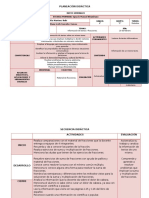

IV. DESARROLLO

MUX-2 CANALES

TABLA I: Tabla de verdad reducida

Enable D1 D0 S0 Z

0 0 0 0 0

0 0 0 1 0

0 0 1 0 1

0 0 1 1 0

0 1 0 0 0

0 1 0 1 1

0 1 1 0 1

0 1 1 1 1

1 X X X 0

Simulaciones.

Fig 5. Simulacin mediante compuertas lgicas.

Fig. 6. Circuito Decodificador.

MUX-3 CANALES

TABLA II: Multiplexor 3 canales.

Foto

Fig. 7. Circuito armado Protoboard

I. MATERIALES

1 Multiplexores 74151

1 555 Generador de Pulsos.

1 Compuerta NOT.

1 Codificador 74147.

7 Pulsantes.

Cable multipar.

10 resistencias de 220ohm.

1 Displays 7 segmentos AC.

7 trimers.

7 Transistores PNP

II. CONCLUSIONES

.

..

..

..

Ahi pon lo tuyo PEDRO.

III. BIBLIOGRAFIA

[1]http://es.scribd.com/doc/96659793/Universa

lidad-de-Compuertas-Multiplexores

Esquema del Circuito (Piano)

U1

LM555CM

GND

1

DIS

7

OUT

3

RST

4

VCC

8

THR

6

CON

5

TRI

2

C1

0.1F

C2

0.1F

R1

220

R2

6k

R3

100k

Key=A

30%

30%

30%

30%

30%

30%

Q1

2N2906

Q2

2N2906

Q3

2N2906

Q4

2N2906

Q5

2N2906

Q6

2N2906

U2

74LS147D

A

9

B

7

C

6

D

14

3

13

4

1

5

2

2

12

1

11

8

5

7

4

6

3

9

10

U3A

74LS32D

U3B

74LS32D

R9

220

VCC 5V

U4

74LS151D

~W

6

D0

4

D1

3

D2

2

D3

1

D4

15

D5

14

D6

13

D7

12

A

11

C

9

B

10

Y

5

~G

7

U5

74LS151D

~W

6

D0

4

D1

3

D2

2

D3

1

D4

15

D5

14

D6

13

D7

12

A

11

C

9

B

10

Y

5

~G

7

U7

74LS151D

~W

6

D0

4

D1

3

D2

2

D3

1

D4

15

D5

14

D6

13

D7

12

A

11

C

9

B

10

Y

5

~G

7

U8

74LS151D

~W

6

D0

4

D1

3

D2

2

D3

1

D4

15

D5

14

D6

13

D7

12

A

11

C

9

B

10

Y

5

~G

7

U9

74LS151D

~W

6

D0

4

D1

3

D2

2

D3

1

D4

15

D5

14

D6

13

D7

12

A

11

C

9

B

10

Y

5

~G

7

U10

74LS151D

~W

6

D0

4

D1

3

D2

2

D3

1

D4

15

D5

14

D6

13

D7

12

A

11

C

9

B

10

Y

5

~G

7

U11

74LS151D

~W

6

D0

4

D1

3

D2

2

D3

1

D4

15

D5

14

D6

13

D7

12

A

11

C

9

B

10

Y

5

~G

7

U12

A B C D E F G

CA

VCC

5V

VCC

5V

VCC

5V

VCC

5V

VCC

5V

VCC

5V

VCC

5V

VCC

5V

Вам также может понравиться

- DBR1 2do Inter Derecho LaboralДокумент6 страницDBR1 2do Inter Derecho LaboralDiego CriolloОценок пока нет

- Deber Piramide de KelsenДокумент3 страницыDeber Piramide de KelsenDiego CriolloОценок пока нет

- Mecanismo de Ruptura StreamerДокумент4 страницыMecanismo de Ruptura StreamerDiego CriolloОценок пока нет

- Informe Consumo-Deber 1Документ4 страницыInforme Consumo-Deber 1Diego CriolloОценок пока нет

- SOPLADORAДокумент4 страницыSOPLADORADiego CriolloОценок пока нет

- SOPLADORAДокумент4 страницыSOPLADORADiego CriolloОценок пока нет

- Deber OITДокумент2 страницыDeber OITDiego CriolloОценок пока нет

- Ethical Professional Ensayo Grupal VideoДокумент1 страницаEthical Professional Ensayo Grupal VideoDiego CriolloОценок пока нет

- Amplificadores potencia clases A-DДокумент2 страницыAmplificadores potencia clases A-DDiego CriolloОценок пока нет

- La Firma Del Acuerdo de ParisДокумент2 страницыLa Firma Del Acuerdo de ParisDiego CriolloОценок пока нет

- La Firma Del Acuerdo de ParisДокумент2 страницыLa Firma Del Acuerdo de ParisDiego CriolloОценок пока нет

- Especificaciones técnicas aisladores MTДокумент6 страницEspecificaciones técnicas aisladores MTDiego CriolloОценок пока нет

- Ejercicio 5.3 EnviarДокумент3 страницыEjercicio 5.3 EnviarDiego CriolloОценок пока нет

- Deber PreguntasДокумент3 страницыDeber PreguntasDiego CriolloОценок пока нет

- Elementos Pasivos y ActivosДокумент2 страницыElementos Pasivos y ActivosDiego CriolloОценок пока нет

- Grafica de Flujo de SeñalesДокумент3 страницыGrafica de Flujo de SeñalesDiego CriolloОценок пока нет

- Graficas de Funciones Con Periodo de 2?Документ1 страницаGraficas de Funciones Con Periodo de 2?Diego CriolloОценок пока нет

- Empalmes ElectricosДокумент7 страницEmpalmes ElectricosDiego CriolloОценок пока нет

- Universidad Politecnica SalesianaДокумент2 страницыUniversidad Politecnica SalesianaDiego CriolloОценок пока нет

- Efecto HallДокумент2 страницыEfecto HallDiego CriolloОценок пока нет

- Dijital 23Документ8 страницDijital 23Diego CriolloОценок пока нет

- Efecto HallДокумент2 страницыEfecto HallDiego CriolloОценок пока нет

- Tipos de Amplificadores de PotênciaДокумент3 страницыTipos de Amplificadores de PotênciaMartin CastilloОценок пока нет

- Integrador Trigonometria FinalДокумент7 страницIntegrador Trigonometria FinalDiego CriolloОценок пока нет

- Comp G10 08Документ16 страницComp G10 08Juan Manuel Barrera CruzОценок пока нет

- AnexoPractica 5 DigДокумент1 страницаAnexoPractica 5 DigDiego CriolloОценок пока нет

- Mando D Un Motor Desde Un Puesto !!Документ2 страницыMando D Un Motor Desde Un Puesto !!Diego CriolloОценок пока нет

- Energia Hidroelectrica PDFДокумент25 страницEnergia Hidroelectrica PDFDiego CriolloОценок пока нет

- Energia Hidroelectrica PDFДокумент25 страницEnergia Hidroelectrica PDFDiego CriolloОценок пока нет

- Física II: IntroducciónДокумент90 страницFísica II: IntroducciónCarlos Daniel Isaac QuijadaОценок пока нет

- Conceptos de La IOДокумент5 страницConceptos de La IOAntoni CruzОценок пока нет

- Estudio Hidrologico de Las Cuencas Hidrográficas Como Base para La Gestión de Los Recursos HídricosДокумент12 страницEstudio Hidrologico de Las Cuencas Hidrográficas Como Base para La Gestión de Los Recursos HídricosDavid ArévaloОценок пока нет

- Tarea1 PDSДокумент4 страницыTarea1 PDSLuis Llanganate75% (4)

- 2021 Medición Del Riesgo de Liquidez (UNAB)Документ528 страниц2021 Medición Del Riesgo de Liquidez (UNAB)FabianAndresCardenasRamirezОценок пока нет

- Manual de Practicas Dibujo IndustrialДокумент74 страницыManual de Practicas Dibujo IndustrialSalvador Cien Cuatro SeisОценок пока нет

- Alge 02Документ6 страницAlge 02Yois Isayol Armas PalominoОценок пока нет

- Unidad 1 Teoria - TermometriaДокумент5 страницUnidad 1 Teoria - TermometriaPabloОценок пока нет

- Flexocompresión 2020 01 21Документ19 страницFlexocompresión 2020 01 21Oscar RamirezОценок пока нет

- Alternador Trifásico, PRINCIPIO DE FUNCIONAMIENTO, CONSTITUCIÓN Y RELACIÓN ENTRE TENSIÓN GENERADA Y TENSIÓN EN BORNES PARA VARIOS FACTORES DE POTENCIA DE CARGA DE UN ALTERNADOR TRIFÁSICO.Документ4 страницыAlternador Trifásico, PRINCIPIO DE FUNCIONAMIENTO, CONSTITUCIÓN Y RELACIÓN ENTRE TENSIÓN GENERADA Y TENSIÓN EN BORNES PARA VARIOS FACTORES DE POTENCIA DE CARGA DE UN ALTERNADOR TRIFÁSICO.Georddy HerreraОценок пока нет

- Funciones Reales de Variable Real: Sen X XДокумент12 страницFunciones Reales de Variable Real: Sen X XgustavoОценок пока нет

- ¿Intuición Eidética o Abstracción Formal?Документ12 страниц¿Intuición Eidética o Abstracción Formal?Judas!100% (1)

- Medidas de Dispersión para Datos Agrupados y No AgrupadosДокумент5 страницMedidas de Dispersión para Datos Agrupados y No AgrupadosAndy CordovaОценок пока нет

- Proyecto Minero ApuntesДокумент52 страницыProyecto Minero ApuntesGonzalo IОценок пока нет

- Guía #5Документ2 страницыGuía #5Anonymous SdzZ7beqOvОценок пока нет

- Informe 2 - Cuerpos Parcialmente SumergidosДокумент14 страницInforme 2 - Cuerpos Parcialmente SumergidosYelitza TrejoОценок пока нет

- Introducción a la HidráulicaДокумент198 страницIntroducción a la HidráulicaMauricio LópezОценок пока нет

- Corte DirectoДокумент17 страницCorte DirectoPercy AJОценок пока нет

- Conservación Del ÍmpetuДокумент9 страницConservación Del ÍmpetuQaty's Morelos RamosОценок пока нет

- ANEXO 01 Cálculo de Fibra y Pol en CañaДокумент6 страницANEXO 01 Cálculo de Fibra y Pol en Cañarauldecima100% (4)

- Enteros ResueltosДокумент7 страницEnteros ResueltosfelixОценок пока нет

- Distribución BinomialДокумент3 страницыDistribución BinomialLidia AyosaОценок пока нет

- Lizarraga TC PDFДокумент235 страницLizarraga TC PDFJuan GutierrezОценок пока нет

- Ejer Cici OsДокумент6 страницEjer Cici Osansa.190308Оценок пока нет

- Temas 1er Grado Primaria MATEMATICAДокумент4 страницыTemas 1er Grado Primaria MATEMATICAAngie León RodriguezОценок пока нет

- Teoria de Conjuntos UcvДокумент29 страницTeoria de Conjuntos UcvmarciallopezОценок пока нет

- MM5Документ13 страницMM5jairo huamanОценок пока нет

- Dokumen - Tips - Tippens Fisica 7ediapositivas31aДокумент29 страницDokumen - Tips - Tippens Fisica 7ediapositivas31aGerry Antonio Cosme GarateОценок пока нет

- Informe de Filtracion A Presion Constante UNMSMДокумент33 страницыInforme de Filtracion A Presion Constante UNMSMBrian WilliamsОценок пока нет

- PLANEACIÓN DIDÁCTICA MarzoДокумент24 страницыPLANEACIÓN DIDÁCTICA MarzoIveth GonzálezОценок пока нет