Академический Документы

Профессиональный Документы

Культура Документы

Xc4000 Fpga Mod 4

Загружено:

ksm_commonИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Xc4000 Fpga Mod 4

Загружено:

ksm_commonАвторское право:

Доступные форматы

FIELD PROGRAMMABLE GATE ARRAY (FPGA)

XC4000

Introduction

FPGA consists of an array of uncommitted elements that can be interconnected in general

way .

the interconnections between elements are user-programmable .

Consist of an array of logic blocks, surrounded by programmable I/O blocks, and

connected with programmable interconnect.

It consists of a two-dimensional array of logic blocks that can be connected by general

interconnection resources.

The interconnect comprises segments of wire , where the segments may be of various

length .

Present in the interconnect are the programmable switches that serve to connect the logic

blocks to the wire segments , or one wire segment to another .

XC4000

XC4000 Series high-performance, high-capacity Field Programmable Gate Arrays

(FPGAs) provide the benefits of custom CMOS VLSI.

while avoiding the initial cost, long development cycle, and inherent risk of a

conventional masked gate array.

Detailed Functional Description

XC4000 Series devices are more powerful. They offer on-chip edge-triggered and dual-port

RAM, clock enables on I/O flip-flops, and wide-input decoders. They are more versatile in many

applications, especially those involving RAM. Design cycles are faster due to a combination of

increased routing resources and more sophisticated software.

Basic Building Blocks

Xilinx user-programmable gate arrays include two major configurable elements:

configurable logic blocks (CLBs) and

input/output blocks (IOBs).

CLBs provide the functional elements for constructing the users logic.

IOBs provide the interface between the package pins and internal signal lines.

Three other types of circuits are also available:

3-State buffers (TBUFs) driving horizontal long lines are associated with each CLB.

Wide edge decoders are available around the periphery of each device.

An on-chip oscillator is provided.

Programmable interconnect resources provide routing paths to connect the inputs and outputs of

these configurable elements to the appropriate networks.

The functionality of each circuit block is customized during configuration by programming

internal static memory cells. The values stored in these memory cells determine the logic

functions and interconnections implemented in the FPGA.

Configurable Logic Block (CLB)

Configurable Logic Blocks implement most of the logic in an FPGA. The principal CLB

elements are shown in Figure 1.

Two 4-input function generators (F and G) offer unrestricted versatility. Most

combinatorial logic functions need four or fewer inputs. However, a third function

generator (H) is provided.

The H function generator has three inputs. Either zero, one, or two of these inputs can be

the outputs of F and G; the other input(s) are from outside the CLB.

The CLB can, therefore, implement certain functions of up to nine variables, like parity

check or expandable-identity comparison of two sets of four inputs.

Each CLB contains two storage elements that can be used to store the function generator outputs.

However, the storage elements and function generators can also be used independently.

DIN can be used as a direct input to either of the two storage elements. H1 can drive the other

through the H function generator. Function generator outputs can also drive two outputs

independent of the storage element outputs.

This versatility increases logic capacity and simplifies routing. Thirteen CLB inputs and four

CLB outputs provide access to the function generators and storage elements. These inputs and

outputs connect to the programmable interconnect resources outside the block.

Components of CLB

Function Generators

Four independent inputs are provided to each of two function generators (F1 - F4 and G1 - G4).

These function generators, with outputs labeled F and G, are each capable of implementing any

arbitrarily defined Boolean function of four inputs. The function generators are implemented as

memory look-up tables. The propagation delay is therefore independent of the function

implemented.

A third function generator, labeled H, can implement any Boolean function of its three inputs.

Two of these inputs can optionally be the F and G functional generator outputs. Alternatively,

one or both of these inputs can come from outside the CLB (H2, H0). The third input must come

from outside the block (H1). Signals from the function generators can exit the CLB on two

outputs. F or H can be connected to the X output. G or H can be connected to the Y output.

A CLB can be used to implement any of the following functions:

any function of up to four variables, plus any second function of up to four unrelated variables,

plus any third function of up to three unrelated variables1

any single function of five variables

any function of four variables together with some functions of six variables

some functions of up to nine variables.

Function generators (LUTs) can be treated as RAM cells _ Single-port operation

Configure as either one 16x2 or 32x1 bit array (both LUTs), two 16x1 bit arrays

(both LUTs), or one 16x1 bit array (one LUT; use the other as logic)

Each has a common read / write port

Synchronous (edge-triggered) operation

Asynchronous (level-triggered) operation _ Dual-port operation

Configure as one 16x1 bit array, using both LUTs

One write port, two read ports _ Supports simultaneous read and write operations to same or

different addresses

Synchronous (edge-triggered) operation

Flip-Flops

The two edge-triggered D-type flip-flops have common clock (K) and clock enable (EC) inputs.

Either or both clock inputs can also be permanently enabled.

Latches

The CLB storage elements can also be configured as latches. The two latches have common

clock (K) and clock enable (EC) inputs.

Clock Input

Each flip-flop can be triggered on either the rising or falling clock edge. The clock pin is shared

by both storage elements. However, the clock is individually invertible for each storage element.

Any inverter placed on the clock input is automatically absorbed into the CLB.

Clock Enable

The clock enable signal (EC) is active High. The EC pin is shared by both storage elements. If

left unconnected for either, the clock enable for that storage element defaults to the active state.

EC is not invertible within the CLB.

Set/Reset

An asynchronous storage element input (SR) can be configured as either set or reset. This

configuration option determines the state in which each flip-flop becomes operational

after configuration.

Data Inputs and Outputs

The source of a storage element data input is programmable. It is driven by any of the functions

F, G, and H, or by the Direct In (DIN) block input. The flip-flops or latches drive the XQ and

YQ CLB outputs.

Control Signals

Multiplexers in the CLB map the four control inputs (C1 - C4 in Figure 1) into the four internal

control signals (H1,DIN/H2, SR/H0, and EC). Any of these inputs can drive any of the four

internal control signals.

When the logic function is enabled, the four inputs are:

EC Enable Clock

SR/H0 Asynchronous Set/Reset or H function

generator Input 0

DIN/H2 Direct In or H function generator Input 2

H1 H function generator Input 1.

When the memory function is enabled, the four inputs are:

EC Enable Clock

WE Write Enable

D0 Data Input to F and/or G function generator

D1 Data input to G function generator (16x1 and

16x2 modes) or 5th Address bit (32x1 mode).

Input/Output Blocks (IOBs)

User-configurable input/output blocks (IOBs) provide the interface between external package

pins and the internal logic. Each IOB controls one package pin and can be configured for input,

output, or bidirectional signals.Figure 15 shows a simplified block diagram of the XC4000 IOB.

Two I/O Blocks (IOBs) are at the end of each row and column

Each IOB contains an input register/ latch and an output register / latch

Two inputs (to chip): direct & register

The associated I/O pin can be used as either an input, output, or bidirectional pin

I1 and I2 are input Pins.

OUT, T, OUTPUT CLOCK and CLOCK ENABLE are the out bit bit, its three state

enable, ouput clock and input clock enable respectively.

The ouput driver,s slew rate is programmable and a pull-up or pull down resistor is

connected to its output pin.

Programmable Switch Matrices

The horizontal and vertical single- and double-length lines intersect at a box called a

programmable switch matrix (PSM). Each switch matrix consists of programmable pass

transistors used to establish connections between the lines (see Figure 26).

For example, a single-length signal entering on the right side of the switch matrix can be routed

to a single-length line on the top, left, or bottom sides, or any combination thereof, if multiple

branches are required. Similarly, a double- length signal can be routed to a double-length line on

any or all of the other three edges of the programmable switch matrix.

Single-Length Lines

Single-length lines provide the greatest interconnect flexibility and offer fast routing between

adjacent blocks. There are eight vertical and eight horizontal single-length lines associated with

each CLB. These lines connect the switching matrices that are located in every row and a column

of CLBs.

Double-Length Lines

The double-length lines consist of a grid of metal segments, each twice as long as the single-

length lines: they run past two CLBs before entering a switch matrix. Double-length lines are

grouped in pairs with the switch matrices staggered, so that each line goes through a switch

matrix at every other row or column of CLBs (see Figure 28).

Quad- Length Lines

XC4000X devices also include twelve vertical and twelve horizontal quad lines per CLB row

and column. Quad lines are four times as long as the single-length lines. They are interconnected

via buffered switch matrices

Quad lines run past four CLBs before entering a buffered switch matrix. They are grouped in

fours, with the buffered switch matrices staggered, so that each line goes through a buffered

switch matrix at every fourth CLB location in that row or column. (See Figure 29.)

Direct Interconnect (XC4000X only)

The XC4000X offers two direct, efficient and fast connections between adjacent CLBs. These

nets facilitate a data flow from the left to the right side of the device, or from the top to the

bottom, as shown in Figure 30. Signals routed on the direct interconnect exhibit minimum

interconnect propagation delay and use no general routing resources. The direct interconnect is

also present between CLBs and adjacent IOBs. Each IOB on the left and top device edges has a

direct path to the nearest CLB. Each CLB on the right and bottom edges of the array has a direct

path to the nearest two IOBs, since there are two IOBs for each row or column of CLBs. The

place and route software uses direct interconnect whenever possible, to maximize routing

resources and minimize interconnect delays.

Вам также может понравиться

- Unit Ii: CPLD & Fpga Architecture & ApplicationsДокумент20 страницUnit Ii: CPLD & Fpga Architecture & ApplicationsNarasimha Murthy Yayavaram100% (1)

- Unit Ii: CPLD & Fpga Architecture & ApplicationsДокумент18 страницUnit Ii: CPLD & Fpga Architecture & ApplicationsGoutham DevisettyОценок пока нет

- Xilinx XC4000Документ24 страницыXilinx XC4000jeevitha100% (3)

- Field Programmable Gate ArrayДокумент18 страницField Programmable Gate ArrayTushar GargОценок пока нет

- Part2 PDFДокумент6 страницPart2 PDFمحيي الدين الكميشىОценок пока нет

- Altera FLEX 8000 Block Diagram (Review) Altera FLEX 10K Block Diagram (Review)Документ4 страницыAltera FLEX 8000 Block Diagram (Review) Altera FLEX 10K Block Diagram (Review)Rohith RajОценок пока нет

- Spartan II FPGAДокумент18 страницSpartan II FPGAA B ShindeОценок пока нет

- Fpga & It's ArchitectureДокумент39 страницFpga & It's Architectureeeshgarg100% (6)

- Abstract:: Figure 1: Basic FPGA ConfigurationДокумент4 страницыAbstract:: Figure 1: Basic FPGA ConfigurationEr Nayan PithadiyaОценок пока нет

- LUT - (Look Up Table) : Field Programmable Gate ArraysДокумент3 страницыLUT - (Look Up Table) : Field Programmable Gate ArrayspawanzОценок пока нет

- FPGA TechnologyДокумент26 страницFPGA TechnologyvinaypantraОценок пока нет

- XILINX XC SeriesДокумент41 страницаXILINX XC SeriesAnil Kumar YernintiОценок пока нет

- Module 2 ASICДокумент52 страницыModule 2 ASICmanjunathanaikvОценок пока нет

- Xapp024.pdfxilinx XC 3000Документ11 страницXapp024.pdfxilinx XC 3000Rohith RajОценок пока нет

- PLD Architectures and TestingДокумент37 страницPLD Architectures and TestingParesh SawantОценок пока нет

- Spartan and Spartan-XL FPGA Families Data Sheet: Product SpecificationДокумент83 страницыSpartan and Spartan-XL FPGA Families Data Sheet: Product SpecificationAkash ShejuleОценок пока нет

- FPG AДокумент29 страницFPG AfacelessОценок пока нет

- CPLD XC9500Документ16 страницCPLD XC9500A B ShindeОценок пока нет

- Spartan 2 e 07Документ74 страницыSpartan 2 e 07Huzur AhmedОценок пока нет

- FpgaДокумент6 страницFpgaÁryâñ SinghОценок пока нет

- Lec 2Документ26 страницLec 2sk2417Оценок пока нет

- VHDL TutorialДокумент127 страницVHDL TutorialDeepanker KumeriaОценок пока нет

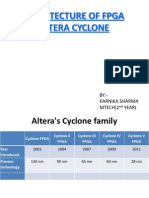

- Architecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)Документ29 страницArchitecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)karnika143100% (1)

- Xapp 465Документ17 страницXapp 465chakri474Оценок пока нет

- Mapping The SISO Module of The Turbo Decoder To A FPFAДокумент8 страницMapping The SISO Module of The Turbo Decoder To A FPFAAnonymous 9ksuyYy34PОценок пока нет

- Combinational Logic CircuitДокумент29 страницCombinational Logic CircuitKalkidan SisayОценок пока нет

- Fpga Introduction 20190626aДокумент26 страницFpga Introduction 20190626atulasiОценок пока нет

- DCS-2 Practical File Part-1Документ26 страницDCS-2 Practical File Part-1ykr007Оценок пока нет

- BY Prof. Y. P. Jadhav Physics Department Smt. CHM College, Ulhasnagar - 3Документ52 страницыBY Prof. Y. P. Jadhav Physics Department Smt. CHM College, Ulhasnagar - 3Prof. Yashavant p. JadhavОценок пока нет

- XC9500XL High-Performance CPLD Family Data Sheet: Preliminary Product SpecificationДокумент17 страницXC9500XL High-Performance CPLD Family Data Sheet: Preliminary Product SpecificationArunkumar PatilОценок пока нет

- ALU MISSDV0716 G.kaladhar Design PlanДокумент16 страницALU MISSDV0716 G.kaladhar Design Plangourishettikaladhar562Оценок пока нет

- Spartan 6 Slice and Io ResourcesДокумент31 страницаSpartan 6 Slice and Io ResourcesJabeen BanuОценок пока нет

- FPGA Arquitectura BasicaДокумент7 страницFPGA Arquitectura BasicaJesus LeyvaОценок пока нет

- Programmable ASIC Logic CellsДокумент36 страницProgrammable ASIC Logic CellsnandanОценок пока нет

- Xilinx XC 3000Документ21 страницаXilinx XC 3000shabbir470100% (1)

- m10 HandbookДокумент593 страницыm10 HandbookHChОценок пока нет

- Presentation 1Документ23 страницыPresentation 1khushalee.chavadaОценок пока нет

- C 789Документ18 страницC 789Ác QủyОценок пока нет

- Microprocessors and Its Application Answer KeyДокумент18 страницMicroprocessors and Its Application Answer Keyselvi0412Оценок пока нет

- Xilinx xc4000 & Altera'S Flex 8000/10000 FPGAДокумент17 страницXilinx xc4000 & Altera'S Flex 8000/10000 FPGAkumarkankipati19Оценок пока нет

- Xilinx XC 3000 56c80ecc547beДокумент21 страницаXilinx XC 3000 56c80ecc547beATHULYA AJAYAN KОценок пока нет

- Introduction To International Electro Technical Commission (IEC) 61131-3Документ38 страницIntroduction To International Electro Technical Commission (IEC) 61131-3Glan DevadhasОценок пока нет

- Actel Device ArchitectureДокумент8 страницActel Device ArchitectureUday KumarОценок пока нет

- Basic FPGA Architectures: Altera XilinxДокумент8 страницBasic FPGA Architectures: Altera XilinxkvinothscetОценок пока нет

- Introduction To Field Programmable Gate Array (FPGA)Документ7 страницIntroduction To Field Programmable Gate Array (FPGA)Burakcan GuvenirОценок пока нет

- Lab 5Документ7 страницLab 5Harish RamasubramanianОценок пока нет

- Lab MC P1 1618200Документ17 страницLab MC P1 1618200luis gonzalezОценок пока нет

- L12: Reconfigurable Logic ArchitecturesДокумент30 страницL12: Reconfigurable Logic ArchitecturesGaurav UpadhyayОценок пока нет

- 8255 Programmable Peripheral InterfaceДокумент78 страниц8255 Programmable Peripheral Interfaceedwardianirfan89% (9)

- Digital LogicДокумент6 страницDigital LogicIS-HAK SULEMAN BAAKOОценок пока нет

- XC9500XL High-Performance CPLD Family Data Sheet: Product SpecificationДокумент18 страницXC9500XL High-Performance CPLD Family Data Sheet: Product SpecificationonafetsОценок пока нет

- EMISY Second Test Exemplary Questions Solved-3Документ15 страницEMISY Second Test Exemplary Questions Solved-3YANG LIUОценок пока нет

- Lecture 2 - Introduction To FPGAs PDFДокумент14 страницLecture 2 - Introduction To FPGAs PDFVenkateswara ReddyОценок пока нет

- PeelДокумент4 страницыPeelSaurabh Bansal100% (1)

- Main Memory 64kB Block Size 8 Bytes Direct Mapped Cache - 32 LinesДокумент34 страницыMain Memory 64kB Block Size 8 Bytes Direct Mapped Cache - 32 LinesSri Vivek VangaОценок пока нет

- PLDsДокумент39 страницPLDsSANDEEP KUMARОценок пока нет

- Antifuse-Based Fpgas: Actel & QuicklogicДокумент38 страницAntifuse-Based Fpgas: Actel & QuicklogicSaurabh KukretiОценок пока нет

- Rohini 90925466680Документ6 страницRohini 90925466680SubraОценок пока нет

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960От EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Оценок пока нет

- ThaabangaleДокумент2 страницыThaabangaleksm_commonОценок пока нет

- Explain The Operation of SEPIC Converter With Neat DiagramsДокумент1 страницаExplain The Operation of SEPIC Converter With Neat Diagramsksm_commonОценок пока нет

- Tum Paas Aaye Yun MuskurayeДокумент1 страницаTum Paas Aaye Yun Muskurayeksm_commonОценок пока нет

- Electric Motors Traction MotorsДокумент1 страницаElectric Motors Traction Motorsksm_commonОценок пока нет

- Earthing: Akhila.RДокумент19 страницEarthing: Akhila.Rksm_commonОценок пока нет

- Invoicing System v2Документ26 страницInvoicing System v2api-137303031Оценок пока нет

- JNTU Old Question Papers 2007Документ8 страницJNTU Old Question Papers 2007Srinivasa Rao GОценок пока нет

- Global CatalogueДокумент12 страницGlobal CatalogueSalmanОценок пока нет

- Unit01-Getting Started With .NET Framework 4.0Документ40 страницUnit01-Getting Started With .NET Framework 4.0mgsumaОценок пока нет

- Confidentiality Agreement TemplateДокумент2 страницыConfidentiality Agreement TemplateJulie BarramedaОценок пока нет

- TutoriaДокумент351 страницаTutoriasakunthalapcsОценок пока нет

- Bridge Design Pattern: Presented By: Atif Saeed Misbah NiaziДокумент22 страницыBridge Design Pattern: Presented By: Atif Saeed Misbah Niaziaaatif121Оценок пока нет

- SEO Cheat SheetДокумент5 страницSEO Cheat SheetIvona Ivkovic100% (2)

- Fintech PaperДокумент16 страницFintech PaperTarun kumar100% (1)

- Reviews: Virtual Reality Technology (2nd Edition)Документ2 страницыReviews: Virtual Reality Technology (2nd Edition)llОценок пока нет

- Case RCBДокумент76 страницCase RCBSaurabh KatariaОценок пока нет

- CNS Course Plan - Iv CДокумент9 страницCNS Course Plan - Iv CMohana SubbuОценок пока нет

- Cyinder Track CalculatorДокумент3 страницыCyinder Track CalculatorSpockCritical CriticalОценок пока нет

- English 6 - EJE 4 - Week 10Документ3 страницыEnglish 6 - EJE 4 - Week 10Yan Carlos Morales MurciaОценок пока нет

- An Acknowledgement LetterДокумент1 страницаAn Acknowledgement LetterGovindan PerumalОценок пока нет

- Hyperion EssbaseДокумент16 страницHyperion Essbaseguru_rcpОценок пока нет

- BU R&D Form 1 - Detailed R&D Program or Project ProposalДокумент2 страницыBU R&D Form 1 - Detailed R&D Program or Project ProposalOween SamsonОценок пока нет

- Facility Design GuidelinesДокумент440 страницFacility Design GuidelinesWalid Abou HassanОценок пока нет

- SystemDesk - EB Tresos Studio Workflow DescriptionsДокумент23 страницыSystemDesk - EB Tresos Studio Workflow DescriptionsAmalkumar V GОценок пока нет

- CustomPC 2023-2 PDFДокумент100 страницCustomPC 2023-2 PDFTavimmmmmОценок пока нет

- Jbase Locking MecanismeДокумент33 страницыJbase Locking MecanismeMamat AdoumaОценок пока нет

- HRB754Документ2 страницыHRB754عبدالله رحيمОценок пока нет

- SEC08-20 Rehabilitation TechnologyДокумент2 страницыSEC08-20 Rehabilitation TechnologyJuliana Orjuela Garcia100% (1)

- 5 Pengenalan OSДокумент44 страницы5 Pengenalan OSFahrul WahidОценок пока нет

- The Basics of Resume WritingДокумент29 страницThe Basics of Resume WritinglolaОценок пока нет

- Best Lesson PlanДокумент4 страницыBest Lesson Planapi-398545121Оценок пока нет

- Obsolete Product: Descriptio FeaturesДокумент8 страницObsolete Product: Descriptio FeaturesMaria Das Dores RodriguesОценок пока нет

- Batch Process in SAP Net Weaver GatewayДокумент12 страницBatch Process in SAP Net Weaver GatewayArun Varshney (MULAYAM)Оценок пока нет

- TIBCO BW Performance Best PracticesДокумент48 страницTIBCO BW Performance Best PracticesSrinivasKannanОценок пока нет

- Your World Made Simple.: Door Lock Interface InstructionsДокумент8 страницYour World Made Simple.: Door Lock Interface InstructionshungleteОценок пока нет