Академический Документы

Профессиональный Документы

Культура Документы

Lecture16 Memorias

Загружено:

Bala KrishnaОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Lecture16 Memorias

Загружено:

Bala KrishnaАвторское право:

Доступные форматы

Lecture 13 ECE 425

Lecture 13 -- Memories

Lecture 13 ECE 425

Outline

Types of memory in semiconductor systems

Basic array layout

ROM design

SRAM cell design

Multi-port SRAMs

Content-addressable memories

DRAMs

Decoders

Lecture 13 ECE 425

Storage Systems

Many types of storage devices in electronic systems -- disk,

tape, memory chips, etc.

Two high-level differentiating features:

Volatility -- does data go away if you remove power?

Does time to access a datum depend on the

address/location of the datum? (random-access)

Most semiconductor memories are described as random-

access, although this description is becoming increasingly

untrue.

Lecture 13 ECE 425

Memory Terminology

ROM -- Read-Only Memory. Once fabricated, you cant

change the contents of the memory

PROM -- Programmable Read-Only Memory. Writes

take orders of magnitude longer than reads (often

milliseconds)

FLASH memory is an example of this technology

RAM -- Random-Access Memory. Reads and writes take

approximately the same amount of time. Access time is

independent of which address youre referencing.

Lecture 13 ECE 425

Basic Memory Layout

Organization is similar for all types of semiconductor

memory, difference is in the cells that hold bits

Lecture 13 ECE 425

Chip-Level Organization

Memory chips may contain multiple arrays, or modules, to

improve performance

Also allows idle modules to be powered down

Lecture 13 ECE 425

Memory Cells

Memory arrays are grids of bit cells, each of which holds

one bit of data

Typically the high bits of the address select a row of the

memory, the signal that selects the row is called a word

line

Each cell in the selected row drives its output and/or

reads its input on a bit line or lines

Low bits of the address select which of the bit lines are

sent to the output or written

Lecture 13 ECE 425

ROMs

Simplest ROM cell is a single transistor

Precharge all bit lines high, assert word line. Transistors

pull bits whose output = 0 low.

Lecture 13 ECE 425

Example Layout

Lecture 13 ECE 425

Programming ROMs

Done at fabrication time

Multiple options

Put transistors in the array where you want 0s in the

output

Place transistors in every possible position, only

connect up the ones that correspond to 0s

If you care about speed, you only want to include

necessary transistors (reduce load on wordlines)

For general-purpose ROM chips, often use the connection

method, as that allows chip to be customized by changing

only 1-2 layers/masks

In some technologies, can program by burning

connections with a laser/electron beam

Lecture 13 ECE 425

Random-Access Memories

Two major types:

1. Static RAM (SRAM): relies on active transistor drive to

hold state

Retains data indefinitely

Fast

Relatively large bit cells

2. Dynamic RAM (DRAM): stores data on capacitors

Small bit cells

Slower than SRAM

Needs to be refreshed, or will lose data over time

Destructive read

Lecture 13 ECE 425

Basic SRAM Cell

Cross-coupled inverters hold state

To write, drive data strongly on bit lines, such that you

overwhelm the stored value

Lecture 13 ECE 425

Circuit Implementation

Generally precharge bit lines to Vdd/2 while decoder is

determining which word line to drive

Reduces read time

Allows use of differential sense-amplifier

Lecture 13 ECE 425

Example Layout

Lecture 13 ECE 425

Multi-Ported SRAM Cell

Often want to be able to access multiple locations within

an array simultaneously

Example: Processor register file typically wants to

handle two reads, one write per cycle

Add additional pass-transistors, bit lines to each cell to

allow this

Need to be careful about simultaneous reads/writes and

not writing multiple times to the same bit

Area grows quadratically with number of ports

If you need many ports, often better to make multiple

copies of the memory with fewer ports/copy

Lecture 13 ECE 425

Three-Port SRAM Cell

Lecture 13 ECE 425

Variant -- Content-Addressable Memory

Can do parallel comparison of all words in an array to see

if their data matches a given value

Drive data on !bit line, !data on bit, do not assert any

word lines

Match signals of all bits in a word act as wired-AND

Lecture 13 ECE 425

SRAM Cell Design Issues

N-FET pass-transistors limit voltage on bit lines to V

dd

-V

t

Count on sense amplifiers to generate rail-rail outputs

with these inputs

Older designs precharged both bitlines to V

dd

, let cell

discharge one of them to ground.

Lecture 13 ECE 425

Design Issues -- Reads

Strong size/speed trade-off

Small transistors will take a long time to

charge/discharge the bit lines

Big transistors take more space, require stronger drive

to write

Lecture 13 ECE 425

Design Issues -- Writes

Lecture 13 ECE 425

Dynamic RAMs

Use single-transistor cell to store charge on a capacitor

Output voltage depends on relative capacitances of C

d

and bit line

Destructive read, requires sense amplifier

Lecture 13 ECE 425

DRAM Cell Layout

Lecture 13 ECE 425

DRAM Layout

Bit cell capacitor is effectively a dummy transistor that

we only use for its gate capacitance

Can bias polysilicon line to create a depletion region and

increase cell capacitance

Modern designs use more sophisticated structures, such

as trench capacitors, to reduce area

Tradeoff:

High cell capacitance increases cell area and write

time, but increases output voltage swing and time

before data is lost

Low cell capacitance reduces area, but increases

demands on the sense amplifier

Lecture 13 ECE 425

Decoders

Reminder of basic array layout

Decoders job is to generate a one-hot output

Word line corresponding to input value is high, all

others low

Lecture 13 ECE 425

Example

If there are only two address inputs, decoder truth table is

We can implement decoders using static or dynamic

circuits

Lecture 13 ECE 425

Static Row Decoder

Lecture 13 ECE 425

Static Row Decoder

If there are many address inputs, may be better to use

multi-level structure

Limits number of inputs to each gate

Allows staging of transistor sizes to get enough drive

on word line without too much load on address lines

Lecture 13 ECE 425

Example Using Two-Input Predecoders

Lecture 13 ECE 425

Dynamic Row Decoders

Lecture 13 ECE 425

Dynamic Row Decoders

Lecture 13 ECE 425

Column Decoders

Lecture 13 ECE 425

Column Decoders

Lecture 13 ECE 425

Column Decoders

An alternative design is to use a structure similar to the

row decoder to generate a one-hot drive signal based on

the address bits

Put full pass-gate at the output of each bit line, control

signal to pass-gates are the outputs of the decoder

Gives full output swings

Fewer transistors in series --> faster

May take more area, especially when you consider the

number of control wires

Lecture 13 ECE 425

Putting it All Together

Lecture 13 ECE 425

Readings

Sections 11.1-11.4, 11.6 in your book

Вам также может понравиться

- BJT Switching CircuitsДокумент48 страницBJT Switching CircuitsMohammad Gulam AhamadОценок пока нет

- Lecture07 Capacitance ResistanceДокумент44 страницыLecture07 Capacitance ResistanceMd MianОценок пока нет

- Parte2 Clase04 ADC DCAДокумент56 страницParte2 Clase04 ADC DCABala KrishnaОценок пока нет

- Parte2 - Clase03 - Analog View of Digital SignalsДокумент63 страницыParte2 - Clase03 - Analog View of Digital SignalsBala KrishnaОценок пока нет

- Lecture 5 - Gate-Level LayoutДокумент23 страницыLecture 5 - Gate-Level LayoutspvenuОценок пока нет

- Lecture10 Power ConsumptionДокумент14 страницLecture10 Power ConsumptionBala KrishnaОценок пока нет

- Lecture13 AddersДокумент48 страницLecture13 Addersnguyenbinh12xОценок пока нет

- MultiplicationДокумент15 страницMultiplicationTi I âu PiОценок пока нет

- Lecture14 ALUДокумент26 страницLecture14 ALUBala KrishnaОценок пока нет

- Lecture09 Performance 01Документ33 страницыLecture09 Performance 01Bala KrishnaОценок пока нет

- Power Dissipation: Modified From "Digital Integrated Circuits", by J. Rabaey, A. Chandrakasan and B. NikolicДокумент14 страницPower Dissipation: Modified From "Digital Integrated Circuits", by J. Rabaey, A. Chandrakasan and B. NikolicBala KrishnaОценок пока нет

- Lecture03 Static CMOSДокумент24 страницыLecture03 Static CMOSBala KrishnaОценок пока нет

- Lecture12 DynamicДокумент22 страницыLecture12 Dynamicarun.sunaniya8701Оценок пока нет

- Lecture09 Performance 01Документ33 страницыLecture09 Performance 01Bala KrishnaОценок пока нет

- Lecture 8 - Gate-Level Delay EstimationДокумент40 страницLecture 8 - Gate-Level Delay EstimationBala KrishnaОценок пока нет

- Lecture06 LatchesДокумент30 страницLecture06 LatchesBala KrishnaОценок пока нет

- COD4 ManualДокумент18 страницCOD4 Manualfastback82Оценок пока нет

- Lecture02 InverterДокумент20 страницLecture02 InverterBala KrishnaОценок пока нет

- Software License Agreement SummaryДокумент2 страницыSoftware License Agreement SummaryChad SchroederОценок пока нет

- Win Configure Updated Title "Recommended Settings Updated"Документ2 страницыWin Configure Updated Title "Recommended Settings Updated"dams6797Оценок пока нет

- Lecture04 FabricationДокумент21 страницаLecture04 FabricationBala KrishnaОценок пока нет

- Eee CombinedДокумент89 страницEee CombinedBala KrishnaОценок пока нет

- Videocon ProjectДокумент58 страницVideocon Projectmrinal_kakkar8215100% (2)

- Win Configure Updated Title "Recommended Settings Updated"Документ2 страницыWin Configure Updated Title "Recommended Settings Updated"dams6797Оценок пока нет

- Win Configure Updated Title "Recommended Settings Updated"Документ2 страницыWin Configure Updated Title "Recommended Settings Updated"dams6797Оценок пока нет

- Linear DielctricsДокумент6 страницLinear DielctricsBala KrishnaОценок пока нет

- PCHEM1Документ3 страницыPCHEM1Bala KrishnaОценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- Advance Manufacturing Technology 26100720014Документ10 страницAdvance Manufacturing Technology 26100720014matrika adhikariОценок пока нет

- MOSFET DC Circuit AnalysisДокумент13 страницMOSFET DC Circuit AnalysisDiana AnggreaniОценок пока нет

- FinFET History and FundamentalsДокумент55 страницFinFET History and FundamentalsMurali Shanmuga Sundaram100% (2)

- CMOSDICDДокумент19 страницCMOSDICDsrihari_56657801Оценок пока нет

- BSM75GB120DLC: Technische Information / Technical InformationДокумент8 страницBSM75GB120DLC: Technische Information / Technical InformationolegОценок пока нет

- Heatwatch 3D Nand Errors and Self Recovery - Hpca18 - TalkДокумент68 страницHeatwatch 3D Nand Errors and Self Recovery - Hpca18 - TalkbilllanadeОценок пока нет

- Part Number Status Package ConfigurationДокумент9 страницPart Number Status Package ConfigurationholinsunОценок пока нет

- Lecture 1 Introduction To VLSI DesignДокумент58 страницLecture 1 Introduction To VLSI DesignHasan YeaseenОценок пока нет

- Gujarat Technological University Subject: VLSI Technology & Design Code:2161101 Topic - 3 - MOS TransistorДокумент122 страницыGujarat Technological University Subject: VLSI Technology & Design Code:2161101 Topic - 3 - MOS Transistorbakoliy218Оценок пока нет

- PROJECT1 S 2013 v2 PDFДокумент4 страницыPROJECT1 S 2013 v2 PDFHarshal SinghОценок пока нет

- Fw26025a1 T1829-1Документ4 страницыFw26025a1 T1829-1RaduОценок пока нет

- 2022-TED-Novel Step Field Plate RF LDMOS Transistor For Improved BV textDS - R textON Tradeoff and RF Performance PDFДокумент7 страниц2022-TED-Novel Step Field Plate RF LDMOS Transistor For Improved BV textDS - R textON Tradeoff and RF Performance PDFXiaole JiaОценок пока нет

- Nte 943Документ5 страницNte 943LUDWINGОценок пока нет

- Logic Gates Physical Implementation LabДокумент3 страницыLogic Gates Physical Implementation LabEdward Javier PatiñoОценок пока нет

- 25N06Документ6 страниц25N06Luismar LimaОценок пока нет

- Unit 4 - Bipolar Junction TransistorДокумент38 страницUnit 4 - Bipolar Junction TransistorCel LuviaОценок пока нет

- PRACTICAL1Документ7 страницPRACTICAL1Boy MachoОценок пока нет

- FTP11N08 B DataSheet.Документ11 страницFTP11N08 B DataSheet.Juan Cruz dafonОценок пока нет

- Logic FamilyДокумент2 страницыLogic FamilytowfiqeeeОценок пока нет

- Newsletter February 2022Документ11 страницNewsletter February 2022Gary Ryan DonovanОценок пока нет

- Practical 2.1 & 2.2 - Transistor Suis & AmplifierДокумент13 страницPractical 2.1 & 2.2 - Transistor Suis & AmplifierJamuna RaniОценок пока нет

- Applied Electronics II (Chapter 2)Документ29 страницApplied Electronics II (Chapter 2)Ermias Mesfin100% (2)

- Lecture 6 - Special Purpose Diodes - 2Документ26 страницLecture 6 - Special Purpose Diodes - 2Willian CarlosОценок пока нет

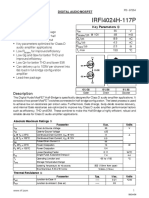

- IRFI4024H-117P: DescriptionДокумент6 страницIRFI4024H-117P: Descriptionjean grangeonОценок пока нет

- Dibl Extraction: Ssuprem 4/S-PiscesДокумент1 страницаDibl Extraction: Ssuprem 4/S-PiscesBhaskar KОценок пока нет

- The Transistor: The Invention That Changed ElectronicsДокумент58 страницThe Transistor: The Invention That Changed ElectronicsJames Rannel BayonaОценок пока нет

- Electronics For Starters 4 - Constant Current SourcesДокумент4 страницыElectronics For Starters 4 - Constant Current SourcesNuno MonteiroОценок пока нет

- LM35Документ31 страницаLM35Sandhya DeviОценок пока нет

- EC 8453 LINEAR INTEGRATED CIRCUITS Unit 1Документ16 страницEC 8453 LINEAR INTEGRATED CIRCUITS Unit 1Madhavan Sam0% (1)

- Cargador de Memorias.Документ591 страницаCargador de Memorias.Jpaul RodriguezОценок пока нет