Академический Документы

Профессиональный Документы

Культура Документы

02 HW

Загружено:

SandipChowdhury0 оценок0% нашли этот документ полезным (0 голосов)

10 просмотров6 страницCA

Оригинальное название

02_HW

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документCA

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

10 просмотров6 страниц02 HW

Загружено:

SandipChowdhuryCA

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 6

CSE 30321 Computer Architecture I Fall 2011

Homework 02 Architectural Performance Metrics 70 points

Assigned: September 6, 2011 Due: September 13, 2011

Problem 1: (15 points)

The scope of this 1

st

problem is more in-line with Lectures 02 and 03 than Lecture 04. It is included in

this problem set to re-enforce and review concepts that will be revisited throughout the semester i.e.

register transfer language, when the contents of a register or memory address change, etc.

Parts A and B both refer to the 6-instruction processor equivalent assembly shown below:

6-instruction processor assembly

# Assume R0 = 0

0: MOV R6, #7

1: MOV R1, #1

2: SUB R2, R6, R1

3: ADD R2, R2, R2

4: JUMPZ R2, E

5: SUB R11, R11, R1

6: JUMPZ R0, E

7: ADD R1, R11 R1

E:

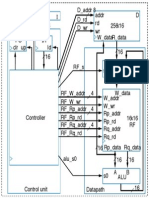

For your reference, the finite state diagram for the 6-instruciton processor is also shown below:

Part A: (9 points)

For instructions 1, 2, and 3, write out the basic register/memory transfer operations that occur during

each clock cycle. Also, for each clock cycle, provide the contents of the registers/memory locations

whose contents have changed.

An example of how to get started (for instruction 0) is included below:

Cycle Events and Register File (RF) /Memory Contents

0000 IR = I[0] ! PC ! PC + 1

0001 IR = 0x3607 (in hex) ! PC = 1

0002 Determine/calculate value to go into R6 (value will be 7)

Part B: (6 points)

During clock cycle 15, what state is the processor in? (i.e. Fetch, Decode, etc.)

Problem 2: (20 points)

Setup:

In Problem #5 of Homework #1, we considered a subset of the ARM ISA. One of the ideas discussed

in this problem was that of condition codes. More specifically, when certain instructions were

executed, bit-sized flags would be set depending upon the result that the instruction produced. For

example, consider the CMP (or compare) instruction:

- Assume that R1 = 10 and R2 = 9.

- Status flags are set based on the value produced by R1 R2.

- Thus, after CMP R1, R2 is executed:

o If GT condition is tested, the result will be TRUE, as R1 is > R2

o If GE condition is tested, the result will be TRUE, as R1 is ! R2

o If LT condition is tested, the result will be FALSE, as R1 is not < R2

o If LE condition is tested, the result will be FALSE, as R1 is not " R2

o If EQ condition is tested, the result will be FALSE, as R1 # R2

o If Mi condition is tested, the result will be FALSE, as the result is positive / not negative

" (Mi stands for minus)

o If Pl condition is tested, the result will be TRUE, as the result is positive

" (Pl stands for plus and it is TRUE if a checked value is positive OR zero)

Interestingly, when a normal ADD or SUB instruction is executed, condition codes are NOT set. For

example, if the instruction SUB R3, R4, R4 were executed, R3 would obviously contain the number 0.

However, the existing state of the EQ flag would not change.

However, another type of ADD or SUB instruction can also set condition codes in addition to performing

an add or subtract operation (as normal). For example, if the subtract instruction SUB R3, R4, R4 is

replaced with the instruction SUBS R3, R4, R4, the following would be done:

- R3 would be set to 0

- The EQ flag would we be set to TRUE

Even more interestingly, add and subtract instructions exist that are conditionally executed based on

the value of a condition code. For example, given the instruction SUBGT R3, R4, R4, the contents of

R3 would only be changed if the GT flag were TRUE (or 1) otherwise the value of R3 would remain

the same (i.e. for the case where GT is FALSE or 0).

Part A: (15 points)

In Table 2.1, I have provided two translations of the C-code shown below into ARM assembly. (One

translation uses instructions like SUBGT, and the other does not.)

Assume that EVERY instruction branches, jumps, conditional adds, etc. take 3 CCs.

Is the new code faster than the old code? If so, calculate a speedup and explain very

specifically where the speedup comes from.

C-code:

for(i=0; i<1000; i++) {

y(i) = y(i) + A*x(i);

if y(i) > 0

a = a + 1;

else

a = a 1;

}

Table 2.1

Program without conditional ALU instructions Program with conditional ALU instructions

MOV R1, R0 i maps to R1, initialize i to 0 MOV R1, R0 Same

loop CMP R1, #1000 compare R1 to the #1000,

set condition flags

loop CMP R1, #1000 Same

BGE end if i ! 1000, exit loop BGE end Same

LDR R4, [R1] load y(i) LDR R4, [R1] Same

LDR R5, [R1+1000] load x(i) LDR R5, [R1+1000] Same

MULT R5, R5, R6 (assume R6 = A)

A*x(i);

MULT R5, R5, R6 Same

ADD R4, R5, R4 y(i) + A*x(i) ADDS R4, R5, R4 Same; set code

ADDi R1, R1, #1 update counter ADDi R1, R1, #1 Same

CMP R4, R0 compare y(i) with Q SUBiMi R10, R10, #1 Set R10 only if

Mi check is true

BPl plus goto plus if y(i) > Q

(i.e. R4 > R0)

ADDiPl R10, R10, #1 Set R10 only if

Pl check is true

SUBi R10, R10, #1 otherwise, subtract 1 from a

(assume R10 = a)

B loop

B loop start loop again end

plus ADDi R10, R10, #1 add 1 to a, if condition met

(assume R10 = a)

B loop start loop again

end

Part B: (5 points)

Now, assume that condition flags are analyzed in the 2

nd

clock cycle of instruction execution as

opposed to the 3

rd

? Thus, an instruction like AddiPl only takes 2 CCs instead of 3 CCs. How does this

change your answer to Part A?

Problem 3: (15 points)

Assume that a computer has 4 different classes of instructions:

1. Floating Point (i.e. for non-integer operations)

2. Integer (i.e. for general, integer addition and subtraction)

3. Load / Store (i.e. to fetch data from memory and write data to memory)

4. Branch (i.e. jump instructions that take you to different parts of a program)

Some instructions require more work than others and may require a different number of clock cycles (or

percentage of the total program time). To make an analogy to the 6-instruction processor, you could

say that:

1. ADD/SUB represents one class of instructions (each of which takes 3 CCs to execute)

2. MOV (constant) and MOV (load/store) represents another class (and all instructions in this class

also require 3 CCs to finish)

3. JUMPZ represents a third class and may take 3 or 4 CCs to complete depending on the state

of the referenced register.

Part A: (12 points)

Assume that a given program takes 2 hours to finish. As a computer architect, you have been asked to

make this program run faster and can make 1 of 3 design decisions:

1. Improve the processor hardware to make your floating-point unit 5X faster.

2. Improve the processor hardware to make your integer unit 1.5X faster.

3. Change your processor hardware and compiler to support a new instruction that will immediately

allow data loaded from memory to be used in an arithmetic operation. With this new instruction,

the time spent executing integer instructions can be reduced by 20% and the time spent

executing load/store instructions can be reduced by 15%.

You may assume that:

o 10% of the program time is spent executing floating point instructions

o 35% of the program time is spent executing integer instructions

o 30% of the program time is spent executing load/store instructions

o 25% of the program time is spent executing branch instructions

Which option if any is best?

Part B: (3 points)

What insight does your answer to Part A provide about what type of enhancement (if any) may be best?

Problem 4: (10 points)

Note: Except for the fact that we assume the same 4 classes of instructions floating point, integer,

load/store, and branch this part of the question is unrelated to Part A and Part B.

Assume that a 2.33 GHz microprocessor is used to execute a program where the mix of instructions is

as shown in Table 4.1. The finite state diagram for this processor is also shown below.

Table 4.1: Percentage of each instruction class for program in question.

Instruction Class Floating Point Integer Load / Store Branch

% of program 10% 50% 25% 15%

fetch

Floating

Point EX 1

Floating

Point EX 2

Floating

Point EX 3

Floating

Point EX 4

Write

Register

Integer

Write

Result

Load/Store

1

Load/Store

2

Load/Store

3

Branch

(or jump)

decode

Figure: Finite state diagram for processor in question.

As before, as a computer architect, you have been asked to make this program run faster and can

make 1 of 3 design decisions:

1. Reduce the number of clock cycles required for any integer instruction from 4 to 3 but at the

expense of a 2.15 GHz clock rate for every instruction.

2. Eliminate all floating-point instructions with no change to the clock rate. The new instruction mix

is now: 60% Integer, 25% Load/Store, 15% Branch.

3. Improve the clock rate to 2.5 GHz for every instruction but at the expense of a 4-cycle branch

instruction.

Which design option if any is best?

Problem 5: (10 points)

You are currently running a program on a single core microprocessor. To improve performance, you

are contemplating buying a new 8-core microprocessor.

You would like your overall execution time to improve by 6X. How much of your original code must you

parallelize?

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5795)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- CWNA Guide To Wireless LANs, Second Edition - Ch9Документ3 страницыCWNA Guide To Wireless LANs, Second Edition - Ch9NickHenry100% (1)

- 05 HWДокумент3 страницы05 HWSandipChowdhuryОценок пока нет

- MIPS Datapath (With Exception Handling) !Документ1 страницаMIPS Datapath (With Exception Handling) !SandipChowdhuryОценок пока нет

- MIPS FSM Diagram!: Cycle 1!Документ1 страницаMIPS FSM Diagram!: Cycle 1!SandipChowdhuryОценок пока нет

- Lectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"Документ30 страницLectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"SandipChowdhuryОценок пока нет

- CSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsДокумент8 страницCSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsSandipChowdhuryОценок пока нет

- CSE 30321: Computer Architecture I: LogisticsДокумент3 страницыCSE 30321: Computer Architecture I: LogisticsSandipChowdhuryОценок пока нет

- Control Unit and Datapath For 3-Instruction Processor!Документ1 страницаControl Unit and Datapath For 3-Instruction Processor!SandipChowdhuryОценок пока нет

- From: Subject: Date: To: Reply-ToДокумент1 страницаFrom: Subject: Date: To: Reply-ToSandipChowdhuryОценок пока нет

- 1HДокумент8 страниц1HSandipChowdhuryОценок пока нет

- Indice AashtoДокумент71 страницаIndice AashtoFranklinОценок пока нет

- Exchange 2003 Backup Restore & RecoveryДокумент64 страницыExchange 2003 Backup Restore & RecoveryRajeev KumarОценок пока нет

- SSD Case StudyДокумент2 страницыSSD Case StudyRuthwik S GowdaОценок пока нет

- Active Data Guard and Oracle Golden GateДокумент3 страницыActive Data Guard and Oracle Golden GateMahendranath ReddyОценок пока нет

- BSCE Building ScienceДокумент16 страницBSCE Building ScienceMayank BhatnagarОценок пока нет

- Changes in Is 1893 and Is 13920Документ61 страницаChanges in Is 1893 and Is 13920Kamarajan100% (1)

- Cve 2012 6081Документ25 страницCve 2012 6081Miguel LozanoОценок пока нет

- Feng Shui in Modern House Design Searching For The Rationale and Possible Impacts Assessment Author Gunawan Tanuwidjaja Linda OctaviaДокумент9 страницFeng Shui in Modern House Design Searching For The Rationale and Possible Impacts Assessment Author Gunawan Tanuwidjaja Linda OctaviaIuliaОценок пока нет

- OCI TerraformДокумент15 страницOCI Terraformambipac@yahoo.com100% (1)

- 1.1 Expansive SoilДокумент9 страниц1.1 Expansive SoilYatin JethiОценок пока нет

- Ik2-Bam - B2-SC-D-6503 - 02 PDFДокумент1 страницаIk2-Bam - B2-SC-D-6503 - 02 PDFkramlester1982Оценок пока нет

- Obs Admin Guide enДокумент69 страницObs Admin Guide enKlaas SlagerОценок пока нет

- Project Builder Location:: Mahaveer Rich: Mahaveer Group: Geleyara Balaga Layout, Bangalore WestДокумент6 страницProject Builder Location:: Mahaveer Rich: Mahaveer Group: Geleyara Balaga Layout, Bangalore WestVIRUPAKSHA D GoudaОценок пока нет

- BP090&120 50 HZ TechДокумент24 страницыBP090&120 50 HZ Techmauricio.vidalyork6735Оценок пока нет

- BSR 2020 ConstructionДокумент105 страницBSR 2020 ConstructionGihan KarunasingheОценок пока нет

- F25 - FGB Metro Station To Al Qouz LNDL Area 3&4 Dubai Bus Service TimetableДокумент8 страницF25 - FGB Metro Station To Al Qouz LNDL Area 3&4 Dubai Bus Service TimetableDubai Q&AОценок пока нет

- Alstom Stress 3Документ36 страницAlstom Stress 3sivaguruswamy thangaraj100% (1)

- Alcatel-Lucent 7250 SAS: Service Access Switch - Release 2.0Документ6 страницAlcatel-Lucent 7250 SAS: Service Access Switch - Release 2.0Julio C. Jordán AОценок пока нет

- Steel Tips Committee of California Parte 2Документ391 страницаSteel Tips Committee of California Parte 2RigobertoGuerraОценок пока нет

- Flexbeam ManualДокумент8 страницFlexbeam ManualAnonymous 5S5j8wOОценок пока нет

- Ferrous Metals: General Grade Cast IronsДокумент8 страницFerrous Metals: General Grade Cast IronskkamalakannaОценок пока нет

- Road Widening Review and Questionnaire-2010Документ34 страницыRoad Widening Review and Questionnaire-2010Joshua Ceniza100% (1)

- 3 4 2 A ParkinglotdesignДокумент3 страницы3 4 2 A Parkinglotdesignapi-300375532Оценок пока нет

- Answer Key: Diagnostic TestДокумент3 страницыAnswer Key: Diagnostic TestAndreia SantosОценок пока нет

- OSA Express White PaperДокумент12 страницOSA Express White PaperapmountОценок пока нет

- Sand ColumnДокумент16 страницSand ColumnZulfadli MunfazОценок пока нет

- HTML Kodları-Tr - GG - Sitene Ekle - Ana SayfaДокумент85 страницHTML Kodları-Tr - GG - Sitene Ekle - Ana SayfaKenan ÇankayaОценок пока нет

- Hilfe ZF Extranet enДокумент14 страницHilfe ZF Extranet enDejan StevanovicОценок пока нет