Академический Документы

Профессиональный Документы

Культура Документы

03 PPT 4up

Загружено:

SandipChowdhuryОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

03 PPT 4up

Загружено:

SandipChowdhuryАвторское право:

Доступные форматы

Lectures 02, 03

Introduction to Stored Programs

Suggested reading:

HP Chapters 1.1-1.3

1

Copyright 2007 Frank Vahid

Instructors of courses requiring Vahid's Digital Design textbook (published by John Wiley and Sons) have permission to modify and use these slides for customary course-related activities,

subject to keeping this copyright notice in place and unmodified. These slides may be posted as unanimated pdf versions on publicly-accessible course websites.. PowerPoint source (or pdf

with animations) may not be posted to publicly-accessible websites, but may be posted for students on internal protected sites or distributed directly to students by other electronic means.

Instructors may make printouts of the slides available to students for a reasonable photocopying charge, without incurring royalties. Any other use requires explicit permission. Instructors

may obtain PowerPoint source or obtain special use permissions from Wiley see http://www.ddvahid.com for information.

Some slides/images from Vahid text hence this notice:

2

Processor components

vs.

Processor comparison

University of Notre Dame

CSE 30321 - Lecture 01 - Introduction to CSE 30321 44

vs.

for i=0; i<5; i++ {

a = (a*b) + c;

}

MULT r1,r2,r3 # r1 ! r2*r3

ADD r2,r1,r4 # r2 ! r1+r4

110011 000001 000010 000011

001110 000010 000001 000100

or

HLL code translation

The right HW for the

right application

Writing more

efcient code

Multicore processors

and programming

CSE 30321

Fundamental lesson(s)

How code you write (compiled C for example) is

ultimately run on HW.

3

Why its important

You'll learn what your microprocessor actually does

when you compile and execute code written in a HLL.

Equally important, at the heart of this discussion is the

"stored program model.

This is a fundamental idea that we'll discuss over the

entire semester and many things build off of it.

4

Board Discussion #1:

Introduction to stored programs

5

A

6

Board discussion summary:

Stored program model has been around for a long time...

Program memory

Data Memory

Program

counter

(index)

Processing Logic

Board discussion summary:

7

for i=0; i<5; i++ {

a = (a*b) + c;

}

A hypothetical translation:

MULT temp,a,b # temp ! a*b

MULT r1,r2,r3 # r1 ! r2*r3

ADD a,temp,c # a ! temp+c

ADD r2,r1,r4 # r2 ! r1+r4

Can dene codes for MULT and ADD

Assume MULT = 110011 & ADD = 001110

stored

program

becomes

PC 110011 000001 000010 000011

PC+1 001110 000010 000001 000100

A simple Von Neumann architecture

Von Neumann architecture synonymous

with programmable processor

Processing generally consists of:

Loading some data

Transforming that data

Storing that data

Datapath: core of a programmable processor

Can read/write data memory

Has register le to hold subsets of memory

(in a local, fast memory)

Has ALU to transform local data

8

D a ta memo ry D

n-bit

2x 1

R e g is ter le RF

A L U

Datapath

Connected to

other, peripheral

HW

Basic datapath operations

Load: load data from data memory to RF

ALU operation: transforms data by passing one or two RF values

through ALU (for ADD, SUB, AND, OR, etc.); data written back to RF

Store operation: stores RF register value back into data memory

Each operation can be done in one clock cycle

9

Register le RF

Data memory D

ALU

n-bit

2x 1

Register le RF

Data memory D

ALU

n-bit

2x 1

Register le RF

Data memory D

ALU

n-bit

2x 1

Load operation ALU operation Store operation B

10

The datapath control unit

D[9] = D[0] + D[1] requires a

sequence of four datapath

operations:

0: RF[0] = D[0]

1: RF[1] = D[1]

2: RF[2] = RF[0] + RF[1]

3: D[9] = RF[2]

Each operation is an instruction

Sequence of instructions program

Programmable processors

decomposing desired computations into

processor-supported operations

Store program in instruction memory

Control unit reads each instruction and

executes it on the datapath

PC: Program counter address of

current instruction

IR: Instruction register current

instruction

Register le RF

Data memory D

ALU

n-bit

2 x 1

Datapath

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

I

Control unit

Instruction memory

PC IR

Controller

Foreshadowing:

What if we want ALU to add, subtract?

How do we tell it what to do?

The datapath control unit

To carry out each instruction, the control unit must:

Fetch Read instruction from instruction memory

Decode Determine the operation and operands of the instruction

Execute Carry out the instruction's operation using the datapath

11

RF[0]=D[0]

0 > 1

R[0]: ?? " 99

"load"

Instruction memory I

Control unit

Controller

PC I R

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

( a )

Fetch

RF[0]=D[0]

Instruction memory I

Control unit

PC I R

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

1

( b )

Controller

Decode

Register le RF

Data memory D

D[0]: 99

ALU

n-bit

2 x 1

Datapath

Instruction memory I

Control unit

Controller

PC I R

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

RF[0]=D[0]

1

( c )

Execute

12

The datapath control unit

RF[1]=D[1}

1 > 2

R[1]: ?? " 102

"load"

Instruction memory I

Control unit

Controller

PC I R

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

( a )

Fetch

RF[1]=D[1]

Instruction memory I

Control unit

PC I R

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

2

( b )

Controller

Decode

Register le RF

Data memory D

D[1]: 102

ALU

n-bit

2 x 1

Datapath

Instruction memory I

Control unit

Controller

PC I R

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

RF[1]=D[1]

2

( c )

Execute

To carry out each instruction, the control unit must:

Fetch Read instruction from instruction memory

Decode Determine the operation and operands of the instruction

Execute Carry out the instruction's operation using the datapath

Instruction Set List of allowable instructions and their

representation in memory, e.g.,

Load instruction0000 r

3

r

2

r

1

r

0

d

7

d

6

d

5

d

4

d

3

d

2

d

1

d

0

Store instruction0001 r

3

r

2

r

1

r

0

d

7

d

6

d

5

d

4

d

3

d

2

d

1

d

0

Add instruction 0010 ra

3

ra

2

ra

1

ra

0

rb

3

rb

2

rb

1

rb

0

rc

3

rc

2

rc

1

rc

0

13

Datapath + control =

Instruction memory I

0: 0000 0000 00000000

1: 0000 0001 00000001

2: 0010 0010 0000 0001

3: 0001 0010 00001001

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

Desired program

operands

Instructions in 0s and 1s

machine code

opcode

Instruction is an idea that

helps abstract 1s, 0s, but

still provides info. about HW

What does this tell you

about data memory?

What does this tell us about

the register le?

3-instruction

programmable processor

Toward a more detailed, realistic datapath

To design the processor, we can begin with a high-level

state machine description of the processor's behavior

Control unit manages instruction fetch, ow through

datapath HW

14

Decode

Fetch

Init

PC=0

IR=I[PC]

PC=PC+1

Load

RF[ra]=D[d]

op=0000

Store Add

RF[ra] =

RF[rb]+ RF[rc]

D[d]=RF[ra]

op=0001 op=0010

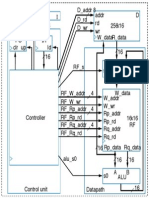

Toward a more detailed, realistic datapath

Now, create detailed connections among components

15

Fetch

Decode

Init

PC=0

Store

IR=I[PC]

PC=PC+1

Load Add

RF[ra] =

RF[rb]+

RF[rc]

D[d]=RF[ra] RF[ra]=D[d]

op=0000 op=0001 op=0010

Datapath

D

D_addr 8

D_rd

D_wr

addr

rd

wr

256 x 16

16 x 16

RF

16-bit

2 x 1

W_data R_data

Rp_data Rq_data

W_data

W_addr

W_wr

Rp_addr

Rp_rd

Rq_addr

Rq_rd

0

16

16

16

16 16

16

RF_s

s

1

A B

alu_s0

s0

ALU

RF_W_wr

RF_Rp_addr

RF_Rq_addr

RF_Rq_rd

RF_Rp_rd

RF_W_addr 4

4

4

PC

clr up

16

I R

Id

16

16

I data rd addr

Controller

Control unit

Register le RF

Data memory D

ALU

n-bit

2x 1

Before

Toward a more detailed, realistic datapath

Convert high-level state machine description of entire

processor to FSM description of controller

Use datapath and other components to achieve same

behavior

16

Fetch

Decode

Init

PC=0

Store

IR=I[PC]

PC=PC+1

Load Add

RF[ra] =

RF[rb]+

RF[rc]

D[d]=RF[ra] RF[ra]=D[d]

op=0000 op=0001 op=0010

PC

clr up

16

I R

Id

16

16

I data rd addr

Controller

Control unit Datapath

RF_W_wr

RF_Rp_addr

RF_Rq_addr

RF_Rq_rd

RF_Rp_rd

RF_W_addr

D_addr 8

D_rd

D_wr

RF_s

alu_s0

addr D

rd

wr

256 x 16

16 x 16

RF

16-bit

2 x 1

W_data R_data

Rp_data Rq_data

W_data

W_addr

W_wr

Rp_addr

Rp_rd

Rq_addr

Rq_rd

0

16

16

16

16 16

16

s

1

A B

s0 ALU

4

4

4

Fetch

Decode

Init

PC=0

PC_ clr=1

Store

I R= I [PC] PC=PC+1

I _rd=1 PC_inc=1

I R_ld=1

Load Add

RF[ra] = RF[rb]+

RF[rc]

D[d]=RF[ra] RF[ra]=D[d]

op=0000 op=0001 op=0010

D_addr=d

D_wr=1

RF_s=X

RF_Rp_addr=ra

RF_Rp_rd=1

RF_Rp_addr=rb

RF_Rp_rd=1

RF_s=0

RF_Rq_addr=rc

RF_Rq _rd=1

RF_W_addr=ra

RF_W_wr=1

alu_s0=1

D_addr=d

D_rd=1

RF_s=1

RF_W_addr=ra

RF_W_wr=1

C

17

Q1: D[8] = D[8] + RF[1] + RF[4]

I[15]: Add R2, R1, R4 RF[1] = 4

I[16]: MOV R3, 8 RF[4] = 5

I[17]: Add R2, R2, R3 D[8] = 7

(n+1)

Fetch

PC=15

IR=xxxx

(n+2)

Decode

PC=16

IR=2214h

(n+3)

Execute

PC=16

IR=2214h

RF[2]=

xxxxh

(n+4)

Fetch

PC=16

IR=2214h

RF[2]=

0009h

(n+5)

Decode

PC=17

IR=0308h

(n+6)

Execute

PC=17

IR=0308h

RF[3]=

xxxxh

CLK

(n+7)

Fetch

PC=17

IR=0308h

RF[3]=

0007h

Be sure you understand the timing! Assembly code (for 3-instruction processor)

Machine code (0s and 1s) hard to work with

Assembly code uses mnemonics

Load instructionMOV Ra, d

species the operation RF[a]=D[d].

a is # between 0 and 15

R0 means RF[0], R1 means RF[1], etc.

d is # between 0 and 255

Store instructionMOV d, Ra

species the operation D[d]=RF[a]

Add instructionADD Ra, Rb, Rc

species the operation RF[a]=RF[b]+RF[c]

18

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

Desired program

0: 0000 0000 00000000

1: 0000 0001 00000001

2: 0010 0010 0000 0001

3: 0001 0010 00001001

machine code

0: MOV R0, 0

1: MOV R1, 1

2: ADD R2, R0, R1

3: MOV 9, R2

assembly code

Important: understand the timing!

19

Will the correct instruction be fetched if PC is incremented during

the fetch cycle?

No, since PC will not be updated until the beginning of the next

cycle

While executing MOV R1, 3, what is the content of PC and IR

at the end of the 1st cycle, 2nd cycle, 3rd cycle, etc.? (assume

were at start of program)

1st cycle: PC = 0, IR = xxxx

2

nd

cycle: PC = 1, IR = I[0]

3

rd

cycle: PC = 1, IR = I[0]

What if it takes more than 1 cycle for memory read?

Cannot decode until IR is loaded

D

20

A 6-Instruction programmable processor

Let's add three more (useful) instructions:

Load-constant instruction0011 r

3

r

2

r

1

r

0

c

7

c

6

c

5

c

4

c

3

c

2

c

1

c

0

MOV Ra, #cspecies the operation RF[a]=c

Subtract instruction0100 ra

3

ra

2

ra

1

ra

0

rb

3

rb

2

rb

1

rb

0

rc

3

rc

2

rc

1

rc

0

SUB Ra, Rb, Rcspecies the operation RF[a]=RF[b] RF[c]

Jump-if-zero instruction0101 ra

3

ra

2

ra

1

ra

0

o

7

o

6

o

5

o

4

o

3

o

2

o

1

o

0

JMPZ Ra, offsetspecies the operation PC = PC + offset if RF[a]

is 0

21

Example program

Compare the contents of D[4] and D[5].

If equal, D[3] =1, otherwise set D[3]=0.

MOV R0, #1 # RF[0] = 1

MOV R1, 4 # RF[1] = D[4]

MOV R2, 5 # RF[2] = D[5]

SUB R3, R1, R2 # RF[3] = RF[1]-RF[2]

JMPZ R3, B1 # if RF[3] = 0, jump to B1

SUB R0, R0, R0 # RF[0] = 0

B1: MOV 3, R0 # D[3] = RF[0]

Program for the 6-Instruction processor

Example program:

Count number of non-zero words in D[4] and D[5]

Result will be either 0, 1, or 2

Put result in D[9]

22

E

23

Modications to 3-instruction processor

Load-constant instruction

0011 r

3

r

2

r

1

r

0

c

7

c

6

c

5

c

4

c

3

c

2

c

1

c

0

Subtract instruction

0100 ra

3

ra

2

ra

1

ra

0

rb

3

rb

2

rb

1

rb

0

rc

3

rc

2

rc

1

rc

0

Jump-if-zero instruction

0101 ra

3

ra

2

ra

1

ra

0

o

7

o

6

o

5

o

4

o

3

o

2

o

1

o

0

PC

clr up

16

I R

Id

16

16

I data rd addr

Controller

Control unit Datapath

RF_W_wr

RF_Rp_addr

RF_Rq_addr

RF_Rq_rd

RF_Rp_rd

RF_W_addr

D_addr 8

D_rd

D_wr

RF_s

alu_s0

addr D

rd

wr

256 x 16

16 x 16

RF

16-bit

2 x 1

W_data R_data

Rp_data Rq_data

W_data

W_addr

W_wr

Rp_addr

Rp_rd

Rq_addr

Rq_rd

0

16

16

16

16 16

16

s

1

A B

s0 ALU

4

4

4

Adding instructions can also mean adding hardware

24

Extending the control unit and datapath

I

Datapath

RF_Rp_addr

RF_Rq_addr

RF_Rp_zero

RF_W_addr

D_addr

D_rd

D_wr

RF_s1

RF_W_data

RF_s0

alu_s1

alu_s0

addr D

rd

wr

256 x 16

16 x 16

RF

16-bit

3 x 1

W_data R_data

Rp_data Rq_data

W_data

W_addr

W_wr

Rp_addr

Rp_rd

Rq_addr

Rq_rd

0

16

16

16

16 16

16

s1

s0

1 2

A B

s1

s0

ALU

4

4

4

=0

3a

1

8

8

1

PC

clr ld up

16

I R

Id

16

data rd addr

Controller

Control unit

a+b-1

16

+

3b

IR[7..0]

2

s1

0

0

1

s0

0

1

0

ALU operation

pass A through

A+B

A-B

F

25

Controller FSM for 6-instruction processor

Fetch

Decode

Init

PC_clr=1

Store

I _rd=1

PC_inc=1

I R_ld=1

Load Add

D_addr=d

D_wr=1

RF_s1 = X

RF_s0 = X

RF_Rp_addr=ra

RF_Rp_rd=1

RF_Rp_addr=rb

RF_Rp_rd=1

RF_s1 = 0

RF_s0 = 0

RF_Rq_add=rc

RF_Rq_rd=1

RF_W_addr_ra

RF_W_wr=1

alu_s1 = 0

alu_s0 = 1

D_addr=d

D_rd=1

RF_s1 = 0

R F _ s0 = 1

RF_W_addr=ra

RF_W_wr=1

Subtract

Load-

constant

Jump-if-zero

RF_Rp_addr=rb

RF_Rp_rd=1

RF_s1=0

RF_s0=0

RF_Rq_addr=rc

RF_Rq_rd=1

RF_W_addr=ra

RF_W_wr=1

alu_s1=1

alu_s0=0

RF_Rp_addr=ra

RF_Rp_rd=1

RF_s1=1

RF_s0=0

RF_W_addr=ra

RF_W_wr=1

Jump-if-

zero-jmp

PC_ld=1

op=0100 op=0101 op=0010 op=0011 op=0001 op=0000

R

F

_

R

p

_

z

e

r

o

R

F

_

R

p

_

z

e

r

o

'

HOW REALISTIC IS WHAT WE

JUST DISCUSSED?

26

ARM7TDMI is real, commodity processor

27

http://www.st.com/stonline/products/families/evaluation_boards/

industrial/factory_automation/motion_control/steval-ifn002v1/img/

image_steval-ifn002v1.jpg

Introduction

1-2 Copyright 2001, 2004 ARM Limited. All rights reserved. ARM DDI 0210C

1.1 About the ARM7TDMI core

The ARM7TDMI core is a member of the ARM family of general-purpose 32-bit

microprocessors. The ARM family offers high performance for very low power

consumption, and small size.

The ARM architecture is based on Reduced Instruction Set Computer (RISC)

principles. The RISC instruction set and related decode mechanism are much simpler

than those of Complex Instruction Set Computer (CISC) designs. This simplicity gives:

a high instruction throughput

an excellent real-time interrupt response

a small, cost-effective, processor macrocell.

This section describes:

The instruction pipeline

Memory access on page 1-3

Memory interface on page 1-3.

EmbeddedICE-RT logic on page 1-3.

1.1.1 The instruction pipeline

The ARM7TDMI core uses a pipeline to increase the speed of the flow of instructions

to the processor. This enables several operations to take place simultaneously, and the

processing and memory systems to operate continuously.

A three-stage pipeline is used, so instructions are executed in three stages:

Fetch

Decode

Execute.

The instruction pipeline is shown in Figure 1-1.

Figure 1-1 Instruction pipeline

Fetch

Decode

Execute

Instruction fetched from memory

Decoding of registers used in

instruction

Register(s) read from register bank

Shift and ALU operation

Write register(s) back to register bank

S

o

u

rc

e

: A

R

M

7

T

D

M

I T

e

c

h

n

ic

a

l R

e

fe

re

n

c

e

M

a

n

u

a

l

University of Notre Dame

CSE 30321 - Lecture 02-03 Stored Programs 10

Basic Architecture Control Unit

To carry out each instruction, the control unit must:

Fetch Read instruction from inst. mem.

Decode Determine the operation and operands of the instruction

Execute Carry out the instruction's operation using the datapath

RF[1]=D[1}

1 > 2

R[1]: ?? !102

"load"

Instruction memory I

Control unit

Controller

PC I R

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

( a )

Fetch

RF[1]=D[1]

Instruction memory I

Control unit

PC I R

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

2

( b )

Controller

Decode

Register le RF

Data memory D

D[1]: 102

ALU

n-bit

2 x 1

Datapath

Instruction memory I

Control unit

Controller

PC I R

0: RF[0]=D[0]

1: RF[1]=D[1]

2: RF[2]=RF[0]+RF[1]

3: D[9]=RF[2]

RF[1]=D[1]

2

( c )

Execute

Very similar to

instruction

execution stages

just discussed

ARM7TDMI is real, commodity processor

28

Introduction

ARM7TDMI Data Sheet

ARM DDI 0029E

1-5

O

p

e

n

A

c

c

e

s

s

1.4 ARM7TDMI Core Diagram

Figure 1-2: ARM7TDMI core

nRESET

nMREQ

SEQ

ABORT

nIRQ

nFIQ

nRW

LOCK

nCPI

CPA

CPB

nWAIT

MCLK

nOPC

nTRANS

Instruction

Decoder

&

Control

Logic

Instruction Pipeline

& Read Data Register

DBE D[31:0]

32-bit ALU

Barrel

Shifter

Address

Incrementer

Address Register

Register Bank

(31 x 32-bit registers)

(6 status registers)

A[31:0]

ALE

Multiplier

ABE

Write Data Register

nM[4:0]

32 x 8

nENOUT nENIN

TBE

Scan

Control

BREAKPTI

DBGRQI

nEXEC

DBGACK

ECLK

ISYNC

B

b

u

s

A

L

U

b

u

s

A

b

u

s

P

C

b

u

s

I

n

c

r

e

m

e

n

t

e

r

b

u

s

APE

BL[3:0]

MAS[1:0]

TBIT

HIGHZ

& Thumb Instruction Decoder

University of Notre Dame

CSE 30321 - Lecture 02-03 Stored Programs 15

Control unit and datapath for 3-

instruction processor

Convert high-level state machine

description of entire processor to

FSM description of controller that

uses datapath and other

components to achieve same

behavior

Fetch

Decode

Init

PC=0

Store

IR=I[PC]

PC=PC+1

Load Add

RF[ra] =

RF[rb]+

RF[rc]

D[d]=RF[ra] RF[ra]=D[d]

op=0000 op=0001 op=0010

PC

clr up

16

I R

Id

16

16

I data rd addr

Controller

Control unit Datapath

RF_W_wr

RF_Rp_addr

RF_Rq_addr

RF_Rq_rd

RF_Rp_rd

RF_W_addr

D_addr 8

D_rd

D_wr

RF_s

alu_s0

addr D

rd

wr

256 x 16

16 x 16

RF

16-bit

2 x 1

W_data R_data

Rp_data Rq_data

W_data

W_addr

W_wr

Rp_addr

Rp_rd

Rq_addr

Rq_rd

0

16

16

16

16 16

16

s

1

A B

s0 ALU

4

4

4

Fetch

Decode

Init

PC=0

PC_ clr=1

Store

I R= I [PC] PC=PC+1

I _rd=1 PC_inc=1

I R_ld=1

Load Add

RF[ra] = RF[rb]+

RF[rc]

D[d]=RF[ra] RF[ra]=D[d]

op=0000 op=0001 op=0010

D_addr=d

D_wr=1

RF_s=X

RF_Rp_addr=ra

RF_Rp_rd=1

RF_Rp_addr=rb

RF_Rp_rd=1

RF_s=0

RF_Rq_addr=rc

RF_Rq _rd=1

RF_W_addr=ra

RF_W_wr=1

alu_s0=1

D_addr=d

D_rd=1

RF_s=1

RF_W_addr=ra

RF_W_wr=1

Very similar to instruction execution stages just discussed

Where is it used?

29

Over 10 billion units shipped.

http://www.arm.com/products/processors/classic/arm7/arm7tdmi.php

B&N Nook E-Reader

Triworks BEAUTY

RF PLUS mod.

BRF1

Microsoft Xbox 360 Wireless

Steering Wheel

Ugobe Pleo

Dinosaur

Fuji xerox DocuPrint

C2090FS Colour Printer

Nokia 500 Navigation

ExaDigm

XD2100SP Mobile

Payment system

Board Discussion #5:

Wrap up, nal examples

30

G

Вам также может понравиться

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.От EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Оценок пока нет

- CSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsДокумент8 страницCSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsSandipChowdhuryОценок пока нет

- Processor Design - Chapter 8Документ27 страницProcessor Design - Chapter 8John JonesОценок пока нет

- Embedded Systems Design: A Unified Hardware/Software IntroductionДокумент8 страницEmbedded Systems Design: A Unified Hardware/Software IntroductionsarangaslОценок пока нет

- EC 101AComputerOrganizationДокумент10 страницEC 101AComputerOrganizationAkshay SinghОценок пока нет

- Chapter1 - Basic Structure of ComputersДокумент119 страницChapter1 - Basic Structure of ComputersAnkit SharmaОценок пока нет

- Arhitectura CalculatoarelorДокумент22 страницыArhitectura CalculatoarelormiryangelОценок пока нет

- 02-General Purpose ProcessorsДокумент37 страниц02-General Purpose Processorswaqar khan77Оценок пока нет

- Revision Problems ECE3073/TRC3300 Weeks 7-12Документ9 страницRevision Problems ECE3073/TRC3300 Weeks 7-12kewancamОценок пока нет

- Coa Lecture Unit 2Документ82 страницыCoa Lecture Unit 2Sumathy JayaramОценок пока нет

- System Software Question Bank 2012 With Part-B AnswersДокумент49 страницSystem Software Question Bank 2012 With Part-B Answerssumathi7975% (16)

- Revision Problems ECE3073/TRC3300 Weeks 7-12Документ10 страницRevision Problems ECE3073/TRC3300 Weeks 7-12kewancamОценок пока нет

- Computer Architecture MIPS Processor DescriptionДокумент41 страницаComputer Architecture MIPS Processor DescriptionAsif HussainОценок пока нет

- Coa 2018 SДокумент7 страницCoa 2018 S21052159Оценок пока нет

- Control UnitДокумент67 страницControl UnitnitinmgОценок пока нет

- Chapter1 Basic Structure of ComputersДокумент7 страницChapter1 Basic Structure of ComputersAhmed Sulejmanovic100% (2)

- CENG 331 Course Slides Chapter 5Документ73 страницыCENG 331 Course Slides Chapter 5Odunayo KusoroОценок пока нет

- Chapter 1 - Basic Structure of ComputersДокумент33 страницыChapter 1 - Basic Structure of Computersanusrini23Оценок пока нет

- CpuДокумент51 страницаCpujunaidalighouriОценок пока нет

- Chapter 5Документ86 страницChapter 5Muhammad OmerОценок пока нет

- Embedded Systems Design: A Unified Hardware/Software IntroductionДокумент35 страницEmbedded Systems Design: A Unified Hardware/Software IntroductionSyed AshmadОценок пока нет

- Chapter1 - Basic Structure of ComputersДокумент123 страницыChapter1 - Basic Structure of ComputersAlbert AlexОценок пока нет

- COE301 Lab 12 Single Cycle CPU DesignДокумент10 страницCOE301 Lab 12 Single Cycle CPU DesignItz Sami UddinОценок пока нет

- Chapter3 - Basic Processing UnitДокумент47 страницChapter3 - Basic Processing UnitKaruppanan KomathyОценок пока нет

- Basic Performance EquationДокумент42 страницыBasic Performance EquationVishal BasugadeОценок пока нет

- Implementation of A Verilog Multicycle CPU-FinalDraftДокумент67 страницImplementation of A Verilog Multicycle CPU-FinalDraftujjwalsОценок пока нет

- Computer Organization & Assembly Language: CS/COE0447Документ82 страницыComputer Organization & Assembly Language: CS/COE0447Danilo AlbayОценок пока нет

- Instructions and Instruction SequencingДокумент25 страницInstructions and Instruction Sequencingsamueljamespeter100% (4)

- Single Cycle Datapath PDFДокумент30 страницSingle Cycle Datapath PDFShivam KhandelwalОценок пока нет

- UNIT 1 - Basic Structure of ComputersДокумент91 страницаUNIT 1 - Basic Structure of ComputersRaul GutierrezОценок пока нет

- Execution of InstructionДокумент60 страницExecution of InstructionKr RanjithОценок пока нет

- Computer Architecture: Nguyễn Trí ThànhДокумент101 страницаComputer Architecture: Nguyễn Trí ThànhAnh Lê Huy VươngОценок пока нет

- Module 01-MicrocontrollerДокумент15 страницModule 01-MicrocontrollerRejwan TanzinОценок пока нет

- FPGA Microprocessor: ECE 428 Programmable ASIC DesignДокумент20 страницFPGA Microprocessor: ECE 428 Programmable ASIC DesignHuzur AhmedОценок пока нет

- What Is Computer and What Are Its Types?Документ5 страницWhat Is Computer and What Are Its Types?Sk ShettyОценок пока нет

- 1HДокумент8 страниц1HSandipChowdhuryОценок пока нет

- DLD Paper - 2 - SolutionДокумент20 страницDLD Paper - 2 - Solutionsinner4everyoneОценок пока нет

- 8051 CH2Документ89 страниц8051 CH2Amardeep PotdarОценок пока нет

- SicДокумент32 страницыSicMohit BhansaliОценок пока нет

- Basic Computer Organization and DesignДокумент35 страницBasic Computer Organization and DesignVinay KumarОценок пока нет

- Central Processing UnitДокумент43 страницыCentral Processing Unitmanishbhardwaj8131Оценок пока нет

- Basic Computer Organization and Design: - Computer Registers - Instruction CycleДокумент21 страницаBasic Computer Organization and Design: - Computer Registers - Instruction CycleShashank PandeyОценок пока нет

- Chapter 1. Basic Structure of ComputersДокумент119 страницChapter 1. Basic Structure of Computersvinay5716Оценок пока нет

- Assembly ProgrammingДокумент6 страницAssembly ProgrammingASKKSAОценок пока нет

- Unit IДокумент59 страницUnit IJEEVANANTHAM GОценок пока нет

- Chapter 5: Processing UnitДокумент18 страницChapter 5: Processing UnitHazwan Khalid MojamОценок пока нет

- General Purpose ProcessorsДокумент45 страницGeneral Purpose ProcessorsJacob Chako0% (1)

- Embedded Systems Design: A Unified Hardware/Software IntroductionДокумент44 страницыEmbedded Systems Design: A Unified Hardware/Software IntroductionM Rameez Ur RehmanОценок пока нет

- Chapter 2Документ14 страницChapter 2Mauricio Alejandro Pozo UribeОценок пока нет

- Introduction To Compilers: Jun.-Prof. Dr. Christian Plessl Custom Computing University of PaderbornДокумент51 страницаIntroduction To Compilers: Jun.-Prof. Dr. Christian Plessl Custom Computing University of PaderbornHariharan ElangandhiОценок пока нет

- An Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreДокумент35 страницAn Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreVasudev Rao KonjetiОценок пока нет

- Week 2Документ22 страницыWeek 2Shubhadeep GhatakОценок пока нет

- Lecture 03Документ30 страницLecture 03hamza abbasОценок пока нет

- Implementation of A 16-Bit RISC Processor Using FPGA ProgrammingДокумент25 страницImplementation of A 16-Bit RISC Processor Using FPGA ProgrammingTejashree100% (3)

- TUTORIAL 5 Datapath For R Format, I Format and J Format: For ALU, Load/store, Branch and JumpДокумент1 страницаTUTORIAL 5 Datapath For R Format, I Format and J Format: For ALU, Load/store, Branch and JumpEric LeonardoОценок пока нет

- ArchitectureДокумент5 страницArchitectureLove SharmaОценок пока нет

- Ca 2 Marks & Big Ques PDFДокумент96 страницCa 2 Marks & Big Ques PDFsathya priyaОценок пока нет

- CPU Organization Bindu AgarwallaДокумент22 страницыCPU Organization Bindu AgarwallaNobodyОценок пока нет

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkОт EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkОценок пока нет

- 04 PPT 1up PDFДокумент30 страниц04 PPT 1up PDFSandipChowdhuryОценок пока нет

- 05 HWДокумент3 страницы05 HWSandipChowdhuryОценок пока нет

- MIPS Datapath (With Exception Handling) !Документ1 страницаMIPS Datapath (With Exception Handling) !SandipChowdhuryОценок пока нет

- MIPS FSM Diagram!: Cycle 1!Документ1 страницаMIPS FSM Diagram!: Cycle 1!SandipChowdhuryОценок пока нет

- 04 PPT 4upДокумент8 страниц04 PPT 4upSandipChowdhuryОценок пока нет

- 05 BoardДокумент4 страницы05 BoardSandipChowdhuryОценок пока нет

- 03 LabДокумент8 страниц03 LabSandipChowdhuryОценок пока нет

- 04 BoardДокумент10 страниц04 BoardSandipChowdhuryОценок пока нет

- 03 HWДокумент3 страницы03 HWSandipChowdhuryОценок пока нет

- 02 LabДокумент7 страниц02 LabSandipChowdhuryОценок пока нет

- Lectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"Документ30 страницLectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"SandipChowdhuryОценок пока нет

- Comparator PDFДокумент24 страницыComparator PDFBá Anh ĐàoОценок пока нет

- 02 HWДокумент6 страниц02 HWSandipChowdhuryОценок пока нет

- 1HДокумент8 страниц1HSandipChowdhuryОценок пока нет

- CSE 30321: Computer Architecture I: LogisticsДокумент3 страницыCSE 30321: Computer Architecture I: LogisticsSandipChowdhuryОценок пока нет

- 1Документ12 страниц1SandipChowdhuryОценок пока нет

- Control Unit and Datapath For 3-Instruction Processor!Документ1 страницаControl Unit and Datapath For 3-Instruction Processor!SandipChowdhuryОценок пока нет

- 1 LabДокумент10 страниц1 LabSandipChowdhuryОценок пока нет

- From: Subject: Date: To: Reply-ToДокумент1 страницаFrom: Subject: Date: To: Reply-ToSandipChowdhuryОценок пока нет