Академический Документы

Профессиональный Документы

Культура Документы

04 PPT 1up PDF

Загружено:

SandipChowdhuryОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

04 PPT 1up PDF

Загружено:

SandipChowdhuryАвторское право:

Доступные форматы

Lectures 04

Architectural-level Performance

Metrics

Suggested reading:

(the remainder of HP Chapter 1)

1

2

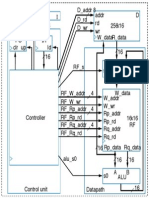

Processor components

vs.

Processor comparison

University of Notre Dame

CSE 30321 - Lecture 01 - Introduction to CSE 30321

44

vs.

for i=0; i<5; i++ {

a = (a*b) + c;

}

MULT r1,r2,r3 # r1 ! r2*r3

ADD r2,r1,r4 # r2 ! r1+r4

110011 000001 000010 000011

001110 000010 000001 000100

or

HLL code translation

The right HW for the

right application

Writing more

efcient code

Multicore processors

and programming

CSE 30321

Fundamental lesson(s)

How to quantitatively compare and contrast different

computer architectures

3

Why its important

You'll use the analysis techniques discussed today for

the rest of the semester

so in order to get a good grade in the class, you

should be sure that your comfortable with the material

If you're making / designing HW, you need to hit certain

performance metrics

If you're buying hardware, you want to make sure it

meets your software needs

i.e. you may want to achieve a certain execution time, etc.

4

5

Which is the best?

Measuring and improving performance

(if planes were computers)

6

But what about fuel efciency? Load time?

In architecture, lots of times performance (or whats

best) depends on the application

Plane People Range

(miles)

Speed

(mph)

Avg. Cost

(millions)

Passenger*Miles

$

(full range)

Passenger*Miles

$

(1500 mile trip)

737-800 162 3,060 530 63.5 7806 3826

747-8I 467 8000 633 257.5 14508 2720

777-300 368 5995 622 222 9945 2486

787-8 230 8000 630 153 12026 2254

Which is best?

737 747 777 787

7

An architecture example

1 GHz clock rate, each

instruction takes ~1.2 cycles to

execute

2 GHz clock rate, each

instruction takes ~1.8 cycles to

execute

How do we determine

which machine is better?

...

MOV R1, d(8)

Add R2, R3, R1

Sub R5, R2, R1

MOV d(9) R5

Add R4, R3, R0

...

May be a minimum performance requirement

8

I NVI TED

P A P E R

Technologies for Ultradynamic

Voltage Scaling

Circuits such as logic cells, static random access memories, analog-digital converters

and dcdc converters can be used as building blocks for applications that can

function efficiently over a wide range of supply voltages.

By Anantha P. Chandrakasan, Fellow IEEE, Denis C. Daly, Member IEEE,

Daniel Frederic Finchelstein, Member IEEE, Joyce Kwong, Student Member IEEE,

Yogesh Kumar Ramadass, Member IEEE, Mahmut Ersin Sinangil, Student Member IEEE,

Vivienne Sze, Student Member IEEE, and Naveen Verma, Member IEEE

ABSTRACT | Energy efficiency of electronic circuits is a critical

concern in a wide range of applications from mobile multi-

media to biomedical monitoring. An added challenge is that

many of these applications have dynamic workloads. To reduce

the energy consumption under these variable computation

requirements, the underlying circuits must function efficiently

over a wide range of supply voltages. This paper presents

voltage-scalable circuits such as logic cells, SRAMs, ADCs, and

dcdc converters. Using these circuits as building blocks, two

different applications are highlighted. First, we describe an

H.264/AVC video decoder that efficiently scales between

QCIF and 1080p resolutions, using a supply voltage varying

from 0.5 V to 0.85 V. Second, we describe a 0.3 V 16-bit micro-

controller with on-chip SRAM, where the supply voltage is

generated efficiently by an integrated dcdc converter.

KEYWORDS | Integrated circuits; low power; ultradynamic

voltage scaling

I. INTRODUCTION AND MOTIVATION

As we continue to target severely energy-limited applica-

tions, technology scaling, circuit topologies, and architec-

ture trends have all aligned to specifically target low-power

trade-offs through the use of fine-grained parallelism [1],

[2] and low-voltage operation [3]. Power-management has

evolved from static custom-hardware optimization to

highly dynamic run-time monitoring, assessing, and

adapting of hardware performance and energy with precise

awareness of the instantaneous application demands.

In applications such as mobile and embedded comput-

ing, dynamic voltage scaling (DVS) [4], [5] serves as an

effective means to reduce power through voltage scaling in

response to varying performance requirements. However,

a far more diverse and energy-constrained set of applica-

tions are emerging, including implanted biomedical,

remote wireless sensing, and rich mobile multimedia,

that have complex use-cases and stringent power limita-

tions. These require ultradynamic voltage scaling (UDVS),

where the range in ratio of supply-voltage to threshold-

voltage must be extended aggressively to yield orders of

magnitude in energy savings or performance increase.

In these systems, ultralow-voltage operation is required

in addition to high-speed, making scalability and reliability

the primary circuit concerns. Despite issues of variation

and leakage-currents, advanced technologies are increas-

ingly important in UDVS systems due to the elevating

instantaneous performance demands and the increasing

prevalence of energy-constraints in high-volume applica-

tions. Conventional DVS design requires moderate scal-

ability in power-delivery and circuit VDD, largely

permitting the use of standard architectures and topolo-

gies. However, UDVS design requires new logic design

Manuscript received February 18, 2009; revised August 6, 2009 and September 7,

2009. Current version published January 20, 2010. This work was funded by the

Defense Research Advanced Projects Agency (DARPA), the Focus Center for

Circuit and System Solutions (C2S2), one of five research centers funded under the

Focus Center Research Program, a Semiconductor Research Corporation program,

Nokia and Texas Instruments (TI). The work was also supported by the Intel Ph.D.

Fellowship Program, the Texas Instruments Graduate Womens Fellowship for

Leadership in Microelectronics, and Natural Sciences and Engineering Research

Council of Canada (NSERC) Fellowships. Chip fabrication was provided by

National Semiconductor and Texas Instruments.

A. P. Chandrakasan, D. C. Daly, J. Kwong, Y. K. Ramadass, M. E. Sinangil, V. Sze,

and N. Verma are with the Massachusetts Institute of Technology, Cambridge, MA

02142-1479 USA (e-mail: anantha@mit.edu; ddaly@alum.mit.edu; jyskwong@mit.edu;

ryogesh@mit.edu; sinangil@mit.edu; sze@alum.mit.edu; nverma@princeton.edu).

D. F. Finchelstein is with Nvidia, Santa Clara, CA 95050 USA

(e-mail: dfinchel@alum.mit.edu).

Digital Object Identifier: 10.1109/JPROC.2009.2033621

Vol. 98, No. 2, February 2010 | Proceedings of the IEEE 191 0018-9219/$26.00 2010 IEEE

Authorized licensed use limited to: MIT Libraries. Downloaded on January 27, 2010 at 19:25 from IEEE Xplore. Restrictions apply.

I NVI TED

P A P E R

Technologies for Ultradynamic

Voltage Scaling

Circuits such as logic cells, static random access memories, analog-digital converters

and dcdc converters can be used as building blocks for applications that can

function efficiently over a wide range of supply voltages.

By Anantha P. Chandrakasan, Fellow IEEE, Denis C. Daly, Member IEEE,

Daniel Frederic Finchelstein, Member IEEE, Joyce Kwong, Student Member IEEE,

Yogesh Kumar Ramadass, Member IEEE, Mahmut Ersin Sinangil, Student Member IEEE,

Vivienne Sze, Student Member IEEE, and Naveen Verma, Member IEEE

ABSTRACT | Energy efficiency of electronic circuits is a critical

concern in a wide range of applications from mobile multi-

media to biomedical monitoring. An added challenge is that

many of these applications have dynamic workloads. To reduce

the energy consumption under these variable computation

requirements, the underlying circuits must function efficiently

over a wide range of supply voltages. This paper presents

voltage-scalable circuits such as logic cells, SRAMs, ADCs, and

dcdc converters. Using these circuits as building blocks, two

different applications are highlighted. First, we describe an

H.264/AVC video decoder that efficiently scales between

QCIF and 1080p resolutions, using a supply voltage varying

from 0.5 V to 0.85 V. Second, we describe a 0.3 V 16-bit micro-

controller with on-chip SRAM, where the supply voltage is

generated efficiently by an integrated dcdc converter.

KEYWORDS | Integrated circuits; low power; ultradynamic

voltage scaling

I. INTRODUCTION AND MOTIVATION

As we continue to target severely energy-limited applica-

tions, technology scaling, circuit topologies, and architec-

ture trends have all aligned to specifically target low-power

trade-offs through the use of fine-grained parallelism [1],

[2] and low-voltage operation [3]. Power-management has

evolved from static custom-hardware optimization to

highly dynamic run-time monitoring, assessing, and

adapting of hardware performance and energy with precise

awareness of the instantaneous application demands.

In applications such as mobile and embedded comput-

ing, dynamic voltage scaling (DVS) [4], [5] serves as an

effective means to reduce power through voltage scaling in

response to varying performance requirements. However,

a far more diverse and energy-constrained set of applica-

tions are emerging, including implanted biomedical,

remote wireless sensing, and rich mobile multimedia,

that have complex use-cases and stringent power limita-

tions. These require ultradynamic voltage scaling (UDVS),

where the range in ratio of supply-voltage to threshold-

voltage must be extended aggressively to yield orders of

magnitude in energy savings or performance increase.

In these systems, ultralow-voltage operation is required

in addition to high-speed, making scalability and reliability

the primary circuit concerns. Despite issues of variation

and leakage-currents, advanced technologies are increas-

ingly important in UDVS systems due to the elevating

instantaneous performance demands and the increasing

prevalence of energy-constraints in high-volume applica-

tions. Conventional DVS design requires moderate scal-

ability in power-delivery and circuit VDD, largely

permitting the use of standard architectures and topolo-

gies. However, UDVS design requires new logic design

Manuscript received February 18, 2009; revised August 6, 2009 and September 7,

2009. Current version published January 20, 2010. This work was funded by the

Defense Research Advanced Projects Agency (DARPA), the Focus Center for

Circuit and System Solutions (C2S2), one of five research centers funded under the

Focus Center Research Program, a Semiconductor Research Corporation program,

Nokia and Texas Instruments (TI). The work was also supported by the Intel Ph.D.

Fellowship Program, the Texas Instruments Graduate Womens Fellowship for

Leadership in Microelectronics, and Natural Sciences and Engineering Research

Council of Canada (NSERC) Fellowships. Chip fabrication was provided by

National Semiconductor and Texas Instruments.

A. P. Chandrakasan, D. C. Daly, J. Kwong, Y. K. Ramadass, M. E. Sinangil, V. Sze,

and N. Verma are with the Massachusetts Institute of Technology, Cambridge, MA

02142-1479 USA (e-mail: anantha@mit.edu; ddaly@alum.mit.edu; jyskwong@mit.edu;

ryogesh@mit.edu; sinangil@mit.edu; sze@alum.mit.edu; nverma@princeton.edu).

D. F. Finchelstein is with Nvidia, Santa Clara, CA 95050 USA

(e-mail: dfinchel@alum.mit.edu).

Digital Object Identifier: 10.1109/JPROC.2009.2033621

Vol. 98, No. 2, February 2010 | Proceedings of the IEEE 191 0018-9219/$26.00 2010 IEEE

Authorized licensed use limited to: MIT Libraries. Downloaded on January 27, 2010 at 19:25 from IEEE Xplore. Restrictions apply.

I NVI TED

P A P E R

Technologies for Ultradynamic

Voltage Scaling

Circuits such as logic cells, static random access memories, analog-digital converters

and dcdc converters can be used as building blocks for applications that can

function efficiently over a wide range of supply voltages.

By Anantha P. Chandrakasan, Fellow IEEE, Denis C. Daly, Member IEEE,

Daniel Frederic Finchelstein, Member IEEE, Joyce Kwong, Student Member IEEE,

Yogesh Kumar Ramadass, Member IEEE, Mahmut Ersin Sinangil, Student Member IEEE,

Vivienne Sze, Student Member IEEE, and Naveen Verma, Member IEEE

ABSTRACT | Energy efficiency of electronic circuits is a critical

concern in a wide range of applications from mobile multi-

media to biomedical monitoring. An added challenge is that

many of these applications have dynamic workloads. To reduce

the energy consumption under these variable computation

requirements, the underlying circuits must function efficiently

over a wide range of supply voltages. This paper presents

voltage-scalable circuits such as logic cells, SRAMs, ADCs, and

dcdc converters. Using these circuits as building blocks, two

different applications are highlighted. First, we describe an

H.264/AVC video decoder that efficiently scales between

QCIF and 1080p resolutions, using a supply voltage varying

from 0.5 V to 0.85 V. Second, we describe a 0.3 V 16-bit micro-

controller with on-chip SRAM, where the supply voltage is

generated efficiently by an integrated dcdc converter.

KEYWORDS | Integrated circuits; low power; ultradynamic

voltage scaling

I. INTRODUCTION AND MOTIVATION

As we continue to target severely energy-limited applica-

tions, technology scaling, circuit topologies, and architec-

ture trends have all aligned to specifically target low-power

trade-offs through the use of fine-grained parallelism [1],

[2] and low-voltage operation [3]. Power-management has

evolved from static custom-hardware optimization to

highly dynamic run-time monitoring, assessing, and

adapting of hardware performance and energy with precise

awareness of the instantaneous application demands.

In applications such as mobile and embedded comput-

ing, dynamic voltage scaling (DVS) [4], [5] serves as an

effective means to reduce power through voltage scaling in

response to varying performance requirements. However,

a far more diverse and energy-constrained set of applica-

tions are emerging, including implanted biomedical,

remote wireless sensing, and rich mobile multimedia,

that have complex use-cases and stringent power limita-

tions. These require ultradynamic voltage scaling (UDVS),

where the range in ratio of supply-voltage to threshold-

voltage must be extended aggressively to yield orders of

magnitude in energy savings or performance increase.

In these systems, ultralow-voltage operation is required

in addition to high-speed, making scalability and reliability

the primary circuit concerns. Despite issues of variation

and leakage-currents, advanced technologies are increas-

ingly important in UDVS systems due to the elevating

instantaneous performance demands and the increasing

prevalence of energy-constraints in high-volume applica-

tions. Conventional DVS design requires moderate scal-

ability in power-delivery and circuit VDD, largely

permitting the use of standard architectures and topolo-

gies. However, UDVS design requires new logic design

Manuscript received February 18, 2009; revised August 6, 2009 and September 7,

2009. Current version published January 20, 2010. This work was funded by the

Defense Research Advanced Projects Agency (DARPA), the Focus Center for

Circuit and System Solutions (C2S2), one of five research centers funded under the

Focus Center Research Program, a Semiconductor Research Corporation program,

Nokia and Texas Instruments (TI). The work was also supported by the Intel Ph.D.

Fellowship Program, the Texas Instruments Graduate Womens Fellowship for

Leadership in Microelectronics, and Natural Sciences and Engineering Research

Council of Canada (NSERC) Fellowships. Chip fabrication was provided by

National Semiconductor and Texas Instruments.

A. P. Chandrakasan, D. C. Daly, J. Kwong, Y. K. Ramadass, M. E. Sinangil, V. Sze,

and N. Verma are with the Massachusetts Institute of Technology, Cambridge, MA

02142-1479 USA (e-mail: anantha@mit.edu; ddaly@alum.mit.edu; jyskwong@mit.edu;

ryogesh@mit.edu; sinangil@mit.edu; sze@alum.mit.edu; nverma@princeton.edu).

D. F. Finchelstein is with Nvidia, Santa Clara, CA 95050 USA

(e-mail: dfinchel@alum.mit.edu).

Digital Object Identifier: 10.1109/JPROC.2009.2033621

Vol. 98, No. 2, February 2010 | Proceedings of the IEEE 191 0018-9219/$26.00 2010 IEEE

Authorized licensed use limited to: MIT Libraries. Downloaded on January 27, 2010 at 19:25 from IEEE Xplore. Restrictions apply.

methodologies, new circuit topologies, and more aggres-

sive use of parallelism in order to ensure reliability over a

wide operating range. The necessary approach combines

balanced circuit optimization considering device trade-offs

over an extreme biasing range; application of specialized

processing algorithms and architectures to broadly exploit

parallelism; and reconfigurable hardware to selectively

improve the power-performance trade-offs of the circuits

in response to the target operating point.

We introduce the challenges of UDVS systems more

concretely in the video decoding and biomedical monitor-

ing applications described below. In the remainder of the

paper, specific circuit components and techniques neces-

sary to enable UDVS systems are considered starting with

digital logic design and SRAMs. Subsequently, the

practical and essential issue of efficient power delivery

over an extreme range is considered. Then, the integration

of highly scalable analog circuits is presented, and finally,

the system applications are considered in detail.

A. Video Decoding

In video decoding, the frame rate and resolution of the

playback video dictates the performance requirement of

the video decoder hardware. Over the past years, video has

become increasingly ubiquitous due to the reduction in

storage and transmission costs. The number of different

types of video content has been growing rapidly ranging

from professional cinema to news reports to, most

recently, user-generated content. In addition, the numer-

ous modes of transmission of the video have also expanded

from broadcast and playback of local storage material (e.g.,

DVD), to streaming across the internet and cellular

network. Both of these factors cause the frame rate and

resolution of todays video content to vary widely. Fig. 1

shows the resolutions and frame rates for different

applications and their corresponding performance require-

ment (in terms of pixels/s). For instance, high definition

(e.g., 720 or 1080 HD) is used for playback of movies and

broadcast television on a high resolution monitor. A higher

frame rate [e.g., 60 or 120 frames per second (fps)] is used

for high-action sports. Video conferencing and streaming

media can be done at lower resolutions (e.g., CIF or VGA)

and frame rates (e.g., 15 or 30 fps) for display on a phone.

Accordingly, the current state of the art video coding

standard H.264/AVC [7] was designed to support a wide

range of resolutions and frame rates as seen in Fig. 1.

H.264/AVC supports videos from QCIF (176 144) at

15 fps [380 kpixels/s] up to 4 k 2 k (4096 2048)

at 30 fps [252 Mpixels/s]; the performance require-

ment for 4 k 2 k at 30 fps is 662 greater than

QCIF at 15 fps. It is likely that in the next-generation

standards [8], [9], both the lower and upper bound of

this range will be increased supporting QVGA (320

240) at 24 fps [1.92 Mpixels/s] up to 4 k 2 k (4096

2048) at 120 fps [1 Gpixels/s], which covers a performance

range of more than 500. In addition to resolution and

frame rate, workload variation can occur frame-to-frame

depending on the form of compression used. A highly

scalable video decoder is needed to support the wide

variety of H.264/AVC sequences.

The use of video playback on handheld battery-operated

devices is increasingly common. It is expected that a video

decoder on a cellphone can playback different types of

video under various use cases. For instance, it should be

able to playback low to medium resolution/frame rate

videos locally on the phone that perhaps were transmitted

over a lowbandwidth network; with the growing popularity

of video capture on a cellphone, it may also be convenient

to be able to connect the phone to a monitor for playback of

high resolution and fast frame rate sequences. Having a

single video decoder ASIC, which is scalable and supports

all these applications, is convenient and cost effective.

Fig. 1. Performance requirements for various applications based on frame rate and resolution [6]. Yellow dashed line shows

limit of H.264/AVC standard. Next-generation standard is expected to reach above this line.

Chandrakasan et al. : Technologies for Ultradynami c Voltage Scaling

192 Proceedings of the IEEE | Vol. 98, No. 2, February 2010

Authorized licensed use limited to: MIT Libraries. Downloaded on January 27, 2010 at 19:25 from IEEE Xplore. Restrictions apply.

Power and energy are important too

9

I NVI TED

P A P E R

Technologies for Ultradynamic

Voltage Scaling

Circuits such as logic cells, static random access memories, analog-digital converters

and dcdc converters can be used as building blocks for applications that can

function efficiently over a wide range of supply voltages.

By Anantha P. Chandrakasan, Fellow IEEE, Denis C. Daly, Member IEEE,

Daniel Frederic Finchelstein, Member IEEE, Joyce Kwong, Student Member IEEE,

Yogesh Kumar Ramadass, Member IEEE, Mahmut Ersin Sinangil, Student Member IEEE,

Vivienne Sze, Student Member IEEE, and Naveen Verma, Member IEEE

ABSTRACT | Energy efficiency of electronic circuits is a critical

concern in a wide range of applications from mobile multi-

media to biomedical monitoring. An added challenge is that

many of these applications have dynamic workloads. To reduce

the energy consumption under these variable computation

requirements, the underlying circuits must function efficiently

over a wide range of supply voltages. This paper presents

voltage-scalable circuits such as logic cells, SRAMs, ADCs, and

dcdc converters. Using these circuits as building blocks, two

different applications are highlighted. First, we describe an

H.264/AVC video decoder that efficiently scales between

QCIF and 1080p resolutions, using a supply voltage varying

from 0.5 V to 0.85 V. Second, we describe a 0.3 V 16-bit micro-

controller with on-chip SRAM, where the supply voltage is

generated efficiently by an integrated dcdc converter.

KEYWORDS | Integrated circuits; low power; ultradynamic

voltage scaling

I. INTRODUCTION AND MOTIVATION

As we continue to target severely energy-limited applica-

tions, technology scaling, circuit topologies, and architec-

ture trends have all aligned to specifically target low-power

trade-offs through the use of fine-grained parallelism [1],

[2] and low-voltage operation [3]. Power-management has

evolved from static custom-hardware optimization to

highly dynamic run-time monitoring, assessing, and

adapting of hardware performance and energy with precise

awareness of the instantaneous application demands.

In applications such as mobile and embedded comput-

ing, dynamic voltage scaling (DVS) [4], [5] serves as an

effective means to reduce power through voltage scaling in

response to varying performance requirements. However,

a far more diverse and energy-constrained set of applica-

tions are emerging, including implanted biomedical,

remote wireless sensing, and rich mobile multimedia,

that have complex use-cases and stringent power limita-

tions. These require ultradynamic voltage scaling (UDVS),

where the range in ratio of supply-voltage to threshold-

voltage must be extended aggressively to yield orders of

magnitude in energy savings or performance increase.

In these systems, ultralow-voltage operation is required

in addition to high-speed, making scalability and reliability

the primary circuit concerns. Despite issues of variation

and leakage-currents, advanced technologies are increas-

ingly important in UDVS systems due to the elevating

instantaneous performance demands and the increasing

prevalence of energy-constraints in high-volume applica-

tions. Conventional DVS design requires moderate scal-

ability in power-delivery and circuit VDD, largely

permitting the use of standard architectures and topolo-

gies. However, UDVS design requires new logic design

Manuscript received February 18, 2009; revised August 6, 2009 and September 7,

2009. Current version published January 20, 2010. This work was funded by the

Defense Research Advanced Projects Agency (DARPA), the Focus Center for

Circuit and System Solutions (C2S2), one of five research centers funded under the

Focus Center Research Program, a Semiconductor Research Corporation program,

Nokia and Texas Instruments (TI). The work was also supported by the Intel Ph.D.

Fellowship Program, the Texas Instruments Graduate Womens Fellowship for

Leadership in Microelectronics, and Natural Sciences and Engineering Research

Council of Canada (NSERC) Fellowships. Chip fabrication was provided by

National Semiconductor and Texas Instruments.

A. P. Chandrakasan, D. C. Daly, J. Kwong, Y. K. Ramadass, M. E. Sinangil, V. Sze,

and N. Verma are with the Massachusetts Institute of Technology, Cambridge, MA

02142-1479 USA (e-mail: anantha@mit.edu; ddaly@alum.mit.edu; jyskwong@mit.edu;

ryogesh@mit.edu; sinangil@mit.edu; sze@alum.mit.edu; nverma@princeton.edu).

D. F. Finchelstein is with Nvidia, Santa Clara, CA 95050 USA

(e-mail: dfinchel@alum.mit.edu).

Digital Object Identifier: 10.1109/JPROC.2009.2033621

Vol. 98, No. 2, February 2010 | Proceedings of the IEEE 191 0018-9219/$26.00 2010 IEEE

Authorized licensed use limited to: MIT Libraries. Downloaded on January 27, 2010 at 19:25 from IEEE Xplore. Restrictions apply.

I NVI TED

P A P E R

Technologies for Ultradynamic

Voltage Scaling

Circuits such as logic cells, static random access memories, analog-digital converters

and dcdc converters can be used as building blocks for applications that can

function efficiently over a wide range of supply voltages.

By Anantha P. Chandrakasan, Fellow IEEE, Denis C. Daly, Member IEEE,

Daniel Frederic Finchelstein, Member IEEE, Joyce Kwong, Student Member IEEE,

Yogesh Kumar Ramadass, Member IEEE, Mahmut Ersin Sinangil, Student Member IEEE,

Vivienne Sze, Student Member IEEE, and Naveen Verma, Member IEEE

ABSTRACT | Energy efficiency of electronic circuits is a critical

concern in a wide range of applications from mobile multi-

media to biomedical monitoring. An added challenge is that

many of these applications have dynamic workloads. To reduce

the energy consumption under these variable computation

requirements, the underlying circuits must function efficiently

over a wide range of supply voltages. This paper presents

voltage-scalable circuits such as logic cells, SRAMs, ADCs, and

dcdc converters. Using these circuits as building blocks, two

different applications are highlighted. First, we describe an

H.264/AVC video decoder that efficiently scales between

QCIF and 1080p resolutions, using a supply voltage varying

from 0.5 V to 0.85 V. Second, we describe a 0.3 V 16-bit micro-

controller with on-chip SRAM, where the supply voltage is

generated efficiently by an integrated dcdc converter.

KEYWORDS | Integrated circuits; low power; ultradynamic

voltage scaling

I. INTRODUCTION AND MOTIVATION

As we continue to target severely energy-limited applica-

tions, technology scaling, circuit topologies, and architec-

ture trends have all aligned to specifically target low-power

trade-offs through the use of fine-grained parallelism [1],

[2] and low-voltage operation [3]. Power-management has

evolved from static custom-hardware optimization to

highly dynamic run-time monitoring, assessing, and

adapting of hardware performance and energy with precise

awareness of the instantaneous application demands.

In applications such as mobile and embedded comput-

ing, dynamic voltage scaling (DVS) [4], [5] serves as an

effective means to reduce power through voltage scaling in

response to varying performance requirements. However,

a far more diverse and energy-constrained set of applica-

tions are emerging, including implanted biomedical,

remote wireless sensing, and rich mobile multimedia,

that have complex use-cases and stringent power limita-

tions. These require ultradynamic voltage scaling (UDVS),

where the range in ratio of supply-voltage to threshold-

voltage must be extended aggressively to yield orders of

magnitude in energy savings or performance increase.

In these systems, ultralow-voltage operation is required

in addition to high-speed, making scalability and reliability

the primary circuit concerns. Despite issues of variation

and leakage-currents, advanced technologies are increas-

ingly important in UDVS systems due to the elevating

instantaneous performance demands and the increasing

prevalence of energy-constraints in high-volume applica-

tions. Conventional DVS design requires moderate scal-

ability in power-delivery and circuit VDD, largely

permitting the use of standard architectures and topolo-

gies. However, UDVS design requires new logic design

Manuscript received February 18, 2009; revised August 6, 2009 and September 7,

2009. Current version published January 20, 2010. This work was funded by the

Defense Research Advanced Projects Agency (DARPA), the Focus Center for

Circuit and System Solutions (C2S2), one of five research centers funded under the

Focus Center Research Program, a Semiconductor Research Corporation program,

Nokia and Texas Instruments (TI). The work was also supported by the Intel Ph.D.

Fellowship Program, the Texas Instruments Graduate Womens Fellowship for

Leadership in Microelectronics, and Natural Sciences and Engineering Research

Council of Canada (NSERC) Fellowships. Chip fabrication was provided by

National Semiconductor and Texas Instruments.

A. P. Chandrakasan, D. C. Daly, J. Kwong, Y. K. Ramadass, M. E. Sinangil, V. Sze,

and N. Verma are with the Massachusetts Institute of Technology, Cambridge, MA

02142-1479 USA (e-mail: anantha@mit.edu; ddaly@alum.mit.edu; jyskwong@mit.edu;

ryogesh@mit.edu; sinangil@mit.edu; sze@alum.mit.edu; nverma@princeton.edu).

D. F. Finchelstein is with Nvidia, Santa Clara, CA 95050 USA

(e-mail: dfinchel@alum.mit.edu).

Digital Object Identifier: 10.1109/JPROC.2009.2033621

Vol. 98, No. 2, February 2010 | Proceedings of the IEEE 191 0018-9219/$26.00 2010 IEEE

Authorized licensed use limited to: MIT Libraries. Downloaded on January 27, 2010 at 19:25 from IEEE Xplore. Restrictions apply.

I NVI TED

P A P E R

Technologies for Ultradynamic

Voltage Scaling

Circuits such as logic cells, static random access memories, analog-digital converters

and dcdc converters can be used as building blocks for applications that can

function efficiently over a wide range of supply voltages.

By Anantha P. Chandrakasan, Fellow IEEE, Denis C. Daly, Member IEEE,

Daniel Frederic Finchelstein, Member IEEE, Joyce Kwong, Student Member IEEE,

Yogesh Kumar Ramadass, Member IEEE, Mahmut Ersin Sinangil, Student Member IEEE,

Vivienne Sze, Student Member IEEE, and Naveen Verma, Member IEEE

ABSTRACT | Energy efficiency of electronic circuits is a critical

concern in a wide range of applications from mobile multi-

media to biomedical monitoring. An added challenge is that

many of these applications have dynamic workloads. To reduce

the energy consumption under these variable computation

requirements, the underlying circuits must function efficiently

over a wide range of supply voltages. This paper presents

voltage-scalable circuits such as logic cells, SRAMs, ADCs, and

dcdc converters. Using these circuits as building blocks, two

different applications are highlighted. First, we describe an

H.264/AVC video decoder that efficiently scales between

QCIF and 1080p resolutions, using a supply voltage varying

from 0.5 V to 0.85 V. Second, we describe a 0.3 V 16-bit micro-

controller with on-chip SRAM, where the supply voltage is

generated efficiently by an integrated dcdc converter.

KEYWORDS | Integrated circuits; low power; ultradynamic

voltage scaling

I. INTRODUCTION AND MOTIVATION

As we continue to target severely energy-limited applica-

tions, technology scaling, circuit topologies, and architec-

ture trends have all aligned to specifically target low-power

trade-offs through the use of fine-grained parallelism [1],

[2] and low-voltage operation [3]. Power-management has

evolved from static custom-hardware optimization to

highly dynamic run-time monitoring, assessing, and

adapting of hardware performance and energy with precise

awareness of the instantaneous application demands.

In applications such as mobile and embedded comput-

ing, dynamic voltage scaling (DVS) [4], [5] serves as an

effective means to reduce power through voltage scaling in

response to varying performance requirements. However,

a far more diverse and energy-constrained set of applica-

tions are emerging, including implanted biomedical,

remote wireless sensing, and rich mobile multimedia,

that have complex use-cases and stringent power limita-

tions. These require ultradynamic voltage scaling (UDVS),

where the range in ratio of supply-voltage to threshold-

voltage must be extended aggressively to yield orders of

magnitude in energy savings or performance increase.

In these systems, ultralow-voltage operation is required

in addition to high-speed, making scalability and reliability

the primary circuit concerns. Despite issues of variation

and leakage-currents, advanced technologies are increas-

ingly important in UDVS systems due to the elevating

instantaneous performance demands and the increasing

prevalence of energy-constraints in high-volume applica-

tions. Conventional DVS design requires moderate scal-

ability in power-delivery and circuit VDD, largely

permitting the use of standard architectures and topolo-

gies. However, UDVS design requires new logic design

Manuscript received February 18, 2009; revised August 6, 2009 and September 7,

2009. Current version published January 20, 2010. This work was funded by the

Defense Research Advanced Projects Agency (DARPA), the Focus Center for

Circuit and System Solutions (C2S2), one of five research centers funded under the

Focus Center Research Program, a Semiconductor Research Corporation program,

Nokia and Texas Instruments (TI). The work was also supported by the Intel Ph.D.

Fellowship Program, the Texas Instruments Graduate Womens Fellowship for

Leadership in Microelectronics, and Natural Sciences and Engineering Research

Council of Canada (NSERC) Fellowships. Chip fabrication was provided by

National Semiconductor and Texas Instruments.

A. P. Chandrakasan, D. C. Daly, J. Kwong, Y. K. Ramadass, M. E. Sinangil, V. Sze,

and N. Verma are with the Massachusetts Institute of Technology, Cambridge, MA

02142-1479 USA (e-mail: anantha@mit.edu; ddaly@alum.mit.edu; jyskwong@mit.edu;

ryogesh@mit.edu; sinangil@mit.edu; sze@alum.mit.edu; nverma@princeton.edu).

D. F. Finchelstein is with Nvidia, Santa Clara, CA 95050 USA

(e-mail: dfinchel@alum.mit.edu).

Digital Object Identifier: 10.1109/JPROC.2009.2033621

Vol. 98, No. 2, February 2010 | Proceedings of the IEEE 191 0018-9219/$26.00 2010 IEEE

Authorized licensed use limited to: MIT Libraries. Downloaded on January 27, 2010 at 19:25 from IEEE Xplore. Restrictions apply.

Consequently, it is important to minimize and scale the

power across this wide range. UDVS is an effective method

to support the more than 100 workload variation due to

video content in an energy efficient manner. Section VI-A

will describe how increased concurrency can improve

power-performance trade-off of video decoding. This

approach can also be applied to the video encoding

hardware; unlike video decoding, where the video dictates

the performance requirement, in video encoding, the user

has the ability to select the performance-power point

depending on the desired application.

B. Medical Monitoring

Likewise, UDVS enables sensor processors to support

large workload variation. Several sensor processors have

recently demonstrated voltage scalability down to the

subthreshold region [10][12]. Consider incorporating a

similar UDVS-capable processor into a platform for mobile

medical monitoring, where intelligent sensors acquire

biological signals from a subject through an analog front-

end, perform local processing, then transmit results via a

radio [13]. Since algorithms are continually evolving,

having programmability in the circuits, especially for

digital processing, is highly desirable. To extend the

operating lifetime of this entire system from a limited

energy source, a subset of vital signs can be observed in

normal situations, while more detailed monitoring and

analysis can be enabled should irregularities occur.

As an example, Fig. 2 shows three different scenarios

for monitoring cardiac activity with varying real-time

processing demands. Algorithms for each scenario were

profiled on a processor based on the MSP430 instruction

set [12], [14] with additional application-specific hard-

ware. Pulsoximetry measures the subjects blood oxygen

saturation and heart rate; the algorithm described in [15]

requires a clock frequency of 331 kHz. This is compatible

with minimum energy operation on low-voltage processors

such as [12], which achieved optimum energy/cycle at

V

DD

500 mV with the corresponding speed of 434 kHz,

as detailed in Section VI-B. At the next level of monitoring,

the subjects electrocardiogram (ECG) based on a subset of

leads is analyzed. In particular, the algorithm from [16]

extracts key features from the ECG and performs basic

arrhythmia detection. Lastly, the full set of signals in a

standard 12-lead ECG provides the highest level of detail.

Several algorithms have been developed for automated

analysis of the 12-lead ECG, as examined in [17]. In this

instance, the work in [18] is applied to extract the QT

interval and the QT dispersion, which, if abnormally

prolonged, is associated with arrhythmia, fainting, and

other adverse effects [19], [20]. Because the computations

for one lead require data from other leads, it is preferable

to consolidate the processing on a single node running at a

higher clock rate. Overall, the three scenarios outlined

here span a 78 range in performance, which can be

supported in an energy-efficient manner through UDVS.

II. ULTRALOW- VOLTAGE LOGIC DESIGN

A. Challenges and Approaches

In order to support a UDVS system, logic circuits must

be capable of operating across a wide voltage range, from

nominal V

DD

down to the minimum energy point which

optimizes the energy per operation. This optimum point

typically lies in the subthreshold region [21], below the

transistor threshold voltage V

t

. Although voltage scaling

within the above-threshold region is a well-known

technique [4], [22], extending this down to subthreshold

poses particular challenges due to reduced I

ON

=I

OFF

and

process variation. In subthreshold, drive current of the on

devices I

ON

is several orders of magnitude lower than in

strong inversion. Correspondingly, the ratio of active to

idle leakage currents I

ON

=I

OFF

is much reduced. In

digital logic, this implies that the idle leakage in the off

devices counteract the on devices, such that the on devices

may not pull the output of a logic gate fully to V

DD

or

ground. Moreover, local process variation can further skew

the relative strengths of transistors on the same chip,

increasing delay variability and adversely impacting

functionality of logic gates. A number of effects contribute

to local variation, including random dopant fluctuation

(RDF), line-edge roughness, and local oxide thickness

variations [23]. Effects of RDF, in which placement and

number of dopant atoms in the device channel cause

random V

t

shifts, are especially pronounced in subthresh-

old [24] since these V

t

shifts lead directly to exponential

changes in device currents. The impact on logic gate func-

tionality is illustrated in Fig. 3, by the random perturba-

tions in the voltage transfer curve (VTC) of a two-input

nand gate at 0.3 V.

To address these challenges, logic circuits in sub-V

t

should be designed to ensure sufficient I

ON

=I

OFF

in the

presence of global and local variation. For example, the

Fig. 2. Scenarios for monitoring cardiac activity with varying

real-time processing demands. For each application, locations of

electrodes/probes onthebodyare shown, as well as therequiredclock

frequency of the sensor processor. (Photos courtesy of GANFYD.)

Chandrakasan et al. : Technologies for Ultradynamic Voltage Scaling

Vol. 98, No. 2, February 2010 | Proceedings of the IEEE 193

Authorized licensed use limited to: MIT Libraries. Downloaded on January 27, 2010 at 19:25 from IEEE Xplore. Restrictions apply.

Architecture: kinda like dating

10

Attractive Available

Intelligent

Pick 2

Characterizing Performance

How can one computers performance be understood or

two computers be compared?

What factors go into achieving good performance?

Raw CPU speed?

Memory speed or bandwidth?

I/O speed or bandwidth?

The operating systems overhead?

The compiler?

Battery life?

Critical to succinctly summarize performance, and

meaningfully compare.

11

12

Common (and good) performance metrics

latency: response time, execution time

good metric for xed amount of work (minimize time)

throughput: work per unit time

= (1 / latency) when there is NO OVERLAP

> (1 / latency) when there is overlap

in real processors there is always overlap

good metric for xed amount of time (maximize work)

comparing performance

A is N times faster than B if and only if:

perf(A)/perf(B) = time(B)/time(A) = N

A is X% faster than B if and only if:

perf(A)/perf(B) = time(B)/time(A) = 1 + X/100

10 time units

Finish

each

time unit

13

Throughput vs. Latency

What is better?

A machine that always takes 1 ns to do task X 1 time

A machine that takes 15 ns to do task X 30 times...

...but 5 ns to do task X 1 time

Machine 1:

a lower latency for a single operation...

Machine 2:

better throughput for multiple operations

Whats better?

depends on what kind of computation you need to do

Take away?

Execution time and throughput are really good

performance metrics in that theyre lowest common

denominators

(i.e. if X nishes in 5 seconds and Y nishes in 10, its

hard to make the case that Y is faster!)

14

Instruction

Count

Clock Cycle

Time

15

A CPU : The Bigger Picture

We can see CPU performance dependent on:

Clock rate, CPI, and instruction count

CPU time is directly proportional to all 3:

Therefore an x % improvement in any one variable leads

to an x % improvement in CPU performance

But, everything usually affects everything:

Hardware

Technology

CPI

Organization ISAs

Compiler

Technology

A

16

IC, CPI and IPC

| | | | | | | | | | | | | | | |

time

1 2 3 4 5

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

6 7 8 9 10

Total Execution Time = 15 cycles

Instruction Count (IC) = Number of Instructions = 10

Average number of cycles per instruction (CPI) = 15/10 = 1.5

Instructions per Cycle (IPC) = 10/15 = 0.66

Can CPI < 1?

Consider the following:

17

Different Types of Instructions

Multiplication takes more time than addition

Floating point operations take longer than integer

operations

Memory accesses take more time than register accesses

NOTE:

changing the cycle time often affects the number of cycles

an instruction will take

CPU Clock Cycles

18

Question: Measurement Comparison

Given that two machines have the same ISA, which

measurement is always the same for both machines

running program P?

Clock Rate: No

CPI: No

Execution Time: No

Number of Instructions: Yes

19

The Power of Compiler

A compiler designer is trying to decide between two code

sequences for a particular machine. The machine supports

three classes of instructions: A, B, and C, which take one,

two, and three cycles (respectively):

Sequence 1 contains: 2 As, 1 B, and 2 Cs

Sequence 2 contains: 4 As, 1 B, and 1 C

Which sequence is faster? By how much? What is the CPI

of each?

B

20

Metrics

Metrics Discussed:

Execution time (instructions, cycles, seconds)

Machine throughput (programs/second)

Cycles Per Instruction (CPI)

Instructions Per Cycle (IPC)

Other Common Measures

millions of instructions per second (MIPS)

millions of oating point operations per second (MFLOPS)

MIPS =

IC

seconds x 10

6

= IPC x f

clk

(MHz)

21

Not all benchmarks are good

Example: MIPS (millions of instructions per second)

instruction count is not a reliable indicator of work

Prob #1: some optimizations add instructions

Prob #2: work per instruction varies

(FP mult >> register move)

Prob #3: ISAs not equal (3 Pentium instrs != 3 AMD instrs)

Youll see more when we talk about addressing modes

Addi vs. no Addi from Lecture 03 is a good example

Addi = 1 instruction, 3 cycles;

If no Addi, need 2 instructions and 6 CCs!

C

22

Good Benchmarks: Real Programs

real programs

(plus) only accurate way to characterize performance

(minus) requires considerable work (porting)

Standard Performance Evaluation Corporation (SPEC)

http://www.spec.org

collects, standardizes and distributes benchmark suites

consortium made up of industry leaders

SPEC CPU (CPU intensive benchmarks)

SPEC89, SPEC92, SPEC95, SPEC2000, SPEC2006

other benchmark suites

SPECjvm, SPECmail, SPECweb

Other benchmark suite examples: TPC-C, TPC-H for databases

23

SPEC CPU 2000

12 integer programs (C, C++)

gcc (compiler), perl (interpreter), vortex (database)

bzip2, gzip (compression tools), crafty (chess)

eon (rendering), gap (group theoretic enumerations)

twolf, vpr (FPGA place and route)

parser (grammar checker), mcf (network optimization)

14 oating point programs (C, FORTRAN)

swim (shallow water model), mgrid (multigrid eld solver)

applu (partial diffeqs), apsi (air pollution simulation)

wupwise (quantum chromodynamics), mesa (OpenGL library)

art (neural network image recognition),

equake (wave propagation)

fma3d (crash simulation), sixtrack (accelerator design)

lucas (primality testing), galgel (uid dynamics), ammp

(chemistry)

24

What to expect from a benchmark suite

Different programs in the suite stress different parts of

the architecture

For example:

One benchmark may be memory intensive...

...another may be compute intensive...

...another may be I/O intensive...

Ideally, show wins on all aspects

(but most often not the case which is OK)

Other suites

25

Abstract

This paper examines a set of commercially

representative embedded programs and compares them

to an existing benchmark suite, SPEC2000. A new

version of SimpleScalar that has been adapted to the

ARM instruction set is used to characterize the

performance of the benchmarks using configurations

similar to current and next generation embedded

processors. Several characteristics distinguish the

representative embedded programs from the existing

SPEC benchmarks including instruction distribution,

memory behavior, and available parallelism. The

embedded benchmarks, called MiBench, are freely

available to all researchers.

1. Introduction

Performance based design has made benchmarking

a critical part of the design process [1]. A wide variety

of benchmarks have been proposed including

Dhrystone [2], LINPACK [3], Whetstone [4], CPU2

[5], MediaBench [6] and many others. Most of these

benchmarks are targeted towards specific areas of

computation. Dhrystone, for example, is for system

(integer) performance; LINPACK is for vectorizable

computations; Whetstone and CPU2 are for numerical

(floating point) intensive applications; and

MediaBench is for multimedia applications. Other

benchmarks are available to stress network TCP/IP

stacks, data input/output and other specific tasks.

The most widely used benchmarks are the Standard

Performance Evaluation Corporation (SPEC) CPU

benchmarks [7]. They are now in their third revision

(SPEC2000). They characterize a workload for

general-purpose computers by providing a self-

contained set of programs and data divided into

separate integer and floating-point categories. The

popularity of the SPEC benchmarks as a measure of

performance has heavily influenced the design of

general-purpose microprocessors, particularly those

employed in servers and high-end desktop systems.

Among the common features of these

microarchitectures are deep pipelines, significant

instruction level parallelism, sophisticated branch

prediction schemes, and large caches.

Although this class of machines has been the chief

focus of the computer architecture community,

relatively few microprocessors are employed in this

market segment. The vast majority of microprocessors

are employed in embedded applications [8]. Although

many are just inexpensive microcontrollers, their

combined sales account for nearly half of all

microprocessor revenue. Furthermore, the embedded

application domain is the fastest growing market

segment in the microprocessor industry.

The wide range of applications makes it difficult to

characterize the embedded domain. In fact, an

embedded benchmark suite should reflect this by

emphasizing diversity. The applications range from

sensor systems on simple microcontrollers [9] to smart

cellular phones that have the functionality of a desktop

machine combined with support for wireless

communications. Perhaps the only common

denominators are: 1) that embedded processors often

require power to be considered at the same time in the

design process as performance [11]; and 2) that there is

not a significant legacy code base that would favor a

standard instruction set architecture (ISA) and

operating system, as has happened in the desktop

world. This has led to a remarkable increase in the

number of ISAs for embedded applications and this

number continues to grow.

There have been some efforts to characterize

embedded workloads, most notably the suite developed

by the EDN Embedded Microprocessor Benchmark

Consortium (EEMBC) [10]. They have recognized the

difficulty of using just one suite to characterize such a

diverse application domain and have instead produced

a set of suites that typify workloads in five embedded

markets. Unfortunately, the EEMBC benchmarks,

unlike SPEC, are not readily accessible to academic

MiBench: A free, commercially representative embedded benchmark suite

Matthew R. Guthaus, Jeffrey S. Ringenberg, Dan Ernst,

Todd M. Austin, Trevor Mudge, Richard B. Brown

{mguthaus,jringenb,ernstd,taustin,tnm,brown}@eecs.umich.edu

The University of Michigan

Electrical Engineering and Computer Science

1301 Beal Ave., Ann Arbor, MI 48109-2122

2.2. Network

The Network category represents embedded

processors in network devices like switches and

routers. The work done by these embedded processors

involves shortest path calculations, tree and table

lookups and data input/output. The algorithms used to

demonstrate the networking category are finding a

shortest path in a graph and creating and searching a

Patricia trie data structure. Some of the benchmarks in

the Security and Telecommunications category are also

relevant to the Network category: CRC32, sha, and

blowfish. However, they are separated for organization.

dijkstra: The Dijkstra benchmark constructs a large

graph in an adjacency matrix representation and then

calculates the shortest path between every pair of nodes

using repeated applications of Dijkstras algorithm.

Dijkstras algorithm is a well known solution to the

shortest path problem and completes in O(n

2

) time.

patricia: A Patricia trie is a data structure used in

place of full trees with very sparse leaf nodes.

Branches with only a single leaf are collapsed upwards

in the trie to reduce traversal time at the expense of

code complexity. Often, Patricia tries are used to

represent routing tables in network applications. The

input data for this benchmark is a list of IP traffic from

a highly active web server for a 2 hour period. The IP

numbers are disguised.

2.3. Security

Data Security is going to have increased importance

as the Internet continues to gain popularity in e-

commerce activities. Therefore, Security is given its

own category in MiBench. The Security category

includes several common algorithms for data

encryption, decryption and hashing. One algorithm,

rijndael, is the new Advanced Encryption Standard

(AES) [12]. The other representative security

algorithms are Blowfish [13], PGP [15] and SHA [14].

blowfish encrypt/decrypt: Blowfish is a symmetric

block cipher with a variable length key. It was

developed in 1993 by Bruce Schneider. Since its key

length can range from 32 to 448 bits, it is ideal for

domestic and exportable encryption. The input data

sets are a large and small ASCII text file of an article

found online.

sha: SHA is the secure hash algorithm that produces

a 160-bit message digest for a given input. It is often

used in the secure exchange of cryptographic keys and

for generating digital signatures. It is also used in the

well-known MD4 and MD5 hashing functions. The

input data sets are the same as the ones used by

blowfish.

rijndael encrypt/decrypt: Rijndael was selected as

the National Institute of Standards and Technologies

Advanced Encryption Standard (AES). It is a block

cipher with the option of 128-, 192-, and 256-bit keys

and blocks. The input data sets are the same as the ones

used by blowfish.

pgp sign/verify: Pretty Good Privacy (PGP) is a

public key encryption algorithm developed by Phil

Zimmerman. It allows you to communicate securely

with people youve never met using digital signatures

and the RSA public key cryptosystem. The input data

for both the large and small tests is a small text file.

This is because PGP is usually only used to securely

exchange a key for a block cipher which can then

encrypt/decrypt data at a much faster rate.

2.4. Consumer Devices

The Consumer Devices benchmarks are intended to

represent the many consumer devices that have grown

in popularity during recent years like scanners, digital

cameras and Personal Digital Assistants (PDAs). The

Table 1: MiBench Benchmarks

Auto./Industrial Consumer Office Network Security Telecomm.

basicmath jpeg ghostscript dijkstra blowfish enc. CRC32

bitcount lame ispell patricia blowfish dec. FFT

qsort mad rsynth (CRC32) pgp sign IFFT

susan (edges) tiff2bw sphinx (sha) pgp verify ADPCM enc.

susan (corners) tiff2rgba stringsearch (blowfish) rijndael enc. ADPCM dec.

susan (smoothing) tiffdither rijndael dec. GSM enc.

tiffmedian sha GSM dec.

typeset

6. References

[1] J.L. Hennessy and D.A. Patterson, Computer

Architecture: A Quantitative Approach, Morgan Kaufmann, San

Francisco, CA, 1996.

[2] R. Weicker and S. Nixdorf. Dhrystone, CACM, vol. 27,

num. 10, October 1984.

[3] J.J. Dongarra, J.R. Bunch, C.B. Moler and G.W. Stewart.

LINPACK Users Guide, SIAM Pub, Philadelphia, PA, 1979.

[4] H.J. Curnow and B.A. Wichmann. A Synthetic

Benchmark, The Computer Journal, vol. 19, num. 1, 1976.

[5] Digital Review. CPU2, ftp://swedishchef.lerc.nasa.gov/

drlabs/cpu.

[6] C. Lee, M. Potkonjak and H. Mangione-Smith.

MediaBench: A Tool for Evaluating and Synthesizing

Multimedia and Communications Systems, Micro-30, November

1997.

[7] B. Case. SPEC2000 Retires SPEC92, The

Microprocessor Report, vol. 9, 1995.

[8] J. Turley, Embedded Processors by the Numbers,

Embedded Systems Programming, http://www.embed-ded.com/

1999/9905/9905turley.htm, May 1999.

[9] K.L. Kraver, M.R. Guthaus, T.D. Strong, P.L. Bird, G.S.

Cha, W. Hold, R.B. Brown. A mixed-signal sensor interface

microinstrument, Sensors and Actuators A, vol. 91, pp. 266-

277, 2001.

[10] EDN Embedded Microprocessor Benchmark

Consortium, http://www.eembc.org.

[11] T. Mudge, Power: A First Class Design Constraint for

Future Architectures, IEEE Computer, April 2001, to appear.

[12] Advanced Encryption Standard, http://www.nist.gov/aes.

[13] Counterpane Internet Security, Inc. The Blowfish

Encryption Algorithm, http://www.counterpane.com/

blowfish.html, 1993.

[14] National Institute of Standards and Technology. Secure

Hash Standard, http://www.itl.nist.gov/fipspubs/fip180-1.htm,

April 1995.

[15] P.R. Zimmermann, The Official PGP Users Guide. MIT

Press, 1995.

[16] Silicon Graphics. Tiff Utilities, ftp://ftp.sgi.com/

graphics/tiff, May 1999.

[17] Aladdin Software. Aladdin Ghostscript, http://

www.cs.wisc.edu/~ghost/aladdin, April 2000.

[18] International Telecommunication Union. Global

Standard for Mobile Communication, http://www.itu.int,

February 2000.

[19] International Telecommunication Union.

Recommendation G.726 (12/90) - 40, 32, 24, 16 kbit/s Adaptive

Differential Pulse Code Modulation (ADPCM), http://

www.itu.int, December 1990.

[20] D.C. Burger and T.M. Austin. The SimpleScalar Tool

Set, Version 2.0. Technical Report CS-TR-97-1342, University

of Wisconsin-Madison, June 1997.

[21] R. Sugumar and S. Abraham. cheetah - Single-pass

simulator for direct-mapped, set-associative and fully associative

caches, Unix Manual Page, 1993.

[22] Intel Corporation, SA-110 Microprocessor Technical

Reference Manual, ftp://download.intel.com/design/strong/

applnots/27819401.pdf.

[23] Intel Corporation, The Intel XScale Microarchitecture

Technical Summary, ftp://download.intel.com/design/

intelxscale/XScaleDatasheet4.pdf.

[24] Intel Corporation, Intel StrongARM SA-110

Microprocessors Instruction Timing, ftp://download.intel.com/

design/strong/applnots/27819401.pdf.

[25] Rebel.com, NetWinder Family, http:/www.rebel.com/

netwinder.

Figure 7: Instructions per Cycle (IPC).

0

0.5

1

1.5

2

2.5

3

3.5

b

a

s

i

c

m

a

t

h

b

i

t

c

o

u

n

t

q

s

o

r

t

s

u

s

a

n

.

c

o

r

n

e

r

s

s

u

s

a

n

.

e

d

g

e

s

s

u

s

a

n

.

s

m

o

o

t

h

i

n

g

j

p

e

g

.

d

e

c

o

d

e

j

p

e

g

.

e

n

c

o

d

e

l

a

m

e

m

a

d

t

i

f

f

2

b

w

t

i

f

f

2

r

g

b

a

t

i

f

f

d

i

t

h

e

r

t

i

f

f

m

e

d

i

a

n

t

y

p

e

s

e

t

d

i

j

k

s

t

r

a

p

a

t

r

i

c

i

a

g

h

o

s

t

s

c

r

i

p

t

i

s

p

e

l

l

r

s

y

n

t

h

s

p

h

i

n

x

s

t

r

i

n

g

s

e

a

r

c

h

b

l

o

w

f

i

s

h

.

d

e

c

o

d

e

b

l

o

w

f

i

s

h

.

e

n

c

o

d

e

p

g

p

.

d

e

c

o

d

e

p

g

p

.

e

n

c

o

d

e

r

i

j

n

d

a

e

l

.

d

e

c

o

d

e

r

i

j

n

d

a

e

l

.

e

n

c

o

d

e

s

h

a

C

R

C

3

2

F

F

T

.

i

n

v

e

r

s

e

F

F

T

a

d

p

c

m

.

d

e

c

o

d

e

a

d

p

c

m

.

e

n

c

o

d

e

g

s

m

.

d

e

c

o

d

e

g

s

m

.

e

n

c

o

d

e

g

c

c

0

0

g

z

i

p

0

0

m

c

f

0

0

p

a

r

s

e

r

0

0

t

w

o

l

f

0

0

I

P

C

sa1core xscale highend

Auto Consumer Network Office Security Telecomm. SPEC2000

Some additional examples

26

D

27

Amdahls Law

Qualies performance gain

Amdahls Law dened

The performance improvement to be gained from using

some faster mode of execution is limited by the amount

of time the enhancement is actually used.

Amdahls Law denes speedup:

Speedup =

Execution time for entire task using enhancement

when possible

Execution time for entire task without enhancement

28

Amdahls Law and Speedup

Speedup tells us how much faster the machine will run

with an enhancement

2 things to consider:

1st

Fraction of the computation time in the original machine that

can use the enhancement

i.e. if a program executes in 30 seconds and 15 seconds of

exec. uses enhancement, fraction = # (always < 1)

2nd

Improvement gained by enhancement (i.e. how much faster

does the program run overall)

i.e. if enhanced task takes 3.5 seconds and original task took

7, we say the speedup is 2 (always > 1)

29

Deriving the previous formula

Speedup

overall

=

Execution Time

old

Execution Time

new

=

(1 Fraction

enhanced

) +

Fraction

enhanced

Speedup

enhanced

1

(1 Fraction

enhanced

) +

Fraction

enhanced

Speedup

enhanced

1

normalized old execution time

1 - % enhanced

(i.e. part of the task

will take the same

amount of time as

before)

% of task that will run faster

how much faster it will run

(note: # should be < 1)

(otherwise, performance gets worse)

(represents new component of ex. time)

Amdahls Law examples

30

E

Вам также может понравиться

- 05 HWДокумент3 страницы05 HWSandipChowdhuryОценок пока нет

- MIPS FSM Diagram!: Cycle 1!Документ1 страницаMIPS FSM Diagram!: Cycle 1!SandipChowdhuryОценок пока нет

- 03 HWДокумент3 страницы03 HWSandipChowdhuryОценок пока нет

- Lectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"Документ30 страницLectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"SandipChowdhuryОценок пока нет

- 05 BoardДокумент4 страницы05 BoardSandipChowdhuryОценок пока нет

- Lectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"Документ30 страницLectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"SandipChowdhuryОценок пока нет

- 04 PPT 4upДокумент8 страниц04 PPT 4upSandipChowdhuryОценок пока нет

- MIPS Datapath (With Exception Handling) !Документ1 страницаMIPS Datapath (With Exception Handling) !SandipChowdhuryОценок пока нет

- 04 BoardДокумент10 страниц04 BoardSandipChowdhuryОценок пока нет

- 02 LabДокумент7 страниц02 LabSandipChowdhuryОценок пока нет

- 02 HWДокумент6 страниц02 HWSandipChowdhuryОценок пока нет

- 03 LabДокумент8 страниц03 LabSandipChowdhuryОценок пока нет

- CSE 30321: Computer Architecture I: LogisticsДокумент3 страницыCSE 30321: Computer Architecture I: LogisticsSandipChowdhuryОценок пока нет

- CSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsДокумент8 страницCSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsSandipChowdhuryОценок пока нет

- 1 LabДокумент10 страниц1 LabSandipChowdhuryОценок пока нет

- 1Документ12 страниц1SandipChowdhuryОценок пока нет

- 1HДокумент8 страниц1HSandipChowdhuryОценок пока нет

- Notre Dame CSE 30321 Lecture 02-03 Control and DatapathДокумент1 страницаNotre Dame CSE 30321 Lecture 02-03 Control and DatapathSandipChowdhuryОценок пока нет

- From: Subject: Date: To: Reply-ToДокумент1 страницаFrom: Subject: Date: To: Reply-ToSandipChowdhuryОценок пока нет

- Comparator PDFДокумент24 страницыComparator PDFBá Anh ĐàoОценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- Auto Recloser GEДокумент36 страницAuto Recloser GERamzan QureshiОценок пока нет

- Switching Power SupplyДокумент138 страницSwitching Power SupplyStephen Dunifer95% (22)

- BE 5 UnitДокумент23 страницыBE 5 Unit08sunnyjaganОценок пока нет

- 74HC HCT4851 Q100Документ19 страниц74HC HCT4851 Q100Albaro LedesmaОценок пока нет

- AntennaДокумент8 страницAntennaKimberly Joy FerrerОценок пока нет

- 6264Документ8 страниц6264api-3711187Оценок пока нет

- P72x - EN T - C21 - V11DДокумент334 страницыP72x - EN T - C21 - V11DTlili MahmoudiОценок пока нет

- Electrical PropertiesДокумент4 страницыElectrical PropertiestusharОценок пока нет

- Department of Electronics and Electrical EngineeringДокумент3 страницыDepartment of Electronics and Electrical EngineeringbasabОценок пока нет

- 30V P-Channel MOSFET: Product Summary General DescriptionДокумент5 страниц30V P-Channel MOSFET: Product Summary General DescriptionAndrea CupelloОценок пока нет

- TP 6Документ45 страницTP 6EngrAneelKumarAkhaniОценок пока нет

- Nickel Molybdate Catalysts and Their Use in The Selective Oxidation of HydrocarbonsДокумент60 страницNickel Molybdate Catalysts and Their Use in The Selective Oxidation of HydrocarbonsSandy MartinezОценок пока нет

- Electrical-Engineering Engineering Power-Electronics Inverters NotesДокумент22 страницыElectrical-Engineering Engineering Power-Electronics Inverters NotesAbdelrahman Magdy EbrahimОценок пока нет

- 2014-Green-The Emergence of Perovskite Solar CellsДокумент10 страниц2014-Green-The Emergence of Perovskite Solar CellsChris VilaОценок пока нет

- Shilin Sc3Документ200 страницShilin Sc3Christian JacoboОценок пока нет

- Chapter07 - Electronic Analysis of CMOS Logic GatesДокумент38 страницChapter07 - Electronic Analysis of CMOS Logic GatesRenukaОценок пока нет

- Experiment SuperpositionДокумент6 страницExperiment SuperpositionShara Maica Sincioco SalvadorОценок пока нет

- ARC LS22 Schematic and PartsДокумент7 страницARC LS22 Schematic and PartsarfoceОценок пока нет

- STK621-043A-E: Air Conditioner Three-Phase Compressor Motor Driver IMST Inverter Power Hybrid ICДокумент8 страницSTK621-043A-E: Air Conditioner Three-Phase Compressor Motor Driver IMST Inverter Power Hybrid ICjicoelhoОценок пока нет

- Open Circuit Saturation Curve of An Alternator-EXPT8Документ2 страницыOpen Circuit Saturation Curve of An Alternator-EXPT8Karl Joseph Chua Villariña100% (3)

- Why Are Transformer and Alternator Ratings in KVA On ShipsДокумент18 страницWhy Are Transformer and Alternator Ratings in KVA On Shipsravi_92Оценок пока нет

- Knowles MLC Catalogue 2016Документ102 страницыKnowles MLC Catalogue 2016SalvadorОценок пока нет

- That 1246Документ8 страницThat 1246João PauloОценок пока нет

- Automobile Parking ControlДокумент4 страницыAutomobile Parking ControlHussam AlwareethОценок пока нет

- Kaneyuki Kurokawa Received A B.S. Degree in Electrical Engineering in 1951 and A Ph.D. DegreeДокумент2 страницыKaneyuki Kurokawa Received A B.S. Degree in Electrical Engineering in 1951 and A Ph.D. DegreethgnguyenОценок пока нет

- Westinghouse Ds and DSL Low Voltage Power Circuit Breakers and Cell PartsДокумент28 страницWestinghouse Ds and DSL Low Voltage Power Circuit Breakers and Cell PartsRodney PimentaОценок пока нет

- Electrical Transport MechanismsДокумент106 страницElectrical Transport MechanismslindaОценок пока нет

- Electrical Transmission and Distribution System and DesignДокумент67 страницElectrical Transmission and Distribution System and DesignAdrian Toribio100% (3)

- BJT FundamentalsДокумент33 страницыBJT FundamentalsSamreen ShabbirОценок пока нет