Академический Документы

Профессиональный Документы

Культура Документы

Lecture-42 INTEL 8255: (Programmable Peripheral Interface)

Загружено:

hemu700 оценок0% нашли этот документ полезным (0 голосов)

64 просмотров7 страницThe 8255A is a programmable I/O chip designed for use with Intel microprocessors. It contains three 8-bit ports (PORT A, PORT B, PORT C) that can be independently configured for input or output. PORT C can also be divided into two 4-bit ports. The ports are organized into two groups that can be programmed to operate in one of three modes: basic I/O, strobed I/O, or bidirectional bus mode. The 8255A interfaces the microprocessor with peripheral devices and is programmed by software to support different I/O needs.

Исходное описание:

Microprocessors-8255

Оригинальное название

8255

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документThe 8255A is a programmable I/O chip designed for use with Intel microprocessors. It contains three 8-bit ports (PORT A, PORT B, PORT C) that can be independently configured for input or output. PORT C can also be divided into two 4-bit ports. The ports are organized into two groups that can be programmed to operate in one of three modes: basic I/O, strobed I/O, or bidirectional bus mode. The 8255A interfaces the microprocessor with peripheral devices and is programmed by software to support different I/O needs.

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

64 просмотров7 страницLecture-42 INTEL 8255: (Programmable Peripheral Interface)

Загружено:

hemu70The 8255A is a programmable I/O chip designed for use with Intel microprocessors. It contains three 8-bit ports (PORT A, PORT B, PORT C) that can be independently configured for input or output. PORT C can also be divided into two 4-bit ports. The ports are organized into two groups that can be programmed to operate in one of three modes: basic I/O, strobed I/O, or bidirectional bus mode. The 8255A interfaces the microprocessor with peripheral devices and is programmed by software to support different I/O needs.

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 7

Lecture-42

INTEL 8255: (Programmable Peripheral Interface)

The 8255A is a general purpose programmable I/O device

designed for use with Intel microprocessors. It consists of three 8-bit

bidirectional I/O ports (24I/O lines) that can be configured to meet

different system I/O needs. The three ports are PORT A, PORT B &

PORT C. Port A contains one 8-bit output latch/buffer and one 8-bit

input buffer. Port B is same as PORT A or PORT B. However, PORT

C can be split into two parts PORT C lower (PC

0

-PC

3

) and PORT C

upper (PC

7

-PC

4

) by the control word. The three ports are divided in

two groups Group A (PORT A and upper PORT C) Group B (PORT B

and lower PORT C). The two groups can be programmed in three

different modes. In the first mode (mode 0), each group may be

programmed in either input mode or output mode (PORT A, PORT B,

PORT C lower, PORT C upper). In mode 1, the seconds mode, each

group may be programmed to have 8-lines of input or output (PORT

A or PORT B) of the remaining 4-lines (PORT C lower or PORT C

upper) 3-lines are used for hand shaking and interrupt control signals.

The third mode of operation (mode 2) is a bidirectional bus mode

which uses 8-line (PORT A only for a bidirectional bus and five lines

(PORT C upper 4 lines and borrowing one from other group) for

handshaking.

The 8255 is contained in a 40-pin package, whose pin out is

shown below:

The block diagram is shown below:

PIN Names

RESET Reset input

- Chip selected

- Read input

- Write input

A

0

A

1

Port Address

PA

7

PA

0

PORT A

PB

7

PB

0

PORT B

PC

7

PC

0

PORT C

VCC - +5v

GND - Ground

Functional Description:

This support chip is a general purpose I/O component to interface

peripheral equipment to the microcomputer system bus. It is

programmed by the system software so that normally no external

logic is necessary to interface peripheral devices or structures.

Data Bus Buffer:

It is a tri-state 8-bit buffer used to interface the chip to the system

data bus. Data is transmitted or received by the buffer upon execution

of input or output instructions by the CPU. Control words and status

information are also transferred through the data bus buffer. The data

lines are connected to BDB of p.

Read/Write and logic control:

The function of this block is to control the internal operation of the

device and to control the transfer of data and control or status words.

It accepts inputs from the CPU address and control buses and in turn

issues command to both the control groups.

Chip Select:

A low on this input selects the chip and enables the communication

between the 8255 A & the CPU. It is connected to the output of

address decode circuitry to select the device when it (Read). A

low on this input enables the 8255 to send the data or status

information to the CPU on the data bus.

(Write):

A low on this input pin enables the CPU to write data or control words

into the 8255 A.

A

1

, A

0

port select:

These input signals, in conjunction with the and inputs,

control the selection of one of the three ports or the control word

registers. They are normally connected to the least significant bits of

the address bus (A

0

and A

1

).

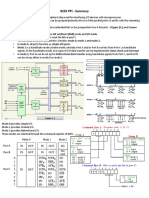

Following Table gives the basic operation,

A

1

A

0

Input operation

0 0 0 1 0 PORT A Data bus

0 1 0 1 0 PORT B Data bus

1 0 0 1 0 PORT C Data bus

0

0

1

0

0

Output operation

Data bus PORT A

0 1 1 0 0 Data bus PORT B

1 0 1 0 0 Data bus PORT C

1 1 1 0 0 Data bus control

All other states put data bus into tri-state/illegal condition.

RESET:

A high on this input pin clears the control register and all ports (A, B &

C) are initialized to input mode. This is connected to RESET OUT of

8255. This is done to prevent destruction of circuitry connected to

port lines. If port lines are initialized as output after a power up or

reset, the port might try to output into the output of a device

connected to same inputs might destroy one or both of them.

PORTs A, B and C:

The 8255A contains three 8-bit ports (A, B and C). All can be

configured in a variety of functional characteristic by the system

software.

PORTA:

One 8-bit data output latch/buffer and one 8-bit data input latch.

PORT B:

One 8-bit data output latch/buffer and one 8-bit data input buffer.

PORT C:

One 8-bit data output latch/buffer and one 8-bit data input buffer (no

latch for input). This port can be divided into two 4-bit ports under the

mode control. Each 4-bit port contains a 4-bit latch and it can be used

for the control signal outputs and status signals inputs in conjunction

with ports A and B.

Group A & Group B control:

The functional configuration of each port is programmed by the

system software. The control words outputted by the CPU configure

the associated ports of the each of the two groups. Each control block

accepts command from Read/Write content logic receives control

words from the internal data bus and issues proper commands to its

associated ports.

Control Group A Port A & Port C upper

Control Group B Port B & Port C lower

The control word register can only be written into No read operation if

the control word register is allowed.

Operation Description:

Mode selection:

There are three basic modes of operation that can be selected by the

system software.

Mode 0: Basic Input/output

Mode 1: Strobes Input/output

Mode 2: Bi-direction bus.

When the reset input goes HIGH all poets are set to mode0 as input

which means all 24 lines are in high impedance state and can be

used as normal input. After the reset is removed the 8255A remains

in the input mode with no additional initialization. During the execution

of the program any of the other modes may be selected using a

single output instruction.

The modes for PORT A & PORT B can be separately defined, while

PORT C is divided into two portions as required by the PORT A and

PORT B definitions. The ports are thus divided into two groups Group

A & Group B. All the output register, including the status flip-flop will

be reset whenever the mode is changed. Modes of the two group

may be combined for any desired I/O operation e.g. Group A in mode

1 and group B in mode 0.

The basic mode definitions with bus interface and the mode definition

format are given in fig (a) & (b),

Вам также может понравиться

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960От EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Оценок пока нет

- MPMC EEE Unit - IV Peripheral Interfacing NewДокумент41 страницаMPMC EEE Unit - IV Peripheral Interfacing NewAnonymous 4u5XkWGOОценок пока нет

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142От EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142Оценок пока нет

- Unit - 3 8255: (Programmable Peripheral Interface)Документ7 страницUnit - 3 8255: (Programmable Peripheral Interface)Praveen SinghОценок пока нет

- Unit 3 - Peripheral InterfacingДокумент56 страницUnit 3 - Peripheral InterfacingSathiyarajОценок пока нет

- Interfacing ICs - 8255Документ48 страницInterfacing ICs - 8255Adarsh AnandОценок пока нет

- 8155 Static Ram With I/O Ports and TimerДокумент59 страниц8155 Static Ram With I/O Ports and Timerchaturveditanisha17Оценок пока нет

- Programmable Peripheral Interface (8255)Документ6 страницProgrammable Peripheral Interface (8255)Sajid AkramОценок пока нет

- 8255 FunctionДокумент6 страниц8255 Functionapi-26100966Оценок пока нет

- Basics of Peripheral Devices and WorkingДокумент33 страницыBasics of Peripheral Devices and WorkingNarasimha Murthy Yayavaram100% (1)

- Processor Architecture and Interfacing: Part 13: The 8255 PPIДокумент24 страницыProcessor Architecture and Interfacing: Part 13: The 8255 PPIPalash ParmarОценок пока нет

- 8255aДокумент67 страниц8255apranavmahajan45Оценок пока нет

- 8255 Programmable Peripheral InterfaceДокумент32 страницы8255 Programmable Peripheral Interfaceshubham kumarОценок пока нет

- Micro Final TRMPPRДокумент13 страницMicro Final TRMPPRDeependra DabasОценок пока нет

- I/O Interfacing of 8086 Using 8255Документ19 страницI/O Interfacing of 8086 Using 8255SAURABH AGRAWALОценок пока нет

- 8255 and Interfacing With 8086Документ33 страницы8255 and Interfacing With 8086satyanarayana12Оценок пока нет

- Saint Louis University School of Engineering and Architecture Department of Electrical EngineeringДокумент12 страницSaint Louis University School of Engineering and Architecture Department of Electrical EngineeringNaomi Aira Gole CruzОценок пока нет

- Lecture 24 - 8255 Various Modes of OperationsДокумент16 страницLecture 24 - 8255 Various Modes of OperationsTarun SinghОценок пока нет

- 8255 Programmable Peripheral Interface: DescriptionДокумент16 страниц8255 Programmable Peripheral Interface: DescriptionSaksham GargОценок пока нет

- Programmable Peripheral InterfacingДокумент22 страницыProgrammable Peripheral InterfacingGebBerheОценок пока нет

- Programmable Interfacing Devices PDFДокумент6 страницProgrammable Interfacing Devices PDFkunalg293Оценок пока нет

- Ilovepdf MergedДокумент430 страницIlovepdf MergedYuvraj ChhabraОценок пока нет

- 8255 & IO InterfacingДокумент30 страниц8255 & IO Interfacingmoazzam hussainОценок пока нет

- 8255Документ25 страниц8255Phạm HùngОценок пока нет

- New Microsoft Word DocumentДокумент10 страницNew Microsoft Word DocumentSUDIPTA CHATTERJEEОценок пока нет

- Ec8691 - Microprocessors and Microcontrollers: Prepared by MR - Jeeva, Ap/Ece Kgisl Institute of Technology CoimbatoreДокумент116 страницEc8691 - Microprocessors and Microcontrollers: Prepared by MR - Jeeva, Ap/Ece Kgisl Institute of Technology CoimbatoreJeeva NatarajanОценок пока нет

- Instrumentation II Lab2 - 9Документ5 страницInstrumentation II Lab2 - 9Patiram YadavОценок пока нет

- 8255 Programmable Peripheral InterfaceДокумент78 страниц8255 Programmable Peripheral Interfaceedwardianirfan89% (9)

- Microprocessors 4Документ9 страницMicroprocessors 4Ajnamol N RОценок пока нет

- 8255 PpiДокумент14 страниц8255 PpiHarisankar R N R 21BRS1524Оценок пока нет

- 8255Документ34 страницы8255Manjula Bn100% (1)

- Ec8691 Unit Iii - PPTДокумент111 страницEc8691 Unit Iii - PPTVinothkumar UrumanОценок пока нет

- Unit 3Документ46 страницUnit 3Chetan GaurkarОценок пока нет

- 3 UnitДокумент18 страниц3 Unittguna21Оценок пока нет

- Features Description: CMOS Programmable Peripheral InterfaceДокумент22 страницыFeatures Description: CMOS Programmable Peripheral InterfaceNegru P. PlantatieОценок пока нет

- MPMC M4 PDFДокумент17 страницMPMC M4 PDFAjnamol N RОценок пока нет

- Unit3 MicroprocessorДокумент27 страницUnit3 MicroprocessorAshishОценок пока нет

- MP PrintДокумент64 страницыMP PrintpoonamОценок пока нет

- Programmable Perpheral InterfaceДокумент18 страницProgrammable Perpheral InterfaceBisnu SarkarОценок пока нет

- General Purpose Programmable Peripheral DevicesДокумент33 страницыGeneral Purpose Programmable Peripheral DevicesSudarshanBhardwajОценок пока нет

- Unit 4Документ177 страницUnit 4rohanrec92Оценок пока нет

- 8255 PPI-handouts To StudentsДокумент4 страницы8255 PPI-handouts To StudentsSurinder SuriОценок пока нет

- Cam Intel 8255AДокумент34 страницыCam Intel 8255AHarjot KaurОценок пока нет

- 8255 Programmable Peripheral InterfaceДокумент27 страниц8255 Programmable Peripheral InterfaceSivaprakasam KarthikeyanОценок пока нет

- 8255Документ28 страниц8255Gulam Rabbani Mohammed OsmanОценок пока нет

- Mpmcnotesunit IIIДокумент34 страницыMpmcnotesunit IIIAmy OliverОценок пока нет

- Block Diagram of 8255 WITH ExplanationДокумент8 страницBlock Diagram of 8255 WITH Explanationsenthilkumar100% (2)

- Unit II Special Purpose Programmable Peripherals and Their InterfacingДокумент10 страницUnit II Special Purpose Programmable Peripherals and Their InterfacingPraveen RathnamОценок пока нет

- 8255 AДокумент18 страниц8255 ARani MohanlalОценок пока нет

- The Programmable Peripheral Interface (8255)Документ2 страницыThe Programmable Peripheral Interface (8255)crsarinОценок пока нет

- Module 4Документ62 страницыModule 4Chippy TОценок пока нет

- On 8255 PPI by SRBДокумент41 страницаOn 8255 PPI by SRBprbehura64Оценок пока нет

- Peripheral Programmable InterfaceДокумент21 страницаPeripheral Programmable Interfaceaj3120Оценок пока нет

- Unit Iii - Interfacing Memory & Io and Applications of 8086 Microprocessor Static Memory InterfacingДокумент34 страницыUnit Iii - Interfacing Memory & Io and Applications of 8086 Microprocessor Static Memory InterfacingJay Prakash MandalОценок пока нет

- Programmable Peripheral InterfaceДокумент34 страницыProgrammable Peripheral Interfacekshirsagar_anОценок пока нет

- Datasheet 82C55Документ26 страницDatasheet 82C55Paulo VictorОценок пока нет

- 8255-Programmable Peripheral InterfaceДокумент4 страницы8255-Programmable Peripheral Interfaceskarthik.star3481Оценок пока нет

- Features Description: CMOS Programmable Peripheral InterfaceДокумент26 страницFeatures Description: CMOS Programmable Peripheral Interfaceanh_em5503Оценок пока нет

- MicroprocessorДокумент7 страницMicroprocessorSanoxОценок пока нет

- Interfacing With PeripheralsДокумент21 страницаInterfacing With PeripheralsSUDIPTA CHATTERJEEОценок пока нет

- Interview TopicsДокумент1 страницаInterview Topicshemu70Оценок пока нет

- Height GrowthДокумент4 страницыHeight Growthhemu70Оценок пока нет

- Test BankДокумент55 страницTest BankRodel D DosanoОценок пока нет

- When Mapping Your 'Result Set', Set Your 'Result Name' To '0' and 'Variable Name' To The Variable You Are UsingДокумент1 страницаWhen Mapping Your 'Result Set', Set Your 'Result Name' To '0' and 'Variable Name' To The Variable You Are Usinghemu70Оценок пока нет

- Height ExercisesДокумент2 страницыHeight Exerciseshemu70Оценок пока нет

- POTHOLE JournalДокумент5 страницPOTHOLE Journalhemu70Оценок пока нет

- (B) Data Access Tools To Be UsedДокумент1 страница(B) Data Access Tools To Be Usedhemu70Оценок пока нет

- IBM Datastage InfoДокумент1 страницаIBM Datastage Infohemu70Оценок пока нет

- 6th Central Pay Commission Salary CalculatorДокумент15 страниц6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Type Questions: True/False True FalseДокумент7 страницType Questions: True/False True Falsehemu70Оценок пока нет

- Coded InequalitiesДокумент6 страницCoded InequalitiespraveenampilliОценок пока нет

- Iidt BrochureДокумент9 страницIidt Brochurehemu70Оценок пока нет

- HX711 Avia SemiconductorДокумент9 страницHX711 Avia SemiconductorAnjar Bangsa MimpiОценок пока нет

- 07 10 PDFДокумент4 страницы07 10 PDFhemu70Оценок пока нет

- CapegeminiДокумент5 страницCapegeminihemu70Оценок пока нет

- Unit:2 4. Write in Detail About The DMA Controller.: Anup KumarДокумент2 страницыUnit:2 4. Write in Detail About The DMA Controller.: Anup Kumarhemu70Оценок пока нет

- MpegДокумент13 страницMpeghemu70Оценок пока нет

- Coded Inequality: Bank Probationary Officer Reasoning AbilityДокумент9 страницCoded Inequality: Bank Probationary Officer Reasoning AbilityAnkit SaxenaОценок пока нет

- New Microsoft Word DocumentДокумент2 страницыNew Microsoft Word Documenthemu70Оценок пока нет

- The Provision of A Sustainable Energy Supply Is One of The Most Important Issucs Facng Humanity at The Current TimeДокумент1 страницаThe Provision of A Sustainable Energy Supply Is One of The Most Important Issucs Facng Humanity at The Current Timehemu70Оценок пока нет

- Small Wireless ECG With Bluetooth™ Communication To A PDA: Mem99004@student - Mdh.seДокумент33 страницыSmall Wireless ECG With Bluetooth™ Communication To A PDA: Mem99004@student - Mdh.seIonut NeaguОценок пока нет

- Unit:2 4. Write in Detail About The DMA Controller.: Anup KumarДокумент2 страницыUnit:2 4. Write in Detail About The DMA Controller.: Anup Kumarhemu70Оценок пока нет

- UPSC Civil Services Main Examination Revised Syllabus Pattern2013Документ7 страницUPSC Civil Services Main Examination Revised Syllabus Pattern2013hemu70Оценок пока нет

- Electrocardiogram (ECG) Monitoring System Using Bluetooth TechnologyДокумент7 страницElectrocardiogram (ECG) Monitoring System Using Bluetooth TechnologyIsmanu RahadiОценок пока нет

- EM Intro Appl 1Документ29 страницEM Intro Appl 1hemu70Оценок пока нет

- Aec 2 MarksДокумент3 страницыAec 2 Markshemu70Оценок пока нет

- Direct Coupled AmplifierДокумент1 страницаDirect Coupled Amplifierhemu70Оценок пока нет

- Lecture 1Документ23 страницыLecture 1hemu70Оценок пока нет

- Measurements & InstrumentationДокумент29 страницMeasurements & Instrumentationhemu70Оценок пока нет

- VHDL ProgramsДокумент1 страницаVHDL Programshemu70Оценок пока нет

- ABBYY PDF Transformer 2Документ5 страницABBYY PDF Transformer 2sbonaffinoОценок пока нет

- Nota Pseudocode (15feb)Документ2 страницыNota Pseudocode (15feb)Nasheila Binti Abdul GaniОценок пока нет

- MPI LabДокумент4 страницыMPI LabGaurav KalraОценок пока нет

- Fatfree User ManualДокумент33 страницыFatfree User ManualLit Phen TuОценок пока нет

- SL1000 Programming Manual (Basic)Документ36 страницSL1000 Programming Manual (Basic)KatsanaArunrat57% (7)

- Prewikka User ManualДокумент15 страницPrewikka User ManualmouqriezОценок пока нет

- Anatomy of Linux Kernel Shared MemoryДокумент10 страницAnatomy of Linux Kernel Shared MemoryRotariu Dan AndreiОценок пока нет

- Forensic Ws11 12 Exercise1Документ2 страницыForensic Ws11 12 Exercise1andrian raditya rahma0% (7)

- Productflyer - 978 3 319 18841 6Документ1 страницаProductflyer - 978 3 319 18841 6Jesse BurrisОценок пока нет

- Sequence DetectorДокумент25 страницSequence DetectorYudish Nandraj KistoОценок пока нет

- 2009 Ncta Technical Papers PDFДокумент250 страниц2009 Ncta Technical Papers PDFmohitkalraОценок пока нет

- Multicore Processor ReportДокумент19 страницMulticore Processor ReportDilesh Kumar100% (1)

- Essentials of Business Communication 10th Edition Test BankДокумент11 страницEssentials of Business Communication 10th Edition Test BankCarmen40% (1)

- 3m PPT - FinalДокумент13 страниц3m PPT - FinalMaulee Desai Chainani0% (2)

- OracleEloqua Emails UserGuide PDFДокумент215 страницOracleEloqua Emails UserGuide PDFAvinash BmОценок пока нет

- Introduction To Management Science 8th Edition by Bernard W. Taylor IIIДокумент58 страницIntroduction To Management Science 8th Edition by Bernard W. Taylor IIIdsatyanegaraОценок пока нет

- The Production CycleДокумент15 страницThe Production CycleVelia MonicaОценок пока нет

- How To Interface A Microchip PIC MCU With A Hobby RC Servo, Paulo E. MerlotiДокумент18 страницHow To Interface A Microchip PIC MCU With A Hobby RC Servo, Paulo E. MerlotiMarco Medina100% (1)

- 1.optimal Design of Two-Stage Speed ReducerДокумент6 страниц1.optimal Design of Two-Stage Speed Reducermlouredocasado100% (1)

- PROGRAM - DEPED Tech4ed Center LaunchingДокумент2 страницыPROGRAM - DEPED Tech4ed Center LaunchingRick RanteОценок пока нет

- Bad Store Project 2 QuizДокумент9 страницBad Store Project 2 QuizEswar Hari Kumar100% (1)

- Matrix Data AnalysisДокумент78 страницMatrix Data AnalysisSam100% (1)

- Mateusz Grzesiukiewicz (Mateusz Grzesiukiewicz) - Hands-On Design Patterns With React Native-Packt Publishing (2018)Документ326 страницMateusz Grzesiukiewicz (Mateusz Grzesiukiewicz) - Hands-On Design Patterns With React Native-Packt Publishing (2018)hashir mahboobОценок пока нет

- ElGamal Signature SchemeДокумент3 страницыElGamal Signature SchemeJibin PrasadОценок пока нет

- Resistor Color Coding ManualДокумент8 страницResistor Color Coding ManualAbraham Jr E LagudaОценок пока нет

- Cheat Sheet Hibernate Performance Tuning PDFДокумент6 страницCheat Sheet Hibernate Performance Tuning PDFdanielisozaki100% (1)

- Loop CutsetДокумент24 страницыLoop CutsetrezaОценок пока нет

- Oracle 10g GuideДокумент582 страницыOracle 10g Guide04kalpanaОценок пока нет

- Information Flow in Pharma Supply ChainДокумент6 страницInformation Flow in Pharma Supply ChainPika ChuОценок пока нет

- Web Server COnfigurationДокумент3 страницыWeb Server COnfigurationsidd shadabОценок пока нет

- Chip War: The Quest to Dominate the World's Most Critical TechnologyОт EverandChip War: The Quest to Dominate the World's Most Critical TechnologyРейтинг: 4.5 из 5 звезд4.5/5 (227)

- Chip War: The Fight for the World's Most Critical TechnologyОт EverandChip War: The Fight for the World's Most Critical TechnologyРейтинг: 4.5 из 5 звезд4.5/5 (82)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsОт EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsРейтинг: 5 из 5 звезд5/5 (2)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102От EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Рейтинг: 5 из 5 звезд5/5 (2)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)От EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Рейтинг: 5 из 5 звезд5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]От EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Рейтинг: 5 из 5 звезд5/5 (2)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XОт EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XРейтинг: 3 из 5 звезд3/5 (2)

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideОт EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideРейтинг: 1 из 5 звезд1/5 (1)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002От EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Рейтинг: 5 из 5 звезд5/5 (1)

- Amazon Web Services (AWS) Interview Questions and AnswersОт EverandAmazon Web Services (AWS) Interview Questions and AnswersРейтинг: 4.5 из 5 звезд4.5/5 (3)

- Programming with STM32: Getting Started with the Nucleo Board and C/C++От EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Рейтинг: 3.5 из 5 звезд3.5/5 (3)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxОт EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxОценок пока нет

- iWoz: How I Invented the Personal Computer and Had Fun Along the WayОт EverandiWoz: How I Invented the Personal Computer and Had Fun Along the WayРейтинг: 3.5 из 5 звезд3.5/5 (317)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFОт EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFОценок пока нет

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertОт EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertРейтинг: 3.5 из 5 звезд3.5/5 (6)

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesОт EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesОценок пока нет

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-1-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)