Академический Документы

Профессиональный Документы

Культура Документы

Two-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck Converter

Загружено:

Raveendhra IitrИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Two-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck Converter

Загружено:

Raveendhra IitrАвторское право:

Доступные форматы

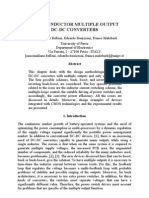

Two-loop voltage-mode control of coupled inductor

step-down buck converter

M. Veerachary

Abstract: A simple two-loop voltage mode control scheme for the two inductor step-down buck

converter is proposed. This is a voltage-mode control scheme in which the external sawtooth

generator for the PWM generation is not required. The controller implementation requires only a

single error amplier and gives almost current-mode control performance. The proposed converter

gives lower ripple in the input current and reduces the input ltering requirements as compared to

the conventional buck topology. To reduce the input current ripple even more, integrated magnetic

components with ripple steering phenomena are proposed. For modelling the converter a signal-

ow-graph approach is developed to nd the converter open, closed-loop small-signal transfer

functions and to eliminate the complexity in the mathematical analysis. A unied signal-ow-graph

model of the converter, from which the complete behaviour can be predetermined, is developed.

Effectiveness of the proposed control scheme and performance improvement is demonstrated

through simulations. Experimental results of load voltage regulation against line and load changes

are provided to validate the proposed modelling and control scheme.

1 Introduction

Several new DCDC converter topologies are being

developed, having high efciency and simple control

scheme, to meet an increasing demand. In the last three

decades, several aspects of DCDC converters have been

explored [1]. These include modelling and analysis, improv-

ing the steady state and dynamic performance etc. Detailed

classication of PWM DCDC converters is discussed in

[2]. The stress is mainly on generation of the two- and four-

switch topologies with two or three energy storage elements.

This exhaustive treatment is useful to identify the nature of

conversion, suitability of the topology for the given

application etc. Among the converter congurations pre-

sented, the topologies having two switches, two inductors

and one capacitor are nding major application in the area

of switch-mode converters. Although these higher-order

converters exhibit complexity in their dynamics, they have

attractive features such as: (i) step-up/down voltage

conversion with continuous input and output current (this

is the major benet for the high-frequency converters as it

reduces the EMI ltering requirement); (ii) since the fourth-

order topologies use two inductors it is possible to

implement the ripple steering phenomena; (iii) realising a

wide variety of voltage conversion ratios with single switch

topology; (iv) simplicity in the control etc.

For meeting the step-down voltage requirements one has

to adapt buck topologies in spite of their larger input

current ripple and EMI. To eliminate some of the

disadvantages of the conventional buck converter a two-

inductor buck converter is proposed in this paper. As

compared to the conventional buck converter it basically

gives continuous input current with less ripple magnitude.

To reduce the input current ripple even more, integrated

magnetic components with ripple steering phenomena [3, 4]

can be used. Several controlling methods, including voltage

mode, current mode and hysteretic control, have been

reported for DCDC converters. Each of the above control

schemes has its own advantages and disadvantages [58].

However, the proposed two-loop voltage-mode control

method is simple in its realisation and achieves almost

similar performance as that of the current-mode control.

The main advantages of the two-loop voltage-mode control

method are: (i) simple controller with low number of

components, (ii) compensation design is easy, (iii) dynamic

response is almost similar to the two-loop current mode

control, (iv) it allows duty ratio variation right from 0 to

100% and thus is capable of compensating for any line or

load disturbances.

For designing the closed-loop controller we need to know

the small-signal models, while the large-signal models are

useful for predetermining the large-signal performance.

Conventionally these models are obtained using the state

space averaging method [9]. However, this method is

tedious, especially when the converter circuit contains a

large number of elements. To overcome some of the

problems mentioned above, a signal-ow graph (SFG)

nonlinear modelling method was developed for PWM

converters [10, 11]. Until now this method was applied for

simple open-loop converters and its applicability for higher-

order closed-loop converter systems was not addressed.

This paper develops a generalised signal-ow graph

(GSFG) of the closed-loop converter system and then

derives expressions useful for controller design. The

advantages of this method includes: (i) it converts the

switching converter, two or multi-state, into a unied

dynamic model; (ii) it is possible to derive large-signal,

small-signal and steady-state models with minimum math-

ematical manipulations; and (iii) the closed-loop SFG

modelling provides exibility in the process of controller

The author is with the Department of Electrical Engineering, Indian Institute of

Technology Delhi, New Delhi-110 016, India

E-mail: mvchary@ee.iitd.ernet.in

r IEE, 2005

IEE Proceedings online no. 20045104

doi:10.1049/ip-epa:20045104

Paper rst received 25th July 2004 and in nal revised form 22nd May 2005

1516 IEE Proc.-Electr. Power Appl., Vol. 152, No. 6, November 2005

design. In the following Section, modelling of the two-loop

voltage-mode-controlled two-inductor buck converter is

discussed.

2 Signal-ow-graph model for two-inductor step-

down buck converter

It is essential to model the converter system both for

designing as well as for controller implementation. Particu-

larly, for controller design one has to know the small-signal

transfer functions of the converter system. If the converter

system contains a higher number of energy storage elements

and switching devices, then the system order is going to

increase. For these higher-order converters nding open-

loop and closed-loop transfer functions, using statespace

averaging technique, becomes a complex task. The

proposed signal-ow-graph approach provides a powerful

mathematical simplication tool and solves some of the

above problems involved in the conventional modelling

methods. Further, using the closed-loop SFG model it is

possible to predict the stability information of the converter

system.

The two-inductor buck converter (Fig. 1) can be operated

either in continuous or discontinuous inductor current

mode. If the input inductor current enters into discontin-

uous current mode then the advantage of using a two-

inductor buck converter is lost. To utilise maximum benets

offered by the proposed converter, the input inductor

current should be continuous. For this continuous inductor

current there are two modes of operation, mode 1 and

mode 2, in one cycle time period. During the time

0ot t

ON

, mode 1, switch S

1

, and during t

ON

ot T,

mode 2, diode D are, respectively, conducting and thus

generating two different ON and OFF state sub-circuits.

Considering the switch S operation as reference, signal-ow

graphs G

ON

and G

OFF

are generated for ON and OFF sub-

circuits sharing common nodes and part of the branches.

The two signal-ow graphs G

ON

and G

OFF

are combined to

form a simplied signal-ow graph. While merging the two

signal-ow graphs, G

ON

and G

OFF

, into a single graph G,

some of the branches exist in the two graphs and some do

not. Branches that exist in G

ON

but not in G

OFF

are replaced

by K

1

branches, and the branches that exist in G

OFF

but not

in G

ON

are replaced by K

2

branches. The resulting graph

topology can be mathematically written as

GK

1

G

ON

+K

2

G

OFF

, where K

1

and K

2

are the switching

functions whose values depend on the switching times

dened by the following expressions:

K

1

1 for 0ot t

ON

0 for t

ON

ot T

1

K

2

0 for 0ot t

ON

1 for t

ON

ot T

2

Using the above switching functions the two SFGs, G

ON

and G

OFF

, are merged to form a single unied SFG, as

shown in Fig. 2a. This is a unied signal-ow graph of the

two-inductor buck converter from which the complete

behaviour, dynamic and steady-state, of the system can be

obtained. A systematic procedure for developing the

large, small-signal and steady-state models, from this

unied signal ow graph, is illustrated in the following

Subsections.

2.1 Large-signal and steady-state models

Assuming that the lter corner frequency is much smaller

than the switching frequency, the effective signals carried at

the outputs of K

1

and K

2

branches, having an average

values d

1

(t) and d

2

(t), respectively, are

yt xtd

j

t 3

where j 1, 2. Equation (3) indicates that the output signal

y(t) from the switching branches K

1

and K

2

is the product of

the input signal and the duty ratio control signal d

1

(t) or

d

2

(t). From these equations the large-signal models for

switching branches are developed. Incorporating these

large-signal models, for the switching branches, in the

graph G and on simplication results in a large-signal ow

graph. This large-signal model can then be directly entered

into the SIMULINK simulator to study its large-signal

behaviour. From the large-signal switching branch models,

the steady-state switching branch models are derived. In the

steady state, the K

1

branch will have a transmittance of

m

1

(t) D

1

and the K

2

branch will have a transmittance of

m

2

(t) D

2

. Simplifying the large-signal ow graph with the

above steady-state switching branch models and setting

complex frequency s-0, a steady-state model is obtained.

From this switching ow graph various steady-state

relations can be derived.

2.2 Small-signal model

A small-signal SFG for the two-inductor buck converter

system can be obtained from the generalised signal-ow

graph, Fig. 2a, by replacing the switching branches, K

1

and

K

2

, with their corresponding small-signal equivalent models.

For illustration, a small-signal equivalent is derived for

switching branch K

1

in the following. For this switching

branch the input and output signals are related as

yt xtd

1

t 4

For linearising the above equation assume that X, Y, D are

the steady-state values of the input, output and duty ratios,

respectively. The small-signal perturbations of these vari-

ables are ^xt; ^ yt;

^

d

1

t, respectively. The input, output

and duty ratio variables, including small-signal perturba-

tions, are: xt X ^xt; yt Y ^ yt; d

1

t D

1

^

d

1

t and d

2

t D

2

^

d

2

t. Inserting these relationships

in (4) results in

Y ^ yt X ^xtD

1

^

d

1

t

XD

1

D

1

^xt X

^

d

1

t ^xt

^

d

1

t 5

R

L

1

i

2

i

1

i

g

S

L

2

D

C

1

V

g

V

0

+

PWM

generator

V

ref

+

G

control

signal

C

2

compensator

V

c

Fig. 1 Two-loop voltage-mode control of two-inductor step-down

buck converter

IEE Proc.-Electr. Power Appl., Vol. 152, No. 6, November 2005 1517

Substituting the condition for operating point, YXD

1

,

and on the assumption of neglecting second-order perturba-

tion terms, ^xt

^

d

1

t, the small-signal switching equation for

the K

1

branch is

^ yt D

1

^xt X

^

d

1

t 6

On similar lines the small-signal switching branch equation

for the K

2

branch can be derived and it is

^ yt D

2

^xt X

^

d

2

t, where D

1

and D

2

( (1D

1

)) are

the duty ratio control functions of mode 1 and mode 2,

respectively. The above equations dene the graphical

representation of small-signal switching branches. On

substitution of the above small-signal switch branches in

Fig. 2a, an extra branch with node d is going to appear.

We have to combine all such nodes, d, by moving the

corresponding branches to one common place. While

moving these branches in the signal-ow direction, the

branch transmittance is going to multiply with that path

transmittance. On the other hand if the movement of

branch is opposite to the signal-ow direction then the

branch transmittance is going to be divided by the

corresponding path transmittance. Taking these points into

consideration simplication is made and the nal small-

signal SFG is generated, as shown in Fig. 2b. This small-

signal model can be used to derive the small-signal

performance transfer functions between any two nodes.

However, the most commonly used small-signal transfer

functions are obtained here using the well-known Masons

gain formula [12]. To nd the gain between any two nodes

of the graph we have to identify (i) the forward paths and

(ii) the loops, both touching and non-touching. Once the

forward paths and loops are identied then we need to nd

their path/loop transmittances. Knowing all the above,

nding the transfer function is only a matter of mathema-

tical simplication of the gain formula, gain

P

k

P

k

D

k

D

,

where P

k

is the kth forward path gain and D is the

determinant of the graph. The sample derivation of audio

susceptibility is given in the following. To start with, various

possible forward paths and loops are identied from the

small-signal SFG. There are two forward paths between the

nodes ^v

g

and ^v

0

^v

0

^v

c2

. The corresponding transmit-

tances, formed by the nodes ^v

g

^v

1

^

i

1

^

i

c1

^v

c1

^v

2

^

i

2

^

i

c2

^v

c2

and ^v

g

^v

1

^

i

1

^

i

C2

^v

C2

, are

p

1

R1 sCr

c

d

1

d

2

sC

1

sL

1

r

1

sL

2

r

2

1 sCR r

c

7

p

2

R1 sCr

c

sL

1

r

1

1 sCR r

c

8

In this small-signal ow graph six loops formed by nodes

^v

1

^

i

1

^

i

c1

^v

c1

^v

1

,

^

i

c1

^v

c1

^v

2

^

i

2

^

i

c1

, ^v

2

^

i

2

^

i

c2

^v

c2

^v

2

, ^v

1

^

i

1

^

i

c2

^v

c2

^v

1

, ^v

1

^

i

1

^

i

c1

^v

c1

^v

2

^

i

2

^

i

c2

^v

c2

^v

1

and ^v

1

^

i

1

^

i

c2

^v

c2

^v

2

^

i

2

^

i

c1

^v

c1

^v

1

exist, and their loop transmittances are

l

1

d

2

2

sC

1

sL

1

r

1

; l

2

d

2

1

sC

1

sL

2

r

2

9

l

3

R1 sCr

c

sL

2

r

2

1 sCR r

c

;

l

4

R1 sCr

c

sL

1

r

1

1 sCR r

c

10

l

5

R1 sCr

c

d

1

d

2

sC

1

sL

1

r

1

sL

2

r

2

1 sCR r

c

;

l

6

R1 sCr

c

d

1

d

2

sC

1

sL

1

r

1

sL

2

r

2

1 sCR r

c

11

Among the above six loops the non-touching loop pairs are

(l

1

, l

3

) and (l

2

, l

4

). In this SFG all the loops touch the

forward path p

1

and hence D

1

l and D

2

(1L

2

).

Applying Masons gain formula, the input-to-output

V

1

V

g

V

2

V

c

2

i

g

1

1

i

1

i

2

V

c1

i

c1

i

c2

K

2

K

1

K

2

K

1

1

(sL

2

+r

2

)

1

(sL

1

+r

1

)

1 1

1

1

[1+sC(R+r

c

)]

R(1+sCr

c

)

1

C

1

s

a

1

v

1

v

c

2

i

g

v

2

i

1

i

2

v

c1

i

c1

i

c2

K

2

K

1

(sL

1

+r

1

)

1

[1 +sC(R + r

c

)]

R(1+sCr

c

)

1

1

1

i

0

v

g

d

a

k

K

2

K

1

(sL

2

+r

2

)

1 1 1 1

C

1

s

b

v

g

v

c

v

0

d

F

m3

F

4

F

m1

H

e

A

v

F

m2

F

1

F

2

c

V

1

V

g

1

1

V

su

V

c

V

tm

1

K

1

K

2

1

[1+sC(R+r

c

)]

R(1+sCr

c

)

t =

t

G

T

c

V

2

V

c 2

i

g

1

1

i

1

i

2

V

c1

i

c1

i

c2

K

2

K

1

K

2

K

1

1

(sL

2

+r

2

)

1

(sL

1

+r

1

)

1 1

1

1

1

C

1

s

V

ref

d

Fig. 2 Signal ow graphs of the open and closed loop converter

a Unied signal ow graph of two-inductor step-down buck converter

b Small-signal SFG of two-inductor step-down buck converter

c Small-signal SFG of closed-loop two-inductor buck converter system

d Large-signal SFG of closed-loop two-inductor buck converter

system

1518 IEE Proc.-Electr. Power Appl., Vol. 152, No. 6, November 2005

transfer function is obtained as

M

v

s F

1

^v

0

s

^v

g

s

ds0

p

1

D

1

p

2

D

2

1 l

1

l

2

l

3

l

4

l

5

l

6

l

1

l

3

l

2

l

4

12

Substituting (7)(11) in the above equation and simplifying

results in the following expression:

^v

0

s

^v

g

s

R1 sCr

c

t

2

t

4

d

1

d

1

d

2

t

1

t

2

t

3

t

4

t

3

t

1

d

2

1

t

2

d

2

2

R1 sCr

c

t

4

t

1

t

2

d

1

d

2

13

where t

1

(sL

1

+r

1

), t

2

(sL

2

+r

2

), t

3

[l+sC(R+r

c

)] and

t

4

sC

1

; r

1

and r

2

are the series resistances of the inductors

and r

c

is the equivalent series resistance (ESR) of the

capacitor. L

1

and L

2

are the equivalent inductances of the

integrated inductor, which are dependent on the nature of

the coupling and its value. The open-loop input impedance

is derived as

Z

i

s F

3

^v

g

s

^

i

g

s

ds0

14

^v

g

s

^

i

g

s

t

1

t

2

t

3

t

4

t

3

t

1

d

2

1

t

2

d

2

2

R1 sCr

c

t

4

t

1

t

2

d

1

d

2

t

2

t

3

t

4

t

3

d

2

1

R1 sCr

c

t

4

15

The open-loop output impedance is

Z

0

s F

2

^v

0

s

^

i

0

s

ds0

16

^v

0

s

^

i

0

s

R1 sCr

c

t

1

t

2

t

4

t

1

d

2

1

t

2

d

2

2

t

1

t

2

t

3

t

4

t

3

t

1

d

2

1

t

2

d

2

2

R1 sCr

c

t

4

t

1

t

2

d

1

d

2

17

To nd the control-to-output transfer function it is required

to substitute the condition ^v

g

s 0 and (5) and (6) into the

small-signal SFG. Owing to the presence of the small-signal

duty ratio variation,

^

d, in (5) and (6), an extra node is going

to add up in each switching branch. All such nodes are

combined and replaced by single

^

d node with a branch

transmittance, a

k

, dened by (18). Here a

k

is the branch

transmittance, obtained by moving all the

^

d nodes to a

common node. This node is required only when nding the

small-signal transfer function, ^v

0

s=

^

ds. The remaining

transfer function evaluations simply becomes zero:

a

k

V

c1

sL

1

r

1

V

c1

d

1

d

2

sC

1

sL

1

r

1

sL

2

r

2

I

1

I

2

d

1

sC

1

sL

2

r

2

18

T

p

s F

4

^v

0

s

^

ds

^v

g

s0

19

^v

0

s

^

ds

R1 sCr

c

t

1

t

2

t

4

t

1

d

2

1

t

2

d

2

2

V

C1

t

2

t

4

d

1

d

2

t

1

d

1

I

1

I

2

t

1

t

2

t

4

t

1

t

2

t

3

t

4

t

3

t

1

d

2

1

t

2

d

2

2

R1 sCr

c

t

4

t

1

t

2

d

1

d

2

20

The above transfer functions are in agreement with those

obtained from the state-space averaging method. Manip-

ulating circuit equations and linearisation around the

operating point or matrix inversions for the higher-order

converters becomes a difcult job. The distinct advantage of

the proposed SFG method is that the small-signal transfer

function of the designer choice can be determined directly

without going into details of the other transfer functions.

This fact is demonstrated in the above small-signal analysis.

The open-loop transfer functions, derived above, together

with fast and slow feedback and feedforward modulator

gains are useful to analyse the small-signal characteristics of

the two-loop voltage-mode controlled converter and its

controller design. Controller design details are discussed in

the next Section.

3 Signal-ow graph model of closed-loop

converter system

The above derived open-loop small-signal transfer functions

are useful for obtaining the closed-loop small-signal

characteristics of the converter system. To deduce the

closed-loop small-signal properties of the step-down buck

converter, a closed-loop signal-ow graph is developed

taking F

1

F

4

, given in the preceding Section, as branch

transmittances. The proposed control scheme involves two

voltage loops: a faster inner loop and a slower outer loop.

The inner voltage loop has a characteristic similar to that of

the inner current loop in the current-mode control [6] and it

is represented by F

m1

H

e

, where H

e

is the gain of the inner

voltage loop. Thus, in the closed-loop system signal-ow

graph this inner loop is replaced by a branch having

transmittance of F

m1

H

e

(s). On similar lines the outer voltage

loop is represented by a branch having transmittance of

F

m2

A

v

(s), where A

v

(s) is the gain of the error amplier/

compensator. Detailed derivation of the small-signal

transfer functions F

m1

, F

m2

and F

m3

is given in the

Appendix.

From the closed-loop signal-ow graph (Fig. 2c) we can

easily determine various transfer functions. In this paper the

most commonly used transfer functions, including loop gain

T(s), are derived and tabulated in Table 1 for ready

reference. Once the loop gain is known, the design of the

compensator is a straightforward application of the design

method. Note that here the closed-loop small-signal SFG

model (Fig. 2c) provides faster means for obtaining the

closed-loop small-signal transfer functions with minimum

effort. Starting with loop gain transfer function, T(s), the

closed-loop system is designed here. A type II compensator

is used for stabilising the system and its transfer function is

given by

A

v

s

1 sC

a

r

b

sC

a

r

a

1 sC

b

r

b

21

In this case we have to design the compensator to meet the

predened stability requirements. Once we complete the

Table 1: Small-signal transfer functions of closed-loop

converter system

^ v

0

s

^ v

c

s

F

m2

F

4

1 F

m1

F

4

H

e

F

m2

F

4

A

v

^ v

0

s

^ v

g

s

F

1

F

4

F

m3

1 F

m1

F

4

H

e

F

m2

F

4

A

v

^ v

0

s

^

i

0

s

F

2

1 F

m1

F

4

H

e

F

m2

F

4

A

v

T(s) A

v

F

m2

F

4

1 F

m1

F

4

H

e

s

IEE Proc.-Electr. Power Appl., Vol. 152, No. 6, November 2005 1519

design process of the compensator then verifying its

regulation capability is required. Here the closed-loop

large-signal SFG model of the converter system (Fig. 2d)

is useful to assess the above designed compensator

suitability. Sometimes the designed compensator meets the

design specications, but there is no guarantee that it will

result in better dynamic performance. Under this condition

we need to redesign the compensator with a different set of

parameters and then verify its stabilisation capability. At

this point the closed-loop SFG, derived from GSFG,

provides a powerful tool to test the compensator capability

and to predetermine the large-signal behaviour. Moreover,

we can combine the large-signal SFG SIMULINK

simulation prole with the controller design program

through the subroutine function block. Hence, the closed-

loop SFG modelling provides the exibility in the process of

controller design. All these advantages are mainly due to the

existence of the unied SFG model.

4 Integrated inductor

The concept of ripple steering using coupled inductor/

integrated inductor is very useful in the DCDC converters

[3, 4]. This integrated inductor not only requires fewer cores

but also improves the converter performance. Performance

improvement mainly includes the ripple reduction in one of

the inductors or improving the dynamic response. The

mathematical treatment and conditions for achieving zero

ripple in the source current is given in the following. During

the switch-on period the following circuit equations for the

coupled inductor can be easily obtained:

v

Lj

L

j

di

j

dt

M

di

j

dt

: j 1; 2 22

V

g

v

L1

V

0

; v

C1

v

L2

V

0

23

Substituting (22) into (23) and simplifying results in

di

2

dt

V

g

V

0

M

L

1

M

di

1

dt

24

Using (22), (23) and (24) we can easily arrive at the

following equation:

di

1

dt

L

2

M

L

1

L

2

M

2

V

g

V

0

25

Equation (25) indicates that if L

2

M then di

1

/dt 0, which

means that the inductor current i

1

is essentially a constant

value or the ripple Di

1

0. Similar equations can be easily

derived for the switch-off period. This means the ripple

reduction is possible in the entire switching period. The

above theory indicates perfect ripple compensation, but in

an actual case achieving exact zero ripple compensation

depends on: (i) realising the identical mutual and self-

inductance values, (ii) resistive voltage drops in the

inductors should ideally be zero, and (iii) ripple in the

capacitor voltage should be almost zero.

5 Principle of two-loop voltage-mode control

scheme and experimental system description

The proposed two-loop control is a simple voltage-mode

control and it uses two loops similar to the current-mode

control. However, this control scheme is easy to implement

by using a single error amplier and a PWM generator, as

shown in Fig. 1. The outer loop generates a control signal,

depending on the error signal, to the PWM generator, while

the inner voltage loop acts as a comparator and generates

the PWM sequence to the switching device. The load

voltage is used as the PWM ramp signal and it is fed to the

PWM generator. Whenever a change in the supply voltage

occurs, it will automatically reect the slope of the load

voltage ripple. Since the load voltage is used as the PWM

ramp, the corresponding duty ratio changes accordingly,

either increases or decreases, to maintain the load voltage

almost constant. On similar lines changes in the load

directly affect the load voltage ripple slope, which in turn

changes the pulse width of the PWM output to achieve the

load voltage regulation.

To verify the proposed control methodology an experi-

mental prototype control circuit was breadboarded with a

MOSFET and a fast recovery diode. The semiconductor

devices used are a IRF530 power MOSFET and a

MUR820 fast recovery diode. The inductor is made of a

TDK: HF70 T, whose dimensions are 100127mm.

For designing the converter parameters design equations

are derived based on time-domain analysis; detailed

derivation is not given here to limit the paper length, and

are given in Table 2. The inductance value, L

1

, is chosen to

be higher than the critical inductance requirement. For

ripple cancellation in the inductance L

1

, discussion given in

Section 4, it is required to choose L

2

M. Further, it is

found that through simulations L

2

0.5 L

1

results in better

ripple cancellation. The resulting converter parameters are:

r

1

83mO, r

2

99mO, R12O, L

1

71mH, L

2

35.5mH,

C

1

22mF, C

2

220mF and V

0

14V. The switching

device is driven by a IR2110 gate driver. An IC 6N137 is

used for isolation purposes. The compensator is made with

the help of op-amp TL072, and measurements are taken

from the test circuit. The instantaneous load voltage is

sampled through a resistive potential divider and is given to

the two-loop controller.

6 Experimental results and discussions

The proposed voltage-mode controller based two-inductor

buck converter system is shown in Fig. 1. Simulation is

performed to verify the proposed two-loop control scheme.

To maintain the load voltage constant, against the line

and load disturbances, the converter duty ratio must

be changed. This duty ratio is controlled by means of a

PWM generator, obtained from the two-loop voltage-mode

controller. The proposed control scheme for the two-

inductor buck converter is evaluated through simulations.

First the compensator, transfer function given by (21), is

designed using the loop gain, T(s), of the closed-loop system

converter. The controller design program was developed in

the MATLAB [13] environment. For the converter para-

meters given above, the nal loop gain frequency response

characteristics are shown in Fig. 3. These characteristics

indicate that the combined system is stable (gain margin

8.8dB, phase margin401). Taking this compensator the

performance of the closed-loop system is simulated in the

Table 2: Converter design equations

i

L1max

V

g

v

c2

L

1

DT i

L1min

i

L1min

V

g

v

c1

v

c2

L

1

1 DT i

L1max

L

1(critical)

R1 D

2Df

s

Dv

0

v

0

1 D

8L

2

C

2

f

2

s

1520 IEE Proc.-Electr. Power Appl., Vol. 152, No. 6, November 2005

PSIM circuit-oriented power electronic simulator. The

current-mode control scheme is also simulated and

compared with the proposed control scheme. For illustra-

tion, the load voltage regulation characteristics, for two

controlling methods, are shown in Fig. 4. These dynamic

responses indicate that the proposed two-loop controller

results in an almost similar response to that of the current-

mode control. The load voltage is 14V, which is equal to

the reference voltage set point. Further, the input current is

continuous, which is not the case for a conventional buck

converter, wherein the source current is of a pulsating

nature.

A performance comparison study, ripple reduction in the

source current with and without integrated inductor, with

two-loop voltage-mode control was also carried out. For

illustration of ripple steering phenomena of the integrated

inductor, the steady-state ripple reduction in the source

current and load voltage is shown in Fig. 5. Although the

ripple reduction in the load voltage is not signicant, it is

more effective in source current ripple reduction. Because of

this, the ltering requirements are very much less on the

input side of the converter. For illustration of the control

principle the load voltage regulation characteristics are

150

100

50

0

50

100

0.01 0.1 1 10 100 1000

frequency, kHz

m

a

g

n

i

t

u

d

e

,

d

B

control-to-output (open loop)

compensator

loop gain

300

250

200

150

100

50

0

50

100

150

0.01 0.1 1 10 100 1000

frequency, kHz

p

h

a

s

e

,

d

e

g

control-to-output (open loop)

compensator loop gain

a

b

Fig. 3 Small-signal characteristics of two-inductor buck converter

system

a Magnitude plot

b Phase plot

0

2

4

6

8

10

12

14

36 37 38 39 40 41 42 43 44

0

0.5

1.0

1.5

2.0

I

0

V

0

l

o

a

d

v

o

l

t

a

g

e

,

V

time, ms

l

o

a

d

c

u

r

r

e

n

t

,

A

current-mode control

proposed control

R=12 R=10

Fig. 4 Dynamic response of load voltage and current

13.0

13.2

13.4

13.6

13.8

14.0

14.2

14.4

15.00 15.02 15.04 15.06 15.08 15.10 15.12

0.4

0.6

0.8

1.0

1.2

1.4

I

g

V

0

l

o

a

d

v

o

l

t

a

g

e

,

V

time, ms

s

o

u

r

c

e

c

u

r

r

e

n

t

,

A

non-coupled

coupled

Fig. 5 Steady-state ripple comparison of load voltage and source

current

0

2

4

6

8

10

12

14

5 10 15 20 25

time, ms

l

o

a

d

v

o

l

t

a

g

e

,

V

0

0.5

1.0

1.5

2.0

I

0

V

0

V

g

= 20 V V

g

= 16 V

l

o

a

d

c

u

r

r

e

n

t

,

A

Fig. 6 Dynamic response of load voltage and current (source

disturbance)

IEE Proc.-Electr. Power Appl., Vol. 152, No. 6, November 2005 1521

presented here for two cases: (i) change of load resistance

from 12 to 10O, and (ii) supply voltage change from 20 to

16V. These results are shown in Figs. 4 and 6. The

performance of the two-loop voltage-mode controller was

also veried for variable reference set point voltages

(simulation results are not given here due to limitation on

the number of Figures), and it was found that the controller

is capable of adjusting the load voltage to the new reference

voltage within a reasonable amount of time.

To verify the above simulation results an experimental

closed-loop controlled converter system prototype was

made in the laboratory and measurements were taken from

this test circuit. Initially measurements were recorded on the

two-inductor buck converter without any coupling among

the two inductors. These results indicate that the source

current and load voltage contain considerable amounts of

ripple, which need to be reduced even further. One way to

reduce this ripple current is by increasing the ltering

components, resulting in a physically large size for a

practical design. The alternative option is to use a larger

value of inductance, so that the steady-state current ripple is

minimum. Although increasing the inductance value

reduces the steady-state current ripple, the transient

response becomes sluggish. Under these circumstances the

coupled/integrated inductor can resolve the above pro-

blems, provided that its design parameters satisfy the zero

ripple condition. This coupled inductor will not only give a

compact magnetic design, but also results in an improved

converter performance. Among two possible coupling

structures, direct and inverse coupling, the inverse coupling

results in better performance. This is because with inverse

coupling the common-mode inductance is high. As a result

the steady-state current ripple is low, and hence the

corresponding power loss is also low. Initially the converter

steady-state performance with and without an integrated

inductor was measured for a load voltage reference of 14V.

The measured waveforms, source, load currents and load

voltage are shown in Figs. 7a and b. These results indicate

that the ripple is reduced in both the source current and the

i

g

Ch 1: V

0

Ch 3: i

0

Ch 4: i

0

i

0

V

0

Ch 1: V

0

Ch 3: i

L1

Ch 4: i

0

i

0

V

0

i

L1

a

b

Fig. 7 Steady-state converter waveforms

a Steady-state performance of converter without integrated inductor

Ch 1: 5V/div., Ch 3: 1V/div., Ch 4: 0.5A/div

b Steady-state performance of converter with integrated inductor

Ch 1: 5V/div., Ch 3: 1V/div., Ch 4: 0.5A/div

Ch 1: V

0

Ch 4: i

0

i

0

V

0

Fig. 8 Dynamic response of load voltage and current (load

disturbance)

Ch 1: 5V/div., Ch 4: 1A/div

Ch 1: V

0

Ch 4: i

0

Ch 2: V

g

V

g

i

0

V

0

Fig. 9 Dynamic response of load voltage and current (source

disturbance)

Ch 1: 5V/div., Ch 2: 20V/div., Ch 4: 0.5A/div

1522 IEE Proc.-Electr. Power Appl., Vol. 152, No. 6, November 2005

load voltage. This is mainly because of the coupling between

the two inductors. It is clear that the converter is operating

with a duty ratio such that the load voltage is equal to 14V,

which is equal to the reference voltage set point of the

converter. The closed-loop performance of the converter

with integrated inductor was studied and for illustration of

the control principle, the closed-loop load voltage regulation

characteristics are presented here for two cases: (i) load

change from 12.07 to 10.05O and (ii) supply voltage change

from 20.03 to 16.02V. These experimental results are given

in Figs. 8 and 9, respectively. From these results it can be

noticed that the load voltage is held at constant value, equal

to reference value, even under line and load disturbances.

Experimental observations were also made on whether

the designed controller is capable of changing the load

voltage when there is a change in the reference voltage set

point. For illustration, the reference voltage is changed from

8 to 15V and the corresponding load voltage, current and

input current dynamics were measured, as shown in Fig. 10.

These measurements indicate that the proposed two-loop

controller is adjusting itself for variable set point reference

voltages with faster dynamic response. This control method

results in variable frequencies whenever there is any change

in the operating point. Because of this fact the experimental

and simulation results are slightly different with respect to

the frequency point of view, as is evidenced from Figs. 5

and 7b. The other reason for this difference could be the

difculty of accurate representation of magnetic saturation

of the integrated inductor in the simulation prole. Slight

discrepancies between simulated and experimental results

are mainly due to: (i) the use of available switch models

and integration methods of the simulator, (ii) neglecting

parasitic component voltage drop, (iii) realising actual

experimental conditions while performing the simulations,

(iv) use of simplied assumptions, (v) slight errors in

measuring instruments etc.

7 Conclusions

A simple two-loop voltage-mode controller has been

proposed and implemented for the two-inductor step-down

converter. Mathematical models of open and closed-loop

two-inductor buck converter have been developed using

the signal-ow-graph method. Ripple steering and

performance improvement of the converter with coupled

inductor have been analysed. The proposed voltage-

mode controller performance was compared with that

of the current-mode controller, and it was found that

these two controlling schemes result in almost identical

performance. The designed controller is simple and at the

same time it requires few passive components for its

implementation. Experimental results are presented to

validate the operation, performance advantages of proposed

modelling and control scheme of the two-inductor buck

converter.

8 Acknowledgment

The author would like to thank the Department of Science

and Technology, Government of India for supporting this

research through the SERC FAST Track Scheme.

9 References

1 Forsyth, A.J., and Mollov, S.V.: Modelling and control of DC-DC

converters, Power Eng. J., 1998, 12, (5), pp. 229236

2 Tymerski, R., and Vorperian, V.: Generation and classication of

PWM DC-DC converters, IEEE Trans. Aerosp. Electron. Syst., 1988,

26, (4), pp. 743754

3 Hamill, D.C., and Krein, P.T.: A zero ripple technique applicable to

any DC converter. Proc. IEEE PESC, 1999, pp. 11651171

4 Cuk, S., and Zhang, Z.: Coupled inductor analysis and design. Proc.

IEEE PESC, 1986, pp. 655665

5 Goder, D., and Pelletier, W.R.: V

2

architecture provides ultra-fast

transient response in switch mode power supplies. Proc. High

Frequency Power Converson Conf., 1996

6 Ridley, R.B.: A new continuous time model for current-mode

control, IEEE Trans. Power Electron., 1991, 6, (2), pp. 271280

7 Choi, B.: Step load response of current-mode controlled DC-DC

converter, IEEE Trans. Aerosp. Electron. Syst., 1997, 33, (4),

pp. 11151121

8 Veerachary, M.: V

2

Control of interleaved buck converters. IEEE

Int. Symp. on Circuits and Systems, 2003, Vol. 3, pp. 344346

9 Middlebrook, R.D., and Cuk, S.: A general unied approach to

modeling switching converter power stages. IEEE Power Electronics

Specialist Conf., 1976, Vol. 4, pp. 1834

10 Smedley, K., and Cuk, S.: Switching ow-graph nonlinear modeling

technique, IEEE Trans. Power Electron., 1994, 9, (4), pp. 405413

11 Veerachary, M., Senjyu, T., and Uezato, K.: Signal ow graph

nonlinear modeling of interleaved converters, IEE Proc., Electr.

Power Appl., 2001, 148, (5), pp. 410418

12 Gopal, M.: Modern control systems theory (Wiley, New York, USA,

1984)

13 MATLAB, Math works user manual (MATLAB, 2000)

10 Appendix

In this two-loop voltage-mode control the PWM pattern is

obtained by comparing the load voltage ripple with the

control voltage. The load voltage ripple, of triangular

nature, mainly depends on the capacitance value and its

ESR. In the closed-loop small-signal SFG model, shown in

Fig. 2c, the inner and outer voltage-loop modulator gains

respectively, are F

m1

, F

m2

, and F

m3

is the feedforward

modulator gain. These gains, small-signal transfer functions,

are required while nding the closed-loop characteristics of

the converter given in Table 2. For determining these gains,

rst we have to express the load voltage in terms of circuit

parameters, control voltage and then linearise around the

operating point. The average load voltage is

V

0

v

c

S

c

DT

DV

0

2

26

where v

c

is the control voltage and S

c

is its slope. Here the

control voltage is obtained from the inner voltage loop,

which is equal to the instantaneous load voltage ripple. The

load voltage ripple, DV

0

, is contributed by the capacitor and

its ESR. If DI is the ripple current entering the capacitor

i

g

Ch 2: V

0

Ch 1: V

ref

Ch 3: i

g

Ch 4: i

0

V

0

V

ref

i

0

Fig. 10 Dynamic response of load voltage and current (reference

change)

Ch 1: 5V/div., Ch 2: 5V/div., Ch 3: 2V/div., Ch 4: 1A/div

IEE Proc.-Electr. Power Appl., Vol. 152, No. 6, November 2005 1523

branch then the load voltage ripple can be written as

DV

0

DIr

c

DI

8fC

2

27

where DI

v

g

v

0

DT

L

. The small-signal transfer function

F

m1

can easily be found by linearising the (26) around

the operating point. Incorporating the small-signal

perturbations v

0

v

0

^v

0

, D D

^

d in (26) results in

v

0

^v

0

v

c

D

^

dTS

c

v

g

v

0

^v

0

2L

D

^

dr

c

T

v

g

v

0

^v

0

16LC

2

D

^

dT

2

28

Neglecting second- and higher-order perturbation terms

and simplifying the above equation results in

^v

0

^v

0

r

c

DT

2L

DT

2

16LC

2

^

d TS

c

v

g

v

0

2L

r

c

T

v

g

v

0

16LC

2

T

2

29

F

m

1

^

d

^v

0

^v

g

0

1

r

c

DT

2L

1

T

8r

c

C

2

TS

c

v

g

v

0

2L

T r

c

T

8C

2

30

F

m

2

^

d

^v

0

^v

g

0

1

r

c

DT

2L

1

T

8r

c

C

2

TS

c

v

g

v

0

2L

T r

c

T

8C

2

31

Similar analysis to that given above can be used for

obtaining the F

m3

modulator small-signal transfer function.

Incorporating the small-signal perturbations of v

g

and D,

v

g

v

g

^v

g

and D D

^

d, in (26) and (27) results

in

v

0

v

c

D

^

dTS

c

v

g

^v

g

v

0

2L

D

^

dr

c

T

v

g

^v

g

v

0

16LC

2

D

^

dT

2

32

Neglecting second- and higher-order perturbation terms

and simplifying the above equation results in the following

transfer function:

F

m3

^

d

^v

g

^v

0

0

r

c

D

DT

8C

2

2LS

c

v

g

v

0

r

c

T

8C

2

33

1524 IEE Proc.-Electr. Power Appl., Vol. 152, No. 6, November 2005

Вам также может понравиться

- Self 4Документ8 страницSelf 4ShenbagalakshmiОценок пока нет

- Signal Flow Graph Modeling and Disturbance Observer Based Output Voltage Regulation of An Interleaved Boost ConverterДокумент6 страницSignal Flow Graph Modeling and Disturbance Observer Based Output Voltage Regulation of An Interleaved Boost ConverterJorge MorfinОценок пока нет

- Dynamic Modeling and Analysis of The Bidirectional DCDC Boost-Buck ConverterДокумент40 страницDynamic Modeling and Analysis of The Bidirectional DCDC Boost-Buck ConverterAndresSs NineОценок пока нет

- 3939 Ijet IjensДокумент9 страниц3939 Ijet IjensGarudaOzoОценок пока нет

- Analysis of Fourth-Order DC-DC Converters: A Flow Graph ApproachДокумент9 страницAnalysis of Fourth-Order DC-DC Converters: A Flow Graph ApproachkamiyabОценок пока нет

- Modelling and Control of A Novel Zero-Current-Switching Inverter With Sinusoidal Current OutputДокумент11 страницModelling and Control of A Novel Zero-Current-Switching Inverter With Sinusoidal Current OutputSuresh KumarОценок пока нет

- Current Distribution Control Design For Paralleled DC/DC Converters Using Sliding-Mode ControlДокумент10 страницCurrent Distribution Control Design For Paralleled DC/DC Converters Using Sliding-Mode ControlAnushya RavikumarОценок пока нет

- Fuzzy Logic Controlled Bidirectional DC-DC Converter Applied To DC DriveДокумент12 страницFuzzy Logic Controlled Bidirectional DC-DC Converter Applied To DC DriveTJPRC PublicationsОценок пока нет

- Digital Two-Loop Controller Design For Fourth Order Split-Inductor ConverterДокумент6 страницDigital Two-Loop Controller Design For Fourth Order Split-Inductor ConverterRaveendhra IitrОценок пока нет

- Modelling Bidirectional Buck BoostДокумент7 страницModelling Bidirectional Buck BoostAkay HanafiahОценок пока нет

- Unified Model of PWM Switch Including Inductor in DCM (0074 1Документ2 страницыUnified Model of PWM Switch Including Inductor in DCM (0074 1Jesús MendozaОценок пока нет

- Quadratic Boost Converter For Photovoltaic Micro-Inverter: Ashirvad M and Rupesh K CДокумент6 страницQuadratic Boost Converter For Photovoltaic Micro-Inverter: Ashirvad M and Rupesh K CUmesh KumarОценок пока нет

- Step Down PSIMДокумент6 страницStep Down PSIMAnonymous W44hzJ9roОценок пока нет

- Small-Signal Modeling of Digitally Controlled Grid-Connected Inverters With FiltersДокумент14 страницSmall-Signal Modeling of Digitally Controlled Grid-Connected Inverters With FiltersTravis GrayОценок пока нет

- High-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniqueДокумент9 страницHigh-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniquekerblaОценок пока нет

- Analytical Model of The Half-Bridge Series Resonant Inverter For Improved Power Conversion Efficiency and PerformanceДокумент4 страницыAnalytical Model of The Half-Bridge Series Resonant Inverter For Improved Power Conversion Efficiency and PerformanceMaruthi JacsОценок пока нет

- IEEE 2011 April Boost ConverterДокумент16 страницIEEE 2011 April Boost Convertersam chenОценок пока нет

- Generate Buck and Boost Outputs from a Single DC SourceДокумент3 страницыGenerate Buck and Boost Outputs from a Single DC SourceKEERTHY SОценок пока нет

- Buck Boost Converter Small Signal Model Dynamic Analysis Under System Uncertainties PDFДокумент13 страницBuck Boost Converter Small Signal Model Dynamic Analysis Under System Uncertainties PDFTariq KhanОценок пока нет

- Integrated Dual-Output ConverterДокумент11 страницIntegrated Dual-Output ConverterSeza Dw IslamicsiaОценок пока нет

- Analysis of Buck Converter and Simulating It For Different Switching Frequencies and Different Power DevicesДокумент6 страницAnalysis of Buck Converter and Simulating It For Different Switching Frequencies and Different Power DevicesPrema Vinod PatilОценок пока нет

- High Performance DCDC Buck Converter Using SlidingДокумент9 страницHigh Performance DCDC Buck Converter Using SlidingArivalakan Joyal2002Оценок пока нет

- Buck BoostДокумент6 страницBuck BoostAngel MarianoОценок пока нет

- Design, Simulation and Implementation of An Adaptive Controller On Base of Artificial Neural Networks For A Resonant DC-DC ConverterДокумент4 страницыDesign, Simulation and Implementation of An Adaptive Controller On Base of Artificial Neural Networks For A Resonant DC-DC Converterbacuoc.nguyen356Оценок пока нет

- Matteini PHD Part3Документ28 страницMatteini PHD Part3Jagabar SathikОценок пока нет

- Sensorless Current Mode Control-An Observer-Based Technique For DC-DC ConvertersДокумент5 страницSensorless Current Mode Control-An Observer-Based Technique For DC-DC ConvertersDipanjan DasОценок пока нет

- Control of Dual Active BridgeДокумент15 страницControl of Dual Active Bridget64008Оценок пока нет

- Genetic Algorithm Based 7-Level Step-Up Inverter With Reduced Harmonics and Switching DevicesДокумент17 страницGenetic Algorithm Based 7-Level Step-Up Inverter With Reduced Harmonics and Switching DevicesMasudur RahmanОценок пока нет

- Dynamic Modeling and Controller Design For A SinglДокумент13 страницDynamic Modeling and Controller Design For A SinglSkp FAОценок пока нет

- Zeta DC-DCДокумент8 страницZeta DC-DCferdous sovonОценок пока нет

- Performance Estimation of Tristate DC-DC Buck Converter With Fixed Frequency and Constant Switching Hysteresis ControlДокумент10 страницPerformance Estimation of Tristate DC-DC Buck Converter With Fixed Frequency and Constant Switching Hysteresis ControleditorijaiemОценок пока нет

- Non Isolated Bidirectional DC DC ConverterДокумент6 страницNon Isolated Bidirectional DC DC ConverterAnuja VargheseОценок пока нет

- Ridley 1991Документ10 страницRidley 1991mounicapaluru_351524Оценок пока нет

- Bidirectional LLC Resonant Converter For Energy Storage ApplicationsДокумент7 страницBidirectional LLC Resonant Converter For Energy Storage ApplicationsRodrigo MesquitaОценок пока нет

- Heavy Load Light Load Conversion ReportДокумент41 страницаHeavy Load Light Load Conversion ReportSanjivee SachinОценок пока нет

- IET Power Electronics - 2018 - Blinov - Bidirectional Soft Switching DC DC Converter For Battery Energy Storage SystemsДокумент10 страницIET Power Electronics - 2018 - Blinov - Bidirectional Soft Switching DC DC Converter For Battery Energy Storage SystemsHsekum RamukОценок пока нет

- A Fixed Frequency Dual-Mode DC-DC Buck Converter With Fast-Transient Response and High Efficiency Over A Wide Load RangeДокумент6 страницA Fixed Frequency Dual-Mode DC-DC Buck Converter With Fast-Transient Response and High Efficiency Over A Wide Load RangeskrtamilОценок пока нет

- Sliding Mode Control of SMPS: Ms. A. Jonisha, Mrs. V. Devi MaheswaranДокумент11 страницSliding Mode Control of SMPS: Ms. A. Jonisha, Mrs. V. Devi MaheswaranInternational Organization of Scientific Research (IOSR)Оценок пока нет

- Design and Simulation of PI Control For Positive Output Triple Lift Luo ConverterДокумент3 страницыDesign and Simulation of PI Control For Positive Output Triple Lift Luo ConverterIJMERОценок пока нет

- Ircuit Onfiguration and Perating OdesДокумент3 страницыIrcuit Onfiguration and Perating OdesMukul DasОценок пока нет

- Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial ApplicationsДокумент14 страницWide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applicationsstrngr06Оценок пока нет

- Design, Modelling and Implementation of Interleaved Boost DC-DC ConverterДокумент13 страницDesign, Modelling and Implementation of Interleaved Boost DC-DC ConverterInternational Journal of Innovative Science and Research TechnologyОценок пока нет

- Single-Inductor Multiple-Output DC-DC Converters ExplainedДокумент22 страницыSingle-Inductor Multiple-Output DC-DC Converters Explainedvietanh_askОценок пока нет

- Cascade Controller For DCDC Buck ConvertorДокумент6 страницCascade Controller For DCDC Buck ConvertorCristóbal Eduardo Carreño MosqueiraОценок пока нет

- Single-Inductor Multiple-Output Switching Converters With Time-Multiplexing Control in Discontinuous Conduction ModeДокумент12 страницSingle-Inductor Multiple-Output Switching Converters With Time-Multiplexing Control in Discontinuous Conduction ModeZhongpeng LiangОценок пока нет

- Power Systems-On-Chip: Practical Aspects of DesignОт EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardОценок пока нет

- Design and Simulation of Single Phase Z-Source Buck Boost Matrix ConverterДокумент7 страницDesign and Simulation of Single Phase Z-Source Buck Boost Matrix Convertervinay kumarОценок пока нет

- Nonisolated High Step-Up Boost Converter Integrated With Sepic ConverterДокумент10 страницNonisolated High Step-Up Boost Converter Integrated With Sepic ConverterShirlyОценок пока нет

- Low Cost' Three Phase To Single Phase Matrix ConverterДокумент6 страницLow Cost' Three Phase To Single Phase Matrix ConverterRaghu RamОценок пока нет

- An Open-Loop Stepper Motor Driver Based On FPGAДокумент5 страницAn Open-Loop Stepper Motor Driver Based On FPGADivya JamesОценок пока нет

- Sliding Mode Controller For PWM Based Buck-Boost DC/DC Converter As State Space Averaging Method in Continuous Conduction ModeДокумент5 страницSliding Mode Controller For PWM Based Buck-Boost DC/DC Converter As State Space Averaging Method in Continuous Conduction Modet.benaissaОценок пока нет

- Neural network controls DC-DC converterДокумент12 страницNeural network controls DC-DC converterRumana AliОценок пока нет

- Control H BridgeДокумент5 страницControl H BridgeFahad Al-shammeriОценок пока нет

- v4 342 349 PDFДокумент8 страницv4 342 349 PDFGlan DevadhasОценок пока нет

- Closed Loop Control Design of Two Inductor Current-Fed Isolated DC-DC Converter For Fuel Cells To Utility Interface ApplicationДокумент8 страницClosed Loop Control Design of Two Inductor Current-Fed Isolated DC-DC Converter For Fuel Cells To Utility Interface ApplicationNagababuMutyalaОценок пока нет

- A Low Cost Flyback CCM Inverter For AC Module ApplicationДокумент9 страницA Low Cost Flyback CCM Inverter For AC Module Applicationvinay kumarОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Power Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlОт EverandPower Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlРейтинг: 5 из 5 звезд5/5 (1)

- Telephone Directory: Telephone Exchange Indian Institute of Technology Roorkee ROORKEE - 247 667 June - 2017Документ72 страницыTelephone Directory: Telephone Exchange Indian Institute of Technology Roorkee ROORKEE - 247 667 June - 2017Raveendhra IitrОценок пока нет

- SEO-OPTIMIZED TITLEДокумент4 страницыSEO-OPTIMIZED TITLERaveendhra IitrОценок пока нет

- High Performance DC-DC Converter For Wide Voltage Range OperationДокумент8 страницHigh Performance DC-DC Converter For Wide Voltage Range OperationRaveendhra IitrОценок пока нет

- 0628-1 Course MinhCTaДокумент1 страница0628-1 Course MinhCTaRaveendhra IitrОценок пока нет

- Design of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemДокумент6 страницDesign of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemRaveendhra IitrОценок пока нет

- Pid3418051 PDFДокумент8 страницPid3418051 PDFRaveendhra IitrОценок пока нет

- High efficiency resonant dc-dc converter topologyДокумент7 страницHigh efficiency resonant dc-dc converter topologyRaveendhra IitrОценок пока нет

- A Novel Bidirectional Multilevel Boost-Buck DC-DC Converter: Sergio Busquets-Monge Salvador Alepuz Josep BordonauДокумент8 страницA Novel Bidirectional Multilevel Boost-Buck DC-DC Converter: Sergio Busquets-Monge Salvador Alepuz Josep BordonauRaveendhra IitrОценок пока нет

- A New Single Switch Buck-Boost Type DC-DC ConverterДокумент4 страницыA New Single Switch Buck-Boost Type DC-DC ConverterRaveendhra IitrОценок пока нет

- Study of A Non-Isolated Bidirectional DC - DC Converter: C.-C. Lin, L.-S. Yang, G.W. WuДокумент8 страницStudy of A Non-Isolated Bidirectional DC - DC Converter: C.-C. Lin, L.-S. Yang, G.W. WuPhạm Văn Tưởng100% (1)

- NeuralДокумент20 страницNeuralSai Pranahita BhaskarapantuluОценок пока нет

- Synthesis and Analysis of A Multiple-Input Parallel SC DC-DC ConverterДокумент4 страницыSynthesis and Analysis of A Multiple-Input Parallel SC DC-DC ConverterRaveendhra IitrОценок пока нет

- IEEE A4 FormatДокумент4 страницыIEEE A4 Formatprem035Оценок пока нет

- IEEE A4 FormatДокумент4 страницыIEEE A4 Formatprem035Оценок пока нет

- 06304785Документ5 страниц06304785Raveendhra IitrОценок пока нет

- 06469214Документ11 страниц06469214Raveendhra IitrОценок пока нет

- Digital Two-Loop Controller Design For Fourth Order Split-Inductor ConverterДокумент6 страницDigital Two-Loop Controller Design For Fourth Order Split-Inductor ConverterRaveendhra IitrОценок пока нет

- IEEE A4 FormatДокумент4 страницыIEEE A4 Formatprem035Оценок пока нет

- 06139542Документ5 страниц06139542Raveendhra IitrОценок пока нет

- 05751233Документ16 страниц05751233Raveendhra IitrОценок пока нет

- 04391045Документ9 страниц04391045Raveendhra IitrОценок пока нет

- 05728086Документ5 страниц05728086Raveendhra IitrОценок пока нет

- 01336616Документ7 страниц01336616Raveendhra IitrОценок пока нет

- Design of Robust Digital PID Controller For H-Bridge Soft-Switching Boost ConverterДокумент15 страницDesign of Robust Digital PID Controller For H-Bridge Soft-Switching Boost ConverterRaveendhra IitrОценок пока нет

- Based Power Tracking For Nonlinear PV SourcesДокумент8 страницBased Power Tracking For Nonlinear PV SourcesRaveendhra IitrОценок пока нет

- Dual-Mode Multiple-Band Digital Controller For High-Frequency DC-DC ConverterДокумент15 страницDual-Mode Multiple-Band Digital Controller For High-Frequency DC-DC ConverterRaveendhra IitrОценок пока нет

- 04745294Документ4 страницы04745294Raveendhra IitrОценок пока нет

- Maximum Power Point Tracking of Coupled Interleaved Boost Converter Supplied SystemДокумент10 страницMaximum Power Point Tracking of Coupled Interleaved Boost Converter Supplied SystemRaveendhra IitrОценок пока нет

- 00993245Документ9 страниц00993245Raveendhra IitrОценок пока нет

- Leapfroggers, People Who Start A Company, Manage Its Growth Until They Get Bored, and Then SellДокумент3 страницыLeapfroggers, People Who Start A Company, Manage Its Growth Until They Get Bored, and Then Sellayesha noorОценок пока нет

- Coupled Mode TheoryДокумент5 страницCoupled Mode TheoryRahul RoyОценок пока нет

- Acceptance and Presentment For AcceptanceДокумент27 страницAcceptance and Presentment For AcceptanceAndrei ArkovОценок пока нет

- Lab 2 ReportДокумент9 страницLab 2 Reportsherub wangdiОценок пока нет

- QDA Miner 3.2 (With WordStat & Simstat)Документ6 страницQDA Miner 3.2 (With WordStat & Simstat)ztanga7@yahoo.comОценок пока нет

- Mechanical PropertiesДокумент30 страницMechanical PropertiesChristopher Traifalgar CainglesОценок пока нет

- Borneo United Sawmills SDN BHD V Mui Continental Insurance Berhad (2006) 1 LNS 372Документ6 страницBorneo United Sawmills SDN BHD V Mui Continental Insurance Berhad (2006) 1 LNS 372Cheng LeongОценок пока нет

- 2.4 Adams Equity TheoryДокумент1 страница2.4 Adams Equity TheoryLoraineОценок пока нет

- The Study of Accounting Information SystemsДокумент44 страницыThe Study of Accounting Information SystemsCelso Jr. AleyaОценок пока нет

- PDF Reply Position Paper For ComplainantДокумент4 страницыPDF Reply Position Paper For ComplainantSheron Biase100% (1)

- ITIL - Release and Deployment Roles and Resps PDFДокумент3 страницыITIL - Release and Deployment Roles and Resps PDFAju N G100% (1)

- Terminología Sobre Reducción de Riesgo de DesastresДокумент43 страницыTerminología Sobre Reducción de Riesgo de DesastresJ. Mario VeraОценок пока нет

- BILL OF SALE Pre ApproveДокумент1 страницаBILL OF SALE Pre ApprovedidinurieliaОценок пока нет

- Fleck 3150 Downflow: Service ManualДокумент40 страницFleck 3150 Downflow: Service ManualLund2016Оценок пока нет

- 2011 Mid America - WebДокумент156 страниц2011 Mid America - WebFaronОценок пока нет

- Norms and specifications for distribution transformer, DG set, street light poles, LED lights and high mast lightДокумент4 страницыNorms and specifications for distribution transformer, DG set, street light poles, LED lights and high mast lightKumar AvinashОценок пока нет

- Lab - Activity CCNA 2 Exp: 7.5.3Документ13 страницLab - Activity CCNA 2 Exp: 7.5.3Rico Agung FirmansyahОценок пока нет

- MMPX 403 Parametr ListДокумент30 страницMMPX 403 Parametr ListOğuz Kağan ÖkdemОценок пока нет

- Nuxeo Platform 5.6 UserGuideДокумент255 страницNuxeo Platform 5.6 UserGuidePatrick McCourtОценок пока нет

- Product Catalog: Ductless Mini-Splits, Light Commercial and Multi-Zone SystemsДокумент72 страницыProduct Catalog: Ductless Mini-Splits, Light Commercial and Multi-Zone SystemsFernando ChaddadОценок пока нет

- Blum2020 Book RationalCybersecurityForBusineДокумент349 страницBlum2020 Book RationalCybersecurityForBusineJulio Garcia GarciaОценок пока нет

- Libros de ConcretoДокумент11 страницLibros de ConcretoOSCAR GABRIEL MOSCOL JIBAJAОценок пока нет

- Specialized Government BanksДокумент5 страницSpecialized Government BanksCarazelli AysonОценок пока нет

- Keynes Presentation - FINALДокумент62 страницыKeynes Presentation - FINALFaith LuberasОценок пока нет

- Discount & Percentage Word Problems SolutionsДокумент4 страницыDiscount & Percentage Word Problems SolutionsrheОценок пока нет

- Youtube AlgorithmДокумент27 страницYoutube AlgorithmShubham FarakateОценок пока нет

- UBI1Документ66 страницUBI1Rudra SinghОценок пока нет

- AnswersДокумент3 страницыAnswersrajuraikar100% (1)

- Structures Module 3 Notes FullДокумент273 страницыStructures Module 3 Notes Fulljohnmunjuga50Оценок пока нет

- Synopsis: A Study On Customer Satisfaction AT Nerolac Paints LTD., KadapaДокумент5 страницSynopsis: A Study On Customer Satisfaction AT Nerolac Paints LTD., KadapaAnu GraphicsОценок пока нет