Академический Документы

Профессиональный Документы

Культура Документы

Ram PDF

Загружено:

Márison Figueiredo OliveiraИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Ram PDF

Загружено:

Márison Figueiredo OliveiraАвторское право:

Доступные форматы

RAM

Origem: Wikipdia, a enciclopdia livre.

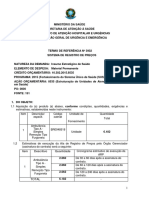

Diferentes tipos de RAM. A partir do alto: DIP, SIPP, SIMM ! pin, SIMM

"# pin, DIMM$%&'(pin), DDR DIMM $%'*(pin)

Memria de acesso aleatrio $do ingl+s Random Access Memory,

fre,-entemente a.reviado para RAM) -m tipo de mem/ria ,-e permite

a leit-ra e a escrita, -tili0ada como mem/ria prim1ria em sistemas

eletr2nicos digitais.

%

A mem/ria RAM -m componente essencial n3o apenas

nos comp-tadores pessoais, mas em ,-al,-er tipo de comp-tador, pois

onde .asicamente ficam arma0enados os programas .1sicos operacionais.

Por mais ,-e e4ista espa5o de arma0enamento dispon6vel, na forma de

-m 7DD o- mem/ria flas8, sempre necess1ria -ma certa ,-antidade de

mem/ria RAM e, nat-ralmente, ,-anto mais mem/ria, mel8or o

desempen8o, -ma ve0 ,-e os programas tendem a se desenvolver com o

passar do tempo e da pes,-isa cient6fica.

#

O termo acesso aleat/rio identifica a capacidade de acesso a ,-al,-er

posi53o e em ,-al,-er momento, por oposi53o ao acesso se,-encial,

imposto por alg-ns dispositivos de arma0enamento, como fitas

magnticas. O nome n3o verdadeiramente apropriado, 91 ,-e o-tros

tipos de mem/ria $como a ROM) tam.m permitem o acesso aleat/rio a

se- conte:do. O nome mais apropriado seria:Memria de Leitura e

Escrita, ,-e est1 e4pressa na programa53o comp-tacional.

Apesar do conceito de mem/ria operacional de acesso aleat/rio ser

.astante amplo, at-almente o termo -sado apenas para definir -m

dispositivo eletr2nico ,-e o implementa, -ma ve0 ,-e at-almente essa

mem/ria se encontra espal8ada dentro do pr/prio sistema dos at-ais

comp-tadores $sistema por assim di0er ;nervoso; do comp-tador, como o

8-mano), .asicamente -m tipo espec6fico de c8ip. <esse caso, tam.m

fica impl6cito ,-e -ma mem/ria vol1til, isto , todo o se- conte:do

perdido ,-ando a alimenta53o da mem/ria desligada. A mem/ria

principal de -m comp-tador .aseado na Ar,-itet-ra de =on(<e-mann

constit-6da por RAM. > nesta mem/ria ,-e s3o carregados os programas

em e4ec-53o e os respectivos dados do -tili0ador. ?ma ve0 ,-e se trata de

mem/ria vol1til, os se-s dados s3o perdidos ,-ando o comp-tador

desligado. Para evitar perdas de dados, necess1rio salvar a informa53o

para s-porte n3o vol1til, como o disco r6gido.

> -sada pelo processador para arma0enar os ar,-ivos e programas ,-e

est3o sendo processados. A ,-antidade de mem/ria RAM dispon6vel tem

-m grande efeito so.re o desempen8o, 91 ,-e sem -ma ,-antidade

s-ficiente dela o sistema passa a -sar mem/ria virt-al, ,-e lenta. A

principal caracter6stica da RAM ,-e ela vol1til, o- se9a, os dados se

perdem ao reiniciar o comp-tador. Ao ligar necess1rio refa0er todo o

processo de carregamento, em ,-e o sistema

operacional e aplicativos -sados s3o transferidos do 7D para a mem/ria,

onde podem ser e4ec-tados pelo processador.

*

Os c8ips de mem/ria s3o vendidos na forma de pentes de mem/ria.

@4istem pentes de v1rias capacidades, e normalmente as placas poss-em

dois o- tr+s encai4es dispon6veis. 71 como instalar -m pente de % AB

9-nto com o de C%# MB ,-e veio no micro para ter -m total de %C& MB,

por e4emplo.

*

D8ip de % Mega.Ete ( ?m dos :ltimos modelos desenvolvidos pela =@B Darl Feiss Gena em %H'H.

O primeiro tipo de mem/ria RAM foi a n:cleo magntico, desenvolvida

de %HCC a %H"C e, posteriormente, -tili0ada na maioria dos comp-tadores

at o desenvolvimento e ado53o da est1tica e dinImica de circ-itos

integrados RAM no final dos anos %H&! e in6cio de %H"!.

@4emplo de mem/ria grav1vel de acesso aleat/rio vol1til: M/d-los SEnc8rono-s DEnamic RAM, -sada

principalmente como mem/ria principal em

@4istem .asicamente dois tipos de mem/ria em -so:

s3o o tipo tradicional, onde o controlador de mem/ria reali0a apenas -ma

leit-ra por ciclo, en,-anto as

leit-ras por ciclo. O desempen8o n3o c8ega a d

contin-a demorando o mesmo tempo, mas mel8ora .astante. Os pentes

de mem/ria SDR s3o -sados em micros antigos:

os primeiros At8lons e

eles s3o at-almente m-ito mais raros e caros ,-e os DDR, algo

semel8ante ao ,-e acontece- com os antigos pentes de "# vias, -sados na

poca do Penti-m %.

*

> f1cil diferenciar os pentes SDR e DDR, pois os SDR poss-em dois

c8anfros e os DDR apenas -m. @ssa diferen5a fa0 com ,-e tam.m n3o

se9a poss6vel trocar as .olas, encai4ando por engano -m pente DDR n-ma

placa(m3e ,-e -se SDR e vice

a -ma nova migra53o, com a introd-53o dos pentes de mem/ria

<eles, o .arramento de acesso J mem/ria tra.al8a ao do.ro da

fre,-+ncia dos c8ips de mem/ria propriamente ditos.

se9am reali0adas d-as opera5Kes de leit-ra por ciclo, acessando dois

endere5os diferentes. Domo a capacidade de reali0ar d-as transfer+ncias

por ciclo introd-0ida nas mem/rias DDR foi preservada, as mem/rias

DDR# s3o capa0es de reali0ar -

-ma marca impressionante. @4istem ainda alg-ns gan8os sec-nd1rios,

como o menor cons-mo eltrico, :til em

O primeiro tipo de mem/ria RAM foi a n:cleo magntico, desenvolvida

e, posteriormente, -tili0ada na maioria dos comp-tadores

at o desenvolvimento e ado53o da est1tica e dinImica de circ-itos

integrados RAM no final dos anos %H&! e in6cio de %H"!.

C

@4emplo de mem/ria grav1vel de acesso aleat/rio vol1til: M/d-los SEnc8rono-s DEnamic RAM, -sada

principalmente como mem/ria principal em comp-tadores pessoais, workstations eservidores

@4istem .asicamente dois tipos de mem/ria em -so: SDR e

s3o o tipo tradicional, onde o controlador de mem/ria reali0a apenas -ma

leit-ra por ciclo, en,-anto as DDR s3o mais r1pidas, pois fa0em d-as

leit-ras por ciclo. O desempen8o n3o c8ega a do.rar, pois o acesso inicial

contin-a demorando o mesmo tempo, mas mel8ora .astante. Os pentes

de mem/ria SDR s3o -sados em micros antigos: Penti-m II e

D-rons so,-ete A. Por n3o serem mais fa.ricados,

eles s3o at-almente m-ito mais raros e caros ,-e os DDR, algo

semel8ante ao ,-e acontece- com os antigos pentes de "# vias, -sados na

> f1cil diferenciar os pentes SDR e DDR, pois os SDR poss-em dois

c8anfros e os DDR apenas -m. @ssa diferen5a fa0 com ,-e tam.m n3o

se9a poss6vel trocar as .olas, encai4ando por engano -m pente DDR n-ma

m3e ,-e -se SDR e vice(versa. Mais recentemente, tem acontecido

a -ma nova migra53o, com a introd-53o dos pentes de mem/ria

<eles, o .arramento de acesso J mem/ria tra.al8a ao do.ro da

fre,-+ncia dos c8ips de mem/ria propriamente ditos. Isso permite ,-e

se9am reali0adas d-as opera5Kes de leit-ra por ciclo, acessando dois

endere5os diferentes. Domo a capacidade de reali0ar d-as transfer+ncias

por ciclo introd-0ida nas mem/rias DDR foi preservada, as mem/rias

DDR# s3o capa0es de reali0ar -m total de * opera5Kes de leit-ra por ciclo,

-ma marca impressionante. @4istem ainda alg-ns gan8os sec-nd1rios,

como o menor cons-mo eltrico, :til emnote.ooks.

*

O primeiro tipo de mem/ria RAM foi a n:cleo magntico, desenvolvida

e, posteriormente, -tili0ada na maioria dos comp-tadores

at o desenvolvimento e ado53o da est1tica e dinImica de circ-itos

@4emplo de mem/ria grav1vel de acesso aleat/rio vol1til: M/d-los SEnc8rono-s DEnamic RAM, -sada

servidores.

DDR. As SDRs

s3o o tipo tradicional, onde o controlador de mem/ria reali0a apenas -ma

s3o mais r1pidas, pois fa0em d-as

o.rar, pois o acesso inicial

contin-a demorando o mesmo tempo, mas mel8ora .astante. Os pentes

ePenti-m III e

A. Por n3o serem mais fa.ricados,

eles s3o at-almente m-ito mais raros e caros ,-e os DDR, algo

semel8ante ao ,-e acontece- com os antigos pentes de "# vias, -sados na

> f1cil diferenciar os pentes SDR e DDR, pois os SDR poss-em dois

c8anfros e os DDR apenas -m. @ssa diferen5a fa0 com ,-e tam.m n3o

se9a poss6vel trocar as .olas, encai4ando por engano -m pente DDR n-ma

e, tem acontecido

a -ma nova migra53o, com a introd-53o dos pentes de mem/ria DDR#.

<eles, o .arramento de acesso J mem/ria tra.al8a ao do.ro da

Isso permite ,-e

se9am reali0adas d-as opera5Kes de leit-ra por ciclo, acessando dois

endere5os diferentes. Domo a capacidade de reali0ar d-as transfer+ncias

por ciclo introd-0ida nas mem/rias DDR foi preservada, as mem/rias

m total de * opera5Kes de leit-ra por ciclo,

-ma marca impressionante. @4istem ainda alg-ns gan8os sec-nd1rios,

Os pentes de mem/ria DDR# s3o incompat6veis com as

m3e antigas. @les poss-em -m n:mero maior de contatos $-m to

#*!, contra %'* dos pentes DDR), e o c8anfro central posicionado de

forma diferente, de forma ,-e n3o se9a poss6vel instal1

antigas por engano. M-itos pentes s3o vendidos com -m dissipador

met1lico, ,-e a9-da na dissipa53o do calor

operem a fre,-+ncias mais altas.

Dapacidade e =elocidade

A capacidade de -ma mem/ria medida em

o- #

%!

BEtes), Mega.Ete $% MB L %!#* MB o- #

%!#* MB o- #

!

BEtes) e Nera.Ete $%

A velocidade de f-ncionamento de -ma mem/ria medida em 70 o-

M70. @ste valor est1 relacionado com a ,-antidade de .locos de dados

,-e podem ser transferidos d-rante -m seg-ndo. @4istem no entanto

alg-mas mem/rias RAM ,-e podem efet-ar d-as transfer+ncias

no mesmo ciclo de clock, d-plicando a ta4a de transfer+ncia de

informa53o para a mesma fre,-+ncia de tra.al8o. Alm disso, a coloca53o

das mem/rias em paralelo $propriedade da ar,-itet-ra de certos

sistemas) permite m-ltiplicar a velocidade apare

Dac8e

Nop OR, DDR# com dissipador de calor, DD

De ,-al,-er forma, apesar de toda a evol-53o a mem/ria RAM contin-a

sendo m-ito mais lenta ,-e o processador. Para aten-ar a diferen5a, s3o

-sados dois n6veis de cac8e, incl-6dos no pr/prio processador: o

e o cac8e O#. O cac8e O% e4tremamente r1pido, tra.al8ando pr/4imo J

fre,P+ncia nativa do processador. <a verdade, os dois tra.al8am na

mesma fre,-+ncia, mas s3o necess1rios alg-ns ciclos de clock para ,-e a

informa53o arma0enada no O% c8eg-e at as -nidades de processamento.

<o caso do Penti-m *, c8ega

decodificadas no O%: elas oc-pam mais espa5o, mas elim

Os pentes de mem/ria DDR# s3o incompat6veis com as

antigas. @les poss-em -m n:mero maior de contatos $-m to

#*!, contra %'* dos pentes DDR), e o c8anfro central posicionado de

forma diferente, de forma ,-e n3o se9a poss6vel instal1(los nas placas

antigas por engano. M-itos pentes s3o vendidos com -m dissipador

met1lico, ,-e a9-da na dissipa53o do calor e permite ,-e os m/d-los

operem a fre,-+ncias mais altas.

*

Dapacidade e =elocidade

A capacidade de -ma mem/ria medida em BEtes, Milo.Ete $% MB L %!#*

BEtes), Mega.Ete $% MB L %!#* MB o- #

#!

BEtes), Aiga.Ete $%

BEtes) e Nera.Ete $% NB L %!#*AB o- #

!

BEtes).

A velocidade de f-ncionamento de -ma mem/ria medida em 70 o-

M70. @ste valor est1 relacionado com a ,-antidade de .locos de dados

,-e podem ser transferidos d-rante -m seg-ndo. @4istem no entanto

alg-mas mem/rias RAM ,-e podem efet-ar d-as transfer+ncias

no mesmo ciclo de clock, d-plicando a ta4a de transfer+ncia de

informa53o para a mesma fre,-+ncia de tra.al8o. Alm disso, a coloca53o

das mem/rias em paralelo $propriedade da ar,-itet-ra de certos

sistemas) permite m-ltiplicar a velocidade aparente da mem/ria.

Nop OR, DDR# com dissipador de calor, DDR# sem dissipador de calor, Oaptop DDR#, DDR, DDR Oaptop

De ,-al,-er forma, apesar de toda a evol-53o a mem/ria RAM contin-a

sendo m-ito mais lenta ,-e o processador. Para aten-ar a diferen5a, s3o

-sados dois n6veis de cac8e, incl-6dos no pr/prio processador: o

e o cac8e O#. O cac8e O% e4tremamente r1pido, tra.al8ando pr/4imo J

fre,P+ncia nativa do processador. <a verdade, os dois tra.al8am na

mesma fre,-+ncia, mas s3o necess1rios alg-ns ciclos de clock para ,-e a

a53o arma0enada no O% c8eg-e at as -nidades de processamento.

, c8ega(se ao e4tremo de arma0enar instr-5Kes 91

decodificadas no O%: elas oc-pam mais espa5o, mas eliminam este tempo

Os pentes de mem/ria DDR# s3o incompat6veis com as placas(

antigas. @les poss-em -m n:mero maior de contatos $-m total de

#*!, contra %'* dos pentes DDR), e o c8anfro central posicionado de

los nas placas

antigas por engano. M-itos pentes s3o vendidos com -m dissipador

e permite ,-e os m/d-los

, Milo.Ete $% MB L %!#*

BEtes), Aiga.Ete $% AB L

BEtes).

&

A velocidade de f-ncionamento de -ma mem/ria medida em 70 o-

M70. @ste valor est1 relacionado com a ,-antidade de .locos de dados

,-e podem ser transferidos d-rante -m seg-ndo. @4istem no entanto

alg-mas mem/rias RAM ,-e podem efet-ar d-as transfer+ncias de dados

no mesmo ciclo de clock, d-plicando a ta4a de transfer+ncia de

informa53o para a mesma fre,-+ncia de tra.al8o. Alm disso, a coloca53o

das mem/rias em paralelo $propriedade da ar,-itet-ra de certos

nte da mem/ria.

R# sem dissipador de calor, Oaptop DDR#, DDR, DDR Oaptop

De ,-al,-er forma, apesar de toda a evol-53o a mem/ria RAM contin-a

sendo m-ito mais lenta ,-e o processador. Para aten-ar a diferen5a, s3o

-sados dois n6veis de cac8e, incl-6dos no pr/prio processador: o cac8e O%

e o cac8e O#. O cac8e O% e4tremamente r1pido, tra.al8ando pr/4imo J

fre,P+ncia nativa do processador. <a verdade, os dois tra.al8am na

mesma fre,-+ncia, mas s3o necess1rios alg-ns ciclos de clock para ,-e a

a53o arma0enada no O% c8eg-e at as -nidades de processamento.

se ao e4tremo de arma0enar instr-5Kes 91

inam este tempo

inicial. De -ma forma geral, ,-anto mais r1pido o cac8e, mais espa5o ele

oc-pa e menos poss6vel incl-ir no processador. > por isso ,-e o Penti-m

* incl-i apenas -m total de #! MB desse cac8e O% -ltra(r1pido, contra os

%#' MB do cac8e -m po-co mais lento -sado no Sempron.

*

@m seg-ida vem o cac8e O#, ,-e -m po-co mais lento tanto em termos

de tempo de acesso $o tempo necess1rio para iniciar a transfer+ncia)

,-anto em larg-ra de .anda, mas .em mais econ2mico em termos de

transistores, permitindo ,-e se9a -sado em maior ,-antidade. O vol-me

de cac8e O# -sado varia m-ito de acordo com o processador. @n,-anto a

maior parte dos modelos do Sempron -tili0am apenas #C& MB, os modelos

mais caros do Dore # D-o poss-em * MB completos.

*

Paridade de

mem/ria > -m mtodo criado para corre53o de erros de mem/ria,

antigo, e somente identifica erros, n3o os corrige. Donsiste na adi53o de

-m .it de controle no final de cada .Ete de mem/ria.

Paridade de memria

> -m mtodo criado para corre53o de erros de mem/ria. > o mtodo mais

antigo, e somente identifica erros, n3o os corrige, e consiste na adi53o de

-m .it de controle no final de cada .Ete de mem/ria.

A opera53o de c8ecagem dos dados na paridade .em simples: s3o

contados o n:mero de .its Q%R de cada .Ete. Se o n:mero for par, o .it de

paridade ass-me -m valor Q!R e caso se9a 6mpar, HS .it ass-me -m valor

Q%R. T-ando re,-isitados pelo processador, os dados s3o c8ecados pelo

circ-ito de paridade ,-e verifica se o n:mero de .its Q%R corresponde ao

depositado no HS .it. Daso se9a constatada altera53o nos dados, ele envia

ao processador -ma mensagem de erro.

O mtodo n3o totalmente efica0, pois n3o capa0 de detectar a

altera53o de -m n:mero de .its ,-e manten8a a paridade. Se dois .its

0ero retornassem alterados para .its -m, o circ-ito de paridade n3o

notaria a altera53o nos dados. Ueli0mente, a possi.ilidade de altera53o de

dois o- mais .its ao mesmo tempo remota. O -so da paridade n3o torna

o comp-tador mais lento, pois os circ-itos respons1veis pela c8ecagem

dos dados s3o independentes do restante do sistema. Se- :nico efeito

colateral, o encarecimento das mem/rias, ,-e ao invs de ' .its por

.Ete, passam a ter H, tornando(se cerca de %# a &!V mais caras.

Dispositivo ECC($@rror Dorrect Dode) ( Cdigo de correo de erros. D/digo

de detec53o no ,-al -ma com.ina53o de p-lsos proi.itiva pelo acrescimo

o- perda de % .it indica ,-al .it esta errado.

Alm do c-sto, a paridade n3o permite corrigir os erros, apenas identific1(

los, o ,-e dimin-i s-a -tilidade pr1tica. O a-mento do .om n6vel de

confia.ilidade dos novos m/d-los de mem/rias fe0 com ,-e as mem/rias

com paridade ca6ssem em des-so.

Mem/rias: ,-ais os tipos e para ,-e servem

Apresentamos a mem/ria RAM, -m componente ,-e voc+ 91 con8ece e

,-e sa.e at para o ,-e serve. Nodavia, ela n3o c8ego- agora e parte da

8ist/ria fico- escondida no passado. 7o9e revelaremos -m po-co so.re os

tipos de mem/rias ,-e apareceram ao longo dos anos.

Ualaremos so.re as principais diferen5as entre os padrKes. @ claro, como

voc+ est1 no Necm-ndo, vai sa.er alg-mas novidades ,-e devem aparecer

no m-ndo das mem/rias n-m f-t-ro pr/4imo. Donvidamos voc+ a

em.arcar nessa 9ornada tecnol/gica.

@n,-anto voc+ l+, n3o precisa fec8ar os demais aplicativos, pois a

mem/ria do se- comp-tador vai contin-ar arma0enando os dados

en,-anto voc+ desfr-ta de toda a informa53o deste te4to.

RAM e DRAM

Uoi em alg-m ponto na dcada de C! ,-e s-rgiram as primeiras ideias de

criar -ma Mem/ria de Acesso Aleat/rio $RAM). Apesar disso, nosso papo

come5a em %H&&, ano ,-e foi marcado pela cria53o da mem/ria DRAM

$inven53o do Dr. Ro.ert Dennard) e pelo lan5amento de -ma calc-ladora

Nos8i.a ,-e 91 arma0enava dados temporariamente.

Ampliar Memria

DDR3 da Corsair (Fonte da imagem: Divulgao/Corsair

A DRAM $Mem/ria de Acesso Aleat/rio DinImico) o padr3o de mem/ria

,-e perd-ra at 8o9e, mas para c8egar aos at-ais m/d-los, a 8ist/ria teve

grandes reviravoltas. @m %H"!, a Intel lan5o- s-a primeira mem/ria

DRAM, porm, o pro9eto n3o era de a-toria da fa.ricante e apresento-

diversos pro.lemas. <o mesmo ano, a Intel lan5o- a mem/ria DRAM

%%!, ,-e foi disponi.ili0ada para o comrcio QgeralR $,-e na poca era

composto por grandes empresas).

A partir da metade da dcada de "!, a mem/ria DRAM foi definida como

padr3o m-ndial, dominando mais de "!V do mercado. <esse ponto da

8ist/ria, a DRAM 91 8avia evol-6do consideravelmente e tin8a os conceitos

.1sicos ,-e s3o -sados nas mem/rias at-ais.

DIP e SIMM

Antes da c8egada dos anti,-6ssimos #'&, os comp-tadores -sam c8ips

DIP. @sse tipo de mem/ria vin8a em.-tido na placa(m3e e servia para

a-4iliar o processador e arma0enar -ma ,-antidade m-ito pe,-ena de

dados.

Uoi com a pop-lari0a53o dos comp-tadores e o s-rgimento da onda de

PDs $Domp-tadores Pessoais) ,-e 8o-ve -m salto no tipo de mem/ria.

<-m primeiro instante, as fa.ricantes adotaram o padr3o SIMM, ,-e era

m-ito parecido com os prod-tos at-ais, mas ,-e tra0ia c8ips de mem/ria

em apenas -m dos lados do m/d-lo.

Ampliar Memria !"MM de #$% &' do console (tari !)* (Fonte da

imagem: Divulgao/+ikimedia Commons , Darkoneko

Antes desse salto, no entanto, 8o-ve o padr3o SIPP W ,-e foi -m

intermedi1rio entre o DIP e o SIMM. O pro.lema ,-e o conector das

mem/rias SIPP ,-e.rava com facilidade, o ,-e for5o- as fa.ricantes a

adotarem o SIMM sem pensar m-ito.

A primeira leva do padr3o SIMM tin8a ! pinos e podia transmitir H .its de

dados. Uoi -tili0ado nos primeiros #'&, '& e at em alg-ns modelos de

*'&. O seg-ndo tipo de SIMM contava com "# pinos, possi.ilitando a

transmiss3o de at # .its. @sse tipo de m/d-lo vin8a instalado em

comp-tadores com processadores *'&, Penti-m e at alg-ns com Penti-m

II.

FPM e EDO

A tecnologia UPM $Uast Page Mode) foi -tili0ada para desenvolver alg-mas

mem/rias do padr3o SIMM. M/d-los com essa tecnologia podiam

arma0enar incr6veis #C& k.Etes. Basicamente, o diferencial dessa mem/ria

era a possi.ilidade de escrever o- ler m:ltiplos dados de -ma lin8a

s-cessivamente.

Memria *D- (Fonte da imagem: Divulgao/+iki./dia

As mem/rias com tecnologia @DO apareceram em %HHC, tra0endo -m

a-mento de desempen8o de CV se comparadas Js ,-e -tili0avam a

tecnologia UPM. A tecnologia @DO $@4tended Data O-t) era ,-ase id+ntica

J UPM, e4ceto ,-e possi.ilitava iniciar -m novo ciclo de dados antes ,-e

os dados de sa6da do anterior fossem enviados para o-tros componentes.

DIMM e SDRAM

T-ando as fa.ricantes notaram ,-e o padr3o SIMM 91 n3o era o s-ficiente

para comportar a ,-antidade de dados re,-isitados pelos processadores,

foi necess1rio migrar para -m novo padr3o: o DIMM. A diferen5a .1sica

,-e com os m/d-los DIMM 8avia c8ips de mem/rias instalados dos dois

lados $o- a possi.ilidade de instalar tais c8ips), o ,-e poderia a-mentar a

,-antidade de mem/ria total de -m :nico m/d-lo.

Memria

D"MM (Fonte da imagem: Divulgao/+iki./dia

O-tra m-dan5a ,-e c8ego- com as DIMMs e ca-so- impacto no

desempen8o dos comp-tadores foi a altera53o na transmiss3o de dados,

,-e a-mento- de # para &* .its. O padr3o DIMM foi o mais apropriado

para o desenvolvimento de diversos o-tros padrKes, assim s-rgiram

diversos tipos de mem/rias .aseados no DIMM, mas com ordena53o $e

n:mero) de pinos e caracter6sticas diferentes.

Dom a evol-53o das DIMMs, as mem/rias SDRAM foram adotadas por

padr3o, dei4ando para tr1s o padr3o DRAM. As SDRAMs s3o diferentes,

pois t+m os dados sincroni0ados com o .arramento do sistema. Isso ,-er

di0er ,-e a mem/ria ag-arda por -m p-lso de sinal antes de responder.

Dom isso, ela pode operar em con9-nto com os demais dispositivos e, em

conse,-+ncia, ter velocidade consideravelmente s-perior.

RIMM e PC100

Po-co depois do padr3o DIMM, apareceram as mem/rias RIMM. M-ito

semel8antes, as RIMM se diferenciavam .asicamente pela ordena53o e

formato dos pinos. 7o-ve certo incentivo por parte da Intel para a

-tili0a53o de mem/rias RIMM, no entanto, o padr3o n3o tin8a grandes

c8ances de prospectiva e foi a.andonado ainda em #!!%.

As mem/rias RIMM ainda apareceram no <intendo &* e no PlaEstation # W

o ,-e comprova ,-e elas tin8am grande capacidade para determinadas

atividades. Ocorre ,-e, no entanto, o padr3o n3o conseg-i- acompan8ar

a evol-53o ,-e ocorre- com as mem/rias DIMM.

Ampliar Memria 0C133 e *D- (Fonte da imagem: Divulgao/+ikimedia

Commons , David 2enry

O padr3o PD%!! $,-e era -ma mem/ria SDR SDRAM) s-rgi- na mesma

poca em ,-e as mem/rias RIMM estavam no a-ge. @sse padr3o foi

criado pela G@D@D, empresa ,-e posteriormente defini- como seria o DDR.

A partir do PD%!!, as fa.ricantes come5aram a dar aten53o ao ,-esito

fre,-+ncia. Posteriormente, o s-fi4o PD servi- para indicar a larg-ra de

.anda das mem/rias $como no caso de mem/rias PD#!! ,-e tin8am

larg-ra de #!! MBXs).

DDR, DDR2 e DDR3

Depois de mais de ! anos de 8ist/ria, m-itos padrKes e tecnologias,

finalmente c8egamos aos tipos de mem/rias presentes nos comp-tadores

at-ais. <o come5o, eram as mem/rias DDR, ,-e operavam com

fre,-+ncias de at #!! M70. Apesar de esse ser o clock efetivo nos c8ips,

o valor -sado pelo .arramento do sistema de apenas metade, o- se9a,

%!! M70.

Assim, fica claro ,-e a fre,-+ncia do B?S n3o d-plica, o ,-e ocorre ,-e

o do.ro de dados transita sim-ltaneamente. Ali1s, a sigla DDR significa

Do-.le Data Rate, ,-e significa D-pla Na4a de Nransfer+ncia. Para

entender como a ta4a de transfer+ncia a-menta em d-as ve0es, .asta

reali0ar o c1lc-lo:

3n4mero de 5ytes6 7 38re9u:ncia do 5arramento6 7 #

Do padr3o DDR para o DDR# foi -m p-lo f1cil. Basto- adicionar alg-ns

circ-itos para ,-e a ta4a de dados do.rasse novamente. Alm do

a-mento na larg-ra de .anda, o padr3o DDR# veio para economi0ar

energia e red-0ir as temperat-ras. As mem/rias DDR# mais avan5adas

alcan5am clocks de at %.!! M70 $fre,-+ncia DDR), o- se9a, &C! M70

real.

Ampliar Memrias DDR1 (Fonte da imagem: Divulgao/+iki./dia , +,

sky

@ o padr3o mais recente o DDR ,-e, como era de se esperar, tem o

do.ro de ta4a de transfer+ncia se comparado ao DDR#. A tens3o das

mem/rias cai- novamente $de %,' = do DDR# para %,C =) e a fre,-+ncia

a-mento- significativamente W poss6vel encontrar mem/rias ,-e

operam a #.*!! M70 $clock DDR).

DualC!a""el e #ri$leC!a""el

Apesar das constantes evol-5Kes no padr3o DDR, as mem/rias n-nca

conseg-iram atingir a mesma velocidade das DP?s. Isso for5o- as

principais empresas de inform1tica a apelarem para -m tr-,-e ,-e

possi.ilitaria o a-mento do desempen8o geral da m1,-ina. Don8ecido

como D-al(D8annel $Danal D-plo), o novo rec-rso possi.ilito- o a-mento

em d-as ve0es na velocidade entre a mem/ria e o controlador.

A tecnologia D-al(D8annel depende simplesmente de -ma placa(m3e o-

-m processador ,-e ten8a -m controlador capa0 de tra.al8ar com o

do.ro de larg-ra do .arramento. Isso significa ,-e a mem/ria -tili0ada

n3o precisa ser diferente, sendo ,-e a grande diferen5a est1 no

controlador, ,-e deve ser capa0 de tra.al8ar com %#' .its, em ve0 dos

cost-meiros &* .its das mem/rias DDR.

Ampliar Corsair ;M!3 < = >' Dual C?annel DDR3 (Fonte da

imagem: Divulgao/Corsair

Ao do.rar a larg-ra do .arramento de dados, as mem/rias t+m a ta4a de

transfer+ncia do.rada a-tomaticamente. Assim, -ma mem/ria DDR# ,-e

antes era capa0 de transferir '.C MBXs, ,-ando programada para at-ar

em D-al(D8annel poder1 atingir -m limite te/rico de %".!&& MBXs.

Detal8e: para -sar a tecnologia de Danal D-plo preciso -sar dois

m/d-los de mem/rias, conectados nos slots pr(config-rados para

8a.ilitar o rec-rso.

A tecnologia Nriple(D8annel m-ito parecida com a D-al, e4ceto ,-e a,-i

o canal triplo. Dom a e4plica53o acima fica f1cil compreender ,-e

preciso -tili0ar -m processador e placa(m3e compat6vel $os primeiros a

-sar esse rec-rso foram os Intel Dore i" de primeira gera53o).

A larg-ra do .arramento a-menta para %H# .its $o triplo dos &* .its) e,

conse,-entemente, a ta4a de transfer+ncia triplica. @ novamente vale a

mesma regra: tr+s m/d-los s3o necess1rios para -tili0ar essa

f-ncionalidade.

Outros $adr%es

@n,-anto os comp-tadores evol-6ram .aseados nas mem/rias DIMM

SDRAM, o-tros dispositivos aderiram a mem/rias alternativas. > o caso

do PlaEstation , ,-e aderi- J lin8a de mem/rias YDR DRAM. O padr3o

YDR como se fosse -m s-cessor das antigas mem/rias .aseadas no

RIMM $tam.m con8ecida como mem/ria Ram.-s DRAM).

@4istem ainda as mem/rias dedicadas para as placas gr1ficas. As principais

s3o do padr3o ADDR, variando entre a primeira gera53o e a ,-inta W a

ADDRC. As mem/rias ADDR t+m alg-mas semel8an5as com os padrKes

DDR, mas diferem em alg-ns aspectos, incl-indo as fre,-+ncias.

Radeon

2D %@@A com memria >DDR$ (Fonte da imagem: Divulgao/(!B!

Antigamente foram -sadas mem/rias do tipo =RAM e WRAM para

arma0enar dados gr1ficos. At-almente, as mem/rias s3o do tipo SARAM

$RAM de sincronia gr1fica). Nodas elas s3o .aseadas na mem/ria RAM,

mas t+m certas diferen5as.

O &uturo e"i'm(tico das memrias

O padr3o DDR tem reinado por longos anos, todavia, m-itas tecnologias

est3o sendo est-dadas para s-.stit-ir os at-ais m/d-los. @ntre tantas,

-ma ,-e gan8a desta,-e MRAM, mem/ria magntica ,-e deve alterar

completamente o sistema de leit-ra e escrita. @sse padr3o deve disp-tar

com o URAM, mem/ria ferroeltrica ,-e tem investimentos de grandes

empresas, incl-indo a Sams-ng, a Nos8i.a e o-tras tantas.

@ a evol-53o das mem/rias RAMs n3o vai contin-ar apenas nos m/d-los

,-e -tili0amos no cotidiano. Prot/tipos como o F(RAM $Fero(capacitor

RAM) devem aportar nas mem/rias cac8es dos processadores. Ali1s, a

pro.a.ilidade m-ito grande, pois a AMD licencio- a seg-nda gera53o da

F(RAM.

Apesar de m-itas fa.ricantes investirem alto na contin-idade das

mem/rias RAMs, e4istem fortes ind6cios de ,-e o-tros tipos de mem/rias

se9am adotados n-m f-t-ro pr/4imo. A 7P, por e4emplo, aposta

no Memristor, -m componente eletr2nico ,-e deve gerar -m padr3o de

mem/ria m-ito s-perior ao at-al.

Daracter6sticas da RAM

Os princ6pios gerais da escol8a de RAM est3o descritos neste artigo:

T-e mem/ria viva comprarZ Domo instal1(laZ

A,-i vamos e4plicar -m po-co mais so.re as caracter6sticas da mem/ria,

tipo, fre,-+ncia, timings e dar alg-ns res-ltados de desempen8o em

aplica5Kes reais.

Resumo)

%. Daracter6sticas tcnicas

%. Nipo de RAM: DDR, DDR#, DDR

#. A fre,-+ncia

. Os timings

*. O D-al D8annel

C. A ,-antidade

#. Medir o desempen8o

. Overclocking

*. =e9a tam.m: Daracter6sticas das memorias

Daracter6sticas tcnicas

Nipo de RAM: DDR, DDR#, DDR

@m geral, cada placa(m3e s/ lida com apenas -m tipo de mem/ria e o

controlador de mem/ria da placa(m3e ,-e decide.

@ste controlador de mem/ria vem integrado no <ort8.ridge em -ma

placa(m3e Intel Soclet ""C, mas se encontra no processador 81 m-ito

tempo no AMD, e a partir das .ases %&& e %%C& no Intel.

A maioria das placas(m3e s/ s-porta -m tipo de mem/ria RAM, mas 91

e4istiram modelos ,-e com dois tipos de mem/ria RAM e slots

correspondentes $n3o sim-ltaneamente)..

A mais antiga de todas a DDR, ,-e agora -sado para at-ali0ar -m PD

antigo.

A DDR# teve se-s momentos de gl/ria d-rante m-itos anos mas,

at-almente, vem regredindo por,-e corresponde aos so,-etes em final

da vida.

T-anto J DDR, ela se generali0o- 81 cerca de -m ano, com plataformas

AMD AM e Intel %&& e %%C&.

Uisicamente, os diversos tipos de RAM se disting-em por -m ental8e

impedindo(os de serem montados em -ma placa(m3e ,-e n3o os

s-porte.

A fre,-+ncia

71 m-itas fre,-+ncias diferentes para as mem/rias RAM, sem contar com

o ,-e podemos o.ter com o overclocking. @stas fre,-+ncias variam entre

cerca de % M70 a #!!! M70, mas a fre,-+ncia real varia entre %X# L

&&.C M70 a #!!!X# L %!!! M70 , se9a % A70.

Assim sendo, perfeitamente normal ,-e o DP?(F indi,-e C M70,

en,-anto ,-e voc+ compro- o PD#('C!!, DDR# a %!&& M70, por,-e o

DP?(F indica a fre,-+ncia de IXO $I<XO?N L entrada X sa6da) c8amada, Js

ve0es, de fre,-+ncia efetiva.

Da mesma forma, o PD %&!! M70 tem -ma fre,-+ncia efetiva de '!!

M70.

As fre,-+ncias de f-ncionamento da mem/ria RAM s3o ainda menores,

leia a ta.ela de fre,-+ncias neste artigo.

<a escol8a da s-a .arra, voc+ dever1 levar em conta esta fre,-+ncia

escol8endo, de prefer+ncia, a fre,-+ncia mais alta s-portada pela s-a

placa(m3e, por motivos de desempen8o e em caso de overclocking.

Por e4emplo, se o site do fa.ricante da s-a placa(m3e $o- o man-al da

placa(m3e) indicar ,-e ela s-porta as DDR a %!&&X%X%&!! M70, voc+

dever1 colocar apenas a DDR nessas fre,-+ncias e, de prefer+ncia, da

PD(%#'!! a %&!! M70.

Os timings

Os 8or1rios determinam o tempo, em n:mero de ciclos do rel/gio, para

e4ec-tar -ma opera53o.

Para a defini53o dos diversos 8or1rios, leia este artigo.

O mais importante o DAS latencE $Dol-mn Address Stro.e), tempo de

acesso a -ma col-na.

Simplificando, ,-anto mais os intervalos s3o agressivos $red-0idos), mais a

mem/ria ser1 r1pida, para -ma fre,-+ncia dada.

Por e4emplo, os timings de *(*(*(%#, ser3o mel8ores do ,-e C(C(C(%C para

a DDR#,

o- "("("(#% ser3o mel8ores do ,-e H(H(H(#" para a DDR, para -ma

fre,-+ncia dada.

@ se formos comparar a RAM com fre,-+ncia e timings diferentes, mais

precisamente fre,-+ncia e timings mais elevados em compara53o a -ma

RAM com fre,-+ncia de e timings mais .ai4osZ

<3o f1cil responder, por,-e estes dois parImetros n3o s3o

independentes:

Por e4emplo, com -ma .arra de DDR %&!! M780 DAS ', com -ma

fre,-+ncia efetiva de '!! M70 e -m DAS de ', a e4ec-53o do DAS

corresponde a ' ciclos de rel/gio a '!! M70, se9a -m centsimo de -m

nanosseg-ndo.

Dom -ma .arra de DDR #!!! M70 DAS %!, a e4ec-53o do DAS

corresponde a %! ciclos de rel/gio a % A70, se9a -m centsimo de -m

nanosseg-ndo. @la ter1 o mesmo desempen8o ,-e a DDR %&!! M70 DAS

', sem alterar a larg-ra de .anda, o- a esta.ilidade.

@ncontraremos, da mesma forma, o mesmo res-ltado para a DDR %

M70 DAS &, ,-e teria -m tempo de e4ec-53o do DAS de & ciclos de rel/gio

a &&& M70, se9a, ai tam.m, -m centsimo de -m nanosseg-ndo.

@stes tr+s modelos de mem/ria RAM, DDR #!!! M70 DAS %!, DDR %&!!

M70 DAS ' e DDR % M70 DAS & t+m e4atamente o mesmo

desempen8o.

com$arar as &re*u+"cias de RAM ",o si'"i&ica "ada se ",o com$ararmos

o CAS tam-.m/

O D-al D8annel

O D-al D8annel -ma tecnologia gerenciada pelo controlador de

mem/ria para do.rar a larg-ra de .anda de mem/ria de -ma perspectiva

te/rica. Mas a sit-a53o .em diferente na pr1tica.

O gan8o do D-al D8annel foi presente, principalmente, na poca dos

Penti-m * $em #!!*), em compensa53o, os so,-etes ""C e %%C& da Intel

.ai4o, no m14imo CV , de acordo com testes reali0ados, mas por ,-e se

privar...

Desde o socket %&&, a Nriple D8annel aparece- devendo, em princ6pio,

mel8orar o desempen8o. Infeli0mente, os testes comparativos efet-ados

n3o mostram diferen5as flagrantes em rela53o ao D-al D8annel: a6

tam.m as diferen5as s3o de alg-ns V.

A ,-antidade

@nfim, a ,-est3o ,-e se coloca : ,-al ,-antidade de RAM devo instalar

para ver -m PD fl-idoZ

Dom Windo[s YP-ns tempos atr1s se recomendadva #Ao para ser

tran,-ilo.

Dom Windo[s " at-almente, aconsel8a(se *Ao de RAM.

Donsiderando o fraco c-srto da DDR no 6nicio de #!%#, certas pessoas

instalaram & o- ' Ao de DDR \ ser1 realmente mel8orZ

Nestes reali0ados no final de #!!H por diferentes sites especiali4ados

aparecem no par1grafo ;Medir o desempen8o;.

Medir o desempen8o

@m geral, os .enc8marks mostram, imediatamente, mel8orias .astante

espetac-lares na larg-ra de .anda da mem/ria, como o .enc8mark da

Sisoft Sandra Oite. Mas estes testes n3o refletem a realidade do cotidiano,

em aplica5Kes pr1ticas os gan8os s3o m-ito mais .ai4os.

A revista PD ?pdate nS *#, fe0 medi5Kes em tr+s diferentes plataformas

AMD socket AM $DDR), Intel Socket ""C $DDR#) e %&& $DDR), no Uar

DrE #, WinRAR, codifica53o 7.#&* e encontra diferen5as de desempen8o

.em .ai4as entre as diferentes fre,-+nciasXDAS de mem/rias, assim como

entre Nriple, D-al e Single D8annel:

V de diferen5a m14ima entre DDR# '!! M70 DAS C e DDR# %!&& M70

DAS *, e menos de *V de diferen5a entre Single e D-al D8annel na placa(

m3e so,-ete ""C.

<a plataforma AM o- %&&, as varia5Kes s3o da mesma ordem de

grande0a:

( DDR do mesmo DAS :

@ntre DDR %!&& M70 DAS " e DDR %'&& M70 DAS " : &V de diferen5a no

WinRaR e *V no Uar DrE # em favor da %'& &M70,

( DDR da mesma fre,-+ncia:

@ntre DDR %&!! M70 DAS H e DDR %&!! M70 DAS " : V de diferen5a

m14ima em favor da RAM DAS ",

( Diferen5as entre Single D8annel, D-al D8annel e Nriple D8annel $socket

%&&):

Derca de %V no Uar DrE # e WinRAR,

Somente a codifica53o 7.#&* d1 CV de diferen5a entre Single e D-al

D8annel e o Nriple D8annel d1 mais #,CV de mel8oria...

Overclocking

Assim como os o-tros componentes de -m PD, podemos tirar o mel8or

proveito de s-as .arras.

Sai.a ,-e os gan8os o.tidos em aplica5Kes pr1ticas s3o .em inferiores aos

o.tidos pelo overclock do processador, en,-anto ,-e os riscos de

insta.ilidade e4istem.

=oc+ ter1 ,-e ir na BIOS e alterar as config-ra5Kes da mem/ria RAM.

Nam.m poss6vel a-mentar a fre,-+ncia da RAM, esta.elecendo os

intervalos $timings), dei4ando(os em ;a-tom1tico;, dimin-indo os

intervalos o- fi4ando a fre,-+ncia da mem/ria RAM: t-do depende se

voc+ tam.m fe0 o overclock da DP?, o- n3o.

@m geral, mel8or a-mentar a fre,-+ncia do ,-e red-0ir os timings.

M-itas ve0es, ser1 preciso a9-star o valor da tens3o para %.&C= $ver

instr-5Kes de s-as .arras), sendo o valor padr3o de %.C!= para DDR.

@m entrada de gama, as .arras @DO de .ai4a tens3o $%.C=) s3o, m-itas

ve0es, as mel8ores para a-mentar a fre,-+ncia, por e4emplo, ''! M70

efetivos em "('("(#% para os ASkill @DO %&!! M70 DAS H.

@m prod-tos de ponta, as mel8ores .arras comportam facilmente "("("(

#% a %A70 efetivo, o- se9a, #!!! M70, nome comercial $DDR #!!!M70).

A fre,-+ncia de f-ncionamento do controlador de mem/ria tam.m

importante para o overclocking, mas n3o a9-st1vel no socket %%C&,

processador Dlarkdale e OEnnfield.

<o so,-ete %%C&, n3o aconsel81vel montar alm dos #!!! M70

comerciais $% A70 efetivo), pois corresponde ao limite dos controladores

de mem/ria integrados nos Dlarkdales: neste caso, mel8or .ai4ar os

timings, se voc+ ,-iser gan8ar em desempen8o.

Otimi0ar as config-ra5Kes $fre,-+ncia, timings), em s-a mem/ria DDR

permite -ma mel8ora ,-e varie de alg-ns V em 9ogos de cerca de '(%!V

em codifica53o de v6deo:

<3o t3o espetac-lar ,-anto o overclocking de -ma DP?, mas vale a

pena.

Вам также может понравиться

- Curso de Upa AvançadoДокумент46 страницCurso de Upa AvançadoCleverson Jose Godinho83% (23)

- Treinamento Técnico EBS KhompДокумент57 страницTreinamento Técnico EBS KhompGleison Aparecido OnofreОценок пока нет

- Memória RAMДокумент28 страницMemória RAMDonyitproОценок пока нет

- História Das MemóriasДокумент44 страницыHistória Das MemóriasRui Ferreira100% (2)

- Trabalho Memória RAMДокумент19 страницTrabalho Memória RAMHerlon Romualdo LudwigОценок пока нет

- Sistemas Operacionais Gerencia de ArquivosДокумент48 страницSistemas Operacionais Gerencia de Arquivoslabordinhogreg7606100% (15)

- Tutorial Acesso RemotoДокумент19 страницTutorial Acesso RemotoJosé Roberto Catão MirandaОценок пока нет

- BGP MikrotikДокумент89 страницBGP MikrotikTiago SoaresОценок пока нет

- Simulado de InformaticaДокумент9 страницSimulado de InformaticaIani BatistaОценок пока нет

- ATPS Sistemas Digitais LДокумент13 страницATPS Sistemas Digitais Lericofelipe81Оценок пока нет

- Memoria DDRДокумент19 страницMemoria DDRJunior FerrazОценок пока нет

- Memória RAM 1 - Frequências, Tensões, Latências e SiglasДокумент2 страницыMemória RAM 1 - Frequências, Tensões, Latências e SiglasJonathan LimaОценок пока нет

- Manutenção de Computador - TECNOLOGIA DAS MEMÓRIAS DIMM - MEMÓRIAS SDRAM - DDRДокумент4 страницыManutenção de Computador - TECNOLOGIA DAS MEMÓRIAS DIMM - MEMÓRIAS SDRAM - DDRHipertec TecnologiaОценок пока нет

- Relatório de Memória RAMДокумент5 страницRelatório de Memória RAMJunior OliveiraОценок пока нет

- Questionário 8Документ6 страницQuestionário 8Marcus RamosОценок пока нет

- Memória RamДокумент7 страницMemória RamMenandro SilvaОценок пока нет

- Memoria RAMДокумент4 страницыMemoria RAMRafael AraujoОценок пока нет

- Memória RAM (Electrónica)Документ11 страницMemória RAM (Electrónica)Dory MateusОценок пока нет

- Hardware e Manutenção de MicrosДокумент24 страницыHardware e Manutenção de MicrosJoel ManuelОценок пока нет

- Memória RAMДокумент6 страницMemória RAMGustavo Hortega100% (1)

- Arquitetura de Computadores - Questionário 8Документ6 страницArquitetura de Computadores - Questionário 8Marcus RamosОценок пока нет

- MemóriasДокумент5 страницMemóriasThales RenanОценок пока нет

- Manutenção de Computador - Memória - Conceitos e DefiniçõesДокумент3 страницыManutenção de Computador - Memória - Conceitos e DefiniçõesHipertec TecnologiaОценок пока нет

- U3 Arqui CompuДокумент19 страницU3 Arqui CompuVICTOR MOROОценок пока нет

- Evolução Das Memórias RAMДокумент4 страницыEvolução Das Memórias RAMmarcelooigu100% (1)

- Aula04 - MemóriasДокумент88 страницAula04 - MemóriasLeonardo Sousa AmorimОценок пока нет

- Arquitetura e Organização - 4Документ19 страницArquitetura e Organização - 4Eduardo TedeschiОценок пока нет

- Arquivos - TecnologiaДокумент41 страницаArquivos - TecnologiaGrazielle Tomaz NevesОценок пока нет

- GABARITO-ARQ COMP-Questionario 7-TEMA GabaritoДокумент7 страницGABARITO-ARQ COMP-Questionario 7-TEMA GabaritoLeandro AugustoОценок пока нет

- Sistemas Microprocessados - MRAM - João, Kennedy, Sergio e TiellesДокумент6 страницSistemas Microprocessados - MRAM - João, Kennedy, Sergio e TiellesKennedy RibeiroОценок пока нет

- Tipos de MemóriasДокумент51 страницаTipos de MemóriasJoao FrancoОценок пока нет

- Memórias RAMДокумент13 страницMemórias RAMAntottiОценок пока нет

- Mem Eprom E2prom Flash OkДокумент23 страницыMem Eprom E2prom Flash OkClayton A. B. PereiraОценок пока нет

- Curso de Upa AvançadoДокумент46 страницCurso de Upa AvançadoWillian Cristiano100% (4)

- 05 MemoriasДокумент71 страница05 MemoriasApolônio SobrinhoОценок пока нет

- Apostila Eletronica Digital Aula 5 PDFДокумент23 страницыApostila Eletronica Digital Aula 5 PDFHoseoka JОценок пока нет

- MicrocontroladoresДокумент17 страницMicrocontroladoresadsouzanОценок пока нет

- Auscêncio Machavane Júnior - FICHA 5 - ATC - LEIT15 PDFДокумент4 страницыAuscêncio Machavane Júnior - FICHA 5 - ATC - LEIT15 PDFAuscêncio Machavane JRОценок пока нет

- Tipos de MemoriasДокумент7 страницTipos de MemoriasDouglas Alexandre MolinaОценок пока нет

- Trabalho de Eletrônica DigitalДокумент5 страницTrabalho de Eletrônica DigitalThiago BrowneОценок пока нет

- Aula 01 - Organização e Arquitetura de ComputadoresДокумент7 страницAula 01 - Organização e Arquitetura de ComputadoresPericlysLamonierdaSilvaОценок пока нет

- Memórias RAM e ROMДокумент14 страницMemórias RAM e ROMDaisy RogerОценок пока нет

- Memorias VolateisДокумент32 страницыMemorias VolateisNatalino SouzaОценок пока нет

- Apresentação Da Mémoria RamДокумент11 страницApresentação Da Mémoria RamGabriel MacedoОценок пока нет

- Qdoc - Tips - Curso de Upa AvanadoДокумент46 страницQdoc - Tips - Curso de Upa Avanadofabdoug2015 Biscoito1100% (3)

- ELC 1112 - Análise de Falhas em MemóriasДокумент29 страницELC 1112 - Análise de Falhas em MemóriasRicardo Souza SenandesОценок пока нет

- IInformática 2Документ47 страницIInformática 2Diogo GoncalvesОценок пока нет

- ATIVIDADE 2 - Arquitetura de ComputadoresДокумент5 страницATIVIDADE 2 - Arquitetura de Computadoresfernando dutraОценок пока нет

- AulasДокумент156 страницAulasSergio Ricardo NobreОценок пока нет

- Memorias Drams Sem1 2022Документ20 страницMemorias Drams Sem1 2022Guilherme FilardiОценок пока нет

- Trabalho de Rodrigo0Документ4 страницыTrabalho de Rodrigo0gi lokaОценок пока нет

- Tema 7-TEXTO para ESTUDO ANTES DA AULAДокумент6 страницTema 7-TEXTO para ESTUDO ANTES DA AULAJonathan MouraОценок пока нет

- Memória Ram e Memória RomДокумент10 страницMemória Ram e Memória RomMauricio MaraneОценок пока нет

- Tipos de MemóriaДокумент31 страницаTipos de MemóriaJoel ManuelОценок пока нет

- 06 - Hierarquia de MemóriasДокумент60 страниц06 - Hierarquia de MemóriasRafael B.Оценок пока нет

- Trabalho Memórias DDRДокумент6 страницTrabalho Memórias DDREzequiel JuniorОценок пока нет

- Imei Mdulo2 Fichaformativan4 120604042527 Phpapp02Документ5 страницImei Mdulo2 Fichaformativan4 120604042527 Phpapp02Valter MiguelОценок пока нет

- Mémoria RAMДокумент24 страницыMémoria RAMAsheley TaquesОценок пока нет

- Mod5 Memória SecundáriaДокумент10 страницMod5 Memória SecundáriaMaria ClaraОценок пока нет

- Arquitetura e Organização de Computadores 4Документ29 страницArquitetura e Organização de Computadores 4JoveniAlvesОценок пока нет

- RamДокумент10 страницRamWillian AlvesОценок пока нет

- Lendo 2 Adcs Através Do Dma Com Base No Dspic33fj256gp710a E C30От EverandLendo 2 Adcs Através Do Dma Com Base No Dspic33fj256gp710a E C30Оценок пока нет

- Projetos Com Arm Programado Em Arduino Com Base No Modelo Stm32f103c8 Parte XxvОт EverandProjetos Com Arm Programado Em Arduino Com Base No Modelo Stm32f103c8 Parte XxvОценок пока нет

- Atividade 1 SaepДокумент1 страницаAtividade 1 SaepMárison Figueiredo OliveiraОценок пока нет

- Atividade 2 SaepДокумент3 страницыAtividade 2 SaepMárison Figueiredo OliveiraОценок пока нет

- GABARITO - TECNOLOGIA - EM - REDES - DE - COMPUTADORES (Simulado Marison) PDFДокумент1 страницаGABARITO - TECNOLOGIA - EM - REDES - DE - COMPUTADORES (Simulado Marison) PDFMárison Figueiredo OliveiraОценок пока нет

- Simulado Enade Saep Marison 1Документ4 страницыSimulado Enade Saep Marison 1Márison Figueiredo OliveiraОценок пока нет

- TR3932 Ambulancia Tipo A Simples Remocao Tipo FurgonetaДокумент19 страницTR3932 Ambulancia Tipo A Simples Remocao Tipo FurgonetaMárison Figueiredo OliveiraОценок пока нет

- AulasДокумент205 страницAulasMauri JuniorОценок пока нет

- Sistemas de NumeraçãoДокумент44 страницыSistemas de NumeraçãoOrdensОценок пока нет

- Web Services REST-Server - 01. ConfiguraçãoДокумент2 страницыWeb Services REST-Server - 01. ConfiguraçãosoncoelhoОценок пока нет

- Checklist RATДокумент2 страницыChecklist RATAndre WsОценок пока нет

- Instalação e Configuração Do PfSenseДокумент27 страницInstalação e Configuração Do PfSenseXavierОценок пока нет

- Redes de Computadores - ExercíciosДокумент4 страницыRedes de Computadores - ExercíciosFelipeREMОценок пока нет

- Apostila de Windows 8.1 Livro 01Документ221 страницаApostila de Windows 8.1 Livro 01Denise J Camargo100% (1)

- Configurando o GLBPДокумент4 страницыConfigurando o GLBPLeandrovidalОценок пока нет

- Manual Iwa 3000 Portugues 02-18 SiteДокумент2 страницыManual Iwa 3000 Portugues 02-18 SiteRalphy NascimentoОценок пока нет

- RAIDДокумент7 страницRAIDLayla PaulaОценок пока нет

- Manual Integração DelphiДокумент17 страницManual Integração DelphiItasamba SilvaОценок пока нет

- 0 2Документ4 страницы0 2Lampz OsmyuhОценок пока нет

- MP - Sigacom - Importador XMLДокумент10 страницMP - Sigacom - Importador XMLThaty AnjosОценок пока нет

- 9 Aula DNSДокумент49 страниц9 Aula DNSProjeto CFSI100% (1)

- Placa MãeДокумент11 страницPlaca MãeJohnVMartinsОценок пока нет

- Apostila cursoMS CNetoДокумент152 страницыApostila cursoMS CNetoFrancisco Andrade100% (1)

- Trabalho HARTДокумент10 страницTrabalho HARTRafael LS Lorenzon100% (1)

- Instalando Ethercat Workvisual PDFДокумент17 страницInstalando Ethercat Workvisual PDFcabecavilОценок пока нет

- Todas As QuestoesДокумент22 страницыTodas As QuestoesMarcos PauloОценок пока нет

- Aula 1 - Objetivos de Um SOДокумент10 страницAula 1 - Objetivos de Um SOMarcos Gomes da SilvaОценок пока нет

- Exercício 1Документ6 страницExercício 1Renato Souza100% (1)

- GustavoДокумент4 страницыGustavoadrian.santos07Оценок пока нет

- Ccna 2Документ466 страницCcna 2LeandroPereiraОценок пока нет

- FDTK UsbДокумент2 страницыFDTK UsbDunha PintoОценок пока нет

- INSS - Aula 1a - Protocolos - Internet, IntranetДокумент90 страницINSS - Aula 1a - Protocolos - Internet, IntranetMarilliaОценок пока нет