Академический Документы

Профессиональный Документы

Культура Документы

New Cascaded Multilevel Inverter Topology With Reduced Number of Switches PDF

Загружено:

raghuevmИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

New Cascaded Multilevel Inverter Topology With Reduced Number of Switches PDF

Загружено:

raghuevmАвторское право:

Доступные форматы

New Cascaded Multilevel Inverter Topology with Reduced Number of Switches

and Sources

Seyed Hossein Hosseini

1

, Amir Farakhor

2

, and Saeideh Khadem Haghighian

1

1

Faculty of Electrical and Computer Engineering, University of Tabriz, Tabriz, Iran

hosseini@tabrizu.ac.ir, khademhaghighian.s.k@ieee.org

2

Department of Electrical Engineering, Azarbaijan Shahid Madani University, Tabriz, Iran

Amir.farakhor.2013@ieee.org

Abstract

This paper presents a novel topology for cascaded multilevel

inverters. The proposed topology employs less number of

components. This structure consists of a single DC voltage

source, several low-frequency transformers and switching

devices. There are two switching devices in each module of

the proposed structure and there is only a module with three

power switches. However, in conventional cascaded H-bridge

multilevel inverters four switches are used in each module.

The number of gate drivers are reduced respectively along

with the switches which results in smaller size, lower cost,

lower power consumption in driving circuits and higher

efficiency. To verify the performance of the proposed

structure, Simulation results carried out by PSCAD/EMTDC

and a low-power experimental setup was used to test the

converter in practice.

1. Introduction

The elementary concept of a multilevel converter to achieve

higher power is to use a series of power semiconductor switches

with several lower voltage DC sources to perform the power

conversion by synthesizing a staircase voltage waveform.

Capacitors, batteries, and renewable energy voltage sources can

be used as the multiple DC voltage sources [1]. The

commutation of the power switches aggregates these multiple

DC sources in order to achieve high voltage at the output.

However, the rated voltage of the power semiconductor switches

depends only upon the rating of the DC voltage sources to

which they are connected. Numerous industrial applications

have begun to require higher power apparatus in recent years.

Some medium voltage motor drives and utility applications

require medium voltage and megawatt power level. As a result, a

multilevel power converter structure has been introduced as an

alternative in high power and medium voltage situations [2].

Multilevel converters can be divided into four remarkable

topologies: diode-clamped multilevel converter (DCMC) [3],

flying capacitors multilevel converter (FCMC) [4], P2

Multilevel converter (P2MC) [5] and cascaded multilevel

converter (CMC) with separate DC sources [6]. Compared to m-

level DCMC, FCMC, and P2MC, which use m-1 capacitors on

the dc bus, the CMC uses only (m-1)/2 capacitors for the same

m-level output voltage. Clamping diodes are not required for

FCMC, P2MC and CMC. In overall P2MC undeniably require

too many components as compared to other multilevel

converters so it is not suitable for higher voltage levels [7].

However, comparing CMC with DCMC, FCMC and P2MC, it

requires minimum number of components and its dominant

advantage is the circuit layout with flexibility. But a primary

disadvantage of the CMC is that it requires a separate DC source

for each H-Bridge module, which yields significant cost [8].

Another clear disadvantage of multilevel power conversion is

the great number of power semiconductor switches needed.

Although low-voltage-rated switches can be utilized in a

multilevel converter, each switch requires a related gate driver

and protection circuits. This may lead the overall system to be

more expensive and complex [9]. Therefore, in practical

implementation, reduction of the number of switches and gate

driver circuits is very important. Many topologies of multilevel

inverters using a reduced number of switches and gate-driver

circuits are presented in recent years [1012].

In this paper a new topology for cascaded transformer H-

Bridge multilevel inverter is presented which employs one DC

voltage source and several isolated single-phase low-frequency

transformers. There are two switches in each module except the

last module which consists of three switching devices. Using

fewer switching devices respectively, fewer gate drivers result in

smaller implementation size and lower cost. To verify the

validity of the proposed multilevel inverter, simulation and

experimental results are provided.

2. Conventional Cascaded Multilevel Inverters

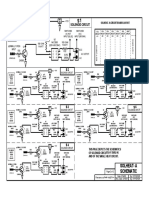

The circuit configuration of a cascaded H-bridge multilevel

inverter is depicted in Fig. 1. As it is shown in Fig. 1, there are

four H-bridge modules in this structure. Therefore, nine-level

output voltage can be synthesized. Each H-bridge module can

generate three voltage levels positive, negative and zero

according to its different switching states. The outputs of H-

bridge modules are series connected in order to generate a

stepwise output voltage. The main disadvantage of this structure

is that each H-bridge module requires independent DC voltage

sources.

Fig. 2 shows the cascaded transformer H-bridge multilevel

inverter which only requires a single DC voltage source. Each

H-bridge module is connected to a low-frequency transformer.

The secondary sides of the transformers are series connected to

synthesize the stepwise output voltage.

In both structures shown in Fig. 1, 2, four switches are

employed in each H-bridge module. Respectively, four gate

driver circuits are required in each H-bridge module. However,

the number of components used in these structures could be

reduced which result in lower implementation cost, smaller size,

higher efficiency and simplicity of the structure.

97

Fig. 1. Cascaded H-bridge multilevel inverter

Fig. 2. Cascaded transformer H-bridge multilevel inverter

3. Proposed Multilevel Inverter

Among multilevel inverter structures, cascaded H-bridge

inverters have the advantage of being modular. It is easily

expandable for higher output voltage levels. Therefore, the

output voltage resembles to sinusoidal waveform as the number

of modules increases. Higher number of H-bridge modules

requires excessive number of semiconductor switches and other

components which increases the size and the cost of the circuit.

The proposed structure is shown in Fig. 3. The proposed

structure consists of a single DC voltage source, several low-

frequency transformers and fewer number of switching

components in comparison to conventional multilevel inverters.

As it is shown in Fig. 3, each module comprises of two

switching components except the last module which includes

two typical switches and one bidirectional switch. Each module

is connected to a transformer. Secondary sides of the

transformers are series connected to generate the output voltage.

Considering K as the number of transformers in this

structure, the number of switching devices can be obtained as

follows:

1 2 SW K (1)

Where SW is the number of switches. Assuming m as the

number of output voltage level, the number of switches with

respect to the output voltage level is given as follows:

SW m (2)

The output voltage can be obtained as follows:

1 2 output o o ok V V V V ok Vo (3)

If all turn-ratios of transformers in Fig. 3 are equal then the

inverter is known as uniform step symmetric multilevel inverter.

Fig. 3. Circuit configuration of the proposed inverter

3.1. Operation of Proposed Inverter

To demonstrate the operation of the proposed inverter, a

nine-level configuration, which is shown in Fig. 4, is used. As it

is shown in Fig. 4, the structure consists of four transformers,

eight unidirectional switches and a bidirectional switch. There

are also four modules in this structure. Each module can

generate two voltage levels positive (+Vdc) and negative (-Vdc)

except the last module with three switches which can create

three voltage levels positive (+Vdc), zero, negative (-Vdc).

Therefore, the zero voltage level can only be generated by the

last module with three switching devices. The maximum output

voltage level can be generated from this structure is +4Vdc.

Table 1 shows the switching pattern of the inverter shown in

Fig. 4 for different output voltage levels. It is worth noting that

various switching states are possible for the same voltage level.

For instance, to generate the output voltage of the +Vdc,

switches S1, S3, S6 and Sbidirectional are turned on. It is also

possible to obtain the same output voltage by turning on the

switches S1, S4, S5 and Sbidirectional.

There are several modulation strategies for multilevel

inverters and operation of them depends on modulation

strategies [13 15]. The modulation methods used in multilevel

inverters can be categorized according to switching frequency.

In this paper, the fundamental frequency switching technique

has been employed. It is important to note that the calculation of

optimal switching angles for different purposes such as

elimination of the selected harmonics and minimizing THD are

not the objective of this paper.

Fig. 4. Circuit configuration of nine-level inverter

98

Table 1. Output voltage for various states of switches

Output Voltage

Level

S1 S2 S3 S4 S5 S6 S7 S8 S bidirectional

+4Vdc On Off On Off On Off On Off Off

+3Vdc On Off On Off On Off Off Off On

+2Vdc On Off On Off On Off Off On Off

+Vdc On Off On Off Off On Off Off On

0 On Off On Off Off On Off On Off

-Vdc Off On Off On On Off Off Off On

-2Vdc Off On Off On Off On On Off Off

-3Vdc Off On Off On Off On Off Off On

-4Vdc Off On Off On Off On Off On Off

3.2. Voltage and Current Ratings of the Switches

There are two important criteria for selecting the proper

switching devices peak inverse voltage (PIV) and current rating.

Considering the input DC voltage 2 per unit (P.u), the PIV of

the all switches are 2 P.u except the bidirectional switch which

has the PIV of 1 P.u. The PIV of the all switches can be

calculated as follows:

2 1 Total PIV m (3)

Assuming the load current 1 P.u, the current ratings of all the

switches are 1 P.u.

In comparison with the conventional cascaded H-bridge

inverter, the PIV of the switches in the proposed inverter is

higher.

3.3. Comparison Study

The present paper aims to reduce the number of components

used in multilevel inverter. There is only a single DC source

used in this structure. The number of switching devices required

to realize an m-level output voltage in conventional cascaded H-

bridge inverters is as follows:

2 2 SW m (4)

The numbers of switches in the proposed structure are

compared with the cascaded H-bridge multilevel inverter in Fig.

5. As it is shown in Fig. 5, the proposed structure requires fewer

switching components. Each switching device requires a gate

driver to operate. Therefore, reduction in the number of

switching devices also results in fewer number of gate drivers

which leads to a smaller size and lower cost of the

implementation.

The number of on switches is also an important criterion to

compare the structures. There are two on switches in each

module of the conventional H-bridge inverter. However, the

number of on switches in each module of the proposed inverter

is one. More number of on switches means more voltage drop

on these switches. The number of on switches for an m-level

output voltage in conventional cascaded H-bridge inverter can

be calculated as follows:

1 on N m (5)

The number of on switches in the proposed structure

can be given as follows:

1

2

on

m

N

(6)

Where m is the number of output voltage levels.

Fig. 5. Comparison of switches to realize m-level voltages

4. Simulation and Experimental Results

The simulation results are carried out by PSCAD/EMTDC

with consideration of an R-L load (R=50 , L=0.5 mH)for a

nine-level structure shown in Fig. 4. In this simulation, input

voltage is equal (Vdc=20 V) and the turn-ratios of

transformers are chosen as 1:1. Fig. 6 -8 show waveforms of

output voltage (vout) of the modules 1-3 , respectively and as

shown in these figures , the transformer output voltage of each

module for all times has negative or positive values. Fig. 9

illustrates , the transformer voltage of fourth module and it has

negative, positive or zero values. In this proposed multilevel

inverter, fourth module uses bidirectional switch for

generating the zero voltage level.

The secondary sides of the transformers are series connected

in order to create a stepwise output voltage. Consequently, as

shown in Fig. 10, the final output voltage becomes the sum of

the terminal voltage of all modules also Fig. 11 shows load

current. The output voltage has a waveform close to a sinusoidal

waveform, 50 Hz voltage with amplitude 40 V. in Fig. 12 the

frequency spectrum of output voltage is illustrated, the

THD of the output voltage is found as 10.41%.

99

Fig. 6. Output voltage of transformer T1

Fig. 7. Output voltage of transformer T2

Fig. 8. Output voltage of transformer T3

Fig. 9. Output voltage of transformer T4

Fig. 10. Stepwise output voltage (Vdc=20 v)

Fig. 11. Load current

Fig. 12. Frequency spectrum of output voltage

To verify the performance of the proposed inverter

experimentally, a prototype has been built in the laboratory

scale. In order to validate the proposed concept, the inverter of

was constructed and tested in the 9-level mode. To get 9 output

voltage levels of the inverter, the ratio of transformers are set to

1:1. The DC sources were supplied by a battery sources that has

a voltage of 50V. This multilevel generates staircase waveform

with maximum 100 V and 50Hz. The common MOSFET with

internal anti-parallel diodes has been used in prototype. For

every module, only two switches are used with a single-phase

transformer. In module 4 a bidirectional switch is applied. The

MOSFETs are the types IRFP460 with voltage and current

ratings equal to 500V and 10 A, respectively. The ATMEGA32-

8PT microcontroller by ATMEL Company has been used to

generate the switching patterns and the opt coupler TLP521-1 is

used to drive switches.

100

Fig. 13 shows the output voltage of proposed inverter. As it

can be seen, the results verify the ability of proposed inverter in

generation of desired output voltage. Consequently, we can say

that the proposed topology is more advantageous in switch and

DC voltage source cost compared with the conventional

cascaded multilevel inverter because the proposed topology can

reduce the number of switches and DC voltage sources.

Fig. 13. Measured output voltage (Vdc=50 v)

5. Conclusions

In this paper, a novel topology for cascaded multilevel inverters

is presented. The proposed structure benefits from the advantage

of fewer numbers of components. The number of switching

devices as well as the number of gate drivers is reduced in the

proposed topology. Therefore, the size and the cost of

implementation are decreased. To validate the proper operation

of the proposed structure, simulation and experimental results

are provided.

6. References

[1] P. Panagis, P. Stergiopolos, S. Manios, "Comparison of st

at e of t he art mul t i l evel i nvert ers ", Proc. Power

Electronics Specialists Conf., Rhodes, PESC, 2008, pp.

4296-4301.

[2] F.Z. Peng, J.S. Lai, "Multilevel convertersA new breed

of power converters", IEEE Trans. Ind. Application., vol.

49, no. 3, pp. 509 - 517, May/June, 1996.

[3] E. Zeliang, D. Na, C. Jie and Z. Haifeng, "A Simple

Voltage Balancing Scheme for m-Level Diode-Clamped

Multilevel Converters Based on a Generalized Current

Flow Model", IEEE Trans on Industrial Electronics, vol.

60, no. 5, pp. 1884 - 1896, April, 2013.

[4] H. Sepahvand, K.A. Corzine, M. Ferdowsi, M. Khazraei,

"Active Capacitor Voltage Balancing in Single-Phase

Flying-Capacitor Multilevel Power Converters", IEEE

Trans on Industrial Electronics, vol. 59, no. 2, pp. 769

- 778, April, 2012.

[5] Y. Suresh and A.K. Panda, "Performance of cascade

multilevel H-Bridge inverter with single DC source by

employing low frequency three-phase transformers", 6th

Annual Conference on IEEE Industrial Electronics

Society, Glendale, AZ,. IECON. 2010, pp. 1981 - 1986.

[6] L. Jingsheng, H. Sepahvand, M. Ferdowsi, " Investigation

on Capacitor Voltage Regulation in Cascaded H-Bridge

Multilevel Converters With Fundamental Frequency

Switching", IEEE Trans on Industrial Electronic, vol. 58,

no. 11, pp. 5102 - 5111, April, 2011.

[7] S. Sirisukprasert, "The Modeling and Control of a

Cascaded-Multilevel Converter-Based STATCOM", Ph.D.

thesis, faculty of the Virginia Polytechnic Institute and

State University., Blacksburg., Virginia, 2004.

[8] J. Rodriguez, L. Jih-Sheng, P. F. Zheng, "Multilevel

inverters: a survey of topologies, controls, and

applications", IEEE Trans on Industrial Electronics, vol.

49, no. 4, pp. 724 738, Aug , 2002.

[9] Z. Xu, B. Zhang, J. S. Lai and A. Q. Huang, "A high-

frequency 1.5 MVA H-bridge building block for cascaded

multilevel converters using emitter turn-off thyrister",

Applied Power Electronics Conference and Exposition, D

allas,TX ,APEC, 2002, pp. 2732.

[10] E. Babaei, S.H. Hosseini,"New cascaded multilevel

inverter topology with minimum number of switches",

Energy Convers. Manage. vol. 50, no. 11, pp. 27612767,

Nov, 2009.

[11] Y. Suresh, A.K. Panda," Investigation on hybrid cascaded

multilevel inverter with reduced dc sources", Electrical

Power and Energy Systems, vol. 26, pp. 49-59, October,

2013.

[12] D. Vijayakumar, A. Kirubakaran, S. Umashankar," A

multilevel inverter with reduced number of switches",

Electrical, Electronics and Computer Science (SCEECS),

IEEE Students Conference on, Bhopal, 2012, pp.1-4.

[13] K.A. Corzine, M.W. Wielebski, F.Z. Peng, J. Wang,

"Control of cascaded multi-level inverters", Electric

Machines and Drives Conference, IEMDC'03, 2003, pp.

1549-1555.

[14] Z. Du, L.M. Tolbert, J.N. Chiasson, "Active harmonic

elimination for multilevel converters", IEEE Trans. Power

Electron, vol. 21, no. 2, pp. 459469, March, 2006.

[15] L. Tolbert, T.G. Habetler, "Novel multilevel inverter

carrier-based PWM method", IEEE Trans. Ind.

Appl.,vol .35, no. 2, pp. 10981107, Sep/Oct, 1999.

101

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Load Flow Analysis: A ReviewДокумент7 страницLoad Flow Analysis: A ReviewraghuevmОценок пока нет

- Smartgrid FuelcellДокумент28 страницSmartgrid FuelcellraghuevmОценок пока нет

- Simulation Tools For Power Electronics-"An Overview"Документ4 страницыSimulation Tools For Power Electronics-"An Overview"raghuevmОценок пока нет

- Lecture 13Документ6 страницLecture 13Sreekumar RajendrababuОценок пока нет

- UGC-CARE Indian Journals Indexed in Scopus (Source List) 14 2019Документ19 страницUGC-CARE Indian Journals Indexed in Scopus (Source List) 14 2019saminaОценок пока нет

- A New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarДокумент7 страницA New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarraghuevmОценок пока нет

- Chapter 12oldДокумент14 страницChapter 12oldRamada Bama SОценок пока нет

- Power Plant Economics PDFДокумент13 страницPower Plant Economics PDFYalamanchili Singam ChowdaryОценок пока нет

- Special Topic: Flexible AC Transmission Sysntem (FACTS) in Power SystemДокумент3 страницыSpecial Topic: Flexible AC Transmission Sysntem (FACTS) in Power SystemraghuevmОценок пока нет

- Ac Voltage Controller PDFДокумент36 страницAc Voltage Controller PDFsolo4000100% (3)

- Cs LabДокумент1 страницаCs LabraghuevmОценок пока нет

- L-26 (SSG) (Pe) ( (Ee) Nptel)Документ10 страницL-26 (SSG) (Pe) ( (Ee) Nptel)Abhi NáyОценок пока нет

- Facts Flexible AC Transmission System: Presented By: DR Ahmed MassoudДокумент67 страницFacts Flexible AC Transmission System: Presented By: DR Ahmed Massoudstudent_ujjwol3163Оценок пока нет

- Word PosterДокумент6 страницWord PosterraghuevmОценок пока нет

- Ezdsp F2812: Reference TechnicalДокумент32 страницыEzdsp F2812: Reference TechnicalraghuevmОценок пока нет

- A New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarДокумент7 страницA New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarraghuevmОценок пока нет

- Networks and Measurements LabortoryДокумент12 страницNetworks and Measurements LabortoryraghuevmОценок пока нет

- Power Electronics Question Bank UNIT-1Документ2 страницыPower Electronics Question Bank UNIT-1raghuevmОценок пока нет

- MMCДокумент6 страницMMCraghuevmОценок пока нет

- AppMTech AcstДокумент13 страницAppMTech AcstraghuevmОценок пока нет

- EEE SylabusДокумент48 страницEEE SylabusyashaswiyellapragadaОценок пока нет

- Organo GramДокумент6 страницOrgano GramraghuevmОценок пока нет

- Spru065c (Evnt Mang) PDFДокумент152 страницыSpru065c (Evnt Mang) PDFraghuevmОценок пока нет

- WCE2009 pp411-416Документ6 страницWCE2009 pp411-416Soumyadip GhoshОценок пока нет

- 480 SensorsДокумент21 страница480 SensorsAbdulrahman AlsalawiОценок пока нет

- PSP Ice WorkshopДокумент16 страницPSP Ice WorkshopraghuevmОценок пока нет

- Polar SingleДокумент1 страницаPolar SingleraghuevmОценок пока нет

- IntroductionДокумент10 страницIntroductionraghuevmОценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (120)

- Calculation of IDMT Over CurrentДокумент4 страницыCalculation of IDMT Over CurrentAbhishek RajputОценок пока нет

- BilldataДокумент2 страницыBilldataNishantОценок пока нет

- High Voltage, Solid State Relay OptocouplerДокумент4 страницыHigh Voltage, Solid State Relay OptocouplerTony LingОценок пока нет

- Formation of Bus Admittance Matrix UsingДокумент24 страницыFormation of Bus Admittance Matrix UsingQuazi Mosaddequl Haque100% (1)

- Interruptible Load Program: Protoc Ol GuideДокумент7 страницInterruptible Load Program: Protoc Ol GuidecspolaОценок пока нет

- DECS 200N Rev. HДокумент191 страницаDECS 200N Rev. Hneutron1988Оценок пока нет

- 7PA30121AA000 Datasheet enДокумент2 страницы7PA30121AA000 Datasheet enNguyenОценок пока нет

- Krishna+Mohan+Dwivedi+Документ4 страницыKrishna+Mohan+Dwivedi+abhishekatupesОценок пока нет

- SiabДокумент81 страницаSiabAlexandre MorenoОценок пока нет

- MATLAB Simulink Based Modeling of Solar PV Cell PDFДокумент6 страницMATLAB Simulink Based Modeling of Solar PV Cell PDFYuvarekha SenthilkumarОценок пока нет

- Automatic Gate Lamp Circuit Using LDRДокумент5 страницAutomatic Gate Lamp Circuit Using LDRsmartxdigital marketОценок пока нет

- Ee 2022Документ9 страницEe 2022LATIGAR, JEFFERSON 0.Оценок пока нет

- SensorCorriente SCT013 PDFДокумент1 страницаSensorCorriente SCT013 PDFCarmenОценок пока нет

- Type FSD Fast Acting Glass Tube Fuse 5 X 20 MM: Agency Standards and ListingsДокумент2 страницыType FSD Fast Acting Glass Tube Fuse 5 X 20 MM: Agency Standards and ListingsrОценок пока нет

- Renewable Energy WebquestДокумент3 страницыRenewable Energy Webquestapi-265544103Оценок пока нет

- NV3000 14Документ233 страницыNV3000 14Gustavo Castillo100% (1)

- Republic of The Union of Myanmar Preparatory Survey For Power Improvement Project in The Greater YangonДокумент163 страницыRepublic of The Union of Myanmar Preparatory Survey For Power Improvement Project in The Greater YangonAustin Than AungОценок пока нет

- VTX 12Документ2 страницыVTX 12faraz24Оценок пока нет

- Arduino Motor ShieldДокумент3 страницыArduino Motor Shielddigital media technologiesОценок пока нет

- FrontДокумент7 страницFrontJordan Dator MontemayorОценок пока нет

- SolHeat A2Документ1 страницаSolHeat A2Hector Valdes RojasОценок пока нет

- A Synchronous Motor Cannot Start by ItselfДокумент2 страницыA Synchronous Motor Cannot Start by ItselfRedwan AhmedОценок пока нет

- Sanyo - ds27425 Service Manual PDFДокумент30 страницSanyo - ds27425 Service Manual PDFEnrique HernándezОценок пока нет

- Power Generation BookДокумент7 страницPower Generation BookHassan MalghaniОценок пока нет

- 45-Grid Station Lighting PDFДокумент8 страниц45-Grid Station Lighting PDFEngr Muhammad Abu Bakr0% (1)

- Load Curve PPT 01Документ19 страницLoad Curve PPT 01Xen Operation DPHОценок пока нет

- HSPE-144M M6 HC Bifacial 450W Rev.00Документ2 страницыHSPE-144M M6 HC Bifacial 450W Rev.00Alejandro Holguin QuinteroОценок пока нет

- ATA24, Electrical Dash 8 q200Документ63 страницыATA24, Electrical Dash 8 q200rav100% (1)

- Tle/Epas: Quarter 1 - Module 1: Electronic TheoryДокумент24 страницыTle/Epas: Quarter 1 - Module 1: Electronic TheoryKENT REEVE ROSALОценок пока нет