Академический Документы

Профессиональный Документы

Культура Документы

Bascules

Загружено:

BIOS_012Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Bascules

Загружено:

BIOS_012Авторское право:

Доступные форматы

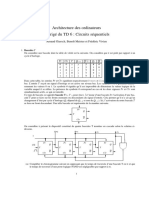

QUELQUES CIRCUITS SEQUENTIELS

1 - La Bascule Reset-Set (RS)

R(eset)

S1

Y y

∆t

S2

S(et)

l Graphe

10 Reset sans effet 10

01

À 00

Maintient

11

01

00

°

Set 10 01 Reset

e

ir

o

it

s

n

ra

11

T

10

Maintient

00

¯ 10

®

01 Set sans effet 01

l Matrice des phases et tableau des sorties

RS

00 01 11 10 s1s2

état

1 1 2 * 4 10

2 1 2 5 * 10

s 1 = s2

3 3 2 * 4 01

4 3 * 5 4 01

5 * 2 5 4 00

Structure des Ordinateurs S

Jacques Guizol Les Bascules Page 1 Ja

l Matrice réduite

RS

00 01 11 10

état

a 1 2 5 4

b 3 2 5 4

l Equation de Y et matrice de l'excitation

RS

y 00 01 11 10

Y = (y + R).S 0 0 0 0 1

1 1 0 0 1

l Equations de sortie et matrice de sortie

RS

y 00 01 11 10

s1 = y + R

0 10 10 00 00

s2 = y

1 01 01 01 01

l Représentation standard

R R

Q Q

Q Q

S S

Structure des Ordinateurs S

Jacques Guizol Les Bascules Page 2 J

l Comportement

R

Q

Q

S

|0 |1000 |2000 |687.5 |750

i n p u t R(eset)

Grossissement : x 16

input S(et)

output Q ∆t

o u t p u t ¬Q

R

Q

Q

S

|1000 |2000 |1937.5 |2000

i n p u t ¬R(eset)

input ¬S(et)

output Q

o u t p u t ¬Q

Structure des Ordinateurs S

Jacques Guizol Les Bascules Page 3 J

l Un autre modèle

Y1 y1

e1

∆1t s1

∆2t s2

e2

Y2 y2

l Graphe

01 Reset sans effet 01

10

00 ®

Maintient

11

10

00

À

Set 01 10 Reset

e

ir

o

it

s

n

ra

11

T

01

Maintient

00

° 01

¯

10 Set sans effet 10

l Matrice des phases et tableau des sorties

RS

00 01 11 10 s1s2

état

1 * 5 1 3 00

2 2 5 * 3 01

3 2 * 1 3 01

s 1 = s2

4 4 5 * 3 10

5 4 5 1 * 10

e1e2

00 01 11 10

états

a * 5 1 3

l Matrice réduite :

b 2 5 1 3

c 4 5 1 3

Structure des Ordinateurs S

Jacques Guizol Les Bascules Page 4 J

l Equations et matrice des excitations :

e1e2

y1y2 00 01 11 10

00 11 10 00 01

Y1 = e1 + y2

01 01 00 00 01

Y2 = e2 + y1 11 00 00 00 00

10 10 10 00 00

l Equations de sortie : s1 = y1 et s2 = y2

l Conclusion

+ Les états stables ne dépendent pas du modèle choisi, mais

uniquement des fonctions logiques et du nombre maximal de

boucles de retour.

e1

s1 = e1 (e2 + s)

e2

s2 = e2 + s

s

Bascule RS dépourvue de retard (y = Y)

e e s s s

1 2 1 2

s = s

0 0 0 0 1 1

s = s

0 0 1 1 0 1

s ≠ s

0 1 0 1 0 1

0 1 1 1 0 s = s

1

1 0 0 0 1 s = s

1

1 0 1 0 0 s ≠ s

1

1 1 0 0 0 s = s

1

1 1 1 0 0 s ≠ s

1

Structure des Ordinateurs

Jacques Guizol Les Bascules Page 5

2 - La Bascule JK

La bascule RS comporte un état “indésirable” atteint

lorsque les entrées R et S sont simultanément

sollicitées. Les deux sorties sont alors nulles.

Si les entrées retombent simultanément à 0, le

système va osciller.

|0 |250 |500

i n p u t R(eset)

input S(et)

output Q

o u t p u t ¬Q

Afin d'éviter ce comportement, on préfère la bascule JK

qui n'est autre qu'une RS dont les entrées sont filtrées

afin de n'autoriser un Set que si Q = 0 (Q\ = 1) et un

Reset que si Q = 1.

S

Q

J

Bascule JK

K Q

R

Structure des Ordinateurs

Jacques Guizol Les Bascules Page 6

Jacques Guizol Ja

Soit, pour dans un soucis d'homogénéité des composants :

J

Q

Bascule JK

réalisée en NAND

D'où le montage sur un circuit SN74LS01

K Q

+Vcc

Ce bistable JK permet de réaliser des éléments mémoire à

3 entrées :

Set (Mise à 1), Reset ( Mise à 0), Comp (Complémentation)

Reset

J Q

Comp

K Q

Set

Structure des Ordinateurs S

Jacques Guizol Les Bascules Page 7 Ja

Jacques Guizol J

3 - Les Bascules “D”

3.1 - Le “Latch”

Les motivations qui ont conduit à la bascule JK

peuvent se résumer ainsi eu égard à la bascule RS :

«En dehors de l'état de maintien où R = S =0,

R et S doivent être affectés à des états complémentaires»

On peut donc imaginer une seule entrée dont le

niveau logique (1 ou 0) aura pour effet d'agir sur l'une

ou l'autre des entrées de la bascule (S ou R)

D S

Bascule D

réalisée en NAND

Validation

(DV) 00

1 0 0

01

À ¯ °

01

Graphe

10 00 01 11 10 00

asynchrone

10

® 11 ±

1 11 1 0

Structure des Ordinateurs S

Jacques Guizol Les Bascules Page 8 J

Jacques Guizol J

|0 |125 |250 |375

input D

i n p u t Valid

output Q

Mode Mode Mode

mémorisation transparent mémorisation

Diagramme de temps…

…où l'on peut voir que lorsque Valid = 0, Q reste

inchangé quelles que soient les variations de D.

En considérant que Valid est un séquencement

d'horloge, on obtient le graphe synchrone :

1 (D) 0

0 Graphe

a b synchrone

1 1 0

Structure des Ordinateurs S

Jacques Guizol Les Bascules Page 9 J

Вам также может понравиться

- Examen VHDLДокумент5 страницExamen VHDLAnonymous opSQda100% (4)

- Carrefo4 TP HC11Документ12 страницCarrefo4 TP HC11BIOS_012100% (2)

- Etude Des Circuits SequentielsДокумент11 страницEtude Des Circuits Sequentielslaperouse200896% (28)

- L1i Architech ExoДокумент77 страницL1i Architech ExoNardy RazandryОценок пока нет

- Série D'exercices N°3-3tech-Bascules-Compteurs-2012-2013Документ9 страницSérie D'exercices N°3-3tech-Bascules-Compteurs-2012-2013Hyacinthe Kossi100% (3)

- Lab 56 H08Документ4 страницыLab 56 H08BIOS_012Оценок пока нет

- TD 03 PDFДокумент6 страницTD 03 PDFbenhasamОценок пока нет

- Cours Liaison EncastrementДокумент7 страницCours Liaison EncastrementBIOS_012100% (2)

- Priorites Aux Feux Pour Les BusДокумент166 страницPriorites Aux Feux Pour Les BusBIOS_012Оценок пока нет

- MaqplusДокумент4 страницыMaqplusBIOS_012Оценок пока нет

- Mini Pro Jet 2005Документ16 страницMini Pro Jet 2005BIOS_012Оценок пока нет

- LiaisonsДокумент6 страницLiaisonsBIOS_012100% (1)

- Liaisons 2Документ8 страницLiaisons 2BIOS_012100% (1)

- Flow CarfourДокумент2 страницыFlow CarfourBIOS_012Оценок пока нет

- Electronique Ex16webДокумент3 страницыElectronique Ex16webBIOS_012Оценок пока нет

- Ex 1Документ9 страницEx 1BIOS_0120% (1)

- Autom Automatec Circulation AlterneeДокумент6 страницAutom Automatec Circulation AlterneeBIOS_012Оценок пока нет

- Corrige TD06 PDFДокумент4 страницыCorrige TD06 PDFabdelgoui rymОценок пока нет

- Chapitre 1Документ13 страницChapitre 1Dhafer MezghaniОценок пока нет

- Electronique Systemes NumeriquesДокумент56 страницElectronique Systemes NumeriquesLeroy Lionel SonfackОценок пока нет

- Chapitre II Les RegistresДокумент18 страницChapitre II Les RegistresMouhamed MoustaphaОценок пока нет

- Architecture Et Technologie Des Ordinateurs - 4 - Logique SéquentielleДокумент30 страницArchitecture Et Technologie Des Ordinateurs - 4 - Logique SéquentielleGuillaume LauresОценок пока нет

- Correction Serie TD2 Mise À JourДокумент8 страницCorrection Serie TD2 Mise À JourNarkhiss TaОценок пока нет

- Simu LogidulesДокумент6 страницSimu LogidulesAbdelhamid HarakatОценок пока нет

- Elnum TD5Документ2 страницыElnum TD5benaouda31Оценок пока нет

- Chapitre III Circuits SéquentielsДокумент1 страницаChapitre III Circuits SéquentielsMathias belingaОценок пока нет

- TD1 CNДокумент3 страницыTD1 CNPapeCheikh SYLLAОценок пока нет

- Sujet TP - VHDL - AMSv1.2Документ4 страницыSujet TP - VHDL - AMSv1.2mn13hhОценок пока нет

- Bascule JK Maître EsclaveДокумент8 страницBascule JK Maître EsclaveMafiazoОценок пока нет

- Cours 1 Diagrammed e FluenceДокумент41 страницаCours 1 Diagrammed e Fluencejihadmak100% (2)

- Logique SequentielleДокумент43 страницыLogique SequentielleGauss MustОценок пока нет

- Ms ELN Touala+Djali PDFДокумент62 страницыMs ELN Touala+Djali PDFmeriem ouaОценок пока нет

- BasculeДокумент18 страницBasculeMohamed HahiouiОценок пока нет

- Suite Cours Fpga Ikram MaaouiДокумент26 страницSuite Cours Fpga Ikram MaaouiFeriel GHOUILAОценок пока нет

- Manuel Oscilloscope Tektronix THS720P (SMed79)Документ238 страницManuel Oscilloscope Tektronix THS720P (SMed79)Med100% (1)

- TD N°5Документ8 страницTD N°5NotnowОценок пока нет

- MonostablesДокумент14 страницMonostablesrouОценок пока нет

- Cours Num1Документ53 страницыCours Num1Maxence KouessiОценок пока нет

- EP0194195A1Документ8 страницEP0194195A1Elon YempОценок пока нет

- Cahier TPДокумент20 страницCahier TPMortimer MeunierОценок пока нет

- Resum Cours 1Документ5 страницResum Cours 1KdiОценок пока нет