Академический Документы

Профессиональный Документы

Культура Документы

Reference Lib PDF

Загружено:

kishoreroy88Исходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Reference Lib PDF

Загружено:

kishoreroy88Авторское право:

Доступные форматы

ASIC-System on Chip-VLSI Design: Issues with Mu...

http://asic-soc.blogspot.in/2008/04/issues-with-mul...

ASIC-System on Chip-VLSI Design

28

Digital chip design articles, tutorials, classes and news

Lenovo Ideatab A 3000

junglee.com

Lenovo A 3000 Starting from Rs. 8,150. Order Online Now!

Home

Links

Verilog

Low Power VLSI

Static Timing Analysis

Physical Design

Synthesis

DFT

Formal Verification

Issues with Multi Height Cell Placement in Multi Vt Flow

Creating the reference libraries

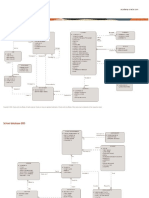

There are two reference libraries required. One is low Vt cell library and another is high Vt cell library. These

libraries have two different height cells. Reference libraries are created as per the standard synopsys flow.

Library creation flow is given in Figure 1. Read_lib command is used for this purpose. As TF and LEF files are

available TF+LEF option is chosen for library creation. After the completion of the physical library preparation

steps, logical libraries are prepared.

WRITE TO ASICSOCBLOG

Send your comments, suggestions, guest articles,

thesis, research papers to: asicsocblog@gmail.com

To subscribe asic-soc blog enter your email

address:

Subscribe

Top Posts

Figure 1 Library preparation command window

Backend (Physical Design) Interview Questions

and Answers

Below are the sequence of questions asked for a

physical design engineer. In which field are you

interested? Answer to this question...

Different Unit Tile Creation

The unit tile height of lvt cells is 2.52 and hvt cells are 1.96 . Hence two separate unit tiles have to be

created and should be added in the technology file. Hvt reference library is created with the unit tile name unit

and lvt reference library is created with unit tile name lvt_unit. By default unit tile is defined in technology file

and the other unit tile lvt_unit is also added to the technology file.

Process-Voltage-Temperature

(PVT) Variations and Static Timing

Analysis

The major design challenges of

ASIC design consist of

microscopic issues and

macroscopic issues [1]. The microscopic issues

are ultra-high s...

What is the difference between FPGA and ASIC?

This question is very popular in VLSI fresher

interviews. It looks simple but a deeper insight

into the subject reveals the fact that the...

1 of 5

04/09/2014 01:29 PM

ASIC-System on Chip-VLSI Design: Issues with Mu...

http://asic-soc.blogspot.in/2008/04/issues-with-mul...

Clock Gating

Clock tree consume more than 50

% of dynamic power. The

components of this power are: 1)

Power consumed by

combinatorial log...

Embedded System for Automatic

Washing Machine using Microchip

PIC18F Series Microcontroller

The design uses the PIC18F

series microcontroller. All the

control functionalities of the

system are built around this. Upgradeability is

th...

Clock Definitions

lock Definitions: Rising and falling

edge of the clock For a +ve edge

triggered design +ve (or rising)

edge is called ...

Figure 2. Tile height specifications in library preparation

Floor Planning

What is the difference between FPGA and

CPLD?

FPGA-Field Programmable Gate Array and

CPLD-Complex Programmable Logic Device-both are programmable logic devices made by

the same compani...

70% of the core utilization is provided. Aspect ratio is kept at 1. Rows are flipped, double backed and made

channel less. No Top Design Format (TDF) file is selected as default placement of the IO pins are considered.

Since we have multi height cells in the reference library separate placement rows have to be provided for two

different unit tiles. The core area is divided into two separate unit tile section providing larger area for Hvt unit

tile as shown in the Figure 3.

Setup and hold slack

13. Setup and hold slack Slack

Slack is defined as difference

between actual or achieved time

and the desired time for a timing

...

Temperature controller using

Microchip PIC16F877A

Microcontroller

In continuously monitoring the

surrounding temperature of

industrial applications

Temperature Monitoring Control System play v...

Verilog code for asynchronous FIFO

Verilog code for asynchronous FIFO is given

below. The module a_fifo5 should be used for

Modelsim (or any other HDL simulator)

simulation...

Figure 3. Different unit tile placement

First as per the default floor planning flow rows are constructed with unit tile. Later rows are deleted from the

part of the core area and new rows are inserted with the tile lvt_unit. Improper allotment of area can give rise

to congestion. Some iteration of trial and error experiments were conducted to find best suitable area for two

different unit tiles. The unit tile covers 44.36% of core area while lvt_unit 65.53% of the core area. PR

summary report of the design after the floor planning stage is provided below.

PR Summary:

Number of Module Cells: 70449

Number of Pins: 368936

Number of IO Pins: 298

Number of Nets: 70858

Average Pins Per Net (Signal): 3.20281

Chip Utilization:

Total Standard Cell Area: 559367.77

Core Size: width 949.76, height 947.80; area 900182.53

Chip Size: width 999.76, height 998.64; area 998400.33

Cell/Core Ratio: 62.1394%

Cell/Chip Ratio: 56.0264%

Number of Cell Rows: 392

Placement Issues with Different Tile Rows

Legal placement of the standard cells is automatically taken care by Astro tool as two separate placement area

is defined for multi heighten cells. Corresponding tile utilization summary is provided below.

Search

Read More...

Verilog

(38)

Synthesis (36)

ASIC

synthesis (34)

Verilog HDL

(34)

verilog

examples (32)

verilog

interview

questions (30)

verilog

tutorials (29)

Verification

(28)

verilog

tutorial

for

beginners (28)

ASIC (26) DSP

(22) HDL (19) Low

Power Techniques

(16) logic synhesis

(16) FPGA (15)

MATLAB

(15)

Static

Timing

Analysis (STA) (15)

Timing

Analysis

(15) logic synthesis

(13)

Mentor

Graphics

(12)

Verification IP (12)

Physical

Design

(11) DSP filters

(10) Digital design (9)

CMOS

2 of 5

(8)

Verilog

There was an error in

this gadget

Blog Archive

2014 (1)

2013 (58)

2012 (21)

2011 (7)

2010 (2)

2009 (14)

2008 (36)

December 2008

(1)

November 2008

(1)

October 2008 (1)

September 2008

(1)

August 2008 (1)

July 2008 (1)

June 2008 (7)

May 2008 (1)

April 2008 (13)

Issues with Multi

Height Cell

Placement in

Multi V...

Power Gating

Voltage Scaling

and DVFS

Multiple

Threshold

CMOS

(MTCMOS)

04/09/2014 01:29 PM

ASIC-System on Chip-VLSI Design: Issues with Mu...

http://asic-soc.blogspot.in/2008/04/issues-with-mul...

PR Summary:

[Tile Utilization]

============================================================

unit 257792 114353 44.36%

lvt_unit 1071872 702425 65.53%

============================================================

But this method of placement generates unacceptable congestion around the junction area of two separate unit

tile sections. The congestion map is shown in Figure 4.

Classes

(8)

Asynchronous

FIFO

(7) 3-D ICs (6) Basic

gates using MUX (6)

Digital filters (6) PIC

Microcontroller (6) low

power (6) .lib (5)

Libraries

(5)

PIC

16F877A (5) interview

(5) Leakage Power (4)

VIP (4) VLSI (4)

Circuits

Multi Threshold

(MVT) Voltage

Technique

Multi Vdd

(Voltage)

Clock Gating

Low Power

Design

Techniques

Reverse Biased

Diode Current

(Junction

Leakage)-Ga..

.

Sub Threshold

Current

Short Circuit

Power

Physical Design

Objective Type

of Questions

and An...

Dynamic and

Internal Power

March 2008 (4)

Figure 4. Congestion

February 2008

(2)

January 2008 (3)

There are two congestion maps. One is related to the floor planning with aspect ratio 1 and core utilization of

70%. This shows horizontal congestion over the limited value of one all over the core area meaning that design

cant be routed at all. Hence core area has to be increased by specifying height and width. The other

congestion map is generated with the floor plan wherein core area is set to 950 m. Here we can observe

although congestion has reduced over the core area it is still a concern over the area wherein two different unit

tiles merge as marked by the circle. But design can be routable and can be carried to next stages of place and

route flow provided timing is met in subsequent implementation steps.

2007 (109)

There was an error in

this gadget

Tighter timing constraints and more interrelated connections of standard cells around the junction area of

different unit tiles have lead to more congestion. It is observed that increasing the area isn't a solution to

congestion. In addition to congestion, situation verses with the timing optimization effort by the tool. Timing

target is not able to meet. Optimization process inserts several buffers around the junction area and some of

them are placed illegally due to the lack of placement area.

Corresponding timing summary is provided below:

Timing/Optimization Information:

[TIMING]

Setup Hold Num Num

Type Slack Num Total Target Slack Num Trans MaxCap Time

========================================================

A.PRE -3.491 3293 -3353.9 0.100 10000.000 0 8461 426 00:02:26

A.IPO -0.487 928 -271.5 0.100 10000.000 0 1301 29 00:01:02

A.IPO -0.454 1383 -312.8 0.100 10000.000 0 1765 36 00:01:57

A.PPO -1.405 1607 -590.9 0.100 10000.000 0 2325 32 00:00:58

A.SETUP -1.405 1517 -466.4 0.100 -0.168 6550 2221 31 00:04:10

========================================================

Since the timing is not possible to meet design has to be abandoned from subsequent steps. Hence in a multi

vt design flow cell library with multi heights are not preferred.

References

[1] Astro, User Guide, Version X-2005.09, September 2005

Tags: Congestion, Multi Vt, Physical Design, Placement

3 of 5

04/09/2014 01:29 PM

ASIC-System on Chip-VLSI Design: Issues with Mu...

http://asic-soc.blogspot.in/2008/04/issues-with-mul...

6 comments:

kiran May 5, 2008 at 6:01 PM

i hav gone through ur blog .. good collection of material.... done good job.. [:)]

Reply

Murali

May 10, 2008 at 9:02 AM

thanks a lot and enjoy !

Reply

shankar May 21, 2008 at 11:15 AM

Good & very informative collection in a glance :)

Reply

Anonymous September 21, 2008 at 4:50 AM

u r blog is very informative..I really really liked it...thanks for your efforts!!

Reply

manoz January 22, 2009 at 12:15 PM

The information posted in this blog are very effective and useful to all the people who want to contribute to VLSI

world.

This,also freshes our mind in free time.

Please do post in this blog.

Reply

Asic Design January 12, 2012 at 7:50 PM

An application-specific incorporated enterprise is a enterprise personalized for a particular use, rather than

suitable for general-purpose use. For example, a nick developed completely to run a mobile cellphone is an

ASIC. Application-specific normal items (ASSPs) are advanced between ASICs and market normal incorporated

tour like the 7400 or the 4000 sequence.

Reply

Comment as:

Publish

Select profile...

Preview

Your Comments... (comments are moderated)

Links to this post

Create a Link

Newer Post

Home

Older Post

Subscribe to: Post Comments (Atom)

Search This Blog

Search

Copyright/Disclaimer

Listed in

This work is licensed under a Creative Commons

Attribution-Share Alike 2.5 India License.

"Nahi Jnanena Sadrusham". Simple template. Powered by Blogger.

4 of 5

04/09/2014 01:29 PM

ASIC-System on Chip-VLSI Design: Issues with Mu...

5 of 5

http://asic-soc.blogspot.in/2008/04/issues-with-mul...

04/09/2014 01:29 PM

Вам также может понравиться

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Answers To Coursebook Exercises: 1 IntegersДокумент3 страницыAnswers To Coursebook Exercises: 1 Integersammara shafique86% (21)

- PAD FOUNDATION DESIGN To BS 81101997Документ15 страницPAD FOUNDATION DESIGN To BS 81101997Carlos Valverde Portilla100% (1)

- Ophthalmologist Email List - Ophthalmologist Mailing ListДокумент3 страницыOphthalmologist Email List - Ophthalmologist Mailing Listgary gillenОценок пока нет

- Clock Balance Ieee Seminar04Документ49 страницClock Balance Ieee Seminar04Anvesh Reddy100% (1)

- Sparecell PDFДокумент7 страницSparecell PDFkishoreroy88Оценок пока нет

- Forum Digital Design and Programming ASIC Design Methodologies and Tools (Digital)Документ9 страницForum Digital Design and Programming ASIC Design Methodologies and Tools (Digital)kishoreroy88Оценок пока нет

- Setup and Hold Basics - 1 PDFДокумент23 страницыSetup and Hold Basics - 1 PDFkishoreroy88Оценок пока нет

- Ir em Syn PDFДокумент6 страницIr em Syn PDFKhadar BashaОценок пока нет

- Setup and Hold Basics PDFДокумент3 страницыSetup and Hold Basics PDFkishoreroy88Оценок пока нет

- Forum Digital Design and Programming ASIC Design Methodologies and Tools (Digital)Документ9 страницForum Digital Design and Programming ASIC Design Methodologies and Tools (Digital)kishoreroy88Оценок пока нет

- Ece5950 T08 Cad Par PDFДокумент56 страницEce5950 T08 Cad Par PDFkishoreroy88Оценок пока нет

- Clock Tree Synthesis For Clock Gating - Cadence ..Документ2 страницыClock Tree Synthesis For Clock Gating - Cadence ..kishoreroy88Оценок пока нет

- Book PDДокумент5 страницBook PDkishoreroy88Оценок пока нет

- ClockDistribution FRIEDMANДокумент28 страницClockDistribution FRIEDMANLionel RiviereОценок пока нет

- 465 Antenna EffectsДокумент30 страниц465 Antenna EffectsMikayel TorosyanОценок пока нет

- Perl One Liner 2Документ12 страницPerl One Liner 2kishoreroy88Оценок пока нет

- Power PlanningДокумент4 страницыPower Planningkishoreroy88Оценок пока нет

- Perl One LinerДокумент5 страницPerl One Linerkishoreroy88Оценок пока нет

- Joint Target Tracking and Classification Using Radar and ESM SensorsДокумент17 страницJoint Target Tracking and Classification Using Radar and ESM SensorsYumnaОценок пока нет

- OTRSMaster SlaveДокумент22 страницыOTRSMaster Slaveing_llenkiОценок пока нет

- Exam 1 Study Guide Chapter Questions TypesДокумент3 страницыExam 1 Study Guide Chapter Questions TypesTrang LeОценок пока нет

- DbmsДокумент26 страницDbmsSoumik DasОценок пока нет

- MSIM 602 Simulation Fundamentals AssignmentДокумент2 страницыMSIM 602 Simulation Fundamentals Assignmentahaque08Оценок пока нет

- Comprehensive Project Plan - Sean SectionsДокумент2 страницыComprehensive Project Plan - Sean SectionsSean HodgsonОценок пока нет

- Resume RealДокумент2 страницыResume RealKurt Ronald SanJuan EstebanОценок пока нет

- E Gazette User Manual PDF 07052018Документ26 страницE Gazette User Manual PDF 07052018Gitesh SalunkeОценок пока нет

- CPointer HKДокумент37 страницCPointer HKhardworking_studentОценок пока нет

- Temperature Controlled Fan Using PIC 16F877A - GadgetronicxДокумент8 страницTemperature Controlled Fan Using PIC 16F877A - Gadgetronicxdevchandar100% (1)

- Programming Logic Concepts For TCS NQTДокумент39 страницProgramming Logic Concepts For TCS NQTAjay Kumar Reddy KummethaОценок пока нет

- Basic Model Behavior With StellaДокумент5 страницBasic Model Behavior With StellaLenin Bullon VillanesОценок пока нет

- Noa MopДокумент103 страницыNoa MopRaja SolaimalaiОценок пока нет

- Programming Logic and Design Comprehensive 7th Edition Joyce Farrell Solutions ManualДокумент36 страницProgramming Logic and Design Comprehensive 7th Edition Joyce Farrell Solutions Manualhangingboune82um100% (9)

- Worksheet BFH - SolutionДокумент7 страницWorksheet BFH - SolutionAmogh D GОценок пока нет

- Reshma Resume RaysДокумент5 страницReshma Resume RaysReshmaОценок пока нет

- 18 08 29Документ22 страницы18 08 29Florian MuellerОценок пока нет

- Managing Government Records Module 1 Benefits ARCS ORCSДокумент4 страницыManaging Government Records Module 1 Benefits ARCS ORCSAndrea ManaloОценок пока нет

- GRCDP00696190000029942Документ2 страницыGRCDP00696190000029942Gokul KrishnanОценок пока нет

- PLSQL Schema ERD and Table DesignsДокумент8 страницPLSQL Schema ERD and Table DesignsSoham GholapОценок пока нет

- Game Development Using BuildboxДокумент2 страницыGame Development Using BuildboxGm SudheerОценок пока нет

- Cse Viii Advanced Computer Architectures 06CS81 Notes PDFДокумент156 страницCse Viii Advanced Computer Architectures 06CS81 Notes PDFHarshith HarshiОценок пока нет

- Iso-Pas 17004 2005 PDFДокумент11 страницIso-Pas 17004 2005 PDFCarlos Felipe Orjuela RamírezОценок пока нет

- World Wide WebДокумент57 страницWorld Wide WebmerinОценок пока нет

- L6 Systems of InequalitiesДокумент25 страницL6 Systems of InequalitiesFlorence FlorendoОценок пока нет

- Visual Tracking of Athletes in Beach Volleyball Using A Single CameraДокумент9 страницVisual Tracking of Athletes in Beach Volleyball Using A Single CameraThomas MauthnerОценок пока нет